以下、本発明の実施形態を図面に基づいて説明する。

<演算装置の構成>

図1は、本発明の実施形態に係る演算装置1の機能的な構成を示す機能ブロック図である。演算装置1は、二進法でそれぞれ表現される変数(具体的には、被乗数と乗数)の乗算を行うものであり、シフトレジスタ2、符号拡張・シフトレジスタ3、制御回路部4、および演算回路部5を備える。

シフトレジスタ2は、本発明の被乗数記憶部に相当するものであり、二進法で表現された被乗数のデータの入力に応じて、該被乗数のデータ、すなわちビット列を記憶する。このシフトレジスタ2は、制御回路部4からのシフト制御信号に応答して、記憶している被乗数のデータの桁をシフトする。

符号拡張・シフトレジスタ3は、本発明の乗数記憶部に相当するものであり、二進法で表現された乗数のデータの入力に応じて、該乗数を符号拡張した乗数(以下「符号拡張乗数」とも称する)を生成し、該符号拡張乗数を記憶する。なお、ここで言う「符号拡張」とは、符号付きのデータをビット長の大きいデータに変換する際に、値を変えないようにビットを補ってデータを拡張することである。また、この符号拡張・シフトレジスタ3は、制御回路部4からのシフト制御信号に応答して、記憶している被乗数のデータの桁をシフトする。

なお、当該実施形態においては、乗数を符号拡張した「符号拡張乗数」を用いているが、符合拡張を行っていない乗数を用い、当該乗数を乗数記憶部に記憶させる構造に応用することもできる。

制御回路部4は、例えば、論理回路などによって構成され、符号拡張乗数のビットのパターンの認識に応じて、シフトレジスタ2および符号拡張・シフトレジスタ3へのシフト制御信号の出力を制御するとともに、演算回路部5における演算を制御する。具体的には、この制御回路部4は、符号拡張・シフトレジスタ3に記憶される符号拡張乗数におけるビットのパターンを認識し、その認識結果に応じて、被乗数に係る加算を指示する信号(以下「加算信号」とも称する)または被乗数に係る減算を指示する信号(以下「減算信号」とも称する)を演算回路部5に対して出力する。より詳細には、制御回路部4は、符号拡張乗数におけるビットの数値の下桁側からの配列を認識し、その配列の認識結果に応じた演算を順次に行うことを決定して、その決定に応じた加算信号および減算信号のうちの少なくとも一方の信号を順次に出力する。なお、ここで決定される演算には、加算基調の演算と減算基調の演算とがあり、まず、加算基調の演算が行われた後に、加算基調の演算および減算基調の演算のうちの少なくとも一方の演算が順次に行われることが決定される。「加算基調の演算」および「減算基調の演算」の演算内容については後述する。

演算回路部5は、例えば、論理回路などによって構成され、制御回路部4による決定結果に応じて、加算基調の演算および減算基調の演算を行う。具体的には、制御回路部4から演算回路部5に入力される加算信号に応答して、シフトレジスタ2から被乗数のデータを読み出して該被乗数のデータに係る加算を行い、制御回路部4から演算回路部5に入力される減算信号に応答して、シフトレジスタ2から被乗数のデータを読み出して該被乗数のデータに係る減算を行う。そして、演算回路部5において、被乗数の桁を順次に上位側にシフトさせつつ、順次に被乗数の加減算を行うことにより、被乗数と乗数との乗算の演算結果を示すデータ(以下「演算結果データ」とも称する)が導出され、該演算結果データが演算回路部5から出力される。

なお、当該実施形態においては、被乗数をシフトレジスタ2で左にシフトすることによって倍数を作り、演算回路部5で加減算する構造となっているが、当該構造に限定されない。例えば、被乗数のデータを記憶するレジスタを、被乗数のビット列をシフトしないレジスタとして、演算回路部に設けられたシフトレジスタにおいて加減算の結果のビット列を右にシフトさせることで、被乗数のデータを相対的に左にシフトしても良い。この変形例に係る演算装置1aの機能的な構成を示す機能ブロック図を図2に例示する。図2では、図1で示した演算装置1と同様な構成については同じ符号が付されている。演算装置1aでは、演算装置1と比較して、シフトレジスタ2がビット列のシフトを行わないレジスタ2aに変更され、制御回路部4がシフト制御信号の出力先が演算回路部5aとされた制御回路部4aに変更され、演算回路部5がシフトレジスタを含む演算回路部5aに変更されている。そして、演算回路部5aが、制御回路部4aからのシフト制御信号に応じて加減算の結果を示すビット列をシフトしつつ、レジスタ2aから被乗数のデータを読み込んで、加算信号および減算信号に応じて被乗数の加減算を行う。当該構成においては、演算に必要なビットの記憶場所が固定されるので、回路サイズの縮小および動作速度の向上を図ることができる。

<演算装置における演算処理フロー>

図3から図5は、演算装置1における演算処理フローを示すフローチャートである。本演算処理フローは、演算装置1への被乗数および乗数のデータの入力に応答して開始される。

ステップS1では、符号拡張・シフトレジスタ3により、乗数について1ビット分の符号拡張が行われ、乗数のデータが1ビット増加される。このとき、符号拡張された乗数(符号拡張乗数)のデータが符号拡張・シフトレジスタ3に記憶される。

ステップS2では、制御回路部4により、符号拡張乗数の数値の認識対象となるビットの桁を特定するためのカウント値nが1に設定される。

ステップS3では、制御回路部4により、符号拡張乗数の全ビットに係る数値が認識されたか否か判定される。ここでは、全ビットに係る数値が認識されていなければ、ステップS4に進み、全ビットに係る数値が認識されていれば、図5のステップS31に進む。

ステップS4では、制御回路部4により、符号拡張乗数の最も下位の桁(最下桁)からn番目およびn+1番目のビットの数値が認識される。

ステップS5では、制御回路部4により、符号拡張乗数の最下桁からn番目のビットの数値が1であるか否か判定される。ここでは、符号拡張乗数の最下桁からn番目のビットの数値が1であれば、ステップS6に進み、符号拡張乗数の最下桁からn番目のビットの数値が1でなければ、ステップS7に進む。

ステップS6では、制御回路部4により、符号拡張乗数の最下桁からn+1番目のビットの数値が1であるか否か判定される。ここでは、n+1番目のビットの数値が1であれば、ステップS8に進み、n+1番目のビットの数値が1でなければ、ステップS10に進む。

ステップS7では、制御回路部4により、カウント値nが1増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが1ビット分左にシフトされる。つまり、被乗数のデータが1桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張乗数のデータが1ビット分右にシフトされる。つまり、符号拡張乗数のデータが1桁下位側にシフトされる。そして、ステップS7の処理が終了すると、ステップS3に進む。

ステップS8では、制御回路部4から減算信号が演算回路部5に出力され、演算回路部5により、シフトレジスタ2に記憶される被乗数のデータに係る減算が行われる。具体的には、被乗数の符号ビットの数値は正論理、その他のビットの数値は負論理で加算される。つまり、被乗数の符号ビットの数値はそのまま加算され、被乗数のその他のビットの数値は反転された上で加算される。

ステップS9では、制御回路部4により、カウント値nが2つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが2ビット分左にシフトされる。つまり、被乗数のデータが2桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張乗数のデータが2ビット分右にシフトされる。つまり、符号拡張乗数のデータが2桁下位側にシフトされる。そして、ステップS9の処理が終了すると、図4のステップS21に進む。

ステップS10では、制御回路部4から加算信号が演算回路部5に出力され、演算回路部5により、シフトレジスタ2に記憶される被乗数のデータに係る加算が行われる。具体的には、被乗数の符号ビットの数値は負論理、その他のビットの数値は正論理で加算される。つまり、被乗数の符号ビットの数値は反転されて加算され、被乗数のその他のビットの数値はそのまま加算される。

ステップS11では、制御回路部4により、カウント値nが2つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが2ビット分左にシフトされる。つまり、被乗数のデータが2桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張乗数のデータが2ビット分右にシフトされる。つまり、符号拡張乗数のデータが2桁下位側にシフトされる。そして、ステップS11の処理が終了すると、ステップS3に進む。

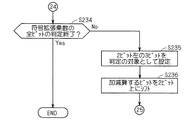

図4のステップS21では、図3のステップS3と同様に、制御回路部4により、符号拡張乗数の全ビットに係る数値が認識されたか否か判定される。ここでは、全ビットに係る数値が認識されていなければ、ステップS22に進み、全ビットに係る数値が認識されていれば、図5のステップS31に進む。

ステップS22では、制御回路部4により、符号拡張乗数の最下桁からn番目およびn+1番目のビットの数値が認識される。

ステップS23では、制御回路部4により、符号拡張乗数の最下桁からn番目のビットの数値が0であるか否か判定される。ここでは、符号拡張乗数の最下桁からn番目のビットの数値が0であれば、ステップS24に進み、符号拡張乗数の最下桁からn番目のビットの数値が0でなければ、ステップS25に進む。

ステップS24では、制御回路部4により、符号拡張乗数の最下桁からn+1番目のビットの数値が0であるか否か判定される。ここでは、符号拡張乗数の最下桁からn+1番目のビットの数値が0であれば、ステップS26に進み、符号拡張乗数の最下桁からn+1番目のビットの数値が0でなければ、ステップS28に進む。

ステップS25では、図3のステップS7と同様に、制御回路部4により、カウント値nが1増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが1ビット分左にシフトされる。つまり、被乗数のデータが1桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張乗数のデータが1ビット分右にシフトされる。つまり、符号拡張乗数のデータが1桁下位側にシフトされる。そして、ステップS25の処理が終了すると、ステップS21に進む。

ステップS26では、図3のステップS10と同様に、制御回路部4から加算信号が演算回路部5に出力され、演算回路部5により、シフトレジスタ2に記憶される被乗数のデータに係る加算が行われる。具体的には、被乗数の符号ビットの数値は負論理、その他のビットの数値は正論理で加算される。つまり、被乗数の符号ビットの数値は反転されて加算され、被乗数のその他のビットの数値はそのまま加算される。

ステップS27では、図3のステップS11と同様に、制御回路部4により、カウント値nが2つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが2ビット分左にシフトされる。つまり、被乗数のデータが2桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張乗数のデータが2ビット分右にシフトされる。つまり、符号拡張乗数のデータが2桁下位側にシフトされる。そして、ステップS27の処理が終了すると、図3のステップS3に進む。

ステップS28では、図3のステップS8と同様に、制御回路部4から減算信号が演算回路部5に出力され、演算回路部5により、シフトレジスタ2に記憶される被乗数のデータに係る減算が行われる。具体的には、被乗数の符号ビットの数値は正論理、その他のビットの数値は負論理で加算される。つまり、被乗数の符号ビットの数値はそのまま加算され、被乗数のその他のビットの数値は反転された上で加算される。

ステップS29では、図3のステップS9と同様に、制御回路部4により、カウント値nが2つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが2ビット分左にシフトされる。つまり、被乗数のデータが2桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張乗数のデータが2ビット分右にシフトされる。つまり、符号拡張乗数のデータが2桁下位側にシフトされる。そして、ステップS29の処理が終了すると、ステップS21に進む。

図5のステップS31では、制御回路部4および演算回路部5により、図3のステップS8,S10、および図4のステップS26,S28で加減算された際に負論理で扱われたビットの項に1が代入され、正論理で扱われたビットの項に0が代入された上で加算されることで、オフセット値が算出される。なお、被乗数に0を代入して、ステップS1〜S29の処理を行うことでオフセット値を算出しても良い。このオフセット値は、被乗数が0になった場合には、被乗数と乗数との乗算結果が0となるべきところ、演算の誤差によって生じる0からの値のズレ(ズレ値)を示す。

ステップS32では、制御回路部4および演算回路部5により、ステップS31で算出されたオフセット値の2の補数が所定の定数として算出される。

ステップS33では、図3および図4のステップS1〜S29における順次の加減算によって得られた値に、ステップS32で算出された所定の定数が加算されることで、被乗数と乗数との乗算結果が求められて、本演算処理フローが終了される。ステップS33では、被乗数に0を代入して被乗数と乗数との乗算結果が0からずれる値(ズレ値)を相殺することを目的として、所定の定数が加算される。

図3から図5で示す演算処理フローでは、主に、加算基調の演算、減算基調の演算、および所定の定数の加算が行われる。図3のステップS3〜S11の演算処理が加算基調の演算に相当し、図4のステップS21〜S29で示される演算処理が減算基調の演算に相当し、図5のステップS31〜S33の演算処理が所定の定数の加算に相当する。そして、図3で示すように、演算装置1における被乗数と乗数との乗算では、まず、加算基調の演算から開始される。

具体的には、加算基調の演算は、符号拡張乗数におけるビットの数値の下桁側からの配列において「0」が連続して出現する間に「1」が単独で出現すると、被乗数の加算が行われる加算を基調とする演算である。より詳細には、加算基調の演算では、符号拡張乗数におけるビットの数値の下桁側からの配列において、「0」が連続している場合には被乗数の加算も減算も行われず、下桁側から順に見て、ビットの数値に「1」が出現し且つ下桁側からのビットの数値の配列が「1、0」である場合には被乗数の加算が行われ、ビットの数値に「1」が出現し且つ下桁側からのビットの数値の配列が「1、1」である場合には減算基調の演算に移行されつつ被乗数の減算が行われる。つまり、「1」が連続するパターンが出現するまで、「1」が単独して出現すれば、被乗数の加算が行われ、「1」が連続するパターンが出現すれば、減算基調の演算への移行が行われる。

また、減算基調の演算は、符号拡張乗数におけるビットの数値の下桁側からの配列において、「1」が連続して出現する間に「0」が単独で出現すると、被乗数の減算が行われる減算を基調とする演算である。より詳細には、減算基調の演算では、符号拡張乗数におけるビットの数値の下桁側からの配列において、「1」が連続している場合には被乗数の加算も減算も行われず、下桁側から順に見て、ビットの数値に「0」が出現し且つ下桁側からのビットの数値の配列が「0、1」である場合には被乗数の減算が行われ、ビットの数値に「0」が出現し且つ下桁側からのビットの数値の配列が「0、0」である場合には加算基調の演算に移行されつつ被乗数の加算が行われる。つまり、「0」が連続するパターンが出現するまで、「0」が単独して出現すれば、被乗数の減算が行われ、「0」が連続するパターンが出現すれば、加算基調の演算への移行が行われる。

換言すれば、制御回路部4は、符号拡張乗数におけるビットの数値の下桁側からの配列を認識して、該配列が下桁側から順に0が連続した後に1、0となる場合に被乗数に係る加算を行い、該配列が下桁側から順に0が連続した後に1、1となる場合に被乗数に係る減算を行うことを決定する。また、制御回路部4は、該配列が下桁側から順に1が連続した後に0、1となる場合に被乗数に係る減算を行い、該配列が下桁側から順に1が連続した後に0、0となる場合に被乗数に係る加算を行うことを決定する。

<演算装置における演算例>

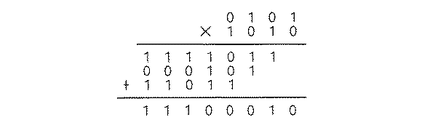

図6は、演算装置1における演算例を示す図である。図6では、十進法で表現された「5×(−6)」の乗算を行う例が示されている。図6(a)で示すように、被乗数に相当する十進法の「5」は、二進法の4ビット整数表記では「0101」であり、乗数に相当する十進法の「−6」は、二進法の4ビット整数表記では「1010」である。そして、図6(a)で示すように、図3および図4のステップS1〜S29における加減算によって、二進法の7ビット整数表記の「0101010」が得られる。また、図6(b)で示すように、図5のステップS31における演算により、二進法の7ビット整数表記のオフセット値「1001000」が算出される。そして、図6(c)で示すように、図3および図4のステップS1〜S29における加減算によって得られた二進法の7ビット整数表記の「0101010」に、オフセット値の2の補数「10111000」が加算されることで、被乗数と乗数との乗算結果「11100010」が得られる。この二進法の8ビット整数表記の「11100010」は、十進法では「−30(=−27+26+25+21)」であり、十進法で表現された「5×(−6)」の乗算が正しく行われていることが分かる。

<加減算の決定方法のバリエーション>

上記実施形態に係る演算装置1では、乗数をそのまま符号拡張して被乗数に係る加減算の決定に利用したが、これに限られない。例えば、乗数の2の補数を算出し、この値を仮の乗数として被乗数に係る加減算の決定に利用するようにしても良い。以下では、上記実施形態のようにそのまま符号拡張した乗数を用いて被乗数に係る加減算を決定する乗算アルゴリズムを「WS法の乗算アルゴリズム」と称し、乗数の2の補数を符号拡張した値を用いて被乗数に係る加減算を決定する乗算アルゴリズムを「2の補数のWS法の乗算アルゴリズム」と称する。なお、WS法の乗算アルゴリズムと、2の補数のWS法の乗算アルゴリズムとは、加減算の決定方法が異なるが、結果的に被乗数に係る加減算の内容は同一となる。ここで、2の補数のWS法の乗算アルゴリズムについて説明する。

図7から図9は、演算装置1において、2の補数のWS法の乗算アルゴリズムを採用した場合の演算処理フローを示すフローチャートである。本演算処理フローは、演算装置1への被乗数および乗数のデータの入力に応答して開始される。

ステップS101では、図示を省略する演算回路により、乗数の2の補数が算出され、この算出された値を仮の乗数(仮乗数)として、該仮乗数が符号拡張・シフトレジスタ3に入力される。

ステップS102では、符号拡張・シフトレジスタ3により、仮乗数について1ビット分の符号拡張が行われ、仮乗数のデータが1ビット増加される。このとき、符号拡張された仮乗数(符号拡張仮乗数)のデータが符号拡張・シフトレジスタ3に記憶される。

ステップS103では、制御回路部4により、符号拡張乗数の数値の認識対象となるビットの桁を特定するためのカウント値nが1に設定される。

ステップS104では、制御回路部4により、符号拡張仮乗数の全ビットに係る数値が認識されたか否か判定される。ここでは、全ビットに係る数値が認識されていなければ、ステップS105に進み、全ビットに係る数値が認識されていれば、図9のステップS131に進む。

ステップS105では、制御回路部4により、符号拡張仮乗数の最下桁からn番目およびn+1番目のビットの数値が認識される。

ステップS106では、制御回路部4により、符号拡張仮乗数の最下桁からn番目のビットの数値が1であるか否か判定される。ここでは、符号拡張仮乗数の最下桁からn番目のビットの数値が1であれば、ステップS107に進み、符号拡張仮乗数の最下桁からn番目のビットの数値が1でなければ、ステップS108に進む。

ステップS107では、制御回路部4により、符号拡張仮乗数の最下桁からn+1番目のビットの数値が1であるか否か判定される。ここでは、符号拡張仮乗数の最下桁からn+1番目のビットの数値が1であれば、ステップS109に進み、符号拡張仮乗数の最下桁からn+1番目のビットの数値が1でなければ、ステップS111に進む。

ステップS108では、制御回路部4により、カウント値nが1つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが1ビット分左にシフトされる。つまり、被乗数のデータが1桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張仮乗数のデータが1ビット分右にシフトされる。つまり、符号拡張仮乗数のデータが1桁下位側にシフトされる。そして、ステップS108の処理が終了されると、ステップS104に進む。

ステップS109では、制御回路部4から加算信号が演算回路部5に出力され、演算回路部5により、シフトレジスタ2に記憶される被乗数のデータに係る加算が行われる。具体的には、被乗数の符号ビットの数値は負論理、その他のビットの数値は正論理で加算される。つまり、被乗数の符号ビットの数値は反転されて加算され、被乗数のその他のビットの数値はそのまま加算される。

ステップS110では、制御回路部4により、カウント値nが2つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが2ビット分左にシフトされる。つまり、被乗数のデータが2桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張仮乗数のデータが2ビット分右にシフトされる。つまり、符号拡張仮乗数のデータが2桁下位側にシフトされる。そして、ステップS110の処理が終了すると、図8のステップS121に進む。

ステップS111では、制御回路部4から減算信号が演算回路部5に出力され、演算回路部5により、シフトレジスタ2に記憶される被乗数のデータに係る減算が行われる。具体的には、被乗数の符号ビットの数値は正論理、その他のビットの数値は負論理で加算される。つまり、被乗数の符号ビットの数値はそのまま加算され、被乗数のその他のビットの数値は反転された上で加算される。

ステップS112では、制御回路部4により、カウント値nが2つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが2ビット分左にシフトされる。つまり、被乗数のデータが2桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張仮乗数のデータが2ビット分右にシフトされる。つまり、符号拡張仮乗数のデータが2桁下位側にシフトされる。そして、ステップS112の処理が終了すると、ステップS104に進む。

図8のステップS121では、図7のステップS104と同様に、制御回路部4により、符号拡張仮乗数の全ビットに係る数値が認識されたか否か判定される。ここでは、全ビットに係る数値が認識されていなければ、ステップS122に進み、全ビットに係る数値が認識されていれば、図9のステップS131に進む。

ステップS122では、制御回路部4により、符号拡張仮乗数の最下桁からn番目およびn+1番目のビットの数値が認識される。

ステップS123では、制御回路部4により、符号拡張仮乗数の最下桁からn番目のビットの数値が0であるか否か判定される。ここでは、符号拡張仮乗数の最下桁からn番目のビットの数値が0であれば、ステップS124に進み、符号拡張仮乗数の最下桁からn番目のビットの数値が0でなければ、ステップS125に進む。

ステップS124では、制御回路部4により、符号拡張仮乗数の最下桁からn+1番目のビットの数値が0であるか否か判定される。ここでは、符号拡張仮乗数の最下桁からn+1番目のビットの数値が0であれば、ステップS126に進み、符号拡張仮乗数の最下桁からn+1番目のビットの数値が0でなければ、ステップS128に進む。

ステップS125では、図7のステップS108と同様に、制御回路部4により、カウント値nが1つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが1ビット分左にシフトされる。つまり、被乗数のデータが1桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張仮乗数のデータが1ビット分右にシフトされる。つまり、符号拡張仮乗数のデータが1桁下位側にシフトされる。

ステップS126では、図7のステップS111と同様に、制御回路部4から減算信号が演算回路部5に出力され、演算回路部5により、シフトレジスタ2に記憶される被乗数のデータに係る減算が行われる。具体的には、被乗数の符号ビットの数値は正論理、その他のビットの数値は負論理で加算される。つまり、被乗数の符号ビットの数値はそのまま加算され、被乗数のその他のビットの数値は反転された上で加算される。

ステップS127では、図7のステップS112と同様に、制御回路部4により、カウント値nが2つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが2ビット分左にシフトされる。つまり、被乗数のデータが2桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張仮乗数のデータが2ビット分右にシフトされる。つまり、符号拡張仮乗数のデータが2桁下位側にシフトされる。そして、ステップS127の処理が終了すると、図7のステップS104に進む。

ステップS128では、図7のステップS109と同様に、制御回路部4から加算信号が演算回路部5に出力され、演算回路部5により、シフトレジスタ2に記憶される被乗数のデータに係る加算が行われる。具体的には、被乗数の符号ビットの数値は負論理、その他のビットの数値は正論理で加算される。つまり、被乗数の符号ビットの数値は反転されて加算され、被乗数のその他のビットの数値はそのまま加算される。

ステップS129では、図7のステップS110と同様に、制御回路部4により、カウント値nが2つ増加されるとともに、制御回路部4からシフト制御信号が出力されて、シフトレジスタ2に記憶される被乗数のデータが2ビット分左にシフトされる。つまり、被乗数のデータが2桁上位側にシフトされる。また、このとき、符号拡張・シフトレジスタ3に記憶される符号拡張仮乗数のデータが2ビット分右にシフトされる。つまり、符号拡張仮乗数のデータが2桁下位側にシフトされる。そして、ステップS129の処理が終了すると、ステップS121に進む。

図9のステップS131では、図5のステップS31と同様に、制御回路部4および演算回路部5により、図7のステップS109,S111、および図8のステップS126,S128で加減算された際に負論理で扱われたビットの項に1が代入され、正論理で扱われたビットの項に0が代入された上で加算されることで、オフセット値が算出される。

ステップS132では、制御回路部4および演算回路部5により、ステップS131で算出されたオフセット値の2の補数が所定の定数として算出される。

ステップS133では、図7および図8のステップS101〜S129における順次の加減算によって得られた値に、ステップS132で算出された所定の定数が加算されることで、被乗数と乗数との乗算結果が求められて、本演算処理フローが終了される。

<従来技術との比較>

図10は、演算装置1における被乗数に係る加減算の回数と、従来技術における被乗数に係る加減算の回数とを比較するための図である。図10では、二進法で表現された乗数が26ビットの「01011010100000100111100110」である場合に、被乗数と乗数との乗算を行う際に、被乗数の加減算が行われる桁、つまり被乗数の加減算の回数が示されている。具体的には、図10(a)がブースの乗算アルゴリズムを用いた場合に被乗数の加減算が行われる桁を示し、図10(b)が定数加算法の乗算アルゴリズムを用いた場合に被乗数の加減算が行われる桁を示し、図10(c)が2の補数の定数加算法の乗算アルゴリズムを用いた場合に被乗数の加減算が行われる桁を示し、図10(d)がWS法の乗算アルゴリズムを用いた場合に被乗数の加減算が行われる桁を示し、図10(e)が2の補数のWS法の乗算アルゴリズムを用いた場合に被乗数の加減算が行われる桁を示している。なお、図10では、被乗数に係る加算が行われる桁の数値が太線Addで囲まれ、被乗数に係る減算が行われる桁の数値が細線Subで囲まれている。

図10(a)で示すように、ブースの乗算アルゴリズムを用いた場合には、合計14回の被乗数に係る加減算(7回の被乗数に係る加算、および7回の被乗数に係る減算)が行われる。また、図10(b)で示すように、定数加算法の乗算アルゴリズムを用いた場合には、12回の被乗数に係る加算が行われる。また、図10(c)で示すように、2の補数の定数加算法の乗算アルゴリズムを用いた場合には、合計14回の被乗数に係る加減算(1回の被乗数に係る加算、および13回の被乗数に係る減算)が行われる。これに対して、図10(d),(e)で示すように、WS法の乗算アルゴリズムおよび2の補数のWS法の乗算アルゴリズムを用いた場合には、合計10回の被乗数に係る加減算(6回の被乗数に係る加算、および4回の被乗数に係る減算)が行われる。したがって、従来技術と比較して、WS法の乗算アルゴリズムおよび2の補数のWS法の乗算アルゴリズムを用いた場合には、被乗数に係る加減算の回数が低減される。

ここで、二進法で表現されるNビット(Nは2以上の自然数)の乗数と被乗数とを乗算する場合について、被乗数に係る加減算の最大回数を考える。ブースの乗算アルゴリズムを用いる場合、仮に乗数を構成するビットの数値の配列が1と0とが全長に渡って交互に並ぶものとなると、被乗数に係る加減算の回数が最大回数である(N−1)回となる。また、定数加算法の乗算アルゴリズムを用いる場合、仮に乗数を構成するビットの数値の配列が1が全長に渡って並ぶものとなると、被乗数に係る加減算の回数が最大回数であるN回となる。更に、2の補数の定数加算法の乗算アルゴリズムを用いる場合、仮に乗数の2の補数を構成するビットの数値の配列が1が全長に渡って並ぶものとなると、被乗数に係る加減算の回数が最大回数であるN回となる。

これに対して、WS法の乗算アルゴリズムを用いる場合には、仮に乗数を構成するビットの数値の配列が1と0とが全長に渡って交互に並ぶものとなると、Nが偶数の場合には、被乗数に係る加減算の回数が最大回数であるN/2回となり、Nが奇数の場合には、被乗数に係る加減算の回数が最大回数である(N+1)/2回となる。また、2の補数のWS法の乗算アルゴリズムを用いる場合にも、仮に乗数の2の補数を構成するビットの数値の配列が1と0とが全長に渡って交互に並ぶものとなると、Nが偶数の場合には、被乗数に係る加減算の回数が最大回数であるN/2回となり、Nが奇数の場合には、被乗数に係る加減算の回数が最大回数である(N+1)/2回となる。

したがって、乗数が4ビット以上のものであれば、ブースの乗算アルゴリズム、定数加算法の乗算アルゴリズム、および2の補数の定数加算法の乗算アルゴリズムを用いる従来技術と比べて、WS法の乗算アルゴリズムおよび2の補数のWS法の乗算アルゴリズムを用いる場合には、乗数と被乗数とを乗算する際における被乗数に係る加減算の最大回数が相対的に少なくなる。そして、演算回路部5の構成や性能が、被乗数に係る加減算の最大回数に合わせたものとなることを考慮すると、WS法の乗算アルゴリズムおよび2の補数のWS法の乗算アルゴリズムを採用することで、従来技術と比較して、乗算における加算および減算の最大回数が低減されるため、演算装置1の小型化および演算速度の向上を図ることができる。このような効果は、乗数のビット数が増える程、顕著となる。

図11は、二進法で表現された乗数が図10で示すような26ビットの「01011010100000100111100110」である場合に、被乗数に係る加減算および所定の定数の加算を行う演算態様を示すイメージ図である。図11では、被乗数の加算に係るビット列Addと、被乗数の減算に係るビット列Subと、所定の定数の加算に係るビット列Constとが模式的に示されており、ビット列Add,Sub,Constが相互に加算されることで、被乗数と乗数との乗算結果が得られる。

なお、以上では、被乗数および乗数の双方が変数である場合にも被乗数と乗数との乗算が可能な構成を示して説明したが、これに限られない。例えば、乗数が既知の定数である場合には、予め乗数のビットの数値の配列を解析して、被乗数の加減算を行う桁、ならびに加算するための所定の定数を求めておくことができる。そして、乗算を実際に行う際には、乗数のビットを解析することなく、シフトレジスタにおいて被乗数のデータを決められた桁までシフトしつつ該被乗数に係る加算または減算を順次に行うとともに、所定の定数を加算するようにすれば良い。このような構成を採用することで、例えば、演算装置1から符号拡張・シフトレジスタ3を取り除き、制御回路部4および演算回路部5の構成の簡略化を図った演算回路を実現することができる。

<WS法の乗算アルゴリズムの画像表示装置への応用>

図12は、ビデオカメラ10、テレビ20、および画像表示装置30を備えて構成される映像システムを例示する図である。ビデオカメラ10は、NTSCの規格に基づく画像信号(以下「NTSC信号」と称する)を取得して、該NTSC信号をテレビ20および画像表示装置30に提供する。テレビ20は、アナログテレビとして構成され、NTSC信号をそのまま利用して、該NTSC信号に基づく動画を表示する。一方、画像表示装置30は、NTSC信号から、赤(R)色、緑(G)色、青(B)色の3原色の画像信号(以下「RGB画像信号」と称する)に変換した上で、該RGB画像信号に基づく動画を表示する。この画像表示装置30では、NTSC信号からRGB画像信号を生成する際に、上述したWS法の乗算アルゴリズムを利用する。以下、画像表示装置30の構成について説明する。

<画像表示装置の構成>

図13は、画像表示装置30の機能構成を示すブロック図である。画像表示装置30は、信号変換部31、RGB変換部32、タイミング制御部33、表示パネルDP、XドライバXd、およびYドライバYdを備える。

信号変換部31は、NTSC信号を受け付け、アナログ動画信号であるNTSC信号を所定の規格(例えば、ITU−R BT.601)で規定されたフォーマットに沿ってデジタル信号に変換し、該デジタル信号の各フレームを構成する各画素の信号(画素信号)について、いわゆるYC分離(輝度信号と色差信号とを高精度に分離する技術)を行う。そして、信号変換部31は、YC分離によって得られる輝度信号であるYのデータと、色差信号であるCr,Cbのデータとを出力する。

RGB変換部32は、上式(1)〜(3)で示される所定の変換式に沿って、各フレームの画素信号について、入力画像信号であるY,Cr,Cbのデータを表示用画像信号であるR,G,Bのデータ(RGB画像信号)に変換する。図14は、RGB変換部32の構成を例示する図である。正数を示すYのデータが、上式(1)〜(3)の演算を行う回路に供され、整数を示すCrのデータが、上式(1),(2)の演算を行う回路に供され、整数を示すCbのデータが、上式(2),(3)の演算を行う回路に供される。このRGB変換部32では、上式(1)〜(3)に沿った演算に上述したWS法の乗算アルゴリズムを利用する。この演算の具体例については後述する。

タイミング制御部33は、NTSC信号の水平同期信号Hsyncおよび垂直同期信号Vsyncに基づき、XドライバXdに制御信号(例えば、スタートパルスSTH)を出力するとともに、YドライバYdに制御信号(例えば、スタートパルスSTV)を出力することで、表示パネルDPにおける動画像の表示タイミングを制御する。

表示パネルDPは、例えば、有機EL素子などの発光素子をそれぞれ含む多数の発光部がマトリックス状に配列されたディスプレイを備え、例えば、横320×縦240のドットからなるQVGAの解像度の画像が再生可能に構成されている。ここでは、多数の発光部は、それぞれR色の光を発する発光素子を有する発光部と、G色の光を発する発光素子を有する発光部と、B色の光を発する発光素子を有する発光部とによって構成されている。そして、表示パネルDPは、RGB画像信号に基づいて画像を表示する表示部として機能する。

XドライバXdは、タイミング制御部33からのスタートパルスSTH、およびRGB変換部32からのRGB画像信号に基づき、該RGB画像信号に含まれる各画素のデータ信号(画素信号)に応じた電位を表示パネルDPに配設された画像信号線に付与する。

YドライバYdは、タイミング制御部33からのスタートパルスSTVに応答して、表示パネルDPに配設された走査信号線に所定の電位を付与する。

<WS法の乗算アルゴリズムを用いたRGB変換>

Y,Cr,CbのデータをR,G,Bのデータに変換する変換式は、具体的には、下式(4)〜(6)で示される。

R=1.164×(Y−16)+1.596×(Cr−128) ・・・(4)

G=1.164×(Y−16)−0.391×(Cb−128)−0.813×(Cr−128) ・・・(5)

B=1.164×(Y−16)+2.018×(Cb−128) ・・・(6)。

ここでは、Yが0〜255の範囲で変化する場合が示されている。そして、上式(4)〜(6)において、(Y−16)となるのは、Yの0〜15は同期信号として使用され、16〜255が実際の輝度信号になるためである。但し、Yが0〜15のときには、輝度信号が負の値を示すことになるが、この場合には、RGB色の発光が不要となるため、RGBの信号を0とする。また、Cr,Cbについては、正負を含む整数を示す8ビットの数値であり、(Cr−128)および(Cb−128)は、それぞれ8ビットの整数(−128〜127)の範囲で変化する。

ここで、下式(7),(8)の関係が成立するものとして、上式(4)〜(6)に下式(7),(8)を代入して整理すると、下式(9)〜(11)が得られる。

(Cr−128)=(Cr*) ・・・(7)

(Cb−128)=(Cb*) ・・・(8)。

R=1.164×(Y)+1.596×(Cr*)−18.624 ・・・(9)

G=1.164×(Y)−0.391×(Cb*)−0.813×(Cr*)−18.624 ・・・(10)

B=1.164×(Y)+2.018×(Cb*)−18.624 ・・・(11)。

更に、上式(9)〜(11)の各定数の表現を十進法から二進法に書き換えると、下式(12)〜(14)が得られる。

R=1.00101010×(Y)+1.10011001×(Cr*)−10010.10100000 ・・・(12)

G=1.00101010×(Y)−0.01100100×(Cb*)−0.11010000×(Cr*)−10010.10100000 ・・・(13)

B=1.00101010×(Y)+10.00000101×(Cb*)−10010.10100000 ・・・(14)。

図15〜図17は、WS法の乗算アルゴリズムを使用して上式(12)〜(14)にそれぞれ従った演算を行う過程を示す図である。詳細には、図15では、上式(12)に従ってY,Cr*のデータからRのデータを導出する演算を行う過程が示され、図16では、上式(13)に従ってY,Cb*,Cr*のデータからGのデータを導出する演算を行う過程が示され、図17では、上式(14)に従ってY,Cb*のデータからBのデータを導出する演算を行う過程が示されている。また、ここでは、(Y)を、二進法の表現で最上位が符号ビットではない8ビットの「(Y7)(Y6)(Y5)(Y4)(Y3)(Y2)(Y1)(Y0)」と表し、Y7〜Y0には、0または1の数値が入る。また、(Cr)を、二進法の表現で最上位が符号ビットである8ビットの「(Cr7)(Cr6)(Cr5)(Cr4)(Cr3)(Cr2)(Cr1)(Cr0)」と表し、(Cb)を、二進法の表現で最上位ビットが符号ビットである8ビットの「(Cb7)(Cb6)(Cb5)(Cb4)(Cb3)(Cb2)(Cb1)(Cb0)」と表す。なお、Cr0〜Cr7およびCb0〜Cb7には、0または1の数値が入る。更に、図15〜図17では、小数点が入る桁を明確化するために、小数点が入る位置に太破線が付されている。

ここで、(Cr*)および(Cb*)すなわち(Cr−128)および(Cb−128)については、(Cr)および(Cb)と比較して最上位ビットが反転する。例えば、(Cr)の最上位ビットの数値が"1"である場合には、(Cr−128)は正の値となり、その値を表す整数の符号ビットの値は"0"となる。また、(Cr)の最上位ビットの数値が"0"である場合には、(Cr−128)は負の値となり、その値を表す整数の符号ビットの値は"1"となる。具体的には、(Cr*)すなわち(Cr−128)は、二進法の表現では「(notCr7)(Cr6)(Cr5)(Cr4)(Cr3)(Cr2)(Cr1)(Cr0)」となり、(Cb*)すなわち(Cb−128)は、二進法の表現では「(notCb7)(Cb6)(Cb5)(Cb4)(Cb3)(Cb2)(Cb1)(Cb0)」となる。なお、(notCr7)は(Cr7)のビットを反転したものを示し、(notCb7)は(Cb7)のビットを反転したものを示す。したがって、WS法の乗算アルゴリズムの演算では、最上位ビットを負論理として加算を行う場合には、最上位ビットの数値は(Cb7)および(Cr7)の正論理で加算が行われることになるが、所定の定数を求めるためのオフセット値の算出については、最上位ビットは負論理の項として扱われる。

以下、図15〜図17を参照しつつ、被乗数が正負の双方を取り得るCb,Crの項についてWS法の乗算アルゴリズムを使用して上式(12)〜(14)にそれぞれ従った演算を行う過程について説明する。なお、図15〜図17では、ハッチングが付されず且つ単に太枠で囲まれたビットは、正論理で加算されるが、オフセット値の算出については負論理のビットの項として扱われる。また、ハッチングが付され且つ太線で囲まれたビットは、負論理で加算され、且つオフセット値の算出についても負論理のビットの項として扱われる。更に、ハッチングが付され且つ細線で囲まれたビットは、負論理で加算されるが、オフセット値の算出については正論理のビットの項として扱われる。

図15(a)では、1〜4行目が「+1.00101010×(Y)」の項の演算を示し、5〜9行目が「1.10011001×(Cr*)」の項の演算を示し、10行目がオフセット値を相殺するための所定の定数を示し、11行目が「10010.10100000」の負数を示し、12行目が小数点以下を四捨五入するために加算する数を示す。そして、図15(b)では、図15(a)で示すビット列に係る加算のうち、10〜12行目の定数部分をまとめたものが示されている。

図16(a)では、1〜4行目が「+1.00101010×(Y)」の項の演算を示し、5〜7行目が「−0.01100100×(Cb*)」の項の演算を示し、8〜10行目が「−0.11010000×(Cr*)」の項の演算を示し、11行目がオフセット値を相殺するための所定の定数を示し、12行目が「10010.10100000」の負数を示し、13行目が小数点以下を四捨五入するために加算する数を示す。そして、図16(b)では、図16(a)で示すビット列に係る加算のうち、11〜13行目の定数部分をまとめたものが示されている。

図17(a)では、1〜4行目が「+1.00101010×(Y)」の項の演算を示し、5〜7行目が「+10.00000101×(Cb*)」の項の演算を示し、8行目がオフセット値を相殺するための所定の定数を示し、9行目が「10010.10100000」の負数を示し、10行目が小数点以下を四捨五入するために加算する数を示す。そして、図17(b)では、図17(a)で示すビット列に係る加算のうち、8〜10行目の定数部分をまとめたものが示されている。

このように、Y,Cr,CbのデータをR,G,Bのデータに変換する際に、WS法の乗算アルゴリズムを採用することで、入力画像信号に相当するY,Cr,Cbのデータから、表示用信号に相当するRGBのデータに変換するための構成の簡略化と演算速度の高速化とが容易に図られる。このため、画像表示装置30の小型化および製造コストの低減が図られる。

<変形例>

本発明は上述の実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更、改良等が可能である。

◎例えば、上記実施形態に係る演算装置1では、例えば、論理回路を用いて演算を行うことを基本としていたが、これに限られない。例えば、演算装置1における演算を行う構成の一部または全部の構成がCPUにおいてソフトウエアが実行されることで機能的に実現されても良い。以下、被乗数と乗数との乗算アルゴリズムをソフトウエアを用いて実現する演算装置1Aを具体例として説明する。

図18は、本発明の変形例に係る演算装置1Aの概略構成を示す図である。図18で示すように、演算装置1Aは、CPU100およびメモリ200をバスラインBLで接続した一般的なコンピュータの構成を有する。なお、メモリ200は、適宜RAMやROMやハードディスクなどの記憶部を含む。また、バスラインBLは、適宜インターフェース(図示を省略)などを介して表示部300および操作部400に接続される。そして、CPU100がメモリ200に格納されるプログラムに従って動作することにより、演算装置1Aの各種機能および動作が実現される。

図19は、演算装置1Aにおいて実現される機能的な構成を示すブロック図である。図19で示すように、演算装置1Aは、CPU100とメモリ200との協働により機能的な構成として、被乗数保持部101、乗数保持部102、シフト反転部103、デコーダ部104、モードマシン部105、タイミング制御部106、および加算部107を備える。例えば、被乗数保持部101、および乗数保持部102は、主にメモリ200などによって実現され、シフト反転部103、デコーダ部104、モードマシン部105、タイミング制御部106、および加算部107は、主に、CPU100などによって実現される。

被乗数保持部101は、外部からバスラインBLを介して入力されてくる被乗数のデータを一時的に保持し、該被乗数のデータが適宜シフト反転部103によって読み出される。

乗数保持部102は、外部からバスラインBLを介して入力されてくる乗数のデータを一時的に保持する。また、乗数保持部102では、乗数のデータのビット数に応じて、符号拡張が行われる。そして、該乗数のビット列が2ビットずつ右(すなわち下位側)に順次にシフトされる毎に、該乗数のビット列から連続する3ビットの数値がデコーダ部104に読み出される。

シフト反転部103は、被乗数を+2倍した数値(以下「+2倍被乗数」と称する)のデータ、被乗数を−1倍した数値(以下「−1倍被乗数」と称する)のデータ、および被乗数を−2倍した数値(以下「−2倍被乗数」と称する)のデータを生成する。つまり、シフト反転部103は、+2倍被乗数、被乗数の+1倍の数値(以下「+1倍被乗数」と称する)、−1倍被乗数、および−2倍被乗数の各データを準備する。また、シフト反転部103は、デコーダ部104からの指令に従って、+2倍被乗数、+1倍被乗数、−1倍被乗数、および−2倍被乗数のうちの何れかの数値のデータを加算部107に対して出力する。

デコーダ部104は、乗数保持部102から読み出した連続する3ビットの数値の配列パターン(ビットパターン)に応じて、モードマシン部105に対して、加算基調の演算を行うモード(以下「モード0」と称する)と減算基調の演算を行うモード(以下「モード1」と称する)との間でモードを切り替えるための指令を送出する。また、デコーダ部104は、モードマシン部105によって設定されているモードを参照しつつ、乗数保持部102から読み出した連続する3ビットの数値の配列パターン(ビットパターン)に応じて、+2倍被乗数、+1倍被乗数、−1倍被乗数、および−2倍被乗数のうちの何れの数値の加算を行うのかを決定し、決定した結果に応じた指令をシフト反転部103に出力する。

モードマシン部105は、デコーダ部104からの指令に従って、モード0とモード1との間でモードを切り替えて、該モードの設定状態を示す情報を保持する。

タイミング制御部106は、スタートパルスに応じて、乗数および被乗数のデータの入力のタイミングと、各構成の動作とが適宜同期するように、演算装置1Aの動作を制御する。

加算部107は、シフト反転部103から出力される+2倍被乗数、+1倍被乗数、−1倍被乗数、および−2倍被乗数のうちの何れかの数値を順次に加算する。但し、加算部107は、デコーダ部104において連続する3ビットの数値の配列パターン(ビットパターン)が認識されるごとに、それまでの加算結果を示すビット列が左(すなわち上位側)に2ビットずつシフトされる。なお、加算部107における加算では、最上位ビットの桁が揃うように、+2倍被乗数、+1倍被乗数、−1倍被乗数、および−2倍被乗数の符号拡張が行われる。

図20から図25は、演算装置1Aにおける演算処理フローを示すフローチャートである。本演算処理フローは、演算装置1Aへの被乗数および乗数のデータの入力に応答して開始される。

ステップS201では、乗数保持部102により、乗数のデータのビット数が2n+1(nは自然数)であるか否か判定される。ここでは、ビット数が2n+1であれば、ステップS202に進み、ビット数が2n+1でなければ、ステップS203に進む。

ステップS202では、乗数保持部102により、乗数について2ビット分符号拡張が行われ、ステップS204に進む。ここで符号拡張された乗数を「符号拡張乗数」と称する。

ステップS203では、乗数保持部102により、乗数について1ビット分符号拡張が行われ、ステップS204に進む。ここで符号拡張された乗数を「符号拡張乗数」と称する。

ステップS204では、シフト反転部103により、被乗数保持部101から被乗数のデータが読み出されて、+2倍被乗数、+1倍被乗数、−1倍被乗数、および−2倍被乗数がそれぞれ算出される。

ステップS205では、モードマシン部105により、デフォルトのモードとして、加算基調の演算を行うモード0が設定される。

ステップS206では、デコーダ部104により、符号拡張乗数の最下位から3ビットが判定対象として設定される。

ステップS207では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"000"であるか否か判定される。ここで、ビットパターンが"000"であれば、加減算を行うことなく、図22のステップS231に進み、ビットパターンが"000"でなければ、ステップS208に進む。

ステップS208では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"001"であるか否か判定される。ここで、ビットパターンが"001"であれば、ステップS209に進み、ビットパターンが"001"でなければ、図21のステップS211に進む。

ステップS209では、シフト反転部103から加算部107に対して+1倍被乗数のデータが出力され、加算部107により、+1倍被乗数が符号拡張されつつ加算される。

図21のステップS211では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"010"であるか否か判定される。ここで、ビットパターンが"010"であれば、ステップS212に進み、ビットパターンが"010"でなければ、ステップS213に進む。

ステップS212では、シフト反転部103から加算部107に対して+2倍被乗数のデータが出力され、加算部107により、+2倍被乗数が符号拡張されつつ加算されて、図22のステップS231に進む。

ステップS213では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"011"であるか否か判定される。ここで、ビットパターンが"011"であれば、ステップS214に進み、ビットパターンが"011"でなければ、ステップS216に進む。

ステップS214では、モードマシン部105により、加算基調の演算を行うモード0から減算基調の演算を行うモード1にモード設定が変更される。

ステップS215では、シフト反転部103から加算部107に対して−1倍被乗数のデータが出力され、加算部107により、−1倍被乗数が符号拡張されつつ加算され、図23のステップS234に進む。なお、ここでは、−1倍被乗数の加算は、+1倍被乗数の減算と同一の演算となる。

ステップS216では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"100"であるか否か判定される。ここで、ビットパターンが"100"であれば、加減算を行うことなく、図22のステップS231に進み、ビットパターンが"100"でなければ、ステップS217に進む。

ステップS217では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"101"であるか否か判定される。ここで、ビットパターンが"101"であれば、ステップS218に進み、ビットパターンが"101"でなければ、ステップS219に進む。

ステップS218では、シフト反転部103から加算部107に対して+1倍被乗数のデータが出力され、加算部107により、+1倍被乗数が符号拡張されつつ加算され、図22のステップS231に進む。

ステップS219では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"110"であるか否か判定される。ここで、ビットパターンが"110"であれば、ステップS220に進み、ビットパターンが"110"でなければ、ステップS222に進む。なお、ステップS222に進む場合には、判定対象の3ビットのビットパターンが"111"であることを意味する。

ステップS220では、ステップS214と同様に、モードマシン部105により、加算基調の演算を行うモード0から減算基調の演算を行うモード1にモード設定が変更される。

ステップS221では、シフト反転部103から加算部107に対して−2倍被乗数のデータが出力され、加算部107により、−2倍被乗数が符号拡張されつつ加算され、図23のステップS234に進む。なお、ここでは、−2倍被乗数の加算は、+2倍被乗数の減算と同一の演算となる。

ステップS222では、ステップS214と同様に、モードマシン部105により、加算基調の演算を行うモード0から減算基調の演算を行うモード1にモード設定が変更される。

ステップS223では、ステップS215と同様に、シフト反転部103から加算部107に対して−1倍被乗数のデータが出力され、加算部107により、−1倍被乗数が符号拡張されつつ加算され、図23のステップS234に進む。なお、ここでは、−1倍被乗数の加算は、+1倍被乗数の減算と同一の演算となる。

図22のステップS231では、ステップS202,S203で符号拡張されたビットも含めた符号拡張乗数の全ビットについてのビットパターンの判定が終了しているか否か判定される。ここでは、符号拡張乗数の全ビットについてのビットパターンの判定が終了していれば、本動作フローが終了され、符号拡張乗数の全ビットについてのビットパターンの判定が終了していなければ、ステップS232に進む。

ステップS232では、乗数保持部102により、符号拡張乗数のビット列が2ビット右(すなわち下位側)にシフトされて、デコーダ部104による判定対象の3ビットが2ビット左(すなわち上位側)に設定される。つまり、判定対象の3ビットが、符号拡張乗数の2ビット分上位側に変更される。

ステップS233では、加算部107により、これまでの加算結果を示すビット列が相対的に右(すなわち下位側)に2ビット分シフトされて、図20のステップS207に進む。

図23のステップS234では、ステップS202,S203で符号拡張されたビットも含めた符号拡張乗数の全ビットについてのビットパターンの判定が終了しているか否か判定される。ここでは、符号拡張乗数の全ビットについてのビットパターンの判定が終了していれば、本動作フローが終了され、符号拡張乗数の全ビットについてのビットパターンの判定が終了していなければ、ステップS235に進む。

ステップS235では、乗数保持部102により、符号拡張乗数のビット列が2ビット右(すなわち下位側)にシフトされて、デコーダ部104による判定対象の3ビットが2ビット左(すなわち上位側)に設定される。つまり、判定対象の3ビットが、符号拡張乗数の2ビット分上位側に変更される。

ステップS236では、加算部107により、これまでの加算結果を示すビット列が相対的に左(すなわち下位側)に2ビット分シフトされて、図24のステップS241に進む。

なお、ステップS231,S234で本演算処理フローが終了される場合には、加算部107において算出されている加算結果が、被乗数と乗数との乗算結果として、加算部107から出力される。

図24のステップS241では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"000"であるか否か判定される。ここで、ビットパターンが"000"であれば、ステップS242に進み、ビットパターンが"000"でなければ、ステップS244に進む。

ステップS242では、モードマシン部105により、減算基調の演算を行うモード1から加算基調の演算を行うモード0にモード設定が変更される。

ステップS243では、ステップS218と同様に、シフト反転部103から加算部107に対して+1倍被乗数のデータが出力され、加算部107により、+1倍被乗数が符号拡張されつつ加算され、図22のステップS231に進む。

ステップS244では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"001"であるか否か判定される。ここで、ビットパターンが"001"であれば、ステップS245に進み、ビットパターンが"001"でなければ、ステップS247に進む。

ステップS245では、ステップS242と同様に、モードマシン部105により、減算基調の演算を行うモード1から加算基調の演算を行うモード0にモード設定が変更される。

ステップS246では、ステップS212と同様に、シフト反転部103から加算部107に対して+2倍被乗数のデータが出力され、加算部107により、+2倍被乗数が符号拡張されつつ加算され、図22のステップS231に進む。

ステップS247では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"010"であるか否か判定される。ここで、ビットパターンが"010"であれば、ステップS248に進み、ビットパターンが"010"でなければ、図25のステップS251に進む。

ステップS248では、シフト反転部103から加算部107に対して−1倍被乗数のデータが出力され、加算部107により、−1倍被乗数が符号拡張されつつ加算され、図23のステップS234に進む。なお、ここでは、−1倍被乗数の加算は、+1倍被乗数の減算と同一の演算となる。

図25のステップS251では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"011"であるか否か判定される。ここで、ビットパターンが"011"であれば、加減算を行うことなく、図23のステップS234に進み、ビットパターンが"011"でなければ、ステップS252に進む。

ステップS252では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"100"であるか否か判定される。ここで、ビットパターンが"100"であれば、ステップS253に進み、ビットパターンが"100"でなければ、ステップS255に進む。

ステップS253では、ステップS242と同様に、モードマシン部105により、減算基調の演算を行うモード1から加算基調の演算を行うモード0にモード設定が変更される。

ステップS254では、ステップS243と同様に、シフト反転部103から加算部107に対して+1倍被乗数のデータが出力され、加算部107により、+1倍被乗数が符号拡張されつつ加算され、図22のステップS231に進む。

ステップS255では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"101"であるか否か判定される。ここで、ビットパターンが"101"であれば、ステップS256に進み、ビットパターンが"101"でなければ、ステップS257に進む。

ステップS256では、シフト反転部103から加算部107に対して−2倍被乗数のデータが出力され、加算部107により、−2倍被乗数が符号拡張されつつ加算され、図23のステップS234に進む。なお、ここでは、−2倍被乗数の加算は、+2倍被乗数の減算と同一の演算となる。

ステップS257では、デコーダ部104により、判定対象である3ビットの数値の配列パターン(ビットパターン)が"110"であるか否か判定される。ここで、ビットパターンが"110"であれば、ステップS258に進み、ビットパターンが"110"でなければ、加減算を行うことなく、図23のステップS234に進む。

ステップS258では、シフト反転部103から加算部107に対して−1倍被乗数のデータが出力され、加算部107により、−1倍被乗数が符号拡張されつつ加算され、図23のステップS234に進む。なお、ここでは、−1倍被乗数の加算は、+1倍被乗数の減算と同一の演算となる。

以上のように、被乗数と乗数との乗算アルゴリズムをソフトウエアを用いて実現する演算装置1Aについて説明したが、演算装置1Aでは、ビットを反転させる負論理や所定の定数の加算などを行わない。これは、ソフトウエアによってCPUで実現される演算では、ビットを反転させる演算のルーチンや、所定の定数の加算を行うための演算のルーチンが別途必要になるため、これらの演算については、行われない方が演算速度や演算による負荷低減を図る上で好ましい。したがって、演算装置1Aでは、被乗数の符号拡張を行いつつ、被乗数に係る加算および減算が行われることで、演算の簡略化が図られて、被乗数と乗数との乗算結果が求められるように構成される。

これに対して、上記実施形態に係る演算装置1の様に、例えば、論理回路を用いて演算を行うことを基本とする場合には、ビットを反転させる演算は、NAND回路などによって容易に実現され、演算に対する論理圧縮も可能である。このため、所定の定数を算出して、加算する演算も容易に実現可能である。また、所定の定数を加算する方式では、加減算する被乗数の符号拡張が不要となり、論理回路の構成の複雑化も招かない。したがって、上記実施形態に係る演算装置1の様に、例えば、論理回路を用いて演算を行うことを基本とする場合には、ビットの反転や、所定の定数の加算を行う演算を採用することで、被乗数の符号拡張を行うことなく、乗算を行うことが可能となり、演算を行う部分の構成の簡略化が図られる。

◎また、上記実施形態に係る画像表示装置30では、明度および色差を示す信号であるY,Cr,Cbの信号を、所定のルールに従ってRGBの各色の階調を示す信号に変換する演算において、WS法の乗算アルゴリズムを適用する例を挙げて説明したが、これに限られない。例えば、温度の変化に対して、いわゆるγ変換のためのテーブルを補正する演算に、WS法の乗算アルゴリズムを適用するようにしても良い。

◎また、上記実施形態に係る画像表示装置30では、RGBの3原色の光の組合せによって各種画像が表現されたが、これに限られず、例えば、イエロー(Y)、マゼンタ(M)、シアン(C)などのその他の複数の色の組合せによって各種画像が表現されても良い。なお、このような構成においても、上記実施形態と同様に、明度および色差を示す信号を所定のルールに従って各色の階調を示す信号に変換するための演算にWS法の乗算アルゴリズムを適用すれば良い。