JP2010039266A - 楽音信号生成装置 - Google Patents

楽音信号生成装置 Download PDFInfo

- Publication number

- JP2010039266A JP2010039266A JP2008202926A JP2008202926A JP2010039266A JP 2010039266 A JP2010039266 A JP 2010039266A JP 2008202926 A JP2008202926 A JP 2008202926A JP 2008202926 A JP2008202926 A JP 2008202926A JP 2010039266 A JP2010039266 A JP 2010039266A

- Authority

- JP

- Japan

- Prior art keywords

- address

- waveform

- memory

- page

- sample

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000005236 sound signal Effects 0.000 title abstract description 23

- 230000015654 memory Effects 0.000 claims abstract description 242

- 238000005070 sampling Methods 0.000 claims abstract description 88

- 230000006870 function Effects 0.000 claims description 8

- 238000000034 method Methods 0.000 description 25

- 238000010586 diagram Methods 0.000 description 7

- 238000001514 detection method Methods 0.000 description 6

- 238000004364 calculation method Methods 0.000 description 5

- 230000008569 process Effects 0.000 description 5

- 230000008859 change Effects 0.000 description 4

- 238000003530 single readout Methods 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 3

- 230000002123 temporal effect Effects 0.000 description 3

- 238000004891 communication Methods 0.000 description 2

- 239000012636 effector Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 238000003825 pressing Methods 0.000 description 2

- 230000001360 synchronised effect Effects 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000009191 jumping Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

Images

Landscapes

- Electrophonic Musical Instruments (AREA)

Abstract

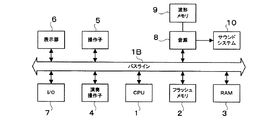

【解決手段】高速ページアクセス可能な波形メモリ9は、8アドレス単位のページサイズpでページ分けされ、各ページの最終アドレスに記憶されたサンプルは、その次のページの先頭アドレスに重複して記憶されている。アドレスカウンタ11は、各発音チャンネルの読み出しレートを累算して、サンプルアドレスを生成し、メモリアドレス生成部12は、サンプルアドレスの整数部SAiとInt[SAi/(p−1)]を加算して、メモリアドレスMAを生成する。メモリアドレスMAを用いて波形メモリをページアクセスしMAと(MA+1)とから2サンプルを読み出して、読み出した2サンプル間をサンプルアドレスの小数部SAfに基づいて補間して、各発音チャンネルの補間済み波形サンプルを累算して、サンプリング周期毎に複数発音チャンネルの楽音信号を生成する。

【選択図】図3

Description

各発音チャンネルのサンプル間補間に用いるサンプルは、サンプリング周期毎に、波形メモリから読み出すようになっているので、発音チャンネル毎のバッファメモリが不要であり、その分だけ楽音信号生成装置の構成を簡単化することができる。

従って、この発明にかかる楽音信号生成装置によれば、簡単な構成で、波形メモリ9に対するアクセス速度を向上して、発音チャンネル数を増やすことができるという優れた効果を奏する。

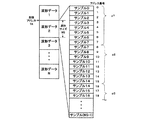

例えば、第1ページp1の最終アドレスであるアドレス番号7に記憶された「サンプル7」は、その次の第2ページp2の先頭アドレスであるアドレス番号8にも記憶されており、アドレス番号8に続くアドレス番号9以降に「サンプル7」に続く「サンプル8」以降の波形サンプルが順次記憶される。同様に、ページp2の最終アドレスであるアドレス番号15に記憶された「サンプル14」は、その次のページp3の先頭アドレスであるアドレス番号16にも記憶されており、アドレス番号17以降に「サンプル14」に続く「サンプル15」以降の波形サンプルが順次記憶される。

つまり、各ページの最終アドレスに記憶された波形サンプルが、次のページの先頭アドレスに重複して記憶されていることを除けば、各波形サンプルは、アドレス番号の順に、波形データの瞬時位相の時間的進展に従って1つずつ時系列順に並べて記憶されている。

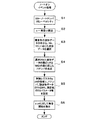

また、音源部8は、システムクロックに基づき、サンプリング周期を、所定複数の発音チャンネルに対応するタイムスロットごとに等分割して、各タイムスロットごとの時分割チャンネルタイミングにおいて、それぞれ対応する発音チャンネルの処理を実行することで、複数の発音チャンネルの時分割動作を行う。具体的には、アドレスカウンタ11、メモリアドレス生成部12、サンプル間補間部13、および音量EG付与部14が、それぞれ、所定の複数発音チャンネルの時分割動作を行う。そして、ミキサ15がサンプリング周期毎に該所定の複数発音チャンネルのデータを累算することで、音源部8は、全体として、サンプリング周期毎に複数発音チャンネル分の楽音信号を生成する処理を行う。

メモリアドレスMAを求めるために行われる演算式は、

MA=TA+SAi+Int[SAi/(p−1)]…(式1)

である。

この演算式(1)において、「TA」は、波形データの先頭アドレスであり、何れかのページの先頭になるよう調整されている。「SAi」はアドレスカウンタ11から供給されたサンプルアドレスの整数部である。「p」はページサイズ(1ページのアドレス数)である。Int[SAi/(p−1)]はサンプルアドレス整数部SAiの関数であって、計算式[SAi/(p−1)]の整数部を求める関数である。(式1)により、サンプルアドレス整数部SAiは、先頭アドレスTAを初期値とし、且つ、Int[SAi/(p−1)]が加算されたメモリアドレスMAに変換される。

この(式1)によりサンプルアドレス整数部SAiに基づくメモリアドレスMAを生成することで、詳しくは後述する通り、各ページの最終アドレスに対応する値となるところで、次のページの先頭アドレスとなるよう後ろにシフトして、該最終アドレスに対応する値を飛び越す(避ける)よう変換して該メモリアドレスMAを生成することができる。これにより、該メモリアドレスを用いてアクセスされる2サンプルが、波形メモリ9の2つのページ境界をまたがないものとなる。この変換は、ページアクセスによる2サンプルの読み出しを実現するために必須である。

音量EG部14は、各サンプリング周期毎に、制御レジスタ17に設定された各発音チャンネル毎の音量エンベロープパラメータに基づいて当該発音チャンネルの音量の時間変化を示す音量エンベロープ波形AEGを生成し、サンプル間補間部13から出力された当該発音チャンネルの補間済み波形サンプルの音量を、該音量エンベロープ波形AEGで制御する。

各サンプリング周期毎に、音源部8から波形メモリ9に対して、時分割で複数発音チャンネル分のページアクセスが行われる。当該発音チャンネルのページアクセスでは、まず最初のアクセスでアドレス信号としてメモリアドレスMAの値「0」が出力され、上位アドレス「0」(4ビット目以上)で選択されたページの、下位アドレス「0」(3ビット)で選択されたデータ、すなわち、アドレス番号「0」の「サンプル0」が読み出される。次の第2のアクセスでメモリアドレス「1」が出力されるが、最初のアクセスと同一ページ内のアドレスであるので、高速ページモードでのアクセスが可能であり、最初のアクセスより短いアクセス時間で、アドレス番号1の「サンプル1」が読み出される。図5において、楕円図像は、波形メモリ9に対する1度のページアクセスにより波形メモリ9から読み出される2アドレス分の波形サンプルを明示するものであって、メモリアドレスMAとして「0」が出力されたときに読み出される2つの波形サンプルを示す楕円図像に符号30を付与している。

このため、メモリアドレスMAを求める演算式(1)において、サンプルアドレス整数部SAiにInt[SAi/(p−1)]を加算することで、順番に進行させて行くと、各ページの最終アドレスとなってしまうMAを次のページの先頭アドレスへシフトして、メモリアドレスMAとして各ページの最終アドレスに該当する値が生成されないようになっている。

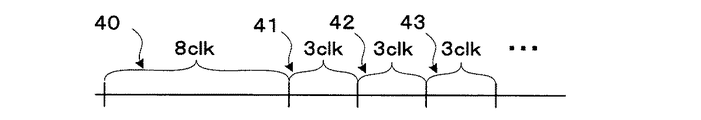

例えば、音源部8のシステムクロックを14ナノ秒(14ns)、1サンプリング周期のシステムクロック数を1536クロック(サンプリング周波数は46.5kHz)とすると、図6の例では、最初のアクセスに8クロック、第2のアクセスに3クロック掛かるので、各発音チャンネルのページアクセスにかかるクロック数は、「8+3」=「11クロック」である。従って、この条件では、音源部8に設けられる最大発音チャンネル数は、1536/「8+3」=139チャンネルとなる。

対するに、従来の通常モードでのアクセスでは、2回のアクセスにそれぞれ8クロック掛かるので、発音チャンネルあたりでは「8+8」=「16クロック」掛かり、最大発音チャンネル数は、1536/「8+8」=96チャンネルとなる。このことから、ページアクセスで発音チャンネルあたりのアクセス時間を短縮することで、音源部8の発音チャンネル数を増加できることが理解できる。

また、各発音チャンネルのサンプル間補間に用いる波形サンプルは、サンプリング周期毎に、波形メモリ9から読み出すようになっているので、発音チャンネル毎のバッファメモリが不要であり、その分だけ音源部8の構成を簡単化することができる。

従って、この実施例にかかる音源部8によれば、簡単な構成で、波形メモリ9に対するアクセス速度を向上して、発音チャンネル数を増やすことができるという優れた効果を奏する。

MA=TA+SAi+Int[SAi/{p−(n−1)}]×(n−1)

=TA+SAi+Int[SAi/(p−n+1)]×(n−1)…(式2)

これにより、メモリアドレスMAを用いて波形メモリ9をページアクセスし、1度のアクセス毎に、メモリアドレスMAから(MA−n+1)までの連続するn個のアドレスから、n個の連続する波形サンプルを各発音チャンネル毎に読み出すことができる。この場合、音源部8は、波形サンプルをラッチするラッチをn個具備して、各サンプリング周期毎に、各発音チャンネル毎に読み出した該n個の波形サンプルを用いて、サンプルアドレス小数部SAfに基づくサンプル間補間を行い、当該発音チャンネルのサンプルアドレスSAに応じた補間済み波形サンプルを得て、更に、当該発音チャンネルの音量エンベロープパラメータに応じた音量の時間変化を付与することで、当該発音チャンネルの波形サンプルを形成する。そして、各サンプリング周期毎に、形成される複数の発音チャンネルの波形サンプルは累算され、複数発音チャンネル分の楽音信号としてDAC16に出力される。この場合、各発音チャンネルのページアクセスに掛かるクロック数は「8+3×(n−1)」である。例えば、nを4として場合は、「8+3×3」=「17クロック」となり、最大発音チャンネル数は、1536/17=90チャンネルである。対するに、ページアクセスを用いない場合の最大発音チャンネル数は、1536/「8×4」=48チャンネルであり、本発明では、それに比べて42チャンネルも増やせることになる。

また、上記実施例では、サンプルアドレスSAは、発音開始時に「0」リセットされるようになっていたが、「0」以外の値(−Toff)をセットして発音を始めるようにしてもよい。その場合、波形データの先頭アドレスTAは、「TA+Toff」になる。

また、上記実施例では、波形データの先頭アドレスTAを、何れかのページの先頭アドレスとしていたが、必ずしもページの先頭アドレスとしなくてもよい。

Claims (4)

- 波形メモリに記憶された波形データに基づいて、サンプリング周期毎に複数発音チャンネルの楽音信号を生成する楽音信号生成装置であって、

アドレス空間がページサイズpでページ分けされ、各ページ内のアドレスに記憶されたデータを高速ページアクセス可能な波形メモリであって、各アドレスに前記波形データを1サンプルずつ記憶しており、各ページの最終アドレスに記憶されたサンプルは、その次のページの先頭アドレスにも重複して記憶した波形メモリと、

各サンプリング周期毎に、各発音チャンネルの読み出しレートを累算して、整数部と小数部からなるサンプルアドレスを各発音チャンネル毎に生成するアドレスカウンタと、

各サンプリング周期毎に、前記アドレスカウンタで生成したサンプルアドレスの整数部を、各ページの最終アドレスに対応する値を飛び越すメモリアドレスに変換するメモリアドレス生成部と、

各サンプリング周期毎に、前記メモリアドレス生成部により生成された各発音チャンネルのメモリアドレスを用いて前記波形メモリをページアクセスし、前記メモリアドレスからの連続する2つのアドレスに記憶された2つのサンプルを読み出す読み出し部と、

各サンプリング周期毎に、前記読み出し部により読み出された各発音チャンネル毎の2個のサンプル間を、前記アドレスカウンタで生成した前記サンプルアドレスの小数部に基づいてサンプル間補間して、該補間されたサンプルを各発音チャンネル毎に生成する補間部と、

前記補間部により補間された各発音チャンネル毎のサンプルに基づいて、サンプリング周期毎に複数発音チャンネルの楽音信号を生成する楽音信号生成部と

を具えることを特徴とする楽音信号生成装置。 - 前記ページサイズの所定アドレス数をpとすると、

前記メモリアドレス生成部は、アドレスカウンタで生成したサンプルアドレスの整数部SAiと該整数部SAiの関数である[SAi/(p−1)]の整数部とを加算した結果に基づきメモリアドレスを生成するものであることを特徴とする請求項1に記載の楽音信号生成装置。 - 波形メモリに記憶された波形データに基づいて、サンプリング周期毎に複数発音チャンネルの楽音信号を生成する楽音信号生成装置であって、

アドレス空間がページサイズpでページ分けされ、各ページ内のアドレスに記憶されたデータを高速ページアクセス可能な波形メモリであって、各アドレスに前記波形データを1サンプルずつ記憶しており、各ページの最終からn−1個の各アドレスに記憶された波形データのサンプルは、その次のページの先頭からn−1個の各アドレスにも重複して記憶した波形メモリと、

各サンプリング周期毎に、各発音チャンネルの読み出しレートを累算して、整数部と小数部からなるサンプルアドレスを各発音チャンネル毎に生成するアドレスカウンタと、

各サンプリング周期毎に、前記アドレスカウンタで生成したサンプルアドレスの整数部を、各ページの最終からn−1個のアドレスに対応する値を飛び越すメモリアドレスに変換するメモリアドレス生成部と、

各サンプリング周期毎に、前記メモリアドレス生成部により生成された各発音チャンネルのメモリアドレスを用いて前記波形メモリをページアクセスし、前記メモリアドレスからの連続するn個のアドレスに記憶されたn個のサンプルを読み出す読み出し部と、

各サンプリング周期毎に、前記読み出し部により読み出された各発音チャンネル毎のn個のサンプル間を、前記アドレスカウンタで生成した前記サンプルアドレスの小数部に基づいてサンプル間補間して、該補間されたサンプルを各発音チャンネル毎に生成する補間部と、

前記補間部により補間された各発音チャンネル毎のサンプルに基づいて、サンプリング周期毎に複数発音チャンネルの楽音信号を生成する楽音信号生成部と

を具えることを特徴とする楽音信号生成装置。 - 前記ページサイズの所定アドレス数をpとすると、

前記メモリアドレス生成部は、アドレスカウンタで生成したサンプルアドレスの整数部SAiと、該整数部SAiの関数である[SAi/(p−n+1)]の整数部に(n−1)を乗算した値とを加算した結果に基づき、メモリアドレスを生成するものであることを特徴とする請求項3に記載の楽音信号生成装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008202926A JP5146188B2 (ja) | 2008-08-06 | 2008-08-06 | 楽音信号生成装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008202926A JP5146188B2 (ja) | 2008-08-06 | 2008-08-06 | 楽音信号生成装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010039266A true JP2010039266A (ja) | 2010-02-18 |

| JP5146188B2 JP5146188B2 (ja) | 2013-02-20 |

Family

ID=42011884

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008202926A Expired - Fee Related JP5146188B2 (ja) | 2008-08-06 | 2008-08-06 | 楽音信号生成装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5146188B2 (ja) |

-

2008

- 2008-08-06 JP JP2008202926A patent/JP5146188B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP5146188B2 (ja) | 2013-02-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5614420B2 (ja) | 楽音発生装置、電子楽器、プログラム及び楽音発生方法 | |

| JP4998046B2 (ja) | 楽音発生装置 | |

| US5625158A (en) | Musical tone generating apparatus | |

| JP2785531B2 (ja) | 電子楽器 | |

| US9040800B2 (en) | Musical tone signal generating apparatus | |

| JP5915420B2 (ja) | 楽音発生装置、楽音発生方法、電子楽器及びプログラム | |

| JP5146188B2 (ja) | 楽音信号生成装置 | |

| US6207885B1 (en) | System and method for rendition control | |

| JPH0563799B2 (ja) | ||

| JP2704722B2 (ja) | 電子楽器 | |

| JP2861007B2 (ja) | 電子楽器 | |

| US5817964A (en) | Electronic musical instrument and method for storing a plurality of waveform sampling data at a single address | |

| JP4236570B2 (ja) | 波形再生装置および波形再生プログラム | |

| JP3045130B2 (ja) | 電子楽器 | |

| JP5807419B2 (ja) | 信号処理装置 | |

| JP6531432B2 (ja) | プログラム、音源装置及び音響信号生成装置 | |

| JP2591160B2 (ja) | 波形選択合成装置 | |

| JP4254677B2 (ja) | 楽音発生装置および楽音発生処理のプログラム | |

| JP3561939B2 (ja) | 波形メモリ音源 | |

| JP3044712B2 (ja) | 電子楽器 | |

| JP3855710B2 (ja) | 音波形データ用ディジタル信号処理装置 | |

| JPH039476B2 (ja) | ||

| JP3858905B2 (ja) | メモリ使用音源装置 | |

| JP2991436B2 (ja) | 楽音信号発生装置 | |

| JP3095323B2 (ja) | 電子楽器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110607 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110620 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120919 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121030 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121112 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5146188 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151207 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |