以下、本発明に係る電子機器を実施するための最良の形態を図面を参照して詳細に説明する。

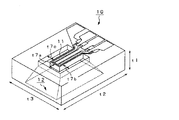

図1は、本発明を適用した角速度センサ50が備える振動型ジャイロセンサ素子10の外観斜視図であり、図2は、角速度センサ50の回路構成の一例を示した図である。なお、説明のため、図1に示す振動型ジャイロセンサ素子10は、一部を透過して示している。

図1に示すように、振動型ジャイロセンサ素子10は、いわゆる片持ち梁の振動子11を備えている。振動子11は、シリコン単結晶基板から切り出される厚みt1、長さt2、幅t3の素子から振動子11の周囲に周囲空間12を設けることで他端が固定された梁として形成される。振動子11は、長手方向と垂直な方向にt7b及びt7cの空間幅、長手方向にt7aの空間幅が確保される。なお、t7bと、t7cとは、同じ長さである。

このような振動子11は、長手方向に対して垂直な平面で切断したときの断面形状が直角四辺形となる四角柱状に形成されている。

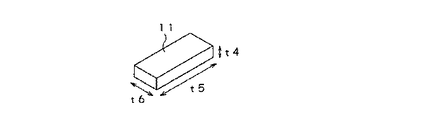

振動型ジャイロセンサ素子10の大きさは、例えば、上述したように素子の厚みをt1、素子の長さをt2、素子の幅をt3とすると、t1=300μm、t2=3mm、t3=1mmとすることができる。また、この時の振動子11の大きさは、図3に示すように振動子の厚みをt4、振動子の長さをt5、振動子の幅をt6とすると、例えば、t4=100μm、t5=2.5mm、t6=100μmとすることができる。

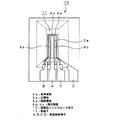

図4に、振動型ジャイロセンサ素子10の平面図を示す。図4に示すように、振動子11の上部には、基準電極4a、圧電体5aが順に積層され、さらに圧電体5a上に駆動電極6aと、駆動電極6aを挟む形で一対の検出電極6b,6cとが、振動子11の長手方向に沿って互いに平行に、且つ接触しないように形成されている。駆動電極6a,検出電極6b,6c、基準電極4aには、それぞれ配線接続端子A,B,C,Dが設けられている。

圧電体5aは、例えば、チタン酸ジルコン酸鉛(PZT)などの圧電セラミックスや、水晶、LaTaO3などの圧電単結晶などからなる薄膜である。

このような、振動型ジャイロセンサ素子10は、図2に示すIC回路40に接続されることで動作し、角速度に応じて発生するコリオリ力を検出する角速度センサ50として機能する。

IC回路40は、加算回路41と、増幅回路42と、移相回路43と、AGC(Automatic Gain Control)44と、差動増幅回路45と、同期検波回路46と、平滑回路47とを備えている。

振動型ジャイロセンサ素子10の1対の検出電極6b,6cは、それぞれ配線接続端子B,Cを介して、加算回路41と、差動増幅回路45に接続される。また、振動型ジャイロセンサ素子10の駆動電極6aは、配線接続端子Aを介して、AGC44の出力端と接続される。

角速度センサ50では、加算回路41、増幅回路42、移相回路43、AGC44及び振動型ジャイロセンサ素子10によっていわゆる移相発振回路が構成されており、この移相発振回路によって振動型ジャイロセンサ素子10の基準電極4a、駆動電極6a間に電圧が印加され振動子11を自励振動させる。振動子11の振動方向は、当該振動子11の厚み方向となる。

また、角速度センサ50では、1対の検出電極6b,6cが配線接続端子B,Cを介して接続された加算回路41、差動増幅回路45の出力端が、同期検波回路46に接続され、この同期検波回路46が平滑回路47に接続されており、これらと、圧電体5aとで、振動子11の角速度を検出する検出部として機能する。

すなわち、図2に示す角速度センサ50では、振動型ジャイロセンサ素子10の振動子11を上述した移相発振回路で自励振動させている際に、振動子11の長手方向に角速度が加えられることで振動方向に垂直な方向に発生するコリオリ力を、圧電体5aで検出し、検出電極6b,6cから互いに逆極性の信号として出力し、差動増幅回路45に入力する。差動増幅回路45にて増幅された出力は、同期検波回路46に入力され、同期検波が行われる。このとき、同期検波回路46には、同期検波を行うために、加算器41からの出力が同期信号として供給される。そして、同期検波回路46からの出力が、平滑回路47を介して、振動子11に生じたコリオリ力を検出することにより得られた直流信号である角速度信号として出力される。

以上のように、角速度センサ50では、圧電体5aを用いて振動子11を振動させるとともに、振動子11に生じるコリオリ力を圧電体5aによって検出し、この圧電体5aによって検出されたコリオリ力に基づいて角速度を検出することができる。

<実施例>

続いて、実施例として、上述した振動型ジャイロセンサ素子10を実際に作製し、その製造方法について説明をする。

上述したように、図1に示した振動型ジャイロセンサ素子10は、単結晶シリコン基板を加工することで形成される。

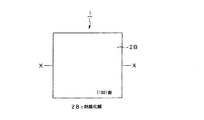

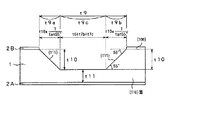

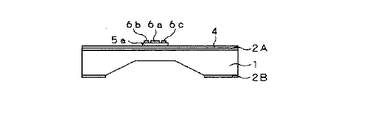

図5は、振動型ジャイロセンサ素子10を形成する際に用いる単結晶シリコン基板1の平面図であり、図6は、図5に示す単結晶シリコン基板1をXX線で切断した断面図である。上記単結晶シリコン基板1の一方主面1B、他方主面1Aは、熱酸化されて、後述する結晶異方性エッチング時の保護膜とするSiO2膜が形成されている。

振動型ジャイロセンサ素子10で使用する単結晶シリコン基板1は、図5に示すように、当該単結晶シリコン基板1の一方主面1Bの面方位が{100}、図6に示すように側面1Cの面方位が{110}となるように切り出されている。なお、他方主面1Aは一方主面1Bと平行であるため、他方主面1Aの面方位も{100}となっている。

但し、“{ }”は、方向が異なる等価な面方位を総称して表すための記号であり、例えば、{100}は、(100),(010),(001)などを総称しているものとする。

このように結晶面方位を規定して切り出される単結晶シリコン基板1の大きさは、加工プロセスのラインに設けられた装置に応じて任意に設定される。例えば、本実施例では、縦×横が3cm×3cm角の単結晶シリコン基板1を用いている。

また、単結晶シリコン基板1の厚みは、作業性や、当該基板の値段により決定されるが、少なくとも振動型ジャイロセンサ素子10に形成する振動子11の厚み以上であればよい。例えば、本実施例では、図3を用いて示したように振動子11の厚みt4を100μmとしているので、単結晶シリコン基板1の厚みを3倍の300μmとしている。

図6に示すように、単結晶シリコン基板1の他方主面1A及び一方主面1Bには、熱酸化することでSiO2膜である熱酸化膜2A,2Bを形成する。この熱酸化膜2A,2Bは、後述する結晶異方性エッチングを行う際の保護膜として機能する。熱酸化膜2A,2Bの厚みは、任意であるが、本実施例では、0.1μmとしている。また、本実施例で用いる、単結晶シリコン基板1は、伝導型としてN型を採用しているが、任意に決めることができる。

なお、以下の説明において、単結晶シリコン基板1において、熱酸化膜2Aが形成された他方主面1A側を表面とし、熱酸化膜2Bが形成された一方主面1B側を裏面とする。

このような単結晶シリコン基板1を用いて、まず、当該単結晶シリコン基板1の裏面において、結晶異方性エッチングを行う個所に形成されている熱酸化膜2Bをフォトエッチングにより除去する。

フォトエッチングは、熱酸化膜2B上に、上記除去する個所が開口したレジスト膜パターンを形成する工程(フォトリソグラフィー)と、上記パターンを用いて熱酸化膜2Bを除去する工程(エッチング)とに大別される。

図7は、単結晶シリコン基板1の熱酸化膜2B上にレジスト膜パターン3が形成された様子を示した平面図であり、図8は、図7で示す単結晶シリコン基板1をXX線で切断した際の断面図である。

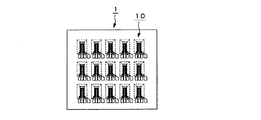

図7に示すように、熱酸化膜2B上に形成されたレジスト膜パターン3は、{110}面と垂直な方向の長さをt8とし、{110}面と平行な方向の長さをt9とするt8×t9のサイズ長方形状をした開口部3aが所定の間隔を持って規則的に配列されたパターンとなっている。本実施例では、3×5個の開口部3aが形成されたパターンとしている。開口部3aの、それぞれが1つの振動型ジャイロセンサ素子10となる。

このレジスト膜パターン3は、半導体加工プロセスで利用されているフォトリソグラフィーと全く同様にして、熱酸化膜2B上をマイクロ波で加熱して水分を除去するプレベーキングを行ってから、感光性樹脂であるフォトレジスト膜を塗布し、上記開口部3aを形成するための上記パターンが形成されたマスクをフォトレジスト膜に露光し、現像をするという工程を経ることで形成される。

開口部3aの大きさを決めるt8、t9は、振動型ジャイロセンサ素子10の振動子11の形状と、単結晶シリコン基板10の厚みt1、図1で示した振動子の空間幅t7a,t7b,t7cによって決定される。なお、t8,t9の具体的な数値については、後で詳細に説明をする。

このようにして、図8に示すように、単結晶シリコン基板1の熱酸化膜2B上には、レジスト膜パターン3が形成されることになる。

続いて、レジスト膜パターン3によって形成された開口部3aの熱酸化膜2Bをエッチングにより除去する。図9は、レジスト膜パターン3によって形成された開口部3aの個所の熱酸化膜2Bのみが除去された単結晶シリコン基板1の様子を示した平面図であり、図10は、図9で示す単結晶シリコン基板1をXX線で切断した際の断面図である。

熱酸化膜2Bの除去する場合のエッチングは、イオンエッチング等の物理的エッチングでもよいし、湿式エッチングでもよいが、単結晶シリコン基板1の界面の平滑性を考慮すると熱酸化膜2Bのみが除去される湿式エッチングが好適である。

本実施例では、湿式エッチングの薬液としてフッ化アンモニウムを用いた。ただし、湿式エッチングの場合、長時間エッチングを行うと開口部分の側面からエッチングが進行する、いわゆるサイドエッチングが大きくなるため、熱酸化膜2Bの開口部分3aのみが除去された時点で終了するようエッチング時間を正確に制御する。

このようにして、レジスト膜パターン3の開口部3aに位置する熱酸化膜2Bは、図10に示すように除去される。

続いて、上述したエッチングにより、熱酸化膜2Bが除去されることで、レジスト膜パターン3の開口部3aと同じ大きさのt8×t9の開口部2Baで{100}面が露出した単結晶シリコン基板1に対して、湿式エッチングを施し、単結晶シリコン基板1の厚みを振動子11の厚みであるt4まで削り取る。

図11は、単結晶シリコン基板1において、熱酸化膜2Bが除去され、{100}面が露出したt8×t9の大きさの開口部2Baのみがエッチングされた様子を示した平面図であり、図12は、図11で示す単結晶シリコン基板1をXX線で切断した際の断面図である。また、図13は、図12に示す領域Aを拡大して示した図である。

ここで、単結晶シリコン基板1に対して施される湿式エッチングは、結晶方向にエッチング速度が依存する性質を利用した結晶異方性エッチングである。熱酸化膜2Bが除去され、{100}面が露出した上記開口部2Baに対して、結晶異方性エッチングをすると、図13に示すように{100}面に対して約55度の角度の面方位となる{111}面が現れ、振動子11の厚みであるt4分を確保するようにエッチングを終了することで、いわゆるダイヤフラム形状となる。

一般に、単結晶シリコンは、その結晶構造から、{111}面が、{100}面に較べ、非常にエッチングされにくいという結晶方向に対するエッチング速度依存性がある。具体的には、単結晶シリコンの{100}面のエッチング速度は、{111}面のエッチング速度の200倍程度となっている。

単結晶シリコンに対して結晶異方性エッチングを施す際に使用可能なエッチング液は、TMAH(水酸化テトラメチルアンモニウム)、KOH(水酸化カリウム)、EDP(エチレンジアミン-ピロカテコール-水)、ヒトラジンなどである。

本実施例では、エッチング液として熱酸化膜2Aと、熱酸化膜2Bとのエッチングレートの選択比がより大きくなるTMAH(水酸化テトラメチルアンモニウム)20%溶液を使用した。エッチング時には、エッチング液を攪拌しながら温度を80℃に保ち、6時間かけてダイヤフラムの深さt10が200μm、つまりエッチングすることで残る単結晶シリコン基板1の厚みt11が、振動子11の厚みt4と同じ、100μmとなるまでエッチングした。

ここで、結晶異方性エッチングを施すために、図7を用いて説明したレジスト膜パターン3によって形成した開口部3aのサイズを規定するt8、t9の数値について具体的に説明をする。

開口部3aの幅t9、つまりエッチング後のダイヤフラムの幅は、図13に示すようにt9=t9a+t9b+t9cとなっている。

t9cは、図3で示した振動子11の幅t6と、図1で示した振動子11の周辺に形成する周囲空間12の空間幅t7b、t7cを用いて、t9c=t6+t7b+t7cと表すことができる。

また、t9a,t9bは、それぞれ同じ長さであり、図13に示すように、結晶異方性エッチングを施した際に現れる{111}面と、単結晶シリコン基板1の裏面である{100}面とが55度の角度をなしていることから、ダイヤフラムの深さt10を用いてt9a=t9b=t10×1/tan55°と表すことができる。

したがって、開口部3aの幅t9は、t9={t10×1/tan55°}×2+(t6+t7b+t7c)となる。ここで、t6=100μm、t7b=t7c=200μm、t10=200μmとすると、t9=780μmとなる。

上述したような結晶性異方エッチングを行うと、レジスト膜パターン3の開口部3aにおけるt8方向にもt9方向と同様に、{100}面と55度の角度をなす{111}面が現れる。したがって、開口部の長さt8、つまりエッチング後のダイヤフラムの長さは、図3で示した振動子11の長さt5、図1で示した振動子11の周辺に形成する周囲空間12の空間幅t7aを用いて、t8={t10×1/tan55°}×2+(t5+t7a)となる。ここで、t5=2.5mm、t7a=200μm、t10=200μmとすると、t8=2980μmとなる。

上述までの説明では、単結晶シリコン基板1全体を図示しながら説明をしたが、説明の都合上、以下の説明においては、図11に領域Wとして示すダイヤフラムが形成された単結晶シリコン基板1のみを用いて説明をする。また、以下の説明では、熱酸化膜2A側に対する加工工程となるため、表面である熱酸化膜2A側を上面にした平面図、及びこの平面図を所定の位置で切断した断面図を用いて説明をする。

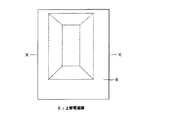

具体的には、図11に示す領域Wのダイヤフラムが形成された単結晶シリコン基板1を、熱酸化膜2Aを上面とすると、図14のような平面図となり、XX線で切断される断面図は、図15のようになる。

続いて、熱酸化膜2A上に、図1で示した基準電極4a、圧電体5a、駆動電極6a、検出電極6b,6cを形成するために下部電極膜、圧電膜、上部電極膜を成膜する。単結晶シリコン基板1の熱酸化膜2A上に、下部電極膜4、圧電膜5、上部電極膜6を順に成膜すると、その平面図は図16のようになり、図16に示すXX線で切断した断面図は図17に示すようになる。

本実施例では、下部電極膜4、圧電膜5、上部電極膜6を、全て、マグネトロンスパッタ装置を用いて成膜した。

まず、熱酸化膜2A上に、下部電極膜4を成膜する。本実施例では、まず、マグネトロンスパッタ装置の条件を、ガス圧:0.5Pa、RFパワー:1kWとして、熱酸化膜2A上にチタン(Ti)を膜厚が50nmとなるように成膜した。続いて、成膜したチタン(Ti)の上に、装置の条件をガス圧:0.5Pa、RFパワー:0.5kWとして、プラチナ(Pt)を膜厚が200nmとなるように成膜した。つまり、チタンと、プラチナとを上記膜厚となるように成膜して下部電極膜4を形成している。

次に、下部電極膜4上に圧電膜5を成膜する。本実施例では、まず、Pb(1+x)(Zr0.53Ti0.47)O3−y酸化物をターゲットとして用い、マグネトロンスパッタ装置の条件を、常温、ガス圧:0.7Pa、RFパワー:0.5kWとして、下層電極4として成膜されたプラチナ(Pt)上にチタン酸ジルコン酸鉛(PZT)の圧電体薄膜を膜厚が1μmとなるように成膜した。続いて、チタン酸ジルコン酸鉛(PZT)を成膜した単結晶シリコン基板1を電気炉に入れ、酸素雰囲気下、700℃、10分間という条件で結晶化熱処理を行うことで圧電膜5を形成した。

最後に、圧電膜5上に上部電極膜6を成膜する。本実施例では、マグネトロンスパッタ装置の条件を、ガス圧0.5Pa、RFパワー:0.5kWとして、圧電膜5上にプラチナ(Pt)を膜圧が200nmとなるように成膜した。

次に、上部電極膜6を加工して駆動電極6a、検出電極6b,6cを形成する。図18は、駆動電極6a、検出電極6b,6cが形成された単結晶シリコン基板1の様子を示した平面図であり、図19は、図18で示す単結晶シリコン基板1をXX線で切断した際の断面図である。

駆動電極6aは、上述したように振動子11を駆動するための電圧を印加する電極であり、振動子11の中心となるように形成される。また、検出電極6b,6cは、上述したように振動子11に発生したコリオリ力を検出するための電極であり、駆動電極6aを挟むように駆動電極6aと平行に、且つ接触しないように、振動子11に形成される。

また、図18に示すように、駆動電極6a,検出電極6b,6cは、その一方端部が、振動子11の根元である根元ラインRと一致するように形成され、各電極の上記一方端部には、それぞれ端子接合部6a1,6b1,6c1が形成される。

本実施例では、駆動電極6aの幅t13を50μm、検出電極6b,6cの幅t14を10μm、駆動電極6a及び検出電極6b,6cの長さt12を2mm、検出電極6b,6cの駆動電極6aとの間隔t15をそれぞれ5μmとした。この駆動電極6a、検出電極6b,6cは、振動子11上に形成される範囲であれば、任意の大きさに設計することができる。また、本実施例では、端子接合部6a1,6b1,6c1のそれぞれの長さt16を50μm、幅t17を50μmとした。

本実施例では、駆動電極6a、検出電極6b,6c及び端子接合部6a1,6b1,6c1を、フォトリソグラフィー技術を用いて、上部電極膜6上にレジスト膜パターンを形成した後、イオンエッチングにより不要な部分の電極膜6を除去することで形成した。

本発明は、この駆動電極6a、検出電極6b,6c及び端子接合部6a1,6b1,6c1を形成する際の手法に限定されるものではなく、上述した手法以外にも様々な手法を適用することができる。

次に、圧電膜5を加工して振動子11上に圧電体5aを形成する。図20は、圧電膜5を加工して圧電体5aが形成された単結晶シリコン基板1の様子を示した平面図であり、図21は、図20で示す単結晶シリコン基板1をXX線で切断した際の断面図である。

圧電体5aは、上部電極膜6を加工して形成した駆動電極6a,検出電極6b,6cを完全に覆うような形状であればどのような形状であってもかまわない。

本実施例では、圧電体5aの長さt18を2.2mm、幅t19を90μmとした。このような大きさの圧電体5aは、その中心が振動子11の中心と一致し、一方端部が、振動子11の根元である根元ラインRと一致させるようにする。

圧電体5aの幅t18は、振動子11の幅t4以下の幅である必要がある。また、本実施例では、上述した端子接合部6a1,6b1、6c1の下に圧電膜5を、端子接合部6a1,6b1、6c1の各外周より5μmの幅を持たせて残してある。この端子接合部6a1,6b1、6c1の下に残される圧電膜5は、振動型ジャイロセンサ素子10全体の形状サイズにより任意に設定されることになる。

本実施例では、フォトリソグラフィー技術を用いて、圧電体5a及び端子接合部6a1,6b1、6c1の下に残す圧電膜5の形状のレジスト膜パターンを形成した後、フッ硝酸溶液による湿式エッチングにより不要な部分の圧電膜5を除去することで、圧電体5aを形成した。

上述したように、本実施例では、圧電体5aを形成するために圧電膜5の不要部分を除去する手法を湿式エッチングとしているが、本発明にはこれに限定されるものではなく、物理的なエッチングであるイオンエッチングによる除去方法や、化学的な作用と物理的な作用でエッチングする反応性イオンエッチング(RIE:Reactive Ion Etching)による除去方法などを適用することができる。

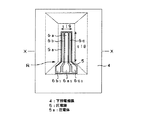

次に、下部電極膜4を加工して、振動子11上に基準電極4aを形成する。図22は、下部電極膜4を加工して基準電極4aが形成された単結晶シリコン基板1の様子を示した平面図であり、図23は、図22で示す単結晶シリコン基板1をXX線で切断した際の断面図である。

基準電極4aは、圧電膜5を加工して形成した圧電体5aを完全に覆うような形状であればどのような形状であってもかまわない。

本実施例では、基準電極4aの長さt20を2.3mmとし、幅t21を94μmとした。このような基準電極4aは、その中心が振動子11の中心と一致し、一方端部を、振動子11の根元である根元ラインRと一致させるようにする。

基準電極4aの幅t20は、振動子11の幅t4以下の幅である必要がある。また、本実施例では、上述したように除去しなかった圧電膜5の下の下部電極膜4を、上記圧電膜5の外周より5μmの幅を持たせて残してある。この幅に関しては振動型ジャイロセンサ素子10全体の形状サイズにより任意に設定されることになる。

また、基準電極4aと、外部との電気的接合を図るため、図22に示すように下部電極膜4によって配線接続端子Dが形成されている。上述したように、圧電膜5の下に残された下部電極膜4を介して基準電極4aと、配線接続端子Dとは、電気的に接続されている。

本実施例では、振動型ジャイロセンサ素子10と、外部との電気的な接続は、ワイヤーボンディングにより行うことを前提としているため、配線接続端子Dの実際に配線される端子部をワイヤーボンディング時に必要となる面積分だけ確保する。

本実施例では、配線接続端子Dの端子部の長さt22を200μm、幅t23を100μmとした。振動型ジャイロセンサ素子10の外部との接合に関しては、接合方法も含めて任意であり、採用する接合方法に応じて、配線接続端子Dの形状を最適となるように設定する。

本実施例では、フォトリソグラフィー技術を用いて、図22に示すような形状となるレジスト膜パターンを形成した後、イオンエッチングにより不要な部分の下部電極膜4を除去することで基準電極4a、配線接続端子D、基準電極4aと配線接続端子Dとを電気的に接続する下部電極膜4を形成した。

上述したように、本実施例では、基準電極4aを形成するために下部電極膜4の不要部分を除去する手法を、物理的なエッチングであるイオンエッチングとしているが、本発明はこれに限定されるものではなく、化学的なエッチングである湿式エッチングや、化学的な作用と物理的な作用でエッチングする反応性イオンエッチング(RIE:Reactive Ion Etching)による除去方法を適用することができる。

次に、駆動電極6a、検出電極6b,6cの一方端部側にそれぞれ形成されている端子接合部6a1,6b1、6c1と、配線接続端子A,B,Cとの電気的接合を円滑にするために平坦化レジスト膜7を形成する。

図24は、平坦化レジスト膜7が形成された単結晶シリコン基板1の様子を示した平面図であり、図25は、図24に示す単結晶シリコン基板1をYY線で切断した際の断面図である。

上述した図22に示すように、配線接続端子A,B,Cと、端子接合部6a1,6b1、6c1とをそれぞれ物理的に接合する際には、圧電体5aを形成する際に残された圧電膜5の端部と、基準電極4aを形成する際に残された下部電極膜4の端部とをそれぞれ通過しなくてはならない。

本実施例において、圧電体5aは、圧電膜5を湿式エッチングによってエッチングすることで形成されており、エッチングされた端部は、単結晶シリコン基板1方向へ、逆テーパ形状、あるいは、垂直形状となっている。そのため、平坦化レジスト膜7を形成せずに、端子接合部6a1,6b1、6c1と、配線接続端子A,B,Cとをそれぞれ電気的に接続するように配線膜を形成すると、上記端部の段差により電気的接続が断たれてしまう虞がある。

また、基準電極4aと電気的に接続されている下部電極膜4の端部が露出しているため、平坦化レジスト膜7を形成しないと、駆動電極6a,検出電極6b,6cと、基準電極4aとが短絡してしまうことになる。

以上の理由により、図24に示すように、端子接合部6a1,6b1、6c1上に、平坦化レジスト膜7を形成し、上記圧電膜5の端部の段差をなくし、上記下部電極膜4の端部が露出しないようにする。

平坦化レジスト膜7の形状は、上述したように上記圧電膜5の端部の段差をなくし、上記下部電極膜4の端部が露出しない形状であれば任意に設定できる。本実施例では、平坦化レジスト膜7の幅t24を200μm、長さt25を50μmとした。

平坦化レジスト膜7は、フォトリソグラフィー技術により、図24に示す個所に所望の形状でパターニングしたレジスト膜を、280〜300℃程度の熱処理を加えることで硬化させる。本実施例では、レジスト膜の厚みを2μm程度としたが、この厚みに関しては、圧電膜5、下部電極膜4の厚みに応じて変化させ、両者の合計の厚み以上とすることが望ましい。本実施例では、レジスト膜を用いて平坦化レジスト膜7を形成しているが、上記理由を回避することの可能な、非導電性の材料であれば、その形成方法も含めて任意である。

次に、駆動電極6a、検出電極6b,6cを外部に接続するための配線処理を施す際に用いる配線接続端子A,B,Cを形成する。図26は、配線接続端子A,B,Cを形成した単結晶シリコン基板1の様子を示す平面図であり、図27は、図26に示した単結晶シリコン基板1をYY線で切断した際の断面図である。

図26に示す配線接続端子A,B,Cは、駆動電極6a、検出電極6b,6cの端子接合部6a1,6b1、6c1とそれぞれ接続されている。本実施例では、振動型ジャイロセンサ素子10と、外部との電気的な接続は、ワイヤーボンディングにより行うことを前提としているため、配線接続端子A,B,Cの実際に配線される端子部を、上述した配線接続端子Dと同様に、ワイヤーボンディング時に必要となる面積分だけ確保する。

各配線接続端子A,B,Cは、平坦化レジスト膜7の上面を通り、端子接合部6a1,6b1、6c1とそれぞれ接触するように、熱酸化膜2A上に形成される。配線接続端子A,B,Cと、端子接続部6a1,6b1、6c1との接合個所である各電極接合部の形状は、任意であるが電気的な接触抵抗を減少させるために5μm四方以上の大きさが望ましい。

配線接続端子A,B,Cにおいて、実際に配線が接続される端子部は、上述したようにワイヤーボンディング接合を行うのに必要な面積分を確保可能な形状となる。

本実施例では、配線接続端子A,B,C、それぞれの端子部の長さt26を200μm、幅t27を100μmとした。振動型ジャイロセンサ素子10の外部との接合に関しては、接合方法も含めて任意であり、採用する接合方法に応じて、配線接続端子A,B,Cの形状を最適となるように設定する。

本実施例では、フォトリソグラフィー技術を用いて、図26に示すような形状となるレジスト膜パターンを形成した後、配線接続端子A,B,Cをスパッタリングにより形成した。スパッタリングした際に、不要な部分に付着した膜は、レジスト膜パターンを除去する際に、同時に除去する、いわゆるリフトオフの手法にて除去した。

具体的には、配線接続端子A,B,Cは、付着力を向上させるためのチタン(Ti)を20nmだけ堆積させ、電気抵抗が低く、低コストである銅(Cu)を300nm堆積させ、さらに、ワイヤーボンディングとの接合を容易にするため、金(Au)を300nm堆積させることで形成した。なお、この配線接続端子A,B,Cを形成する際に用いる材料及び配線接続端子A,B,Cの形成方法は任意であり、本発明は、上記材料及び形成方法に限定されるものではない。

続いての工程は、図1で示したように振動型ジャイロセンサ10に対して周囲空間12を形成することで片持ち梁の振動子11を作製する工程である。図28は、単結晶シリコン基板1に周囲空間12を形成することで片持ち梁の振動子11が形成された様子を示した平面図であり、図29は、図28で示す単結晶シリコン基板1をYY線で切断した様子を示した断面図であり、図30は、図28で示す単結晶シリコン基板1をXX線で切断した様子を示した断面図である。

図28に示すように周囲空間12は、検出電極6b,6cが形成されている側の振動子11の側面から左右の方向にそれぞれt7b及びt7cの幅を有する空間と、振動子11の長手方向で振動子11の根元ラインRと反対の端部側にt7aの幅を有する空間とによって構成された、いわゆる“コ”の字型の形状をした空間となっている。

本実施例では、t7b、t7cを、それぞれ200μmとしている。このt7b、t7cは、周囲空間12内の気体の状態や、要求される振動子11の振動の質を示すQ値などによって決定されることになる。

本実施例では、まず、フォトリソグラフィー技術を用いて、図28に示すような“コ”の字型の形状のレジスト膜パターンを熱酸化膜2A上に形成した後、熱酸化膜2Aをイオンエッチングで除去する。熱酸化膜2Aを除去するには、湿式エッチングでも可能であるが、サイドエッチングが発生することによる寸法誤差を考慮するとイオンエッチングが好適である。

続いて、熱酸化膜2Aが除去された“コ”の字型の単結晶シリコン基板1を、反応性イオンエッチング(RIE:Reactive Ion Etching)にてエッチングして貫通させることで周囲空間12を形成する。

本実施例では、誘導結合型プラズマ(ICP:Inductively Coupled Plasma)を備えたエッチング装置を用いて、エッチング工程と、エッチングした個所に側壁保護のための側壁保護膜を成膜する工程とを繰り返すBoschプロセス(Bosch社)にて、垂直な側壁面を有する振動子11を形成した。

このBoschプロセスを用いることで、ICPにより高密度なプラズマを生成し、エッチングのためのSF6と、側壁保護のためのC4F8のガスを交互に導入することで、毎分10μm程の速度でエッチングしながら、垂直な側壁面を有する振動子11を形成することができる。

以上のプロセスにより、振動型ジャイロセンサ素子10の形成に関する、圧電素子形成、形状形成、配線形成の主要工程が終了し、例えば、図31に示すように、単結晶シリコン基板1内に、振動型ジャイロセンサ素子10が複数個、ここでは、5×3個、形成されることになる。

1枚の単結晶シリコン基板1内に形成される振動型ジャイロセンサ素子10の数は、図31に示すように5×3個に限らず、設計する振動型ジャイロセンサ素子10の大きさ、及び形成する際のそれぞれのピッチにより決定されることになる。

次の工程では、このように単結晶シリコン基板1に形成された複数の振動型ジャイロセンサ素子10を、切断し単一の素子とする。単結晶シリコン基板1から、振動型ジャイロセンサ素子10を分断する際の手法や、寸法は、特に決められたものではなく、分断後の形状も任意である。

本実施例においては、図32に示す素子分断線20をなぞるように、ダイヤモンドカッターで分断傷を付けた後、手で直接、単結晶シリコン基板1を折り、振動型ジャイロセンサ素子10を取り出した。なお、単結晶シリコン基板1を分断する手法も任意の手法が適用可能であり、例えば、砥石による研削や単結晶シリコン基板1の面方位を利用して切断する手法などでもよい。

続いて、図33に示すように、個々に分断した振動型ジャイロセンサ素子10を、IC基板21に貼り付ける。振動型ジャイロセンサ素子10と、IC基板21との貼り付け手法は任意であるが、本実施例では、嫌気性接着剤を用いて貼り付けた。

IC基板21に、振動型ジャイロセンサ素子10を貼り付けた後、電気的な接続を行う。IC基板21上には、冒頭の図2を用いて説明したIC回路40が搭載されている。また、IC基板21には、図2で示したAGC44の端部と接続された基板端子22a、同期検波回路45に接続された基板端子22b,22c、図示しない基準電極と接続された基板端子22dが形成されている。

本実施例では、振動型ジャイロセンサ素子10の配線接続端子A,B,C,Dと、IC基板21内の基板端子22a,22b,22c,22dとをそれぞれワイヤーボンディングによる結線方法を用いて電気的接続を行った。この結線方法に関しても任意であり、半導体で用いられる導電性バンプを形成する手法も利用可能である。

次に、図34に示すように、振動型ジャイロセンサ素子10及びIC基板21上の回路と、外部との接触をなくすためカバー材30を取り付け、保護をする。カバー材30の材料は、任意であるが外部のノイズの影響を考慮してSUSなど、シールド効果のあるものが望ましい。また、カバー材30は、振動子11の振動を妨げない形状とする必要がある。このようにして、角速度センサ50が形成されることになる。

このように角速度センサ50を構成する振動型ジャイロセンサ素子10が備える振動子11の駆動電極6aに、電圧を印加して所定の共振周波数で振動させた場合、振動子11は、振動子11の厚み方向である縦方向に縦共振周波数で共振すると共に、振動子11の幅方向である横方向に横共振周波数で共振することになる。

上述したように振動型ジャイロセンサ素子10は、振動子11の保護や、外部装置への組み込み時の取り扱いを容易にするため、図34に示すように、IC基板21上に貼り付けられ、カバー材30で覆われて、パッケージングされることになる。このとき、カバー材30は、振動子11の振動を妨げない形状とするのが前提となっている。

具体的には、振動子11が、縦共振周波数で自励振動している際のQ値を測定したときに、所望のQ値が得られるように、当該振動子11の周囲に適切な空間領域を確保する必要がある。このように、振動子11の周囲空間に適切な空間領域が確保されれば、振動子11の振動が妨げられず、且つ、安定した振動状態となるため、振動型ジャイロセンサ素子10は、パッケージングが施されたとしても高い感度を維持することができる。

続いて、図35,36を用いて、振動子11の周囲の空間について説明をする。図35は、図28に示す振動型ジャイロセンサ素子10をXX線で切断した際の、振動子11のみを示した断面図であり、図36は、図28に示す振動型ジャイロセンサ素子10の振動子11のみを示した平面図である。

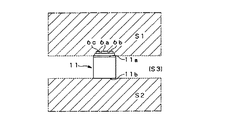

振動型ジャイロセンサ素子10が備える振動子11のように片持ち梁形状の振動子の場合、その周囲空間は、図35に示すような駆動電極6a,検出電極6b,6cが形成された振動子11の上面11aを含む平面上に広がる空間である第1の空間S1と、上面11aと対向する面である下面11bを含む平面上に広がる空間である第2の空間S2と、図36に示すように、反応性イオンエッチング(RIE:Reactive Ion Etching)によって形成された、振動子11の側壁面である側壁面11c,11d,11eをそれぞれ含む各平面上に広がる空間からなる第3の空間S3とに大別される。

この振動子11の周囲空間である第1の空間S1、第2の空間S2、第3の空間S3は、上述したように、振動子11を備える振動型ジャイロセンサ10が、例えば、IC基板21上に貼り付けられ、カバー材30で覆われてパッケージングされるため、その空間サイズに制限が設けられることになる。

図37,38に、図34に示す振動型ジャイロセンサ素子10をXX線で切断した断面図を示す。図37は、振動子11の基準電極4a、駆動電極6a間に電圧を印加して振動子11を自励振動させた際に、振動子11が、上面11a方向に最大変位量dmaxだけ振れた様子を示した断面図であり、図38は、同じく振動子11を自励振動させた際に、振動子11が、下面11b方向に最大変位量dmaxだけ振れた様子を示した断面図である。なお、図37,38において、一点鎖線で示した個所は、振動子11が振動していない状態、もしくは、振動している振動子11の変位量がゼロであるときの状態を示している。

図37に示す振動型ジャイロセンサ素子10において、第1の空間S1は、カバー材30の内壁面30aと、振動子11が振動していない状態での上面11aとの間隔である上部空間幅t7dで空間サイズが規定される。また、図38に示すように、第2の空間S2は、振動型ジャイロセンサ素子10を貼り付けるIC基板21の基板表面21aと、振動子11が振動していない状態での下面11bとの間隔である下部空間幅t7eで空間サイズが規定される。さらに、第3の空間S3は、図39に示すように、上述した反応性エッチングによって形成される周囲空間12、具体的には、空間幅t7a,t7b,t7cによって空間サイズが規定されることになる。

続いて、図34に示すようにIC基板21上に貼り付け、カバー材30で覆うことでパッケージングした振動型ジャイロセンサ素子10の第1の空間S1、第2の空間S2、第3の空間S3をそれぞれ変化させ、機械的品質係数(Mechanical quality factor)であるQ値を測定し、この測定結果から最適な空間サイズを規定する。

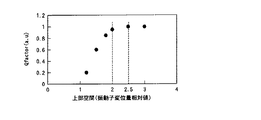

まず、図40に、第1の空間S1を変化させた場合の振動型ジャイロセンサ素子10のQ値を示す。第1の空間S1は、上述したように、図37で示した上部空間幅t7dで規定される。

図40に示す測定結果は、上部空間幅t7dを0から適当な間隔で増加させることで第1の空間S1を変化させ、そのときのQ値を示している。

図40の横軸では、上部空間幅t7dを、振動子11を自励振動させた際の最大変位量dmaxを1としたときの相対値で示している。また、図40の縦軸では、上述したようにパッケージングされ、第1の空間S1を変化させた振動型ジャイロセンサ素子10のQ値を、何のパッケージングもされておらず、振動子11の周囲空間が開放された状態の振動型ジャイロセンサ素子10のQ値を1としたときの相対値で示している。

図40に示すように、横軸に示した相対値がおよそ2、つまり、上部空間幅t7dが、振動子11の最大変位量dmaxの2倍程度となっているとき、Q値が1近傍をとっている。また横軸の相対値がおよそ2.5のとき、つまり、上部空間幅t7dが、振動子11の最大変位量dmaxの2.5倍以上となっているとき、Q値が1に飽和している。

この図40に示す測定結果は、第1の空間S1を規定する上部空間幅t7dが、振動子11を自励振動させた際の最大変位量dmaxの2倍以上となるようにカバー材30を取り付けた場合に、振動子11の共振特性の劣化を大幅に抑制することができることを示している。さらに、図40に示す測定結果は、上部空間幅t7dが、最大変位量dmaxの2.5倍以上となるようにカバー材30を取り付けた場合に、振動子11の共振特性を最適にすることができることを示している。

また、第2の空間S2に関しては測定結果を示さないが、Q値の測定結果は、図40に示す測定結果と同程度となる。したがって、上述した第1の空間S1と同様に、第2の空間S2を規定する図38で示した下部空間幅t7eが、振動子11を自励振動させた際の最大変位量dmaxの2倍以上となるようにIC基板21に貼り付けた場合に、振動子11の共振特性の劣化を大幅に抑制することができる。また、下部空間幅t7eが、最大変位量dmaxの2.5倍以上となるようにIC基板21に貼り付けた場合に、振動子11の共振特性を最適にすることができる。

続いて、図41に、第3の空間S3を変化させた場合の振動型ジャイロセンサ素子10のQ値を示す。第3の空間S3は、上述したように、図39で示した空間幅t7a,t7b,t7cで規定される。

図41に示す測定結果は、空間幅t7a,t7b,t7cを0から適当な間隔で増加させることで第3の空間S3を変化させ、そのときのQ値を示している。なお、ここでは、空間幅t7a,t7b,t7cは、全て同じ値にしている。

図41の横軸では、空間幅t7a,t7b,t7cを、振動子11の幅t6を1としたときの相対値で示している。また、図41の縦軸では、上述したようにパッケージングされ、第3の空間S3を変化させた振動型ジャイロセンサ素子10のQ値を、何のパッケージングもされておらず、振動子11の周囲空間が開放された状態の振動型ジャイロセンサ素子10のQ値を1としたときの相対値で示している。

図41に示すように、横軸に示した相対値がおよそ0.5、つまり、空間幅t7a,t7b,t7cが、振動子11の幅t6の1/2倍程度となっているとき、Q値が1近傍をとっている。また横軸の相対値がおよそ2のとき、つまり、空間幅t7a,t7b,t7cが、振動子11の幅t6の2倍以上となっているとき、Q値が1に飽和している。

この図41に示す測定結果は、第3の空間S3を規定する空間幅t7a,t7b,t7cが、振動子11の幅t6の1/2倍以上となるような周囲空間12を反応性イオンエッチングによって形成することで、振動子11の共振特性の劣化を大幅に抑制することができることを示している。さらに、図41に示す測定結果は、空間幅t7a,t7b,t7cが、振動子11の幅t6の2倍以上となるような周囲空間12を反応性イオンエッチングによって形成することで、振動子11の共振特性を最適にすることができることを示している。

上述した図40,41に示すQ値の測定結果は、常温にて振動型ジャイロセンサ10をパッケージングした場合の結果であるが、本発明は、これに限定されるものではない。例えば、大気中、80℃の環境下で振動型ジャイロセンサ素子10をパッケージングし、室温に戻した場合でも、図40,41に示したQ値の測定結果と同様の結果となる。したがって、振動子11の周囲の空間に気圧の変動があった場合、例えば、大気中でパッケージングされた振動型ジャイロセンサ素子10の振動子11の周囲の空間が、パッケージング後、大気圧となっていなくても有効となる。

なお、実施例においては、上述した手法によって形成した振動型ジャイロセンサ素子10を一例として示し、第1の空間S1を上部空間幅t7d、第2の空間S2を下部空間幅t7e、第3の空間S3を空間幅t7a,t7b,t7cで規定しているが、本発明は、これに限定されるものではなく、単結晶シリコン基板上に薄膜形成プロセスによって形成された下部電極、圧電薄膜、上部電極を有する片持ち梁形状の振動子を備え、圧電薄膜の圧電効果を利用して角速度を検出する振動型ジャイロセンサ素子に対して広く適用することができる。

例えば、本実施例では、図39に示すように、単結晶シリコン基板1に対して、結晶異方性エッチング、反応性イオンエッチングをすることで振動子11を形成しているため、必然的に振動子11の側壁面11c,11d,11eの近傍に単結晶シリコン基板1による外枠が残る形状となる。

しかしながら、本発明は、本実施例のように単結晶シリコン基板1による外枠が形成された振動型ジャイロセンサ素子10以外の振動型ジャイロセンサ素子に対しても、振動子11の側壁面11c,11d,11e、振動子11の上面11a、下面11bからのそれぞれの距離を上述したように確保することで、振動子11の共振特性を良好にする第1の空間S1,第2の空間S2,第3の空間S3を規定することができる。