JP2010026237A - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP2010026237A JP2010026237A JP2008187245A JP2008187245A JP2010026237A JP 2010026237 A JP2010026237 A JP 2010026237A JP 2008187245 A JP2008187245 A JP 2008187245A JP 2008187245 A JP2008187245 A JP 2008187245A JP 2010026237 A JP2010026237 A JP 2010026237A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- liquid crystal

- crystal display

- display device

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Liquid Crystal (AREA)

Abstract

【解決手段】

マトリックス状に複数の画素が配置され、液晶層を介して対向配置される第1及び第2の基板と、前記第1の基板側に、少なくとも各画素内に面状に形成された第1電極と、前記第1電極の上層に第1絶縁層を介して形成され、各画素毎に前記第1電極に重畳して形成される線状の複数の第2電極とを有し、前記第1電極と前記第2電極で生じる電界で前記液晶層を駆動する液晶表示装置であって、前記第1電極と同電位であり、前記第2電極と同層に形成され、前記各第2電極を間にして配置される線状の第3電極を備えた液晶表示装置である。

【選択図】図1

Description

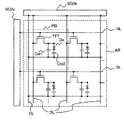

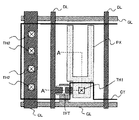

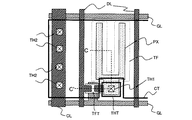

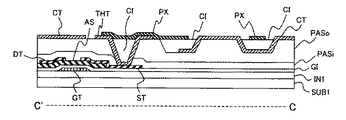

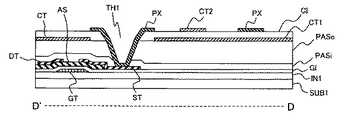

図5は本発明の実施形態1の液晶表示装置の概略構成図であり、図6は図3に示す実施形態1の液晶表示装置の1画素分の液晶表示素子の平面図であり、図1は図6に示すB−B'線での断面図である。なお、薄膜トランジスタとしてアモルファスシリコンTFTの場合について説明するが、これに限定されることはなくポリシリコンTFTを用いてもよい。また、スイッチング素子として薄膜トランジスタの代わりにダイオード等を用いてもよい。

ガラス基板SUB1の上面側(液晶側)の面に、下地膜IN1及びゲート電極GT、ゲート絶縁膜GI、半導体層AS、ドレイン電極DT、ソース電極STを形成し、アモルファスシリコンTFTの薄膜トランジスタTFTを形成する。この時、ドレイン線DLおよびドレイン電極DTと同時に形成される薄膜トランジスタTFTのソース電極STが、半導体層AS上にてドレイン電極DTと対向して形成されている。また、ソース電極STは、半導体層AS上から半導体層ASが形成されていない領域に至って延在され、この延在部はパッド部を構成するようになっている。このパッド部は後述の工程で画素電極PXと電気的及び物理的に接続される部分となる。

薄膜トランジスタTFTを保護する無機質材料である窒化シリコン膜からなる保護絶縁膜PASiをガラス基板SUB1の上面側の全面に形成し、薄膜トランジスタTFTの保護膜とする。この保護絶縁膜PASiの上層(基板の液晶側)に公知のスピンコート法等により、アクリル膜からなる平坦化膜PASoをガラス基板の上面側に形成し、薄膜トランジスタTFTをはじめとしたゲート線GL、ドレイン線DL、コモン線CL等の形成に伴うガラス基板上面の凹凸を平坦化する。なお、実施形態1の液晶表示装置の第1基板では保護絶縁膜PASiと平坦化膜PASoとで保護膜を構成している。

従来の対向電極と同じ領域に、透明電極材料であるITOで対向電極CTを形成する。このとき、実施形態1ではエッチングで形成されたトレンチTFの底部からトレンチTFの縁に沿いエッチングされていない領域までの上層部分が対向電極CTで覆われた構造となる。

容量絶縁膜CIを平坦化膜PASoの高さまでエッチングすることによって、平坦化膜PASoのトレンチTF部分以外の対向電極CTを容量絶縁膜CIから露出させると共に、トレンチTF部分のみに容量絶縁膜CIを形成する。この工程により、画素電極PXと同層に形成される線状の対向電極CTを形成する。ただし、容量絶縁膜CIの高さは対向電極CTとなるITO膜よりも低くなるように形成することが望ましい。

平坦化層PASoと保護絶縁膜PASiにコンタクトホールTH1を形成する。

コンタクトホール部分TH1とトレンチTFが形成される領域内にITO膜を形成することにより、薄膜トランジスタTFTのソース電極STに接続される画素電極PXを形成する。この工程により、線状の対向電極CTの間に、該対向電極CTと同層である線状の画素電極PXが形成される。

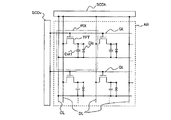

図8は本発明の実施形態2の液晶表示装置の概略構成を説明するための断面図である。ただし、図8は実施形態1の図1に相当する第1基板の断面図であり、図6のB−B'線での断面図に相当する。なお、実施形態2のLCD構成図、画素平面図は、それぞれ図5、図6と同様である。

ガラス基板SUB1の液晶側の面に、下地膜IN1及びゲート電極GT、ゲート絶縁膜GI、半導体層AS、ドレイン電極DT、ソース電極STを形成し、アモルファスシリコンTFTの薄膜トランジスタTFTを形成する。なお、この工程1は実施形態1の工程1と同じである。

薄膜トランジスタTFTを保護するために無機質材料である窒化シリコン膜からなる保護絶縁膜PASiをガラス基板SUB1の上面側(基板の液晶側)の全面に形成し、薄膜トランジスタTFTの保護膜とする。この保護絶縁膜PASiの上層(基板の液晶側)に公知のスピンコート法等により、アクリル膜からなる平坦化膜PASoをガラス基板SUB1の上面側に形成し、薄膜トランジスタTFTをはじめとしたゲート線GL、ドレイン線DL、コモン線CL等の形成に伴うガラス基板SUB1の上面の凹凸を平坦化する。なお、工程2における平坦化膜PASoの形成までの工程は、実施形態1と同じである。また、本実施形態2の液晶表示装置の第1基板SUB1においても保護絶縁膜PASiと平坦化膜PASoとで保護膜を構成する。

実施形態1と同様に、透明電極材料であるITOで対向電極CTを形成する。このとき、エッチングで形成されたトレンチTIの底部からトレンチTIの縁に沿いエッチングされていない領域までの上層部分がITO膜で形成された対向電極CTで覆われた構造となる。

容量絶縁膜CIをトレンチ絶縁膜TIの高さまでエッチングすることによって、トレンチTF部分以外の対向電極CTを容量絶縁膜CIから露出させると共に、トレンチTF部分のみに容量絶縁膜CIを形成する。この工程により、画素電極PXと同層に形成される線状の対向電極CTを形成する。ただし、要領絶縁膜CIの高さは対向電極CTとなるITO膜よりも低くなるように形成することが望ましい。

トレンチ絶縁膜TIから平坦化層PASoと保護絶縁膜PASiを貫通し、ソース電極STのパッド部に達するコンタクトホールTH1を形成する。

コンタクトホールTH1部分とトレンチTFが形成される領域内にITOを電極材料とする画素電極PXを形成することにより、薄膜トランジスタTFTのソース電極STに接続される画素電極PXを形成する。この工程により、線状の対向電極CTの間に、この対向電極CTと同層となる線状の画素電極PXが形成される。

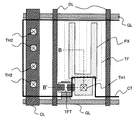

図10は本発明の実施形態1の液晶表示装置の概略構成を説明するための1画素分の液晶表示素子の平面図であり、図11は図10に示すC−C'線での断面図である。

ガラス基板SUB1の液晶LC側の面に、下地膜IN1及びゲート電極GT、ゲート絶縁膜GI、半導体層AS、ドレイン電極DT、ソース電極STを形成し、アモルファスシリコンTFTの薄膜トランジスタTFTを形成する。なお、この工程1は実施形態1、2の工程1と同じである。

薄膜トランジスタTFTを保護するために無機質材料である窒化シリコン膜からなる保護絶縁膜PASiをガラス基板SUB1の上面側(基板の液晶LC側)の全面に形成し、薄膜トランジスタTFTの保護膜とする。この保護絶縁膜PASiの上層(基板の液晶LC側)に公知のスピンコート法等により、アクリル膜からなる平坦化膜PASoをガラス基板SUB1の上面側に形成し、薄膜トランジスタTFTをはじめとしたゲート線GL、ドレイン線DL、コモン線CL等の形成に伴うガラス基板SUB1の上面の凹凸を平坦化する。なお、工程2における平坦化膜PASoの形成までの工程は、実施形態1、2と同じである。また、本実施形態3の液晶表示装置の第1基板SUB1においても保護絶縁膜PASiと平坦化膜PASoとで保護膜を構成する。

次に、平坦化膜PASoの上面に、画素電極PXの形状に沿ったトレンチTFを形成する。

次に、透明電極材料であるITOで対向電極CTを形成すると共に、コンタクトホールTH1部分にコンタクトホール電極THTを形成する。なお、コンタクトホール電極THTを除く対向電極CTの構成は、実施形態1と同様に構成である。

次に、実施形態1と同様に、塗布型絶縁膜を成膜し200度程度の熱処理により焼成処理を行い全面に容量絶縁膜CIを形成し、この容量絶縁膜CIを平坦化膜PASoの高さまでエッチングすることによって、コンタクトホール電極THTの上部とトレンチTF部分以外の対向電極CTを容量絶縁膜CIから露出させる。ただし、容量絶縁膜CIの高さは対向電極CTとなるITO膜よりも低くなるように形成することが望ましい

工程6(図11)

コンタクトホールTH1部分とトレンチTFが形成される領域内にITOを電極材料とする画素電極PXを形成することにより、コンタクトホール電極THTを介して薄膜トランジスタTFTのソース電極STに接続される画素電極PXを形成する。このとき、実施形態3ではコンタクトホールTH1を平坦化しているので、コンタクトホールTH1の上部においても液晶ギャップを均一にできる。

図13は本発明の実施形態4の液晶表示装置の概略構成を説明するための断面図である。ただし、図13は実施形態1の図1に相当する第1基板の断面図であり、実施形態3の図10のC−C'線での断面図に相当する。なお、実施形態4のLCD構成図、画素平面図は、それぞれ実施形態1の図5、実施形態3の図10と同様である。

ガラス基板SUB1の液晶LC側の面に、下地膜IN1及びゲート電極GT、ゲート絶縁膜GI、半導体層AS、ドレイン電極DT、ソース電極STを形成し、アモルファスシリコンTFTの薄膜トランジスタTFTを形成する。なお、この工程1は実施形態1の工程1と同じである。

薄膜トランジスタTFTを保護するために無機質材料である窒化シリコン膜からなる保護絶縁膜PASiをガラス基板SUB1の上面側(基板の液晶LC側)の全面に形成し、薄膜トランジスタTFTの保護膜とする。この保護絶縁膜PASiの上層(基板の液晶LC側)に公知のスピンコート法等により、アクリル膜からなる平坦化膜PASoをガラス基板SUB1の上面側に形成し、薄膜トランジスタTFTをはじめとしたゲート線GL、ドレイン線DL、コモン線CL等の形成に伴うガラス基板SUB1の上面の凹凸を平坦化する。次に、平坦化膜PASoの上層に例えば窒化シリコン膜からなるトレンチ絶縁膜TIを成膜する。なお、工程2におけるトレンチ絶縁膜TIの形成までの工程は、実施形態2と同じである。また、本実施形態4の液晶表示装置の第1基板SUB1においても保護絶縁膜PASiと平坦化膜PASoとで保護膜を構成する。

工程2で形成したトレンチTF1領域内に、平坦化層PASoと保護絶縁膜PASiを貫通し、ソース電極STのパッド部に達するコンタクトホールTH1を形成する。

透明電極材料であるITOで対向電極CTを形成すると共に、コンタクトホールTH1部分にコンタクトホール電極THTを形成する。次に、実施形態2と同様に、塗布型絶縁膜を成膜し200度程度の熱処理により焼成処理を行い全面に容量絶縁膜CIを形成し、この容量絶縁膜CIをトレンチ絶縁膜TIの高さまでエッチングすることによって、コンタクトホール電極THTの上部とトレンチTF部分以外の対向電極CTを容量絶縁膜CIから露出させる。

コンタクトホールTH1部分とトレンチTFが形成される領域内にITOを電極材料とする画素電極PXを形成することにより、コンタクトホール電極THTを介して薄膜トランジスタTFTのソース電極STに接続される画素電極PXを形成する。このとき、実施形態4でもコンタクトホールTH1を平坦化しているので、コンタクトホールTH1の上部においても液晶ギャップを均一にできる。

図15は本発明の実施形態1の液晶表示装置の概略構成を説明するための1画素分の液晶表示素子の平面図であり、図16は図15に示すD−D'線での断面図である。なお、後述するように、画素電極PXと同層に形成された上層対向電極CT2との間には容量絶縁膜CIが介在しないので液晶容量Clcのみが形成され、薄膜トランジスタTFTのソースには保持容量Cst1と液晶容量Clcとが並列に接続されるのみの構成となる。

ガラス基板SUB1の液晶LC側の面に、下地膜IN1及びゲート電極GT、ゲート絶縁膜GI、半導体層AS、ドレイン電極DT、ソース電極STを形成し、アモルファスシリコンTFTの薄膜トランジスタTFTを形成する。なお、この工程1は実施形態1の工程1と同じである。

薄膜トランジスタTFTを保護するために無機質材料である窒化シリコン膜からなる保護絶縁膜PASiをガラス基板SUB1の上面側(基板の液晶LC側)の全面に形成し、薄膜トランジスタTFTの保護膜とする。この保護絶縁膜PASiの上層(基板の液晶LC側)に公知のスピンコート法等により、アクリル膜からなる平坦化膜PASoをガラス基板SUB1の上面側に形成し、薄膜トランジスタTFTをはじめとしたゲート線GL、ドレイン線DL、コモン線CL等の形成に伴うガラス基板SUB1の上面の凹凸を平坦化する。次に、平坦化膜PASoの上層に透明電極材料であるITOで下層対向電極CT1を形成する。

次に、塗布型絶縁膜を成膜し200度程度の熱処理により焼成処理を行い全面に容量絶縁膜CIを形成する。次に、容量絶縁膜CIに下層対向電極CT1に達するコンタクトホールTH3、並びに平坦化層PASoと保護絶縁膜PASiを貫通しソース電極STのパッド部に達するコンタクトホールTH1、及び平坦化層PASoと保護絶縁膜PASiを貫通しコモン線CLに達するコンタクトホールTH4を形成する。

次に、容量絶縁膜CIの上層に、ITOを電極材料とする画素電極PX及び上層対向電極CT2を形成することにより、薄膜トランジスタTFTのソース電極STに電気的に接続される画素電極PXと、コモン線CLに電気的に接続される上層対向電極CT2とを形成する。

AR・・・液晶表示領域、Clc・・・液晶容量、Cst1・・・保持容量

Cst2・・・絶縁膜容量、SCDv・・・ゲートドライバ、

SCDh・・・ドレインドライバ、PX・・・画素電極、CT・・・対向電極

CT1・・・下層対向電極、CT2・・・上層対向電極、TFT・・・薄膜トランジスタ

TH1,TH2,TH3,TH4・・・コンタクトホール

TF,TF1・・・トレンチ(溝)、SUB1,SUB2・・・第1基板、ガラス基板

IN1・・・下地膜、GI・・・ゲート絶縁膜、PASi・・・保護絶縁膜

PASo・・・平坦化膜、CI・・・容量絶縁膜、GT・・・ゲート電極

ST・・・ソース電極、DT・・・ドレイン電極、AS・・・半導体層

THT・・・コンタクトホール電極、BM・・・ブラックマトリクス、LC・・・液晶層

CF・・・カラーフィルタ、ORI1,ORI2・・・配向膜、PL・・・偏光板

TI・・・トレンチ絶縁膜

Claims (7)

- マトリックス状に複数の画素が配置され、液晶層を介して対向配置される第1及び第2の基板と、

前記第1の基板側に、少なくとも各画素内に面状に形成された第1電極と、

前記第1電極の上層に第1絶縁層を介して形成され、各画素毎に前記第1電極に重畳して形成される線状の複数の第2電極と

を有し、前記第1電極と前記第2電極で生じる電界で前記液晶層を駆動する液晶表示装置であって、

前記第1電極と同電位であり、前記第2電極と同層に形成され、前記各第2電極を間にして配置される線状の第3電極

を備えたことを特徴とする液晶表示装置。 - 請求項1に記載の液晶表示装置において、

前記第1電極と前記第3電極とが一体に形成された導電層からなることを特徴とする液晶表示装置。 - 請求項1又は2に記載の液晶表示装置において、

平坦化層に溝が形成され、前記溝に前記第1電極の一部が形成されることを特徴とする液晶表示装置。 - 請求項1又は2に記載の液晶表示装置において、

平坦化層の上層に形成された第2絶縁層を有し、前記第2絶縁層に形成された溝に前記第1電極の一部が形成されていることを特徴とする液晶表示装置。 - 請求項1に記載の液晶表示装置において、

前記第1電極と前記第3電極とが前記第1絶縁層に形成されたコンタクト部を介して接続されることを特徴とする液晶表示装置。 - 請求項1又は5に記載の液晶表示装置において、

前記第1絶縁層が容量絶縁層で形成され、前記第2電極と前記第3電極とが前記第1絶縁層上に形成されることを特徴とする液晶表示装置。 - 請求項1乃至7のいずれか1項に記載の液晶表示装置において、

前記第2電極に表示用の電荷を入力する薄膜トランジスタを有し、前記薄膜トランジスタのソース電極と前記第2電極とを接続するコンタクト部を前記第1絶縁層で平坦化したことを特徴とする液晶表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008187245A JP5502293B2 (ja) | 2008-07-18 | 2008-07-18 | 液晶表示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008187245A JP5502293B2 (ja) | 2008-07-18 | 2008-07-18 | 液晶表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010026237A true JP2010026237A (ja) | 2010-02-04 |

| JP5502293B2 JP5502293B2 (ja) | 2014-05-28 |

Family

ID=41732130

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008187245A Active JP5502293B2 (ja) | 2008-07-18 | 2008-07-18 | 液晶表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5502293B2 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013257530A (ja) * | 2012-06-12 | 2013-12-26 | Hannstar Display Corp | 液晶ディスプレイパネル及びその画素アレイ基板 |

| JP2014010182A (ja) * | 2012-06-27 | 2014-01-20 | Kyocera Corp | 液晶表示装置 |

| JP2014095840A (ja) * | 2012-11-09 | 2014-05-22 | Japan Display Inc | 液晶表示装置 |

| JP2014182234A (ja) * | 2013-03-19 | 2014-09-29 | Mitsubishi Electric Corp | 液晶表示装置及びその製造方法 |

| WO2019167405A1 (ja) * | 2018-03-02 | 2019-09-06 | 株式会社ジャパンディスプレイ | 表示装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007183583A (ja) * | 2005-12-05 | 2007-07-19 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| JP2007310273A (ja) * | 2006-05-22 | 2007-11-29 | Mitsubishi Electric Corp | 液晶表示装置、及びその製造方法 |

| JP2007316535A (ja) * | 2006-05-29 | 2007-12-06 | Nec Lcd Technologies Ltd | 横電界方式のアクティブマトリクス型液晶表示装置 |

| JP2008040189A (ja) * | 2006-08-08 | 2008-02-21 | Hitachi Displays Ltd | 半透過型液晶表示装置 |

| JP2009186869A (ja) * | 2008-02-08 | 2009-08-20 | Epson Imaging Devices Corp | 液晶表示装置 |

-

2008

- 2008-07-18 JP JP2008187245A patent/JP5502293B2/ja active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007183583A (ja) * | 2005-12-05 | 2007-07-19 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| JP2007310273A (ja) * | 2006-05-22 | 2007-11-29 | Mitsubishi Electric Corp | 液晶表示装置、及びその製造方法 |

| JP2007316535A (ja) * | 2006-05-29 | 2007-12-06 | Nec Lcd Technologies Ltd | 横電界方式のアクティブマトリクス型液晶表示装置 |

| JP2008040189A (ja) * | 2006-08-08 | 2008-02-21 | Hitachi Displays Ltd | 半透過型液晶表示装置 |

| JP2009186869A (ja) * | 2008-02-08 | 2009-08-20 | Epson Imaging Devices Corp | 液晶表示装置 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013257530A (ja) * | 2012-06-12 | 2013-12-26 | Hannstar Display Corp | 液晶ディスプレイパネル及びその画素アレイ基板 |

| CN103488013A (zh) * | 2012-06-12 | 2014-01-01 | 瀚宇彩晶股份有限公司 | 液晶显示面板及其像素阵列基板 |

| JP2014010182A (ja) * | 2012-06-27 | 2014-01-20 | Kyocera Corp | 液晶表示装置 |

| JP2014095840A (ja) * | 2012-11-09 | 2014-05-22 | Japan Display Inc | 液晶表示装置 |

| JP2014182234A (ja) * | 2013-03-19 | 2014-09-29 | Mitsubishi Electric Corp | 液晶表示装置及びその製造方法 |

| WO2019167405A1 (ja) * | 2018-03-02 | 2019-09-06 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP2019152745A (ja) * | 2018-03-02 | 2019-09-12 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP7030563B2 (ja) | 2018-03-02 | 2022-03-07 | 株式会社ジャパンディスプレイ | 表示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5502293B2 (ja) | 2014-05-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4356750B2 (ja) | 液晶表示装置及びその製造方法 | |

| JP6182361B2 (ja) | 液晶表示装置 | |

| JP5571759B2 (ja) | 液晶表示素子及びその製造方法 | |

| CN103869554B (zh) | 液晶显示面板 | |

| CN107329339B (zh) | 阵列基板及曲面液晶显示器 | |

| CN101236971B (zh) | 薄膜晶体管基板及包括该基板的显示装置 | |

| JP2015049426A (ja) | 液晶表示装置 | |

| JP5526085B2 (ja) | 液晶表示装置 | |

| JP2009181091A (ja) | 液晶表示装置 | |

| US9235091B2 (en) | Liquid crystal display device and manufacturing method thereof | |

| JP5502293B2 (ja) | 液晶表示装置 | |

| US20160026043A1 (en) | Display device | |

| CN103874957B (zh) | 液晶显示元件和液晶显示装置 | |

| JP2007279634A (ja) | 横電界方式の液晶表示装置 | |

| JP2008262006A (ja) | アクティブマトリクス基板及び液晶パネル | |

| WO2015132819A1 (ja) | 液晶表示装置及びその製造方法 | |

| WO2010103676A1 (ja) | アクティブマトリクス基板、表示パネル、表示装置、並びに電子機器 | |

| JP5917127B2 (ja) | 液晶表示装置 | |

| US9703152B2 (en) | Liquid crystal display device | |

| KR100698049B1 (ko) | 액정표시장치 및 그의 제조방법 | |

| CN108490705A (zh) | 阵列基板、液晶显示面板与显示装置 | |

| CN102998864B (zh) | 液晶显示装置 | |

| US9323112B2 (en) | Liquid crystal display and electronic apparatus having electrodes with openings therein | |

| JP4905011B2 (ja) | 液晶装置、及び電子機器 | |

| JP2009175561A (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20110218 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20110218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110307 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120904 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120905 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121001 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130611 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130805 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140218 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140313 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5502293 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |