JP2010016375A - 積層チップパッケージおよびその製造方法 - Google Patents

積層チップパッケージおよびその製造方法 Download PDFInfo

- Publication number

- JP2010016375A JP2010016375A JP2009148255A JP2009148255A JP2010016375A JP 2010016375 A JP2010016375 A JP 2010016375A JP 2009148255 A JP2009148255 A JP 2009148255A JP 2009148255 A JP2009148255 A JP 2009148255A JP 2010016375 A JP2010016375 A JP 2010016375A

- Authority

- JP

- Japan

- Prior art keywords

- main body

- terminals

- disposed

- wiring

- substructure

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10W90/00—

-

- H10P72/74—

-

- H10W46/00—

-

- H10W70/093—

-

- H10W72/0198—

-

- H10W99/00—

-

- H10P72/743—

-

- H10W46/101—

-

- H10W46/301—

-

- H10W72/01—

-

- H10W72/834—

-

- H10W74/00—

-

- H10W90/20—

-

- H10W90/22—

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Dicing (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

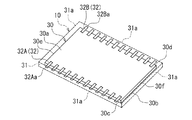

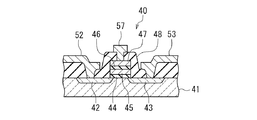

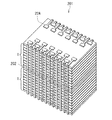

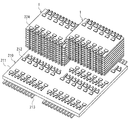

【解決手段】積層チップパッケージ1は、複数の階層部分11〜18を含む本体2と、本体2の側面に配置された配線3A,3Bと、本体2の上面に配置された複数の第1の端子22Aと、本体2の下面に配置された複数の第2の端子22Bとを備えている。各階層部分は、半導体チップと、半導体チップの少なくとも1つの側面を覆う絶縁部と、半導体チップに接続された複数の電極とを含んでいる。各電極は、配線3A,3Bが配置された本体2の側面に配置され且つ絶縁部によって囲まれた端面を有している。配線3A,3Bは、複数の階層部分における複数の電極の端面と複数の第1の端子22Aと複数の第2の端子22Bとに接続されている。

【選択図】図1

Description

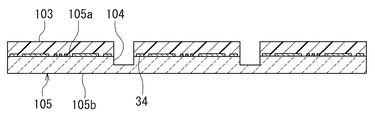

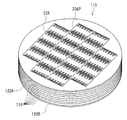

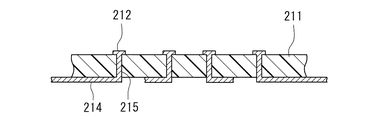

互いに反対側を向いた第1および第2の面を有する1つの半導体ウェハにおける第1の面に処理を施すことによって、それぞれデバイスを含む複数の半導体チップ予定部が配列され、且つ半導体ウェハの第1および第2の面に対応する第1および第2の面を有する基礎構造物前ウェハを作製する工程と、

基礎構造物前ウェハに対して、少なくとも1つの半導体チップ予定部に隣接するように延び、且つ基礎構造物前ウェハの第1の面において開口する1以上の溝を形成する工程と、

1以上の溝を埋めるように、後に絶縁部の一部となる絶縁層を形成する工程と、

一部が絶縁層の上に配置されるように、複数の電極を形成する工程とを含み、

積層チップパッケージを完成させる工程において、溝が延びる方向に沿って切断面が形成されるように絶縁層を切断し、これにより、絶縁層の切断面によって絶縁部の少なくとも1つの端面の一部が形成され、且つ複数の電極の端面が露出してもよい。

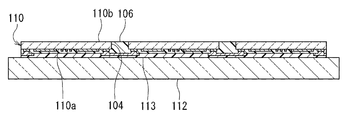

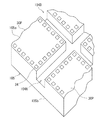

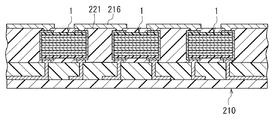

複数の基礎構造物を、積層チップパッケージの複数の階層部分の積層の順序に対応させて積層して積層体を形成すると共に、この積層体に複数組の第1の端子と複数組の第2の端子とを設けて、積層基礎構造物を作製する工程と、

積層基礎構造物を切断することによって、複数の階層部分の積層方向と直交する一方向に配列され、それぞれ後に、第1の端子と複数の第2の端子とが配置された状態の本体となる複数の本体予定部を含む本体集合体を作製する工程と、

本体集合体における各本体予定部に対してそれぞれ配線を形成する工程と、

配線の形成後、複数の本体予定部が互いに分離されてそれぞれ本体となることによって複数の積層チップパッケージが形成されるように、本体集合体を切断する工程とを含んでいてもよい。

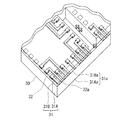

以下、本発明の実施の形態について図面を参照して詳細に説明する。始めに、図1および図2を参照して、本発明の第1の実施の形態に係る積層チップパッケージの構成について説明する。図1は、本実施の形態に係る積層チップパッケージの斜視図である。図2は、下面側から見た図1の積層チップパッケージを示す斜視図である。図1および図2に示したように、本実施の形態に係る積層チップパッケージ1は、直方体形状の本体2を備えている。本体2は、上面2a、下面2b、互いに反対側を向いた第1の側面2cおよび第2の側面2d、ならびに互いに反対側を向いた第3の側面2eおよび第4の側面2fを有している。

次に、本発明の第2の実施の形態について説明する。本実施の形態に係る積層チップパッケージ1の外観は、第1の実施の形態と同様に、図1および図2に示したようになる。

Claims (6)

- 上面、下面および4つの側面を有する本体と、

前記本体の少なくとも1つの側面に配置された配線と、

前記本体の上面に配置された複数の第1の端子と、

前記本体の下面に配置された複数の第2の端子とを備え、

前記本体は、積層された複数の階層部分を含み、

前記複数の階層部分の各々は、上面、下面および4つの側面を有する半導体チップと、前記半導体チップの4つの側面のうちの少なくとも1つの側面を覆う絶縁部と、前記半導体チップに接続された複数の電極とを含み、

前記絶縁部は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置された少なくとも1つの端面を有し、

前記複数の電極の各々は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置され且つ前記絶縁部によって囲まれた端面を有し、

前記配線は、前記複数の階層部分における複数の電極の端面と前記複数の第1の端子と前記複数の第2の端子とに接続されていることを特徴とする積層チップパッケージ。 - 上面、下面および4つの側面を有する本体と、

前記本体の少なくとも1つの側面に配置された配線と、

前記本体の上面に配置された複数の第1の端子と、

前記本体の下面に配置された複数の第2の端子とを備え、

前記本体は、積層された複数の階層部分を含み、

前記複数の階層部分の各々は、上面、下面および4つの側面を有する半導体チップと、前記半導体チップの4つの側面のうちの少なくとも1つの側面を覆う絶縁部と、前記半導体チップに接続された複数の電極とを含み、

前記絶縁部は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置された少なくとも1つの端面を有し、

前記複数の電極の各々は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置され且つ前記絶縁部によって囲まれた端面を有し、

前記配線は、前記複数の階層部分における複数の電極の端面と前記複数の第1の端子と前記複数の第2の端子とに接続されている積層チップパッケージを製造する方法であって、

前記積層チップパッケージの複数の階層部分にそれぞれ対応する複数の基礎構造物であって、各々が対応する階層部分を複数含み、後にそれら対応する階層部分のうちの隣接するもの同士の境界位置で切断される複数の基礎構造物を作製する工程と、

前記複数の基礎構造物を用いて前記本体を作製すると共に、前記本体に対して前記複数の第1の端子と前記複数の第2の端子と前記配線とを形成して、積層チップパッケージを完成させる工程とを備えたことを特徴とする積層チップパッケージの製造方法。 - 前記複数の基礎構造物を作製する工程は、各基礎構造物を作製するための一連の工程として、

互いに反対側を向いた第1および第2の面を有する1つの半導体ウェハにおける前記第1の面に処理を施すことによって、それぞれデバイスを含む複数の半導体チップ予定部が配列され、且つ前記半導体ウェハの第1および第2の面に対応する第1および第2の面を有する基礎構造物前ウェハを作製する工程と、

前記基礎構造物前ウェハに対して、少なくとも1つの半導体チップ予定部に隣接するように延び、且つ前記基礎構造物前ウェハの第1の面において開口する1以上の溝を形成する工程と、

前記1以上の溝を埋めるように、後に前記絶縁部の一部となる絶縁層を形成する工程と、

一部が前記絶縁層の上に配置されるように、前記複数の電極を形成する工程とを含み、

前記積層チップパッケージを完成させる工程において、前記溝が延びる方向に沿って切断面が形成されるように前記絶縁層を切断し、これにより、前記絶縁層の前記切断面によって前記絶縁部の前記少なくとも1つの端面の一部が形成され、且つ前記複数の電極の端面が露出することを特徴とする請求項2記載の積層チップパッケージの製造方法。 - 前記積層チップパッケージを完成させる工程は、

前記複数の基礎構造物を、前記積層チップパッケージの複数の階層部分の積層の順序に対応させて積層して積層体を形成すると共に、この積層体に複数組の第1の端子と複数組の第2の端子とを設けて、積層基礎構造物を作製する工程と、

前記積層基礎構造物を切断することによって、前記複数の階層部分の積層方向と直交する一方向に配列され、それぞれ後に、前記第1の端子と複数の第2の端子とが配置された状態の前記本体となる複数の本体予定部を含む本体集合体を作製する工程と、

前記本体集合体における各本体予定部に対してそれぞれ前記配線を形成する工程と、

前記配線の形成後、複数の本体予定部が互いに分離されてそれぞれ前記本体となることによって複数の前記積層チップパッケージが形成されるように、前記本体集合体を切断する工程とを含むことを特徴とする請求項2記載の積層チップパッケージの製造方法。 - 前記積層基礎構造物を作製する工程では、前記複数の基礎構造物を積層して形成された前記積層体の積層方向の両端面に、それぞれ、前記複数組の第1の端子を含む第1の端子用ウェハと前記複数組の第2の端子を含む第2の端子用ウェハを張り付けることを特徴とする請求項4記載の積層チップパッケージの製造方法。

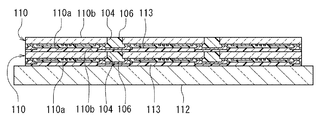

- 積層された複数の積層チップパッケージを含み、上下に隣接する2つの積層チップパッケージが電気的に接続されて構成された電子部品であって、

前記複数の積層チップパッケージは、それぞれ、

上面、下面および4つの側面を有する本体と、

前記本体の少なくとも1つの側面に配置された配線と、

前記本体の上面に配置された複数の第1の端子と、

前記本体の下面に配置された複数の第2の端子とを備え、

前記本体は、積層された複数の階層部分を含み、

前記複数の階層部分の各々は、上面、下面および4つの側面を有する半導体チップと、前記半導体チップの4つの側面のうちの少なくとも1つの側面を覆う絶縁部と、前記半導体チップに接続された複数の電極とを含み、

前記絶縁部は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置された少なくとも1つの端面を有し、

前記複数の電極の各々は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置され且つ前記絶縁部によって囲まれた端面を有し、

前記配線は、前記複数の階層部分における複数の電極の端面と前記複数の第1の端子と前記複数の第2の端子とに接続され、

前記上下に隣接する2つの積層チップパッケージにおいて、下側の積層チップパッケージの複数の第1の端子と上側の積層チップパッケージの複数の第2の端子とが電気的に接続されていることを特徴とする電子部品。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/216,168 | 2008-06-30 | ||

| US12/216,168 US7745259B2 (en) | 2008-06-30 | 2008-06-30 | Layered chip package and method of manufacturing same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010016375A true JP2010016375A (ja) | 2010-01-21 |

| JP5461077B2 JP5461077B2 (ja) | 2014-04-02 |

Family

ID=41446419

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009148255A Expired - Fee Related JP5461077B2 (ja) | 2008-06-30 | 2009-06-23 | 積層チップパッケージ |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7745259B2 (ja) |

| JP (1) | JP5461077B2 (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011151365A (ja) * | 2010-01-22 | 2011-08-04 | Headway Technologies Inc | 積層チップパッケージの製造方法 |

| JP2011166110A (ja) * | 2010-02-04 | 2011-08-25 | Headway Technologies Inc | 積層チップパッケージの製造方法 |

| JP2012009808A (ja) * | 2010-06-28 | 2012-01-12 | Headway Technologies Inc | 積層半導体基板および積層チップパッケージ並びにこれらの製造方法 |

| JP2012023333A (ja) * | 2010-07-13 | 2012-02-02 | Headway Technologies Inc | 積層チップパッケージおよびその製造方法 |

| JP2012023332A (ja) * | 2010-07-13 | 2012-02-02 | Headway Technologies Inc | 積層チップパッケージおよびその製造方法 |

| JP2020194936A (ja) * | 2019-05-30 | 2020-12-03 | 株式会社ディスコ | ウェーハの製造方法及び積層デバイスチップの製造方法 |

| JP2023049827A (ja) * | 2021-09-29 | 2023-04-10 | 株式会社ディスコ | 積層デバイスチップの製造方法 |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009140798A1 (zh) * | 2008-05-21 | 2009-11-26 | 精材科技股份有限公司 | 电子元件封装体及其制作方法 |

| US7846772B2 (en) * | 2008-06-23 | 2010-12-07 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US7868442B2 (en) * | 2008-06-30 | 2011-01-11 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US7968374B2 (en) * | 2009-02-06 | 2011-06-28 | Headway Technologies, Inc. | Layered chip package with wiring on the side surfaces |

| TWI387085B (zh) * | 2009-05-12 | 2013-02-21 | 財團法人工業技術研究院 | 晶片堆疊的硬線式切換器及硬線式切換器的操作方法 |

| US7902677B1 (en) * | 2009-10-28 | 2011-03-08 | Headway Technologies, Inc. | Composite layered chip package and method of manufacturing same |

| US8012802B2 (en) * | 2010-02-04 | 2011-09-06 | Headway Technologies, Inc. | Method of manufacturing layered chip package |

| US8421243B2 (en) | 2010-06-24 | 2013-04-16 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US8362602B2 (en) * | 2010-08-09 | 2013-01-29 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US8541887B2 (en) | 2010-09-03 | 2013-09-24 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US8441112B2 (en) | 2010-10-01 | 2013-05-14 | Headway Technologies, Inc. | Method of manufacturing layered chip package |

| US8618646B2 (en) | 2010-10-12 | 2013-12-31 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US8659166B2 (en) | 2010-11-18 | 2014-02-25 | Headway Technologies, Inc. | Memory device, laminated semiconductor substrate and method of manufacturing the same |

| US8536712B2 (en) | 2011-01-26 | 2013-09-17 | Sae Magnetics Ltd. | Memory device and method of manufacturing the same |

| US8344494B2 (en) * | 2011-04-11 | 2013-01-01 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US8358015B2 (en) | 2011-06-09 | 2013-01-22 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US8653639B2 (en) | 2011-06-09 | 2014-02-18 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US8426981B2 (en) * | 2011-09-22 | 2013-04-23 | Headway Technologies, Inc. | Composite layered chip package |

| US8492175B1 (en) * | 2011-11-28 | 2013-07-23 | Applied Micro Circuits Corporation | System and method for aligning surface mount devices on a substrate |

| FR2985367A1 (fr) * | 2011-12-29 | 2013-07-05 | 3D Plus | Procede de fabrication collective de modules electroniques 3d ne comportant que des pcbs valides |

| US9967984B1 (en) | 2015-01-14 | 2018-05-08 | Vlt, Inc. | Power adapter packaging |

| US9936580B1 (en) | 2015-01-14 | 2018-04-03 | Vlt, Inc. | Method of forming an electrical connection to an electronic module |

| JP6384879B2 (ja) * | 2015-01-23 | 2018-09-05 | オリンパス株式会社 | 撮像装置、および内視鏡 |

| US10264664B1 (en) * | 2015-06-04 | 2019-04-16 | Vlt, Inc. | Method of electrically interconnecting circuit assemblies |

| US10158357B1 (en) | 2016-04-05 | 2018-12-18 | Vlt, Inc. | Method and apparatus for delivering power to semiconductors |

| US10903734B1 (en) | 2016-04-05 | 2021-01-26 | Vicor Corporation | Delivering power to semiconductor loads |

| US10785871B1 (en) | 2018-12-12 | 2020-09-22 | Vlt, Inc. | Panel molded electronic assemblies with integral terminals |

| US11336167B1 (en) | 2016-04-05 | 2022-05-17 | Vicor Corporation | Delivering power to semiconductor loads |

| WO2025208417A1 (zh) * | 2024-04-03 | 2025-10-09 | 玻芯成(重庆)半导体科技有限公司 | 叠层芯片及其制造方法、电路单元的制造方法、叠层基板 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0945848A (ja) * | 1995-07-26 | 1997-02-14 | Internatl Business Mach Corp <Ibm> | マルチチップ・スタック用の導電性モノリシックl接続を備えたエンドキャップ・チップおよびその製造方法 |

| JP2001210782A (ja) * | 2000-01-27 | 2001-08-03 | Seiko Epson Corp | 半導体チップ、マルチチップパッケージ、および半導体装置と、並びに、それを用いた電子機器 |

| JP2002050737A (ja) * | 2000-08-02 | 2002-02-15 | Fujitsu Ltd | 半導体素子積層体、半導体素子積層体の製造方法、及び半導体装置 |

| WO2007066409A1 (ja) * | 2005-12-09 | 2007-06-14 | Spansion Llc | 半導体装置およびその製造方法 |

| WO2007071696A1 (fr) * | 2005-12-23 | 2007-06-28 | 3D Plus | Procede de fabrication collective de modules electroniques 3d |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5953588A (en) | 1996-12-21 | 1999-09-14 | Irvine Sensors Corporation | Stackable layers containing encapsulated IC chips |

| US6734370B2 (en) | 2001-09-07 | 2004-05-11 | Irvine Sensors Corporation | Multilayer modules with flexible substrates |

| JP5014853B2 (ja) * | 2007-03-23 | 2012-08-29 | 株式会社日立製作所 | 半導体装置の製造方法 |

-

2008

- 2008-06-30 US US12/216,168 patent/US7745259B2/en not_active Expired - Fee Related

-

2009

- 2009-06-23 JP JP2009148255A patent/JP5461077B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0945848A (ja) * | 1995-07-26 | 1997-02-14 | Internatl Business Mach Corp <Ibm> | マルチチップ・スタック用の導電性モノリシックl接続を備えたエンドキャップ・チップおよびその製造方法 |

| JP2001210782A (ja) * | 2000-01-27 | 2001-08-03 | Seiko Epson Corp | 半導体チップ、マルチチップパッケージ、および半導体装置と、並びに、それを用いた電子機器 |

| JP2002050737A (ja) * | 2000-08-02 | 2002-02-15 | Fujitsu Ltd | 半導体素子積層体、半導体素子積層体の製造方法、及び半導体装置 |

| WO2007066409A1 (ja) * | 2005-12-09 | 2007-06-14 | Spansion Llc | 半導体装置およびその製造方法 |

| WO2007071696A1 (fr) * | 2005-12-23 | 2007-06-28 | 3D Plus | Procede de fabrication collective de modules electroniques 3d |

| JP2009521116A (ja) * | 2005-12-23 | 2009-05-28 | トロワデー、プリュ | 3d電子モジュールを集積的に製造する方法 |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011151365A (ja) * | 2010-01-22 | 2011-08-04 | Headway Technologies Inc | 積層チップパッケージの製造方法 |

| JP2011166110A (ja) * | 2010-02-04 | 2011-08-25 | Headway Technologies Inc | 積層チップパッケージの製造方法 |

| JP2012009808A (ja) * | 2010-06-28 | 2012-01-12 | Headway Technologies Inc | 積層半導体基板および積層チップパッケージ並びにこれらの製造方法 |

| US8426946B2 (en) | 2010-06-28 | 2013-04-23 | Headway Technologies, Inc. | Laminated semiconductor substrate, laminated chip package and method of manufacturing the same |

| JP2012023333A (ja) * | 2010-07-13 | 2012-02-02 | Headway Technologies Inc | 積層チップパッケージおよびその製造方法 |

| JP2012023332A (ja) * | 2010-07-13 | 2012-02-02 | Headway Technologies Inc | 積層チップパッケージおよびその製造方法 |

| JP2020194936A (ja) * | 2019-05-30 | 2020-12-03 | 株式会社ディスコ | ウェーハの製造方法及び積層デバイスチップの製造方法 |

| JP2023049827A (ja) * | 2021-09-29 | 2023-04-10 | 株式会社ディスコ | 積層デバイスチップの製造方法 |

| JP7716948B2 (ja) | 2021-09-29 | 2025-08-01 | 株式会社ディスコ | 積層デバイスチップの製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090321957A1 (en) | 2009-12-31 |

| US7745259B2 (en) | 2010-06-29 |

| JP5461077B2 (ja) | 2014-04-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5461077B2 (ja) | 積層チップパッケージ | |

| JP5576962B2 (ja) | 積層チップパッケージの製造方法 | |

| JP5451204B2 (ja) | 積層チップパッケージの製造方法 | |

| JP5432604B2 (ja) | 積層チップパッケージの製造方法 | |

| JP5102339B2 (ja) | 積層チップパッケージの製造方法 | |

| JP5535560B2 (ja) | メモリデバイスを実現する積層チップパッケージ | |

| JP5491802B2 (ja) | ヒートシンクを備えた積層チップパッケージ | |

| JP5550872B2 (ja) | 積層チップパッケージおよびその製造方法 | |

| JP5275941B2 (ja) | 積層チップパッケージおよびその製造方法 | |

| JP5154667B2 (ja) | 積層チップパッケージおよびその製造方法 | |

| JP5004311B2 (ja) | 積層チップパッケージおよびその製造方法 | |

| JP5769293B2 (ja) | 積層チップパッケージの製造方法 | |

| JP4927194B2 (ja) | 積層チップパッケージの製造方法 | |

| JP4948635B2 (ja) | 積層チップパッケージの製造方法 | |

| JP5228068B2 (ja) | 積層チップパッケージおよびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120217 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130117 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130122 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130418 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140115 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5461077 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |