JP2008527739A - 被覆キャップを有する相互接続構造およびその製造方法 - Google Patents

被覆キャップを有する相互接続構造およびその製造方法 Download PDFInfo

- Publication number

- JP2008527739A JP2008527739A JP2007551251A JP2007551251A JP2008527739A JP 2008527739 A JP2008527739 A JP 2008527739A JP 2007551251 A JP2007551251 A JP 2007551251A JP 2007551251 A JP2007551251 A JP 2007551251A JP 2008527739 A JP2008527739 A JP 2008527739A

- Authority

- JP

- Japan

- Prior art keywords

- dielectric layer

- interconnect

- covering cap

- interconnect structure

- copper

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 12

- 238000000151 deposition Methods 0.000 claims abstract description 12

- 239000010410 layer Substances 0.000 claims description 89

- 238000000034 method Methods 0.000 claims description 55

- 229910052751 metal Inorganic materials 0.000 claims description 24

- 239000002184 metal Substances 0.000 claims description 24

- 230000008569 process Effects 0.000 claims description 16

- 239000011229 interlayer Substances 0.000 claims description 15

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 14

- 239000010941 cobalt Substances 0.000 claims description 9

- 229910017052 cobalt Inorganic materials 0.000 claims description 9

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 claims description 9

- 229910052759 nickel Inorganic materials 0.000 claims description 7

- 229910001092 metal group alloy Inorganic materials 0.000 claims description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 20

- 239000010949 copper Substances 0.000 description 17

- 229910052802 copper Inorganic materials 0.000 description 16

- 230000004888 barrier function Effects 0.000 description 10

- 239000004020 conductor Substances 0.000 description 7

- 239000000463 material Substances 0.000 description 7

- 238000009792 diffusion process Methods 0.000 description 6

- 238000001465 metallisation Methods 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 150000002739 metals Chemical group 0.000 description 5

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 239000011248 coating agent Substances 0.000 description 4

- 238000000576 coating method Methods 0.000 description 4

- 238000007772 electroless plating Methods 0.000 description 4

- 238000009713 electroplating Methods 0.000 description 4

- 238000005240 physical vapour deposition Methods 0.000 description 4

- 238000001020 plasma etching Methods 0.000 description 4

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- 230000009977 dual effect Effects 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 239000003870 refractory metal Substances 0.000 description 3

- 229910052707 ruthenium Inorganic materials 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- -1 tantalum (Ta) Chemical class 0.000 description 3

- 244000132059 Carica parviflora Species 0.000 description 2

- 235000014653 Carica parviflora Nutrition 0.000 description 2

- 229910000881 Cu alloy Inorganic materials 0.000 description 2

- QAAXRTPGRLVPFH-UHFFFAOYSA-N [Bi].[Cu] Chemical compound [Bi].[Cu] QAAXRTPGRLVPFH-UHFFFAOYSA-N 0.000 description 2

- TYYOGQJRDAYPNI-UHFFFAOYSA-N [Re].[Cu] Chemical compound [Re].[Cu] TYYOGQJRDAYPNI-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- PLZFHNWCKKPCMI-UHFFFAOYSA-N cadmium copper Chemical compound [Cu].[Cd] PLZFHNWCKKPCMI-UHFFFAOYSA-N 0.000 description 2

- HVMJUDPAXRRVQO-UHFFFAOYSA-N copper indium Chemical compound [Cu].[In] HVMJUDPAXRRVQO-UHFFFAOYSA-N 0.000 description 2

- HNWNJTQIXVJQEH-UHFFFAOYSA-N copper rhodium Chemical compound [Cu].[Rh] HNWNJTQIXVJQEH-UHFFFAOYSA-N 0.000 description 2

- OUFLLVQXSGGKOV-UHFFFAOYSA-N copper ruthenium Chemical compound [Cu].[Ru].[Ru].[Ru] OUFLLVQXSGGKOV-UHFFFAOYSA-N 0.000 description 2

- KUNSUQLRTQLHQQ-UHFFFAOYSA-N copper tin Chemical compound [Cu].[Sn] KUNSUQLRTQLHQQ-UHFFFAOYSA-N 0.000 description 2

- SBYXRAKIOMOBFF-UHFFFAOYSA-N copper tungsten Chemical compound [Cu].[W] SBYXRAKIOMOBFF-UHFFFAOYSA-N 0.000 description 2

- 238000004070 electrodeposition Methods 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- 239000010948 rhodium Substances 0.000 description 2

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 229910016347 CuSn Inorganic materials 0.000 description 1

- 229910002535 CuZn Inorganic materials 0.000 description 1

- 229910000570 Cupronickel Inorganic materials 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 229910008807 WSiN Inorganic materials 0.000 description 1

- OWXLRKWPEIAGAT-UHFFFAOYSA-N [Mg].[Cu] Chemical compound [Mg].[Cu] OWXLRKWPEIAGAT-UHFFFAOYSA-N 0.000 description 1

- UGACIEPFGXRWCH-UHFFFAOYSA-N [Si].[Ti] Chemical compound [Si].[Ti] UGACIEPFGXRWCH-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- IVHJCRXBQPGLOV-UHFFFAOYSA-N azanylidynetungsten Chemical compound [W]#N IVHJCRXBQPGLOV-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000003054 catalyst Substances 0.000 description 1

- 230000003197 catalytic effect Effects 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- RYTYSMSQNNBZDP-UHFFFAOYSA-N cobalt copper Chemical compound [Co].[Cu] RYTYSMSQNNBZDP-UHFFFAOYSA-N 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- QRJOYPHTNNOAOJ-UHFFFAOYSA-N copper gold Chemical compound [Cu].[Au] QRJOYPHTNNOAOJ-UHFFFAOYSA-N 0.000 description 1

- YOCUPQPZWBBYIX-UHFFFAOYSA-N copper nickel Chemical compound [Ni].[Cu] YOCUPQPZWBBYIX-UHFFFAOYSA-N 0.000 description 1

- XPPWAISRWKKERW-UHFFFAOYSA-N copper palladium Chemical compound [Cu].[Pd] XPPWAISRWKKERW-UHFFFAOYSA-N 0.000 description 1

- WBLJAACUUGHPMU-UHFFFAOYSA-N copper platinum Chemical compound [Cu].[Pt] WBLJAACUUGHPMU-UHFFFAOYSA-N 0.000 description 1

- YCKOAAUKSGOOJH-UHFFFAOYSA-N copper silver Chemical compound [Cu].[Ag].[Ag] YCKOAAUKSGOOJH-UHFFFAOYSA-N 0.000 description 1

- TVZPLCNGKSPOJA-UHFFFAOYSA-N copper zinc Chemical compound [Cu].[Zn] TVZPLCNGKSPOJA-UHFFFAOYSA-N 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- WUAPFZMCVAUBPE-UHFFFAOYSA-N rhenium atom Chemical compound [Re] WUAPFZMCVAUBPE-UHFFFAOYSA-N 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- HWEYZGSCHQNNEH-UHFFFAOYSA-N silicon tantalum Chemical compound [Si].[Ta] HWEYZGSCHQNNEH-UHFFFAOYSA-N 0.000 description 1

- WNUPENMBHHEARK-UHFFFAOYSA-N silicon tungsten Chemical compound [Si].[W] WNUPENMBHHEARK-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 239000011135 tin Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/7685—Barrier, adhesion or liner layers the layer covering a conductive structure

- H01L21/76852—Barrier, adhesion or liner layers the layer covering a conductive structure the layer also covering the sidewalls of the conductive structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

- H01L21/2885—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition using an external electrical current, i.e. electro-deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76885—By forming conductive members before deposition of protective insulating material, e.g. pillars, studs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5226—Via connections in a multilevel interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

- H01L23/53238—Additional layers associated with copper layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

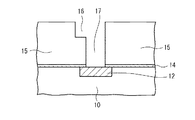

【解決手段】 相互接続構造を製造する方法であって、誘電層に相互接続部を設けるステップと、相互接続部の一部が誘電層の上面よりも上に延出するように誘電層をくぼませるステップと、相互接続部の延出した部分の上に被覆キャップを堆積するステップと、を含む。

【選択図】 図8

Description

Claims (26)

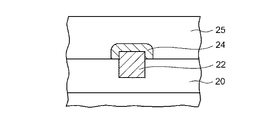

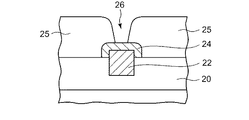

- 相互接続構造を製造する方法であって、

誘電層に相互接続部を設けるステップと、

前記相互接続部の一部が前記誘電層の上面よりも上に延出するように前記誘電層をくぼませるステップと、

前記相互接続部の前記延出した部分の上に被覆キャップを堆積するステップと、

を含む、方法。 - 前記被覆キャップの上に層間誘電層を堆積するステップを更に含む、請求項1に記載の方法。

- 前記層間誘電層にトレンチまたはバイアを形成して、前記トレンチまたは前記バイアの底面が前記被覆キャップの上に位置するようにするステップを更に含む、請求項1に記載の方法。

- 前記相互接続部が寸法幅Wを有する相互接続ラインであり、前記被覆キャップが1.1Wから1.6Wの寸法幅を有する、請求項2に記載の方法。

- 前記被覆キャップが1.2Wから1.4Wの寸法幅を有する、請求項4に記載の方法。

- 前記層間誘電層にバイアを形成して、前記バイアの底面が前記被覆キャップの上に位置するようにするステップを更に含む、請求項4に記載の方法。

- 前記被覆キャップが無電解プロセスによって堆積される、請求項1に記載の方法。

- 前記被覆キャップがニッケルまたはコバルトの一次金属を含む金属合金である、請求項1に記載の方法。

- 前記被覆キャップがCoWPである、請求項1に記載の方法。

- 前記相互接続部が寸法直径Dを有するバイアであり、前記被覆キャップが1.1Dから1.6Dの寸法直径を有する、請求項2に記載の方法。

- 前記被覆キャップが1.2Dから1.4Dの寸法直径を有する、請求項10に記載の方法。

- 前記層間誘電層にトレンチを形成して、前記トレンチの底面が前記被覆キャップの上に位置するようにするステップを更に含む、請求項10に記載の方法。

- 前記被覆キャップが200Åから1500Åの厚さを有する、請求項1に記載の方法。

- 前記相互接続部は延出部分を有し、前記延出部分が15Åから150Åである、請求項1に記載の方法。

- 相互接続構造を製造する方法であって、

誘電層に相互接続ラインを設けるステップと、

前記相互接続ラインの一部が前記誘電層の上面よりも上に延出するように、前記相互接続ラインに隣接する領域において前記誘電層をくぼませるステップと、

前記相互接続ラインの前記延出した部分の上に被覆キャップを堆積するステップと、

前記被覆キャップの上に層間誘電層を堆積するステップと、

前記層間誘電層にバイアを形成して、前記バイアの底面が前記被覆キャップの上に位置するようにするステップと、

を含む、方法。 - 前記相互接続ラインが寸法幅Wを有し、前記キャップが1.1Wから1.6Wの寸法幅を有する、請求項15に記載の方法。

- 相互接続構造を製造する方法であって、

誘電層にバイアを設けるステップと、

前記バイアの一部が前記誘電層の上面よりも上に延出するように、前記バイアに隣接する領域において前記誘電層をくぼませるステップと、

前記バイアの前記延出した部分の上に被覆キャップを堆積するステップと、

前記被覆キャップの上に層間誘電層を堆積するステップと、

前記層間誘電層にトレンチを形成して、前記トレンチの底面が前記被覆キャップの上に位置するようにするステップと、

を含む、方法。 - 前記バイアの直径が寸法直径Dを有し、前記キャップが1.1Dから1.6Dの寸法直径を有する、請求項17に記載の方法。

- 誘電層に配置された相互接続部を含み、前記相互接続部の一部が前記誘電層の表面よりも上に延出し、前記相互接続部の前記延出した部分が被覆キャップによって覆われている、相互接続構造。

- 前記相互接続部が相互接続ラインまたはバイアである、請求項19に記載の相互接続構造。

- 前記相互接続部が寸法幅Wを有する相互接続ラインであり、前記被覆キャップが1.1Wから1.6Wの寸法幅を有する、請求項19に記載の相互接続構造。

- 前記被覆キャップが1.2Wから1.4Wの寸法幅を有する、請求項21に記載の相互接続構造。

- 前記バイアが寸法直径Dを有し、前記被覆キャップが1.1Dから1.6Dの寸法直径を有する、請求項19に記載の相互接続構造。

- 前記被覆キャップが1.2Dから1.4Dの寸法直径を有する、請求項19に記載の相互接続構造。

- 前記被覆キャップが200Åから1500Åの厚さを有する、請求項19に記載の相互接続構造。

- 前記相互接続構造の前記延出した部分が15Åから150Åである、請求項19に記載の相互接続構造。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/034,890 US7105445B2 (en) | 2005-01-14 | 2005-01-14 | Interconnect structures with encasing cap and methods of making thereof |

| PCT/US2005/043465 WO2006088534A1 (en) | 2005-01-14 | 2005-12-02 | Interconnect structures with encasing cap and methods of making thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008527739A true JP2008527739A (ja) | 2008-07-24 |

| JP2008527739A5 JP2008527739A5 (ja) | 2008-10-09 |

Family

ID=36684497

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007551251A Pending JP2008527739A (ja) | 2005-01-14 | 2005-12-02 | 被覆キャップを有する相互接続構造およびその製造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (3) | US7105445B2 (ja) |

| EP (1) | EP1836726A4 (ja) |

| JP (1) | JP2008527739A (ja) |

| CN (1) | CN100517621C (ja) |

| TW (1) | TW200634980A (ja) |

| WO (1) | WO2006088534A1 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7105445B2 (en) * | 2005-01-14 | 2006-09-12 | International Business Machines Corporation | Interconnect structures with encasing cap and methods of making thereof |

| US7317253B2 (en) * | 2005-04-25 | 2008-01-08 | Sony Corporation | Cobalt tungsten phosphate used to fill voids arising in a copper metallization process |

| US7737560B2 (en) * | 2006-05-18 | 2010-06-15 | Infineon Technologies Austria Ag | Metallization layer for a power semiconductor device |

| US7582558B2 (en) * | 2006-07-14 | 2009-09-01 | Intel Corporation | Reducing corrosion in copper damascene processes |

| US20090111263A1 (en) * | 2007-10-26 | 2009-04-30 | Kuan-Neng Chen | Method of Forming Programmable Via Devices |

| US7998864B2 (en) | 2008-01-29 | 2011-08-16 | International Business Machines Corporation | Noble metal cap for interconnect structures |

| US8105937B2 (en) * | 2008-08-13 | 2012-01-31 | International Business Machines Corporation | Conformal adhesion promoter liner for metal interconnects |

| US7803704B2 (en) * | 2008-08-22 | 2010-09-28 | Chartered Semiconductor Manufacturing, Ltd. | Reliable interconnects |

| WO2010049881A1 (en) * | 2008-10-27 | 2010-05-06 | Nxp B.V. | Biocompatible electrodes |

| US20110045171A1 (en) * | 2009-08-19 | 2011-02-24 | International Business Machines Corporation | Multi-Step Method to Selectively Deposit Ruthenium Layers of Arbitrary Thickness on Copper |

| US8809183B2 (en) | 2010-09-21 | 2014-08-19 | International Business Machines Corporation | Interconnect structure with a planar interface between a selective conductive cap and a dielectric cap layer |

| US8492897B2 (en) | 2011-09-14 | 2013-07-23 | International Business Machines Corporation | Microstructure modification in copper interconnect structures |

| US9837356B1 (en) | 2016-06-07 | 2017-12-05 | International Business Machines Corporation | Interconnect structures with enhanced electromigration resistance |

| US10672653B2 (en) * | 2017-12-18 | 2020-06-02 | International Business Machines Corporation | Metallic interconnect structures with wrap around capping layers |

| CN118338662A (zh) * | 2023-01-03 | 2024-07-12 | 长鑫存储技术有限公司 | 半导体结构及其制作方法 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06167308A (ja) * | 1991-06-25 | 1994-06-14 | Nec Corp | 重ね合わせ精度の測定方法 |

| JP2000323479A (ja) * | 1999-05-14 | 2000-11-24 | Sony Corp | 半導体装置およびその製造方法 |

| JP2001210711A (ja) * | 2000-01-25 | 2001-08-03 | Nec Corp | 半導体装置の構造及びその製造方法 |

| JP2003179058A (ja) * | 2001-12-12 | 2003-06-27 | Sony Corp | 半導体装置の製造方法 |

| JP2003243389A (ja) * | 2002-02-15 | 2003-08-29 | Sony Corp | 半導体装置及びその製造方法 |

| JP2004006579A (ja) * | 2002-04-18 | 2004-01-08 | Sony Corp | 記憶装置とその製造方法および使用方法、半導体装置とその製造方法 |

| JP2004158578A (ja) * | 2002-11-05 | 2004-06-03 | Toshiba Corp | 磁気記憶装置及びその製造方法 |

| JP2005136003A (ja) * | 2003-10-28 | 2005-05-26 | Oki Electric Ind Co Ltd | 半導体装置の配線構造及びその製造方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5300813A (en) * | 1992-02-26 | 1994-04-05 | International Business Machines Corporation | Refractory metal capped low resistivity metal conductor lines and vias |

| WO1996002070A2 (en) * | 1994-07-12 | 1996-01-25 | National Semiconductor Corporation | Integrated circuit comprising a trench isolation structure and an oxygen barrier layer and method for forming the integrated circuit |

| JP2985692B2 (ja) * | 1994-11-16 | 1999-12-06 | 日本電気株式会社 | 半導体装置の配線構造及びその製造方法 |

| US6294799B1 (en) | 1995-11-27 | 2001-09-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of fabricating same |

| US5695810A (en) * | 1996-11-20 | 1997-12-09 | Cornell Research Foundation, Inc. | Use of cobalt tungsten phosphide as a barrier material for copper metallization |

| US6215129B1 (en) | 1997-12-01 | 2001-04-10 | Vsli Technology, Inc. | Via alignment, etch completion, and critical dimension measurement method and structure |

| US6103625A (en) | 1997-12-31 | 2000-08-15 | Intel Corporation | Use of a polish stop layer in the formation of metal structures |

| US6157081A (en) | 1999-03-10 | 2000-12-05 | Advanced Micro Devices, Inc. | High-reliability damascene interconnect formation for semiconductor fabrication |

| US6391669B1 (en) | 2000-06-21 | 2002-05-21 | International Business Machines Corporation | Embedded structures to provide electrical testing for via to via and interface layer alignment as well as for conductive interface electrical integrity in multilayer devices |

| TW463307B (en) | 2000-06-29 | 2001-11-11 | Mosel Vitelic Inc | Manufacturing method of dual damascene structure |

| US6461963B1 (en) * | 2000-08-30 | 2002-10-08 | Micron Technology, Inc. | Utilization of disappearing silicon hard mask for fabrication of semiconductor structures |

| JP4169950B2 (ja) | 2001-05-18 | 2008-10-22 | Necエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US6605874B2 (en) | 2001-12-19 | 2003-08-12 | Intel Corporation | Method of making semiconductor device using an interconnect |

| US20030116439A1 (en) * | 2001-12-21 | 2003-06-26 | International Business Machines Corporation | Method for forming encapsulated metal interconnect structures in semiconductor integrated circuit devices |

| US6764919B2 (en) * | 2002-12-20 | 2004-07-20 | Motorola, Inc. | Method for providing a dummy feature and structure thereof |

| FR2857719B1 (fr) * | 2003-07-17 | 2006-02-03 | Snecma Moteurs | Dispositif de vanne a longue course de regulation |

| US6838355B1 (en) * | 2003-08-04 | 2005-01-04 | International Business Machines Corporation | Damascene interconnect structures including etchback for low-k dielectric materials |

| US7105445B2 (en) * | 2005-01-14 | 2006-09-12 | International Business Machines Corporation | Interconnect structures with encasing cap and methods of making thereof |

-

2005

- 2005-01-14 US US11/034,890 patent/US7105445B2/en not_active Expired - Fee Related

- 2005-12-02 EP EP05852629A patent/EP1836726A4/en not_active Withdrawn

- 2005-12-02 JP JP2007551251A patent/JP2008527739A/ja active Pending

- 2005-12-02 CN CN200580046544.0A patent/CN100517621C/zh not_active Expired - Fee Related

- 2005-12-02 WO PCT/US2005/043465 patent/WO2006088534A1/en active Application Filing

-

2006

- 2006-01-04 TW TW095100294A patent/TW200634980A/zh unknown

- 2006-08-14 US US11/503,259 patent/US7488677B2/en not_active Expired - Fee Related

-

2008

- 2008-08-27 US US12/199,407 patent/US7902061B2/en not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06167308A (ja) * | 1991-06-25 | 1994-06-14 | Nec Corp | 重ね合わせ精度の測定方法 |

| JP2000323479A (ja) * | 1999-05-14 | 2000-11-24 | Sony Corp | 半導体装置およびその製造方法 |

| JP2001210711A (ja) * | 2000-01-25 | 2001-08-03 | Nec Corp | 半導体装置の構造及びその製造方法 |

| JP2003179058A (ja) * | 2001-12-12 | 2003-06-27 | Sony Corp | 半導体装置の製造方法 |

| JP2003243389A (ja) * | 2002-02-15 | 2003-08-29 | Sony Corp | 半導体装置及びその製造方法 |

| JP2004006579A (ja) * | 2002-04-18 | 2004-01-08 | Sony Corp | 記憶装置とその製造方法および使用方法、半導体装置とその製造方法 |

| JP2004158578A (ja) * | 2002-11-05 | 2004-06-03 | Toshiba Corp | 磁気記憶装置及びその製造方法 |

| JP2005136003A (ja) * | 2003-10-28 | 2005-05-26 | Oki Electric Ind Co Ltd | 半導体装置の配線構造及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20070054489A1 (en) | 2007-03-08 |

| CN101099235A (zh) | 2008-01-02 |

| US7488677B2 (en) | 2009-02-10 |

| US7105445B2 (en) | 2006-09-12 |

| WO2006088534A1 (en) | 2006-08-24 |

| US20060160349A1 (en) | 2006-07-20 |

| EP1836726A4 (en) | 2010-07-28 |

| US20080318415A1 (en) | 2008-12-25 |

| EP1836726A1 (en) | 2007-09-26 |

| TW200634980A (en) | 2006-10-01 |

| US7902061B2 (en) | 2011-03-08 |

| CN100517621C (zh) | 2009-07-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7488677B2 (en) | Interconnect structures with encasing cap and methods of making thereof | |

| EP2020027B1 (en) | Structure and method for creating reliable via contacts for interconnect applications | |

| US5969422A (en) | Plated copper interconnect structure | |

| US6417094B1 (en) | Dual-damascene interconnect structures and methods of fabricating same | |

| US20170263721A1 (en) | Copper-filled trench contact for transistor performance improvement | |

| US6147404A (en) | Dual barrier and conductor deposition in a dual damascene process for semiconductors | |

| US8124524B2 (en) | Methods of forming metal interconnection structures | |

| US6291082B1 (en) | Method of electroless ag layer formation for cu interconnects | |

| US7879720B2 (en) | Methods of forming electrical interconnects using electroless plating techniques that inhibit void formation | |

| US6998342B2 (en) | Electronic device manufacturing method | |

| KR100798235B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US8053894B2 (en) | Surface treatment of metal interconnect lines | |

| JP4130621B2 (ja) | 半導体装置およびその製造方法 | |

| JP5089850B2 (ja) | 半導体装置 | |

| TW200301524A (en) | Method for improving electromigration performance of metallization features through multiple depositions of binary alloys | |

| US20060228934A1 (en) | Conductive materials for low resistance interconnects and methods of forming the same | |

| US6509257B1 (en) | Semiconductor device and process for making the same | |

| KR20070066298A (ko) | 반도체 소자의 금속배선 및 그의 제조방법 | |

| KR20030060908A (ko) | 반도체 장치 및 그 제조 방법 | |

| KR100462759B1 (ko) | 확산 장벽층을 갖는 금속 배선 및 그 제조 방법 | |

| KR20010076493A (ko) | 다마신 공정으로 형성된 반도체 소자의 배선구조 | |

| KR100195239B1 (ko) | 반도체장치의 금속배선층 구조 및 그 형성방법 | |

| KR20050048170A (ko) | 반도체 장치의 구리 배선 형성 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080822 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080822 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111027 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111101 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120119 |

|

| RD12 | Notification of acceptance of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7432 Effective date: 20120119 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20120120 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120313 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20130625 |