JP2007281114A - 半導体装置の製造方法および半導体装置 - Google Patents

半導体装置の製造方法および半導体装置 Download PDFInfo

- Publication number

- JP2007281114A JP2007281114A JP2006103809A JP2006103809A JP2007281114A JP 2007281114 A JP2007281114 A JP 2007281114A JP 2006103809 A JP2006103809 A JP 2006103809A JP 2006103809 A JP2006103809 A JP 2006103809A JP 2007281114 A JP2007281114 A JP 2007281114A

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- film

- layer

- semiconductor device

- conductive layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/011—Manufacture or treatment of electrodes ohmically coupled to a semiconductor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/41—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes characterised by their conductive parts

- H10W20/425—Barrier, adhesion or liner layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/20—Dry etching; Plasma etching; Reactive-ion etching

- H10P50/24—Dry etching; Plasma etching; Reactive-ion etching of semiconductor materials

- H10P50/242—Dry etching; Plasma etching; Reactive-ion etching of semiconductor materials of Group IV materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/031—Manufacture or treatment of conductive parts of the interconnections

- H10W20/032—Manufacture or treatment of conductive parts of the interconnections of conductive barrier, adhesion or liner layers

- H10W20/055—Manufacture or treatment of conductive parts of the interconnections of conductive barrier, adhesion or liner layers by formation methods other than physical vapour deposition [PVD], chemical vapour deposition [CVD] or liquid deposition

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/074—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H10W20/076—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers in via holes or trenches

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/093—Manufacture or treatment of dielectric parts thereof by modifying materials of the dielectric parts

- H10W20/096—Manufacture or treatment of dielectric parts thereof by modifying materials of the dielectric parts by contacting with gases, liquids or plasmas

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/45—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes characterised by their insulating parts

- H10W20/47—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes characterised by their insulating parts comprising two or more dielectric layers having different properties, e.g. different dielectric constants

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

【課題】本発明は、400℃以上の高温処理をせずに、ドライエッチングによるダメージを補修し、層間絶縁膜からの脱ガスを防止する半導体装置の製造方法および半導体装置を提供する。

【解決手段】基板11上に設けられた下層配線15上および層間絶縁膜12上に、層間絶縁膜17を形成し、層間絶縁膜17に配線溝19と、配線溝19の底部に連通し、下層配線15に達する接続孔18を形成する。次に、層間絶縁膜17に炭素とシリコンを含有するガスを用いたプラズマ処理を行うことで、配線溝19および接続孔18の側壁に露出された層間絶縁膜17の表面側に緻密層31とSixCy膜からなるシール層32を形成する。次いで、プラズマ処理後の配線溝19および接続孔18の内壁を覆う状態で形成されるバリア膜20を介して、接続孔18にヴィア21を形成するとともに配線溝19に上層配線22を形成することを特徴とする半導体装置の製造方法および半導体装置である。

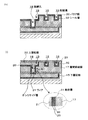

【選択図】図2

【解決手段】基板11上に設けられた下層配線15上および層間絶縁膜12上に、層間絶縁膜17を形成し、層間絶縁膜17に配線溝19と、配線溝19の底部に連通し、下層配線15に達する接続孔18を形成する。次に、層間絶縁膜17に炭素とシリコンを含有するガスを用いたプラズマ処理を行うことで、配線溝19および接続孔18の側壁に露出された層間絶縁膜17の表面側に緻密層31とSixCy膜からなるシール層32を形成する。次いで、プラズマ処理後の配線溝19および接続孔18の内壁を覆う状態で形成されるバリア膜20を介して、接続孔18にヴィア21を形成するとともに配線溝19に上層配線22を形成することを特徴とする半導体装置の製造方法および半導体装置である。

【選択図】図2

Description

本発明は、半導体装置の製造方法および半導体装置に関し、さらに詳しくは、層間絶縁膜として低誘電率膜を用いて多層配線構造を形成するのに好適な半導体装置の製造方法および半導体装置に関する。

近年、半導体装置の高集積化、微細化に伴い、特に、RC遅延の低減が必要となっている。このため、配線材料としては、従来のアルミニウム(Al)に変えて、比抵抗率の低い銅(Cu)を用いると共に、絶縁膜材料としては、従来から用いられている酸化シリコン(SiO2)よりも比誘電率の低い低誘電率(low−k)膜を用いることが考えられている。低誘電率(Low−k)膜としては、比誘電率k<3.0の絶縁膜の研究が進められており、このような低誘電率膜には、例えば、ハイドロゲンシルセスシロキサン(hydrogen silsesquioxane(HSQ)、メチルシルセスキオキサン(methyl silsesquioxane(MSQ)、芳香族含有有機絶縁膜などがある。

なかでも、近年、デュアルダマシン加工が容易であることから、芳香族含有有機絶縁膜とポリメチルシロキサン(poly methyl siloxane)またはMSQからなる無機絶縁膜とを組合わせたハイブリッド構造が広く用いられている。45nmあるいは32nm世代を考えた場合、ヴィア層間絶縁膜としては比誘電率2.5以下の膜が考えられている。

ここで、層間絶縁膜にMSQの多孔質膜(ポーラスMSQ膜)を用いた場合のデュアルダマシン法による多層配線構造の製造方法の一例について、図7〜図8を用いて説明する。図7(a)に示すように、シリコン基板からなる半導体基板11上のSiO2からなる層間絶縁膜12に設けられた配線溝13に、タンタル(Ta)からなるバリア膜14を介してCuからなる下層配線15が設けられている。この下層配線15上および層間絶縁膜12上を覆う状態で、炭窒化シリコン(SiCN)からなるエッチングストッパー膜16を形成した後、エッチングストッパー膜16上に、層間絶縁膜17として、比誘電率が2.5以下のポーラスMSQ膜からなる低誘電率膜を形成する。

次に、図7(b)に示すように、通常のリソグラフィ技術により、層間絶縁膜17上に接続孔パターンの設けられたレジストパターンRを形成する。続いて、図7(c)に示すように、レジストパターンR(前記図7(b)参照)をマスクに用いたプラズマエッチングにより、層間絶縁膜17にエッチングストッパー膜16に達する接続孔18を形成する。その後、レジストパターンRを除去する。

次いで、図7(d)に示すように、通常のリソグラフィ技術により、接続孔18を埋め込む状態で、層間絶縁膜17上に、配線溝パターンの設けられたレジストパターンR’を形成する。続いて、図8(e)に示すように、レジストパターンR’(前記図7(d)参照)をマスクに用いたエッチングにより、層間絶縁膜17に接続孔18に連通する状態の配線溝19を形成する。その後、レジストパターンR’を除去する。

次に、図8(f)に示すように、接続孔18の底部に露出されたエッチングストッパー膜16を除去することで、下層配線15の表面を露出する。その後、有機系洗浄液にて、露出した下層配線15の表面を洗浄する。

次いで、図8(g)に示すように、上記配線溝19および接続孔18の内壁を覆う状態で、層間絶縁膜17上にTaからなるバリア膜20を形成する。続いて、図8(h)に示すように、バリア膜20の形成された接続孔18および配線溝19を埋め込む状態で、バリア膜20上にCuからなる導電膜(図示省略)を形成する。その後、熱処理を行うことで、導電膜中のCuの結晶成長を行う。次いで、層間絶縁膜17の表面が露出するまで、化学的機械的研磨(Chemical Mechanical Polishing(CMP))法により、上記導電膜およびバリア膜20を除去することで、接続孔18にヴィア21を形成するとともに、配線溝19に上層配線22を形成する。

ここで、上述したように、層間絶縁膜17がポーラスMSQ等、比誘電率2.5以下の低誘電率膜で形成されている場合には、層間絶縁膜17の膜密度が粗であることから、エッチング加工時に層間絶縁膜17がプラズマダメージを受け易い。

そこで、上記低誘電率膜のエッチングによるダメージ対策として、層間絶縁膜にエッチング加工を行った後に、テトラメチルシクロテトラシロキサン(Tetra-methylcyclotetrasiloxane(TMCTS))を処理雰囲気に供給し、アニール処理を行うことで、エッチング加工により露出した側壁を補修するダメージ回復技術の研究が報告されている(例えば、非特許文献1参照)。

Y.Oku,et al., Novel Self-Assembled Ultra-Low-k Porous Silica Films with High Mechanical Strength for 45nm BEOL Technology,「International ELECTRON DEVICE Meeting」(米)IEEE,2003年

しかし、上述したような方法により、十分な補修効果を得るためには、400℃程度の高温処理が必要であり、特に、層間絶縁膜に耐熱性の低い有機材料膜を含む場合には、デバイス信頼性を考えると許容し難い条件である。例えば、層間絶縁膜中からの脱ガス促進によるバリア膜の剥がれや密着性劣化、デュアルダマシン構造のヴィア部分の吸い上がりによるボイド形成により、初期特性が劣化してしまう可能性が考えられる。

また、十分な補修効果が得られない場合には、層間絶縁膜が吸湿してしまう。特に、比誘電率低減のために、ポアが設けられている多孔質膜は、ポアの存在が吸湿を加速し、エッチング加工後の洗浄処理により、ポアがあることで薬液の染みこみパスが形成されてしまう。

このため、図9に示すように、層間絶縁膜17からの脱ガスにより、バリア膜20が酸化し易い、という問題がある。また、特にアスペクト比の高い接続孔18の内壁には、成膜ガスが届きにくいため、バリア膜20が薄く形成されることから、バリア膜20の酸化が顕著に生じ易い。このため、バリア膜20の酸化によるバリア性劣化によりヴィア21から層間絶縁膜17中への導電材料(メタル)の染み出しMが生じる。また、層間絶縁膜17とバリア膜20との密着性も劣化するため、ヴィア21中にボイドVが発生し易く、ストレスマイグレーション(Stress Migration(SM))、エレクトロマイグレーション(Electro- Migration(EM))等の信頼性不良が誘発される。さらには、バリア膜20の酸化によりヴィア21が酸化されることで、高抵抗化を引き起こしてしまう。

以上のことから、本発明は、400℃以上の高温処理をせずに、ドライエッチングによるダメージを修復し、層間絶縁膜からの脱ガスを防止する半導体装置の製造方法および半導体装置を提供することを目的とする。

上記課題を解決するために、本発明の半導体装置の製造方法は、次のような工程を順次行うことを特徴としている。まず、第1工程では、表面側に第1導電層が設けられた基板上に絶縁膜を形成し、ドライエッチングにより絶縁膜に凹部を形成する工程を行う。次に、第2工程では、絶縁膜に、炭素またはシリコンを含有するガスを用いたプラズマ処理を行う。次いで、第3工程では、プラズマ処理後の凹部に第2導電層を埋め込み形成する工程を行う。

このような半導体装置の製造方法によれば、ドライエッチングにより凹部を形成した後の絶縁膜に、炭素またはシリコンを含有するガスを用いたプラズマ処理を行うことから、凹部の内壁に付着した脱ガスの要因となるOH基が脱離し、凹部の内壁に露出された絶縁膜の表面側が緻密化されて緻密層が形成される。これにより、400℃以上の熱処理を行わなくても、ドライエッチングによる凹部の内壁に露出した絶縁膜へのダメージが修復され、絶縁膜からの脱ガスが抑制される。特に、炭素を含有するガスを用いたプラズマ処理を行う場合には、凹部の側壁に露出したダングリングボンドが炭素含有基で終端されて、上記緻密層の表面に炭素を含有するシール層が形成されることで、絶縁膜からの脱ガスが顕著に抑制される。このため、凹部の内壁を覆う状態で、第2導電層から絶縁膜への導電材料の拡散を防止するバリア膜を形成する場合には、バリア膜の酸化が抑制される。これにより、バリア膜の酸化によるバリア性劣化が抑制され、絶縁膜への導電材料の染み出しが防止されることから、第2導電層のショートを防止することができる。また、バリア膜の酸化に起因するバリア膜と絶縁膜との密着性低下が抑制されるため、第2導電層中のボイドの発生が防止され、SM、EMの信頼性不良が防止される。さらには、バリア膜の酸化による第2導電層の酸化が防止されるため、第2導電層の高抵抗化が防止される。

また、本発明の第1の半導体装置は、表面側に第1導電層が形成された基板と、基板上に設けられた絶縁膜と、絶縁膜に第1導電層に達する状態で設けられた凹部に埋め込み形成された第2導電層とを備えた半導体装置において、絶縁膜の第2導電層との界面側には、絶縁膜が緻密化された緻密層が設けられており、緻密層と第2導電層との間には、炭素を含有するシール層が設けられていることを特徴としている。

このような第1の半導体装置によれば、絶縁膜の第2導電層との界面側には、緻密層が設けられるとともに、緻密層と第2導電層との間に炭素を含有するシール層が設けられていることで、絶縁膜からの脱ガスが顕著に抑制される。これにより、凹部の内壁を覆う状態で、第2導電層から絶縁膜への導電材料の拡散を防止するバリア膜が設けられている場合には、バリア膜の酸化が抑制される。これにより、バリア膜の酸化によるバリア性劣化が抑制され、絶縁膜への導電材料の染み出しが防止されることから、第2導電層のショートを防止することができる。また、バリア膜の酸化に起因するバリア膜と絶縁膜との密着性低下が抑制されるため、第2導電層中のボイドの発生が防止され、SM、EMの信頼性不良が防止される。さらには、バリア膜の酸化による第2導電層の酸化が防止されるため、第2導電層の高抵抗化が防止される。

また、本発明の第2の半導体装置は、表面側に第1導電層が形成された基板と、基板上に設けられた絶縁膜と、絶縁膜に第1導電層に達する状態で設けられた凹部に埋め込み形成された第2導電層とを備えた半導体装置において、絶縁膜の第2導電層との界面側には、絶縁膜が緻密化された緻密層が設けられており、第1導電層の第2導電層との界面側には、シリサイド層が設けられていることを特徴としている。

このような第2の半導体装置によれば、絶縁膜の第2導電層との界面側には、緻密層が設けられていることで、絶縁膜からの脱ガスが抑制される。これにより、凹部の内壁を覆う状態で、第2導電層から絶縁膜への導電材料の拡散を防止するバリア膜が設けられている場合には、バリア膜の酸化が抑制される。これにより、バリア膜の酸化によるバリア性劣化が抑制され、絶縁膜への導電材料の染み出しが防止されることから、第2導電層のショートを防止することができる。また、バリア膜の酸化に起因するバリア膜と絶縁膜との密着性低下が抑制されるため、第2導電層中のボイドの発生が防止され、SM、EMの信頼性不良が防止される。さらには、バリア膜の酸化による第2導電層の酸化が防止されるため、第2導電層の高抵抗化が防止される。また、第2導電層の第1導電層との界面側にシリサイド層が設けられることで、SM耐性、EM耐性を向上させることができる。

以上、説明したように、本発明の半導体装置の製造方法およびこれによって得られる半導体装置によれば、第2導電層のショートを防止できるとともに、SM耐性、EM耐性を向上させることができ、第2導電層の高抵抗化を防止することができる。したがって、配線構造の信頼性を向上させることができることから、高性能なCMOSデバイスが実現可能であり、コンピュータ、ゲーム機、モバイル商品等の性能を著しく向上させることができる。

以下、本発明の実施の形態を図面に基づいて詳細に説明する。

(第1実施形態)

本発明の半導体装置の製造方法に係わる実施の形態の一例を、図1〜図3の製造工程断面図によって説明する。本実施形態では、デュアルダマシン法を用いたCuと低誘電率膜とからなる多層配線構造の形成方法について説明する。なお、背景技術で説明した半導体装置の製造方法と同様の構成には同一の番号を付して説明する。

本発明の半導体装置の製造方法に係わる実施の形態の一例を、図1〜図3の製造工程断面図によって説明する。本実施形態では、デュアルダマシン法を用いたCuと低誘電率膜とからなる多層配線構造の形成方法について説明する。なお、背景技術で説明した半導体装置の製造方法と同様の構成には同一の番号を付して説明する。

図1(a)に示すように、トランジスタ等の半導体素子が形成された半導体基板11上に、例えばSiO2からなる層間絶縁膜12が設けられている。この層間絶縁膜12に設けられた配線溝13には、例えばTaからなるバリア膜14を介して例えばCuからなる下層配線15(第1導電層)が60nmの厚さで形成されている。ここまでの構成が請求項の基板に相当する。

次に、下層配線15上を含む層間絶縁膜12上に、プラズマ化学的気相成長(Plasma Enhanced Chemical Vapor Deposition(PE−CVD))法により、例えばSiCNからなるエッチングストッパー膜16を30nmの膜厚で形成する。

次に、エッチングストッパー膜16上に、層間絶縁膜17を形成する。この場合には、例えば塗布法またはCVD法により、MSQポーラス膜からなる層間絶縁膜17を250nmの膜厚で形成する。このMSQポーラス膜の比誘電率は2.5以下である。ここで、層間絶縁膜17としては、酸化シリコンよりも比誘電率の低い低誘電率膜で形成されることが好ましく、例えば、ポリメチルシラン、HSQ、MSQ等の無機絶縁膜、または、ポリアリールエーテル(PAE)等の芳香族含有有機絶縁膜がある。特に、層間絶縁膜17がこれらの低誘電率膜の多孔質膜を含む場合には、非多孔質膜と比較して、膜密度が粗になることから、層間絶縁膜17の比誘電率が低減され、配線間容量を低減することができるため、好ましい。

続いて、図1(b)に示すように、層間絶縁膜17上に、例えば化学増幅型ArFレジストを塗布した後、通常のリソグラフィ技術により、このレジストに例えば直径60nmの接続孔パターンを形成することで、レジストパターンRを形成する。

次に、図1(c)に示すように、レジストパターンR(前記図1(b)参照)をマスクとし、フロロカーボン(CF)系ガスを用いたプラズマエッチングにより、層間絶縁膜17にエッチングストッパー膜16に達する状態の接続孔18を形成する。ここで、層間絶縁膜17は、MSQポーラス膜で形成されることから、メチル基を多く含んだ膜構造となっており、接続孔18の加工時のプラズマにより、接続孔18の側壁に露出したメチル基が破壊される。このため、このダメージを受けた部分は、ダングリングボンドが露出され、吸湿し易くなっている。その後、O2系ガスを用いたアッシング処理により、残存したレジストパターンRを除去する。このアッシング処理は、層間絶縁膜17へのダメージを最小限に抑えるため、6.7Pa以下の低圧力条件下で行うことが好ましく、ここでは、例えば2.7Paで行うこととする。

次に、図1(d)に示すように、接続孔18を埋め込む状態で、層間絶縁膜17上に、再び化学増幅型ArFレジストを塗布し、通常のリソグラフィ技術により、配線溝パターンを有するレジストパターンR’を形成する。

続いて、図2(e)に示すように、レジストパターンR’(前記図1(d)参照)をマスクとし、CF系ガスを用いたドライエッチングにより、層間絶縁膜17に、接続孔18に連通する深さ140nmの配線溝19を形成する。このドライエッチングによっても、プラズマにより、配線溝19の側壁に露出したメチル基が破壊される。このため、層間絶縁膜17におけるこのダメージを受けた部分は、ダングリングボンドが露出され、吸湿し易くなる。その後、O2系ガスを用いた低圧力条件下でのアッシングにより、このレジストパターンR’を除去する。

次に、図2(f)に示すように、CF系ガスを用いたドライエッチングにより、接続孔18の底部に露出されたエッチングストッパー膜16をエッチング除去し、下層配線15を露出する。ここで、配線溝19と配線溝19の底部に連通する接続孔18とが請求項の凹部に相当する。続いて、有機系洗浄液にて露出した下層配線15の表面を洗浄する。これにより、配線溝19および接続孔18の側壁に露出された絶縁膜が吸湿し、この側壁に露出されたダングリングボンドに脱ガスに起因するOH基が付着する。

次いで、図2(g)に示すように、層間絶縁膜17に、炭素(C)とシリコン(Si)の両方を含むガスを用いたプラズマ処理を行う。ここでは、上記ガスとして、ジメチルフェニルシラン(Di Methyl Phenyl Silane(DMPS))を用いることとする。これにより、配線溝19または接続孔18の側壁に付着した脱ガスの要因となるOH基が脱離し、領域Aの要部拡大図に示すように、層間絶縁膜17の表面側に層間絶縁膜17が緻密化された緻密層31が形成される。また、上記ガスがCを含むことで、配線溝19または接続孔18の側壁に露出したダングリングボンドが炭素含有基で終端され、緻密層31が設けられた配線溝19および接続孔18の内壁を覆う状態で、層間絶縁膜17上に、炭素を含むSixCy膜からなるシール層32が形成される。これにより、ドライエッチングによる配線溝19または接続孔18の側壁に露出した層間絶縁膜17へのダメージが修復され、層間絶縁膜17の吸湿が抑制されるとともに、層間絶縁膜17に残存した水分の脱ガスが防止される。また、接続孔18の底部の下層配線15上を覆うシール層32は、このプラズマ処理の熱により下層配線15の表面側に拡散されて、シリサイド層Sが形成される。これにより、SM耐性およびEM耐性が向上する。

ここで、上記プラズマ処理の処理条件を制御することで、上記シール層32の膜厚を0.5nm以下の極薄膜にすることが好ましく、極薄膜とすることで、層間絶縁膜17の比誘電率を上昇させることがなく、下層配線15の表面側にシリサイド層Sが設けられることによるヴィアの抵抗値の上昇を許容範囲内に抑えることができる。

このプラズマ処理の処理条件の一例としては、DMPSからなるプリカーサ種と、ヘリウム(He)からなるキャリアガスをガス流量比(DMPS/He=500/1000(ml/min))となるように供給し、基盤RFバイアスパワーを150W、圧力を670Pa、温度を350℃、処理時間を15secに設定する。

なお、ここでは、CとSiの両方を含むガスとして、DMPSを用いることとしたが、本発明はこれに限定されることなく、テトラメチルシクロテトラシロキサン(TMCTS)やオクタメチルシクロテトラシロキサン(OMCTS)、トリメチルシラン(3MS)、テトラメチルシラン(4MS)等を用いてもよい。ただし、DMPSのように分子内にベンゼン環等の環状構造を有する化合物を供給することで、環状構造が立体障害となり、成膜レートを低減することが容易であることから、シール層32を0.5nm以下の膜厚で再現性よく成膜することが可能であるため、好ましい。

なお、ここでは、CとSiの両方を含有するガスを用いたプラズマ処理を行うこととしたが、本発明はこれに限定されず、CまたはSiを含むガスを用いたプラズマ処理であればよく、他の構成元素として、水素(H)、酸素(O)、窒素(N)等を含んでいてもよい。ここで、Cを含みSiを含まないC含有ガスとしては、例えばメタン(CH4)ガスおよびエチレン(C2H4)ガスが挙げられ、Siを含みCを含まないSi含有ガスとしては、例えばシラン(SiH4)ガスが挙げられる。

ここで、上記C含有ガスを用いたプラズマ処理を行う場合には、配線溝19および接続孔18の側壁に付着したOH基が脱離し、層間絶縁膜17の表面側に緻密層31が形成される。また、配線溝19および接続孔18の側壁に露出したダングリングボンドが炭素含有基で終端されるとともに、緻密層31が設けられた配線溝19および接続孔18の内壁を覆う状態で、層間絶縁膜17上にCを含有するシール層32が形成される。この場合には、接続孔18の底部に露出された下層配線15上のシール層32はシリサイド化されずに残存するが、0.5nm以下の極薄膜であることから、除去しなくても後述するヴィアの抵抗値は許容範囲内に抑えられ、配線信頼性は維持される。

また、上記Si含有ガスを用いたプラズマ処理を行う場合には、配線溝19および接続孔18の側壁に付着したOH基が脱離し、層間絶縁膜17の表面側に緻密層31が形成される。この場合には、接続孔18の底部に露出された下層配線15上のシール層32は、プラズマ処理の際の熱処理により、下層配線15の表面側に拡散し、シリサイド層Sとなる。これにより、SM耐性およびEM耐性が向上する。

以上のようにしてシール層32を形成した後、図3(h)に示すように、例えばスパッタリング法またはCVD法により、配線溝19および接続孔18の内壁を覆う状態で、シール層32上に、例えばTaからなるバリア膜20を7nmの膜厚で形成する。

その後、図3(i)に示すように、例えばスパッタリング法またはCVD法により、バリア膜20上に例えばCuからなるシード層(図示省略)を45nmの膜厚で形成した後、電界メッキ(ECP)法またはCVD法により、配線溝19および接続孔18を埋め込む状態で、バリア膜20上に例えばCuからなる導電膜(図示省略)を成膜し、Cuを結晶成長させるためのアニール処理を250℃で90秒間行う。

続いて、例えばCMP法により、層間絶縁膜17の表面が露出するまで、導電膜およびバリア膜20ならびにシール層32を除去することで、接続孔18にヴィア21(第2導電層)を形成するとともに、配線溝19に上層配線22(第2導電層)を形成する。これにより、下層配線15のヴィア21との界面側にシリサイド層Sが設けられた状態となる。その後、上層配線22上を含む層間絶縁膜17上に例えばSiCNからなるエッチングストッパー膜23を形成する。

なお、本実施形態においては、上記CMP法によりシール層32を除去することとしたが、シール層32は除去しなくてもよい。また、ここでは、下層配線15、ヴィア21、上層配線22をCuで形成する例について説明したが、本発明はこれに限定されず、Cuの他に、銀(Ag)、金(Au)、アルミニウム(Al)またはこれらの合金であってもよい。

この後の工程は、図1(a)を用いて説明した層間絶縁膜17の形成工程から、図3(i)を用いて説明したエッチングストッパー膜23の形成工程までを、繰り返して行うことで多層配線構造を製造する。

このような半導体装置の製造方法および半導体装置によれば、ドライエッチングにより配線溝19および接続孔18を形成した後の層間絶縁膜17に、DMPSからなるガスを用いたプラズマ処理を行うことから、領域Aの要部拡大図に示すように、配線溝19および接続孔18の側壁に付着したOH基が脱離し、層間絶縁膜17の表面側が緻密化されて緻密層31が形成される。また、配線溝19および接続孔18の側壁に露出したダングリングボンドが炭素含有基で終端され、緻密層31の表面にSixCy膜からなるシール層32が形成される。これにより、400℃以上の熱処理を行わなくても、ドライエッチングによる層間絶縁膜17へのダメージが改善され、層間絶縁膜17からの脱ガスが抑制される。よって、バリア膜20の酸化が抑制される。

これにより、バリア膜20の酸化によるバリア性劣化が抑制され、層間絶縁膜17への導電材料の染み出しが防止されることから、ヴィア21のショートを防止することができる。また、バリア膜20と層間絶縁膜17との密着性低下が抑制されるため、ヴィア21中のボイドの発生が防止され、SM耐性、EM耐性の劣化が防止される。さらには、バリア膜20の酸化によるヴィア21の酸化が防止されるため、ヴィア21の高抵抗化が防止される。したがって、配線構造の信頼性を向上させることができることから、高性能なCMOSデバイスが実現可能であり、コンピュータ、ゲーム機、モバイル商品等の性能を著しく向上させることができる。

さらに、本実施形態によれば、下層配線15のヴィア21との界面側にシリサイド層Sが形成されることで、SM耐性およびEM耐性を向上させることができる。

なお、上記実施形態においては、図2(g)を用いて説明したように、接続孔18底部のエッチングストッパー膜16を除去し、下層配線15を露出させた工程の後、バリア膜20を形成する工程の前に、DMPSを用いたプラズマ処理を行う例について説明したが、本発明は、配線溝19または接続孔18を形成する工程の後、バリア膜20を形成する工程の前であれば、どの工程でプラズマ処理を行ってもよい。

例えば、図1(c)を用いて説明した層間絶縁膜17にエッチングストッパー膜16に達する状態の接続孔18を形成する工程の後で、図1(d)を用いて説明したレジストパターンR’を形成する工程の前に上記プラズマ処理を行ってもよく、図2(e)を用いて説明した層間絶縁膜17に配線溝19を形成する工程の後で、図2(f)を用いて説明した接続孔18底部のエッチングストッパー膜16を除去する工程の前に行ってもよい。また、上述した各工程の間の2工程以上で上記プラズマ処理を行い、複数回の処理を行ってもよい。ただし、アスペクト比の高い接続孔18の側壁には、バリア膜20が形成され難いため、接続孔18の側壁を覆うバリア膜20の酸化は生じ易いことから、層間絶縁膜17に接続孔18が設けられた状態で、上記プラズマ処理を行うことが好ましい。さらに、接続孔18の底部に下層配線15が露出された状態で、上記プラズマ処理を行うことで、下層配線15の表面側にはシリサイド層Sが形成されるため、好ましい。

(第2実施形態)

次に、本発明の半導体装置の製造方法にかかる第2の実施形態として、層間絶縁膜が無機絶縁膜と有機絶縁膜とを順次積層してなるハイブリット構造で構成された例について、図4〜図6の製造工程断面図を用いて説明する。なお、第1実施形態と同様の構成には同一の番号を付して説明し、詳細な説明は省略する。また、図1(a)を用いて説明した下層配線15上を含む層間絶縁膜12上にエッチングストッパー膜16を形成する工程までは、第1実施形態と同様であることとする。

次に、本発明の半導体装置の製造方法にかかる第2の実施形態として、層間絶縁膜が無機絶縁膜と有機絶縁膜とを順次積層してなるハイブリット構造で構成された例について、図4〜図6の製造工程断面図を用いて説明する。なお、第1実施形態と同様の構成には同一の番号を付して説明し、詳細な説明は省略する。また、図1(a)を用いて説明した下層配線15上を含む層間絶縁膜12上にエッチングストッパー膜16を形成する工程までは、第1実施形態と同様であることとする。

まず、図4(a)に示すように、エッチングストッパー膜16上に層間絶縁膜17’として、無機絶縁膜である例えばポーラスMSQからなる第1絶縁層17a’を100nmの膜厚で形成した後、第1絶縁層17a’上に有機絶縁膜である例えばPAEからなる第2絶縁層17b’を80nmの膜厚で形成する。これにより、無機絶縁膜と有機絶縁膜とを積層してなるハイブリッド構造からなる層間絶縁膜17’が形成される。

続いて、例えばPE−CVD法により、第2絶縁層17b’上に、例えばSiO2からなる第1マスク形成層41を100nmの膜厚で形成する。次いで、例えばPE−CVD法により、第1マスク形成層41上にSiNからなる第2マスク形成層42を50nmの膜厚で形成し、第2マスク形成層42上に、SiO2からなる第3マスク形成層43を50nmの膜厚で形成する。ここで、後述するように、第1マスク形成層41は、配線間絶縁膜として第2絶縁層17b’上に残存する。このため、ここでは、第1マスク形成層41がSiO2の非多孔質膜で形成される例について説明するが、比誘電率を低減するために、第1マスク形成層41をSiO2の多孔質膜で形成してもよい。

続いて、図4(b)に示すように、第3マスク形成層43上に、例えば化学増幅型ArFレジストを塗布した後、通常のリソグラフィー技術により、このレジストに配線溝パターンを形成することで、レジストパターンR’を形成する。

次いで、図4(c)に示すように、レジストパターンR’(前記図4(b)参照)をマスクとして用いたドライエッチングにより、第3マスク形成層43(前記図4(b)参照)をエッチングして、配線溝パターンを有する第3マスク43’を形成する。その後、例えばO2系ガスを用いたアッシング処理と有機アミン系の薬液処理を施すことにより、レジストレジストパターンR’及びエッチング処理の際に生じた残留付着物を完全に除去する。

続いて、上記第3マスク43’上を含む第2マスク形成層42上に、例えば有機系材料からなる反射防止膜(BARC)44を形成し、第3マスク43’による段差を埋め込んだ後、反射防止膜44上に接続孔パターンを有するレジストパターンRを形成する。この際、レジストパターンRに設けられた接続孔パターンの少なくとも一部が、第3マスク43’の配線溝パターンの開口部内に重なるようにレジストパターンRを形成する。

次に、図5(d)に示すように、レジストパターンR(前記図4(c)参照)をマスクに用いたドライエッチングにより、反射防止膜44(前記図4(c)参照)、第3マスク43’、第2マスク形成層42(前記図4(c)参照)、および第1マスク形成層41(前記図4(c)参照)をエッチングし、さらに第2絶縁層17b’をエッチングして、第1絶縁層17a’に達する状態の接続孔18を形成する。

この際、レジストパターンRは、第2絶縁層17b’のエッチングにおいて同時に除去される。そして、このエッチングによって残存する第3マスク43’は、配線溝パターンのマスクとなる。また、第2マスク形成層42のエッチングによってパターン形成された第2マスク42’は、接続孔パターンのマスクとなる。その後、N2/O2系ガスを用いたエッチングにより、残存したレジストパターンRと反射防止膜44を除去する。

次に、図5(e)に示すように、第3マスク(SiO2)43’をエッチングマスクとしたドライエッチング法により、第2マスク(SiCN)42’をエッチングする。これにより、第2マスク42’が配線溝パターンのマスクとなる。また、第1マスク形成層41(前記図5(d)参照)は、接続孔パターンが形成された第1マスク41’になる。このドライエッチングにおいては、接続孔18の底部に露出する第1絶縁層17a’が途中までエッチングされて接続孔18が掘り下げられる。

次に、図5(f)に示すように、第1マスク(SiO2)41’をエッチングマスクにして、第1絶縁層17a’の下部層をエッチングして、接続孔18をさらに掘り下げてエッチングストッパー膜16を露出させる。この際、第3マスク(SiO2)43’(前記図5(e)参照)と第2マスク(SiCN)42’をエッチングマスクとして、第1マスク(SiO2)41’がエッチングされ、第1マスク41’に配線溝19が形成される。

続いて、図6(g)に示すように、第2マスク(SiCN)42’(前記図5(f)参照)をエッチングマスクにして、配線溝19の底部に残存する第2絶縁層17b’をエッチングする。これにより、第1マスク41’に形成された配線溝19をさらに掘り下げ、第1マスク41’と第2絶縁層17b’とに、配線溝19を形成する。

次いで、接続孔18底部に残存しているエッチングストッパー膜16をエッチングすることにより、配線溝19の底部に開口させた接続孔18を下層配線15に連通させる。

次に、図6(h)に示すように、第1実施形態と同一の処理条件で、層間絶縁膜17に、DMPSを用いたプラズマ処理を行う。これにより、上記ドライエッチングによりダメージを受けた配線溝19または接続孔18の側壁に付着したOH基が脱離し、層間絶縁膜17’および第1マスク41’の表面側にこれらが緻密化された緻密層(図示省略)が形成される。また、上記ガスがCを含むことで、配線溝19または接続孔18の側壁に露出したダングリングボンドが炭素含有基で終端され、緻密層が設けられた配線溝19および接続孔18の内壁を覆う状態で、第1マスク41’上に、炭素含有膜(SixCy膜)からなるシール層32が0.5nm以下の膜厚で形成される。これにより、配線溝19または接続孔18の側壁に露出した層間絶縁膜17の吸湿が抑制され、層間絶縁膜17に残存した水分の脱ガスが防止される。また、接続孔18の底部の下層配線15上を覆う状態で形成されるシール層32は、このプラズマ処理の熱により下層配線15の表面側に拡散されてシリサイド層Sが形成される。これにより、SM耐性およびEM耐性が向上する。

なお、ここでは、第1マスク41’がSiO2の非多孔質膜で形成されることとするが、第1マスク41’がSiO2の多孔質膜で形成される場合には、配線溝19の側壁に露出された第1マスク41’もドライエッチングによりダメージを受け吸湿し易くなる。よって、緻密層とシール層32が設けられることで、第1マスク41’の吸湿が防止され、第1マスク41’からの脱ガスが防止される。

この後の工程は、通常のデュアルダマシン法と同様に行う。すなわち、図6(i)に示すように、例えばスパッタリング法により、配線溝19および接続孔18の内壁を覆う状態で、第1マスク41’上に例えばTaからなるバリア膜20を成膜し、例えば電解めっき法またはスパッタリング法により、配線溝19と接続孔18とを埋め込む状態で、バリア膜20上に例えばCuからなる導電膜(図示省略)を形成する。

その後、CMP法により、導電膜(図示省略)およびバリア膜20のうち、配線パターンとして不要な部分とともに、シール層32と第1マスク41’の途中までを除去することで、接続孔18にヴィア21を形成するとともに配線溝19に上層配線22を形成する。これにより、下層配線15のヴィア21との界面側にシリサイド層Sが設けられた状態となる。そして、上層配線22上を含む第1マスク41’上に、例えばSiCNからなるエッチングストッパー膜23を形成する。

この後の工程は、図4(a)〜図6(i)を用いて説明した工程を繰り返すことで、デュアルダマシン構造を有する多層配線構造を形成することができる。

以上説明した半導体装置の製造方法およびこれにより得られる半導体装置によれば、ドライエッチングにより配線溝19および接続孔18を形成した後の層間絶縁膜17’および第1マスク41’に、DMPSガスを用いたプラズマ処理を行うことから、配線溝19および接続孔18の側壁に付着したOH基が脱離し、層間絶縁膜17およの第1マスク41’の表面側が緻密化されて緻密層31が形成される。また、配線溝19および接続孔18の側壁に露出したダングリングボンドが炭素含有基で終端されて、緻密層31の表面にSixCy膜からなるシール層32が形成される。したがって、第1実施形態と同様の効果を奏することができる。

なお、上記実施形態においては、図6(h)を用いて説明したように、接続孔18底部のエッチングストッパー膜16を除去し、第2絶縁層17b’に配線溝19を形成する工程の後、バリア膜20を形成する工程の前に、上記プラズマ処理を行う例について説明したが、本発明は、接続孔18または配線溝19を形成する工程の後、バリア膜20を形成する工程の前であれば、どの工程でプラズマ処理を行ってもよい。

例えば、図5(d)を用いて説明した第1絶縁層17a’に達する状態の接続孔18を形成する工程の後、図5(e)を用いて説明した第1絶縁層17a’の途中まで接続孔18を掘り下げる工程の前に行ってもよく、図5(e)を用いて説明した第1絶縁層17a’の途中まで接続孔18を掘り下げる工程の後、図5(f)を用いて説明した接続孔18をエッチングストッパー膜16に達するまで掘り下げる工程の前に行ってもよい。さらに、図5(f)を用いて説明した接続孔18をエッチングストッパー膜16に達するまで掘り下げ、第1マスク41’に配線溝19を形成する工程の後、図6(g)を用いて説明した接続孔18底部のエッチングストッパー膜16を除去し、第2絶縁層17b’に配線溝19を形成する工程の前で行ってもよい。また、上述した各工程の間の2工程以上で上記プラズマ処理を行い、複数回の処理を行ってもよい。

なお、上述した第1実施形態および第2実施形態では、層間絶縁膜17に接続孔18を先に形成した後、配線溝19を形成する例について説明したが、配線溝19を接続孔18よりも先に形成する場合であっても、本発明は適用可能である。さらに、上述した実施形態では、デュアルダマシン法による半導体装置の製造方法を例にとって説明したが、本発明はこれに限定されず、シングルダマシン法であっても、適用可能である。

11…基板、15…下層配線、17…層間絶縁膜、18…接続孔、19…配線溝、20…バリア膜、31…緻密層、32…シール層

Claims (10)

- 表面側に第1導電層が設けられた基板上に絶縁膜を形成し、ドライエッチングにより当該絶縁膜に凹部を形成する第1工程と、

前記絶縁膜に、炭素またはシリコンを含有するガスを用いたプラズマ処理を行う第2工程と

プラズマ処理後の前記凹部に第2導電層を埋め込み形成する第3工程とを有する

ことを特徴とする半導体装置の製造方法。 - 前記ガスは、炭素とシリコンの両方を含有している

ことを特徴とする請求項1記載の半導体装置の製造方法。 - 前記絶縁膜は、酸化シリコンよりも誘電率の低い低誘電率膜を有しており、当該低誘電率膜が前記凹部の側壁に露出されている

ことを特徴とする請求項1記載の半導体装置の製造方法。 - 前記絶縁膜は、有機絶縁膜と無機絶縁膜との積層膜で構成されている

ことを特徴とする請求項1記載の半導体装置の製造方法。 - 前記第1工程では、前記第1導電層に達する状態で前記凹部を形成する

ことを特徴とする請求項1記載の半導体装置の製造方法。 - 前記第2工程と前記第3工程の間に、前記凹部を前記第1導電層に達する状態まで掘り下げる

ことを特徴とする請求項1記載の半導体装置の製造方法。 - 前記第2工程と前記第3工程の間に、

前記凹部の内壁を覆う状態で、前記第2導電層から前記絶縁膜への導電材料の拡散を防止するバリア膜を形成する工程を行う

ことを特徴とする請求項1記載の半導体装置の製造方法。 - 表面側に第1導電層が形成された基板と、当該基板上に設けられた絶縁膜と、当該絶縁膜に前記第1導電層に達する状態で設けられた凹部に埋め込み形成された第2導電層とを備えた半導体装置において、

前記絶縁膜の前記第2導電層との界面側には、当該絶縁膜が緻密化された緻密層が設けられており、当該緻密層と前記第2導電層との間には、炭素を含有するシール層が設けられている

ことを特徴とする半導体装置。 - 前記第1導電層の前記第2導電層との界面側には、シリサイド層が設けられている

ことを特徴とする請求項8記載の半導体装置。 - 表面側に第1導電層が形成された基板と、当該基板上に設けられた絶縁膜と、当該絶縁膜に前記第1導電層に達する状態で設けられた凹部に埋め込み形成された第2導電層とを備えた半導体装置において、

前記絶縁膜の前記第2導電層との界面側には、当該絶縁膜が緻密化された緻密層が設けられており、前記第1導電層の前記第2導電層との界面側には、シリサイド層が設けられている

ことを特徴とする半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006103809A JP2007281114A (ja) | 2006-04-05 | 2006-04-05 | 半導体装置の製造方法および半導体装置 |

| TW096110606A TW200741970A (en) | 2006-04-05 | 2007-03-27 | Method for manufacturing semiconductor device and semiconductor device |

| CNA200710091615XA CN101051621A (zh) | 2006-04-05 | 2007-04-03 | 半导体装置的制造方法和半导体装置 |

| US11/695,945 US20080136037A1 (en) | 2006-04-05 | 2007-04-03 | Method for manufacturing semiconductor device and semiconductor device |

| KR1020070033219A KR20070100131A (ko) | 2006-04-05 | 2007-04-04 | 반도체 장치의 제조 방법 및 반도체 장치 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006103809A JP2007281114A (ja) | 2006-04-05 | 2006-04-05 | 半導体装置の製造方法および半導体装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2007281114A true JP2007281114A (ja) | 2007-10-25 |

Family

ID=38682276

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006103809A Pending JP2007281114A (ja) | 2006-04-05 | 2006-04-05 | 半導体装置の製造方法および半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20080136037A1 (ja) |

| JP (1) | JP2007281114A (ja) |

| KR (1) | KR20070100131A (ja) |

| CN (1) | CN101051621A (ja) |

| TW (1) | TW200741970A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009153857A1 (ja) * | 2008-06-17 | 2009-12-23 | 富士通株式会社 | 半導体装置及びその製造方法 |

| JP2011171736A (ja) * | 2010-02-17 | 2011-09-01 | Renesas Electronics Corp | 半導体装置及びその製造方法 |

| JP2012015411A (ja) * | 2010-07-02 | 2012-01-19 | Tokyo Electron Ltd | 半導体装置の製造方法及び半導体装置 |

| JP2016042536A (ja) * | 2014-08-18 | 2016-03-31 | 富士通株式会社 | 半導体装置及び半導体装置の製造方法 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100871551B1 (ko) * | 2007-11-06 | 2008-12-01 | 주식회사 동부하이텍 | 반도체 소자 및 그 제조방법 |

| CN102136452B (zh) * | 2010-01-27 | 2013-06-12 | 中芯国际集成电路制造(上海)有限公司 | 铜互连结构的形成方法及用于该方法的cmp设备 |

| US9245797B2 (en) * | 2013-08-19 | 2016-01-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Opening fill process and structure formed thereby |

| KR102163187B1 (ko) * | 2013-10-21 | 2020-10-08 | 삼성전자 주식회사 | 반도체 장치의 제조 방법 및 이를 구현하기 위한 컴퓨팅 시스템 |

| US9754789B2 (en) * | 2013-10-21 | 2017-09-05 | Samsung Electronics Co., Ltd. | Method of fabricating semiconductor device and computing system for implementing the method |

| US9793204B2 (en) * | 2015-11-17 | 2017-10-17 | Taiwan Semiconductor Manufacturing Company Limited | Method of manufacturing semiconductor structure comprising plurality of through holes using metal hard mask |

| JP6663400B2 (ja) * | 2017-09-11 | 2020-03-11 | 株式会社Kokusai Electric | 半導体装置の製造方法、基板処理装置およびプログラム |

| US10741442B2 (en) | 2018-05-31 | 2020-08-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Barrier layer formation for conductive feature |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7049702B2 (en) * | 2003-08-14 | 2006-05-23 | Taiwan Semiconductor Manufacturing Co., Ltd. | Damascene structure at semiconductor substrate level |

| US7329956B1 (en) * | 2006-09-12 | 2008-02-12 | Taiwan Semiconductor Manufacturing Company, Ltd. | Dual damascene cleaning method |

-

2006

- 2006-04-05 JP JP2006103809A patent/JP2007281114A/ja active Pending

-

2007

- 2007-03-27 TW TW096110606A patent/TW200741970A/zh unknown

- 2007-04-03 US US11/695,945 patent/US20080136037A1/en not_active Abandoned

- 2007-04-03 CN CNA200710091615XA patent/CN101051621A/zh active Pending

- 2007-04-04 KR KR1020070033219A patent/KR20070100131A/ko not_active Withdrawn

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009153857A1 (ja) * | 2008-06-17 | 2009-12-23 | 富士通株式会社 | 半導体装置及びその製造方法 |

| JPWO2009153857A1 (ja) * | 2008-06-17 | 2011-11-24 | 富士通株式会社 | 半導体装置及びその製造方法 |

| US8461041B2 (en) | 2008-06-17 | 2013-06-11 | Fujitsu Limited | Semiconductor device and method of manufacturing semiconductor device |

| JP2011171736A (ja) * | 2010-02-17 | 2011-09-01 | Renesas Electronics Corp | 半導体装置及びその製造方法 |

| JP2012015411A (ja) * | 2010-07-02 | 2012-01-19 | Tokyo Electron Ltd | 半導体装置の製造方法及び半導体装置 |

| JP2016042536A (ja) * | 2014-08-18 | 2016-03-31 | 富士通株式会社 | 半導体装置及び半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20080136037A1 (en) | 2008-06-12 |

| CN101051621A (zh) | 2007-10-10 |

| TW200741970A (en) | 2007-11-01 |

| KR20070100131A (ko) | 2007-10-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5204370B2 (ja) | 半導体装置およびその製造方法 | |

| JP4086673B2 (ja) | 半導体装置及びその製造方法 | |

| JP5180426B2 (ja) | 半導体装置の製造方法 | |

| CN100470787C (zh) | 半导体器件及其制造方法 | |

| JP4177993B2 (ja) | 半導体装置及びその製造方法 | |

| US7741224B2 (en) | Plasma treatment and repair processes for reducing sidewall damage in low-k dielectrics | |

| KR20070100131A (ko) | 반도체 장치의 제조 방법 및 반도체 장치 | |

| KR101093915B1 (ko) | 반도체 장치의 제조 방법 | |

| CN100349281C (zh) | 用于在半导体器件中形成互连线的方法及互连线结构 | |

| US20080182405A1 (en) | Self-aligned air-gap in interconnect structures | |

| US7242096B2 (en) | Semiconductor device and method for manufacturing the same | |

| CN101009266A (zh) | 半导体结构及其形成方法 | |

| WO2007091574A1 (ja) | 多層配線構造および多層配線の製造方法 | |

| KR101354126B1 (ko) | 반도체 장치 및 반도체 장치의 제조 방법 | |

| CN100440433C (zh) | 制造半导体器件的方法 | |

| JP2009182000A (ja) | 半導体装置およびその製造方法 | |

| US7259089B2 (en) | Semiconductor device manufacturing method that includes forming a wiring pattern with a mask layer that has a tapered shape | |

| US20060261483A1 (en) | Semiconductor device and method for manufacturing the same | |

| US7250364B2 (en) | Semiconductor devices with composite etch stop layers and methods of fabrication thereof | |

| JP2007157959A (ja) | 半導体装置の製造方法および半導体装置 | |

| US11756878B2 (en) | Self-aligned via structure by selective deposition | |

| JP2005217223A (ja) | 半導体装置の製造方法 | |

| JP2008010610A (ja) | 半導体装置の製造方法 | |

| JP2006253666A (ja) | 半導体装置およびその製造方法 | |

| CN109309044B (zh) | 半导体结构及其形成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080409 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080415 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080812 |