JP2006121663A - データ伝送 - Google Patents

データ伝送 Download PDFInfo

- Publication number

- JP2006121663A JP2006121663A JP2005256873A JP2005256873A JP2006121663A JP 2006121663 A JP2006121663 A JP 2006121663A JP 2005256873 A JP2005256873 A JP 2005256873A JP 2005256873 A JP2005256873 A JP 2005256873A JP 2006121663 A JP2006121663 A JP 2006121663A

- Authority

- JP

- Japan

- Prior art keywords

- data

- transmission path

- transmission

- communication system

- base clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000005540 biological transmission Effects 0.000 title claims abstract description 116

- 238000004891 communication Methods 0.000 claims abstract description 74

- 238000000034 method Methods 0.000 claims abstract description 26

- 238000012545 processing Methods 0.000 claims abstract description 14

- 230000008569 process Effects 0.000 claims abstract description 12

- 230000004044 response Effects 0.000 claims abstract description 4

- 238000005070 sampling Methods 0.000 claims description 38

- 230000000737 periodic effect Effects 0.000 claims description 4

- 238000012790 confirmation Methods 0.000 claims description 2

- 230000001172 regenerating effect Effects 0.000 claims description 2

- 239000000872 buffer Substances 0.000 description 42

- 238000012546 transfer Methods 0.000 description 32

- 238000010586 diagram Methods 0.000 description 14

- 230000003139 buffering effect Effects 0.000 description 11

- 239000013307 optical fiber Substances 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 4

- 239000003550 marker Substances 0.000 description 4

- 238000012544 monitoring process Methods 0.000 description 4

- 230000001360 synchronised effect Effects 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 230000001934 delay Effects 0.000 description 2

- 238000005538 encapsulation Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000003780 insertion Methods 0.000 description 2

- 230000037431 insertion Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000009286 beneficial effect Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 125000004122 cyclic group Chemical group 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0008—Synchronisation information channels, e.g. clock distribution lines

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/04—Speed or phase control by synchronisation signals

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Communication Control (AREA)

Abstract

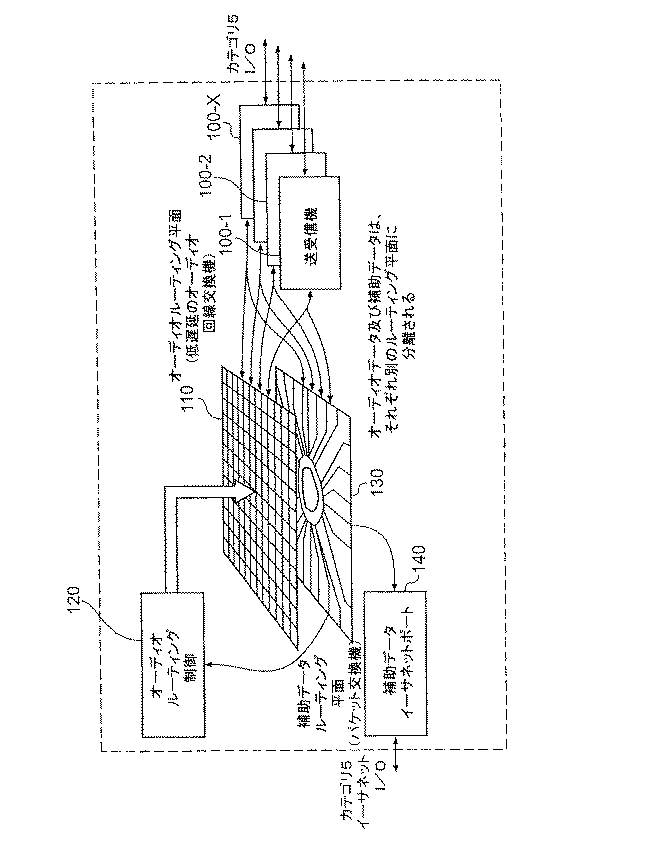

【解決手段】送信ノードは、通信リンクの各伝送パスを介して、少なくとも2つのストリーミングデータ信号からのデータを送信するデータ送信手段と、通信リンクを介して、少なくとも2つのベースクロック信号のタイミング情報を送信するタイミング送信手段と、各伝送パスと、対応するベースクロック信号の1つとの間の各関係を特定し、伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信する。受信ノードは、通信リンクの伝送パスからデータを受信するデータ受信手段と、コンフィグレーションデータに応じてベースクロック信号のタイミング情報を処理し、各伝送パスに対応する各サンプリングクロックを生成する処理手段と、サンプリングクロックを各伝送パスからのデータに関連付け、ストリーミングデータ信号を再生する。

【選択図】 図5

Description

ベースクロックB:48kHz±12.5%

ベースクロックC:44.1kHz±12.5%

ベースクロックD:48kHz±100ppm

したがって、可能な最小ベースクロック周波数は、38.5875kHz(44.1kHz−12.5%)であり、可能な最大ベースクロック周波数は、54kHz(48kHz+12.5%)である。多くの実際の装置(implementations)が±12.5%の動作をサポートしないので、ベースクロックAは、互換性を保証にするために、常に、±100ppmで動作するように構成する。各オーディオストリーム(表2参照)は、4つの可能なベースクロックのうちの1つに同期しなければならない。各オーディオデータストリームには、適切なサンプリングクロックレートを実現するために、オーディオベースクロックに乗算する係数を指定するサンプリングレート乗数(sample rate multiplier)を割り当てる。表2に示す使用可能な各サンプリングレートについて、関連するベースクロック及びサンプリングレート乗数を以下の表4に示す。

・各オーディオデータストリームのベースクロック選択(4つの可能なベースクロックからの選択)

・各ベースクロックの公称周波数を指定するデータ

・各ベースクロックの公差(±100ppm及び±12.5%のいずれか)

・受信機が有効なコンフィグレーションブロックを受信したこと、及び受信機が要求されたオーディオモードで動作できることを示すフラグフィールド(フラグフィールドは送信機ではなく受信機によって提供される)

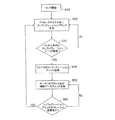

ステップ930において、送信機は、送信したコンフィグレーションの確認応答として、有効なコンフィグレーションブロックが受信機から返信されたか否か判定する。受信機が、要求したオーディオモードを処理することができる場合、確認応答コンフィグレーションブロックのインジケータフラグは、このことを確認するように設定される。ステップ930において、受信機からの確認応答コンフィグレーションブロックがないと判定した場合、処理は、ステップ920に戻り、送信機は、コンフィグレーションデータブロックを受信機に周期的に送信し続ける。一方、ステップ930において、確認応答コンフィグレーションブロックが受信されたと判定した場合、処理は、ステップ940に進み、送信機は、更にもう1つのコンフィグレーションブロックを送信する。確認応答コンフィグレーションブロックを受信し、ステップ940において更にもう1つのコンフィグレーションブロックを送信した送信機は、ステップ950において、オーディオデータブロック及び補助データブロックの送信を開始する。補助データフレームは、本発明に基づくギガビットリンクのオーディオフレーム間で送信される。

・ブロック内のオーディオデータが、送信機における(オーディオベースクロック/2048)同期フラグに対応したオーディオフレームの最初から始まっているか否かを示すオーディオストリーム同期マーカ(Audio Stream Synchronisation Marker:ASSM)

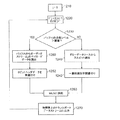

ギガビットリンクの8つの独立したそれぞれのデータ伝送パスは、送信機内の関連したFIFO(ファーストインファーストアウト)バッファと、受信機内の対応したFIFOバッファとを有する。

この場合、受信機における最大出力オーディオデータ転送レートは、各方向において合計384チャンネル(1ストリーム当たり48のチャンネル)を有する、表2の(48kHz+12.5%=54kHz)における24ビットPCMのオーディオフォーマット(24ビットのオーディオ+4ビットのAES3メタデータ)に対応する。この場合、最大出力オーディオデータ転送レートは、28ビット×48チャンネル×54kHz=72.6Mbpsである。また、オーディオフレーム伝送時間=9196×8ビット/1Gbps=73.5μsであり、補助データ伝送時間=1540×8ビット/1Gbps=12.3μsである。したがって、ギガビットリンクの潜在的に同等な連続するデータ転送レートは、(192ビット×366/8=8784ビット)/(73.5+12.3μs)=102.4Mbpsである。したがって、この構成では、ギガビットリンクは、許容可能なレベルの待ち時間で最大データ転送レートをサポートするために必要とされる性能を上回る能力を有する。

Claims (31)

- 通信リンクの各伝送パスを介して、少なくとも2つのストリーミングデータ信号からのデータを送信するデータ送信手段と、

上記通信リンクを介して、少なくとも2つのベースクロック信号のタイミング情報を送信するタイミング送信手段と、

上記各伝送パスと、対応する上記ベースクロック信号の1つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信するコンフィグレーション送信手段とを有する送信ノードと、

上記通信リンクの上記伝送パスからデータを受信するデータ受信機と、

上記コンフィグレーションデータに応じて上記ベースクロック信号の上記タイミング情報を処理し、各伝送パスに対応する各サンプリングクロックを生成するプロセッサと、

上記コンフィグレーションデータに基づいて、上記サンプリングクロックを上記各伝送パスからのデータに関連付け、上記ストリーミングデータ信号を再生するロジックとを有する受信ノードとを備えるデータ通信システム。 - 上記ストリーミングデータ信号のデータは、上記通信リンクを介して、データフレームによって搬送されることを特徴とする請求項1記載のデータ通信システム。

- 上記タイミング情報は、上記データフレームのヘッダに含まれていることを特徴とする請求項2記載のデータ通信システム。

- 上記コンフィグレーションデータは、上記ストリーミングデータ信号の少なくとも1つについて、上記対応するベースクロック信号と、上記各ストリーミングデータ信号のサンプリングレートとの間の関係を指定する乗数を表し、上記プロセッサは、上記ベースクロック信号及び上記乗数に基づいて上記サンプリングクロックを生成することを特徴とする請求項1記載のデータ通信システム。

- 上記コンフィグレーションデータは、上記ベースクロック信号のそれぞれの公称周波数値を表すことを特徴とする請求項1記載のデータ通信システム。

- 上記コンフィグレーションデータは、上記少なくとも2つのベースクロックのそれぞれの公差の値を含むことを特徴とする請求項5記載のデータ通信システム。

- 上記コンフィグレーションデータは、上記ストリーミングデータ信号のそれぞれのデータフォーマットを特定するデータを含むことを特徴とする請求項1記載のデータ通信システム。

- 上記受信ノードは、該受信ノードが上記特定のデータフォーマットを扱うことができるか否かを示す情報を上記送信ノードに送信することを特徴とする請求項7記載のデータ通信システム。

- 上記コンフィグレーション送信手段は、上記通信リンクの開始時にコンフィグレーションデータを送信することを特徴とする請求項1記載のデータ通信システム。

- 上記受信ノードは、上記コンフィグレーションデータの受信の確認応答を送信する確認応答送信手段を備えることを特徴とする請求項9記載のデータ通信システム。

- 上記コンフィグレーション送信手段は、上記確認応答を受信すると、上記コンフィグレーションデータの送信を終了することを特徴とする請求項1記載のデータ通信システム。

- 上記コンフィグレーションデータは、周期的に送信されることを特徴とする請求項9記載のデータ通信システム。

- 上記通信リンクは、イーサネット通信リンクであることを特徴とする請求項1記載のデータ通信システム。

- 上記タイミング情報は、周期的な基準クロックに関連して定義されることを特徴とする請求項1記載のデータ通信システム。

- 上記周期的な基準クロックは、イーサネット物理層クロックであることを特徴とする請求項13記載のデータ通信システム。

- 上記タイミング情報は、所定の基準点に関して、上記対応するベースクロック信号の周波数を所定の整数で除算した値に等しい周波数を有するベース関連クロック信号のエッジ位置を指定することを特徴とする請求項13記載のデータ通信システム。

- 上記所定の基準点は、上記送信ノードにおけるフレームヘッダの出力の完了に対応することを特徴とする請求項15記載のデータ通信システム。

- 上記タイミング情報は、上記所定の基準点と、上記ベース関連クロック信号の後続するエッジ位置との間の上記周期的な基準クロックのサイクル数を指定することを特徴とする請求項15記載のデータ通信システム。

- 上記後続するエッジ位置は、次のベース関連クロック信号のエッジ位置であることを特徴とする請求項16記載のデータ通信システム。

- 上記後続するエッジ位置は、1つおいて隣のベース関連クロック信号のエッジ位置であることを特徴とする請求項16記載のデータ通信システム。

- 上記ストリーミングデータ信号は、オーディオデータ信号であることを特徴とする請求項1記載のデータ通信システム。

- データ通信システムにおいて使用する送信ノードにおいて、

通信リンクの各伝送パスを介して、少なくとも2つのストリーミングデータ信号からのデータを送信するデータ送信手段と、

上記通信リンクを介して、少なくとも2つのベースクロック信号のタイミング情報を送信するタイミング送信手段と、

上記各伝送パスと、対応する上記ベースクロック信号の1つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信するコンフィグレーション送信手段とを備える送信ノード。 - データ通信システムにおいて使用する受信ノードにおいて、

上記通信リンクの上記伝送パスから、少なくとも2つのベースクロック信号のタイミング情報と、少なくとも2つのストリーミングデータ信号からのデータと、上記各伝送パスと、対応する上記ベースクロック信号の1つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータとを含むデータを受信するデータ受信機と、

上記コンフィグレーションデータに応じて上記ベースクロック信号の上記タイミング情報を処理し、各伝送パスに対応する各サンプリングクロックを生成するプロセッサと、

上記コンフィグレーションデータに基づいて、上記サンプリングクロックを上記各伝送パスからのデータに関連付け、上記ストリーミングデータ信号を再生するロジックとを備える受信ノード。 - 通信リンクを介して、送信ノードと受信ノードとの間で通信を行う通信方法において、

上記送信ノードにおいて、

通信リンクの各伝送パスを介して、少なくとも2つのストリーミングデータ信号からのデータを送信するステップと、

上記通信リンクを介して、少なくとも2つのベースクロック信号のタイミング情報を送信するステップと、

上記各伝送パスと、対応する上記ベースクロック信号の1つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信するステップと、

上記受信ノードにおいて、

上記通信リンクの上記伝送パスからデータを受信するステップと、

上記コンフィグレーションデータに応じて上記ベースクロック信号の上記タイミング情報を処理し、各伝送パスに対応する各サンプリングクロックを生成するステップと、

上記コンフィグレーションデータに基づいて、上記サンプリングクロックを上記各伝送パスからのデータに関連付け、上記ストリーミングデータ信号を再生するステップとを有する通信方法。 - データ通信システムにおいて使用する送信ノードの動作方法において、

通信リンクの各伝送パスを介して、少なくとも2つのストリーミングデータ信号からのデータを送信するステップと、

上記通信リンクを介して、少なくとも2つのベースクロック信号のタイミング情報を送信するステップと、

上記各伝送パスと、対応する上記ベースクロック信号の1つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信するステップとを有する送信ノードの動作方法。 - データ通信システムにおいて使用する受信ノードの動作方法において、

上記通信リンクの上記伝送パスから少なくとも2つのベースクロック信号のタイミング情報と、少なくとも2つのストリーミングデータ信号からのデータと、上記各伝送パスと、対応する上記ベースクロック信号の1つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータとを含むデータを受信するステップと、

上記コンフィグレーションデータに応じて上記ベースクロック信号の上記タイミング情報を処理し、各伝送パスに対応する各サンプリングクロックを生成するステップと、

上記コンフィグレーションデータに基づいて、上記サンプリングクロックを上記各伝送パスからのデータに関連付け、上記ストリーミングデータ信号を再生するステップとを有する受信ノードの動作方法。 - 請求項24記載の通信方法のステップを実現するプログラムコードを有するコンピュータソフトウェア。

- 請求項27記載のコンピュータソフトウェアを提供する媒体。

- 当該媒体は、記録媒体であることを特徴とする請求項28記載の媒体。

- 当該媒体は、通信媒体であることを特徴とする請求項28記載の媒体。

- 少なくとも2つのベースクロック信号のタイミング情報と、少なくとも2つのストリーミングデータ信号からのデータと、上記各伝送パスと、対応する上記ベースクロック信号の1つとの間の各関係を特定し、該伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータとを含むデータストリーム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB0419625A GB2417867B (en) | 2004-09-03 | 2004-09-03 | Data transmission |

| GB0419625.9 | 2004-09-03 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006121663A true JP2006121663A (ja) | 2006-05-11 |

| JP2006121663A5 JP2006121663A5 (ja) | 2008-10-02 |

| JP4829569B2 JP4829569B2 (ja) | 2011-12-07 |

Family

ID=33156000

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005256873A Expired - Fee Related JP4829569B2 (ja) | 2004-09-03 | 2005-09-05 | データ伝送 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7672414B2 (ja) |

| JP (1) | JP4829569B2 (ja) |

| GB (1) | GB2417867B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008514054A (ja) * | 2004-09-10 | 2008-05-01 | アビッド テクノロジー インコーポレイテッド | ライブ・オーディオ・プレゼンテーション・システム |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2417866B (en) * | 2004-09-03 | 2007-09-19 | Sony Uk Ltd | Data transmission |

| US7515585B2 (en) * | 2005-01-21 | 2009-04-07 | Ixia | Data communication optimization |

| US7802153B1 (en) * | 2006-12-07 | 2010-09-21 | 3Par, Inc. | Trainable link |

| JP4813602B2 (ja) * | 2006-12-15 | 2011-11-09 | トムソン ライセンシング | 時分割多重アクセス媒体アクセス制御層における媒体アクセス制御プロトコル・データ単位集積 |

| US8767952B2 (en) * | 2007-12-17 | 2014-07-01 | Broadcom Corporation | Method and system for utilizing a single connection for efficient delivery of power and multimedia information |

| US8295304B1 (en) * | 2007-12-27 | 2012-10-23 | Exalt Communications Incorporated | Adaptive multi-service data framing |

| KR101042600B1 (ko) * | 2009-12-04 | 2011-06-20 | 한국전자통신연구원 | 반―선형 센서 네트워크에서 저전력 매체 접근 제어 방법 |

| CN102208208B (zh) * | 2010-04-12 | 2014-04-09 | 佛山市智邦电子科技有限公司 | 无损音频播放方法以及音频播放器 |

| US20130191561A1 (en) * | 2010-10-07 | 2013-07-25 | Ntt Docomo, Inc. | Data reading device, communication device, data reading method and program |

| US8817725B2 (en) * | 2012-01-13 | 2014-08-26 | Blackberry Limited | Scheduling transmission of traffic treated less preferentially despite timing requirements |

| US20190075171A1 (en) * | 2017-09-05 | 2019-03-07 | EtherLabs, Inc. | System and Method for Generating Marker Data |

| DE102019208059A1 (de) * | 2019-06-03 | 2020-12-03 | Robert Bosch Gmbh | Einrichtung für eine Teilnehmerstation eines seriellen Bussystems und Verfahren zur Kommunikation in einem seriellen Bussystem |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004165764A (ja) * | 2002-11-11 | 2004-06-10 | Matsushita Electric Ind Co Ltd | 多重伝送システム、多重装置及び分離装置 |

| JP2004180255A (ja) * | 2002-09-30 | 2004-06-24 | Denon Ltd | ネットワークシステム |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0732373B2 (ja) * | 1988-03-26 | 1995-04-10 | 株式会社ケンウッド | Pcm音楽放送のワンウェイアドレス伝送方法 |

| US5852630A (en) * | 1997-07-17 | 1998-12-22 | Globespan Semiconductor, Inc. | Method and apparatus for a RADSL transceiver warm start activation procedure with precoding |

| JP3450662B2 (ja) * | 1997-08-14 | 2003-09-29 | パイオニア株式会社 | 情報記録媒体、その再生装置及び方法並びにその記録装置及び方法 |

| JP3288282B2 (ja) * | 1997-10-20 | 2002-06-04 | 矢崎総業株式会社 | 通信方法、及び通信システム |

| AU2001289596A1 (en) * | 2000-09-27 | 2002-04-08 | Musicagility Aps | A data transfer system for distribution of real time data between a plurality ofdevices |

| US6470032B2 (en) * | 2001-03-20 | 2002-10-22 | Alloptic, Inc. | System and method for synchronizing telecom-related clocks in ethernet-based passive optical access network |

| US7295578B1 (en) * | 2001-09-12 | 2007-11-13 | Lyle James D | Method and apparatus for synchronizing auxiliary data and video data transmitted over a TMDS-like link |

| US6788687B2 (en) * | 2001-10-30 | 2004-09-07 | Qualcomm Incorporated | Method and apparatus for scheduling packet data transmissions in a wireless communication system |

| US7242766B1 (en) * | 2001-11-21 | 2007-07-10 | Silicon Image, Inc. | Method and system for encrypting and decrypting data using an external agent |

| US7283566B2 (en) * | 2002-06-14 | 2007-10-16 | Silicon Image, Inc. | Method and circuit for generating time stamp data from an embedded-clock audio data stream and a video clock |

| GB2399722A (en) * | 2003-03-21 | 2004-09-22 | Sony Uk Ltd | Data communication synchronisation |

-

2004

- 2004-09-03 GB GB0419625A patent/GB2417867B/en not_active Expired - Fee Related

-

2005

- 2005-09-01 US US11/218,212 patent/US7672414B2/en not_active Expired - Fee Related

- 2005-09-05 JP JP2005256873A patent/JP4829569B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004180255A (ja) * | 2002-09-30 | 2004-06-24 | Denon Ltd | ネットワークシステム |

| JP2004165764A (ja) * | 2002-11-11 | 2004-06-10 | Matsushita Electric Ind Co Ltd | 多重伝送システム、多重装置及び分離装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008514054A (ja) * | 2004-09-10 | 2008-05-01 | アビッド テクノロジー インコーポレイテッド | ライブ・オーディオ・プレゼンテーション・システム |

Also Published As

| Publication number | Publication date |

|---|---|

| GB2417867B (en) | 2007-04-11 |

| JP4829569B2 (ja) | 2011-12-07 |

| US7672414B2 (en) | 2010-03-02 |

| US20060050825A1 (en) | 2006-03-09 |

| GB2417867A (en) | 2006-03-08 |

| GB0419625D0 (en) | 2004-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP1989847B1 (en) | System and method for transferring different types of streaming and packetized data across an ethernet transmission line using a frame and packet structure demarcated with ethernet coding violations | |

| JP3539747B2 (ja) | スイッチング機構における等時性データのローカルループバック | |

| JP3636456B2 (ja) | 等時性リンクプロトコル | |

| US7333478B2 (en) | Methods and apparatus for transporting digital audio-related signals | |

| JPH06284130A (ja) | 等時性能力を備えたデータ通信ネットワーク | |

| US8606382B2 (en) | System and method for transferring non-compliant packetized and streaming data into and from a multimedia device coupled to a network across which compliant data is sent | |

| JPH06216908A (ja) | フレーム構造を有する等時性ソースデータの伝送用ネットワーク | |

| JP4829569B2 (ja) | データ伝送 | |

| JP4907924B2 (ja) | データ伝送 | |

| US6874048B2 (en) | Communication system and methodology for sending a designator for at least one of a set of time-division multiplexed channels forwarded across a locally synchronized bus | |

| CN101385294B (zh) | 利用以以太网编码违例区分的帧和分组结构在以太网传输线上传递不同类型的流数据和分组数据的系统和方法 | |

| US6922747B2 (en) | Communication system and methodology for addressing and sending data of dissimilar type and size across channels formed within a locally synchronized bus | |

| EP1512253B1 (en) | Communication system for sending data of dissimilar type and size across channels formed within a locally synchronized bus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20080418 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080422 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080818 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080818 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110818 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110830 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110916 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140922 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |