JP2005539404A - サブパターン転写ナノスケールメモリ構造 - Google Patents

サブパターン転写ナノスケールメモリ構造 Download PDFInfo

- Publication number

- JP2005539404A JP2005539404A JP2005501049A JP2005501049A JP2005539404A JP 2005539404 A JP2005539404 A JP 2005539404A JP 2005501049 A JP2005501049 A JP 2005501049A JP 2005501049 A JP2005501049 A JP 2005501049A JP 2005539404 A JP2005539404 A JP 2005539404A

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- nanoscale

- microscale

- memory array

- memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000015654 memory Effects 0.000 title claims description 115

- 238000012546 transfer Methods 0.000 title claims description 31

- 239000002070 nanowire Substances 0.000 claims abstract description 63

- 238000000034 method Methods 0.000 claims description 64

- 238000004519 manufacturing process Methods 0.000 claims description 23

- 230000008569 process Effects 0.000 claims description 15

- 238000005530 etching Methods 0.000 claims description 9

- 239000000463 material Substances 0.000 claims description 7

- 230000000903 blocking effect Effects 0.000 claims description 6

- 230000005611 electricity Effects 0.000 claims description 4

- 238000005516 engineering process Methods 0.000 claims description 4

- 230000000704 physical effect Effects 0.000 claims description 4

- 230000001747 exhibiting effect Effects 0.000 claims 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 15

- 229910052710 silicon Inorganic materials 0.000 description 15

- 239000010703 silicon Substances 0.000 description 15

- 239000011295 pitch Substances 0.000 description 14

- 238000003491 array Methods 0.000 description 8

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 5

- 229910021393 carbon nanotube Inorganic materials 0.000 description 5

- 239000002041 carbon nanotube Substances 0.000 description 5

- 239000004020 conductor Substances 0.000 description 5

- 230000007246 mechanism Effects 0.000 description 5

- 239000002071 nanotube Substances 0.000 description 5

- 230000004888 barrier function Effects 0.000 description 4

- 239000000969 carrier Substances 0.000 description 4

- 230000008878 coupling Effects 0.000 description 4

- 238000010168 coupling process Methods 0.000 description 4

- 238000005859 coupling reaction Methods 0.000 description 4

- 239000002019 doping agent Substances 0.000 description 4

- 239000000758 substrate Substances 0.000 description 4

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 238000000926 separation method Methods 0.000 description 3

- 229910000673 Indium arsenide Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 238000007667 floating Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- RPQDHPTXJYYUPQ-UHFFFAOYSA-N indium arsenide Chemical compound [In]#[As] RPQDHPTXJYYUPQ-UHFFFAOYSA-N 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 239000002052 molecular layer Substances 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 239000002105 nanoparticle Substances 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000003252 repetitive effect Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 108091026890 Coding region Proteins 0.000 description 1

- 108700026244 Open Reading Frames Proteins 0.000 description 1

- 230000004075 alteration Effects 0.000 description 1

- 238000000429 assembly Methods 0.000 description 1

- 230000000712 assembly Effects 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000036541 health Effects 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000013139 quantization Methods 0.000 description 1

- 238000001338 self-assembly Methods 0.000 description 1

- 230000008054 signal transmission Effects 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000011232 storage material Substances 0.000 description 1

- 230000005641 tunneling Effects 0.000 description 1

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0023—Address circuits or decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/02—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using elements whose operation depends upon chemical change

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/02—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using elements whose operation depends upon chemical change

- G11C13/025—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using elements whose operation depends upon chemical change using fullerenes, e.g. C60, or nanotubes, e.g. carbon or silicon nanotubes

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/101—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration including resistors or capacitors only

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0657—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body

- H01L29/0665—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body the shape of the body defining a nanostructure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0657—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body

- H01L29/0665—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body the shape of the body defining a nanostructure

- H01L29/0669—Nanowires or nanotubes

- H01L29/0673—Nanowires or nanotubes oriented parallel to a substrate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N99/00—Subject matter not provided for in other groups of this subclass

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/71—Three dimensional array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/77—Array wherein the memory element being directly connected to the bit lines and word lines without any access device being used

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/81—Array wherein the array conductors, e.g. word lines, bit lines, are made of nanowires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/762—Nanowire or quantum wire, i.e. axially elongated structure having two dimensions of 100 nm or less

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/902—Specified use of nanostructure

- Y10S977/932—Specified use of nanostructure for electronic or optoelectronic application

- Y10S977/943—Information storage or retrieval using nanostructure

Abstract

Description

ナノスケール配線の軸方向に沿って分布する第1の複数の制御可能領域を持つナノスケール配線を提供するステップであって、各領域が第1の閾値よりも小さな値の信号で制御された場合、あるいは信号で制御されない場合には、前記領域によって、ナノスケール配線に沿った電気伝導が可能となる、ステップと、

前記領域を制御してまたは制御しないで、ナノスケール配線の電気伝導を可能にし、あるいは遮断するステップと、

を有する方法が提供される。

ナノスケール配線の軸方向に沿って分布する第1の複数の制御可能領域を持つナノスケール配線を提供するステップであって、各領域が第1の閾値よりも大きな値の信号で制御された場合、前記領域によって、ナノスケール配線に沿った電気伝導が可能となる、ステップと、

前記領域を制御してまたは制御しないで、ナノスケール配線の電気伝導を可能にし、あるいは遮断するステップと、

を有する方法が提供される。

ナノスケール配線の軸方向に沿って分布する第1の複数の制御可能領域を持つ各ナノスケール配線を提供するステップであって、各領域が第1の閾値よりも小さな値の信号で制御された場合、あるいは信号で制御されない場合には、前記領域によって、ナノスケール配線に沿った電気伝導が可能となる、ステップと、

複数の制御配線を提供するステップであって、各制御配線は第1の複数の一連の領域に接続され、前記一連の領域を制御する制御信号を伝送することが可能である、ステップと、

制御配線に沿って制御信号を提供するステップであって、複数のナノスケール配線のうち単一のナノスケール配線は電気伝導を示し、複数のナノスケール配線のうちの残りのナノスケール配線は電気伝導を示さないようにする、ステップと、

を有する方法が提供される。

ナノスケール配線の軸方向に沿って分布する第1の複数の制御可能領域を持つ各ナノスケール配線を提供するステップであって、各領域が第1の閾値よりも大きな値の信号で制御された場合、前記領域によって、ナノスケール配線に沿った電気伝導が可能となる、ステップと、

複数の制御配線を提供するステップであって、各制御配線は第1の複数の一連の領域に接続され、前記一連の領域を制御する制御信号を伝送することが可能である、ステップと、

制御配線に沿って制御信号を提供するステップであって、複数のナノスケール配線のうち単一のナノスケール配線は電気伝導を示し、複数のナノスケール配線のうちの残りのナノスケール配線は電気伝導を示さないようにする、ステップと、

を有する方法が提供される。

ナノスケール配線の軸方向に沿って分布する制御可能領域を持つ各ナノスケール配線を提供するステップと、

大きなナノスケール配線組から複数のナノスケール配線を確率的に選択して、複数のナノスケール配線を構成するステップと、

を有する方法が提供される。

軸方向に沿って分布する第1の複数の制御可能領域を持つナノスケール配線であって、各領域が第1の閾値よりも小さな値の信号で制御された場合、あるいは信号で制御されない場合には、前記領域によって、ナノスケール配線に沿った電気伝導が可能となる、ナノスケール配線と、

前記ナノスケール配線に沿った電気伝導を制御する手段と、

を有する配置が提供される。

前記ナノスケール配線に沿った電気伝導を制御する手段と、

を有する配置が提供される。

複数のナノスケール配線であって、各ナノスケール配線は、ナノスケール配線の軸方向に沿って分布する第1の制御可能領域組を有し、各領域が第1の閾値よりも小さな値の信号で制御された場合、あるいは信号で制御されない場合には、前記制御可能領域によって、ナノスケール配線に沿った電気伝導が可能となる、複数のナノスケール配線と、

複数の制御配線であって、各制御配線は、一連の制御可能領域に接続され、該一連の制御可能領域を制御する信号を伝送することの可能な、複数の制御配線と、

を有する装置が提供される。

複数のナノスケール配線であって、各ナノスケール配線は、ナノスケール配線の軸方向に沿って分布する第1の制御可能領域組を有し、各領域が第1の閾値よりも小さな値の信号で制御された場合、あるいは信号で制御されない場合には、前記制御可能領域によって、ナノスケール配線に沿った電気伝導が可能となる、複数のナノスケール配線と、

複数の制御配線であって、各制御配線は、一連の制御可能領域に接続され、該一連の制御可能領域を制御する信号を伝送することの可能な、複数の制御配線と、

を有する装置が提供される。

複数のナノスケール配線であって、各ナノスケール配線は、ナノスケール配線の軸方向に沿って分布する第1の制御可能領域組を有し、各領域が第1の閾値よりも大きな値の信号で制御された場合、前記制御可能領域によって、ナノスケール配線に沿った電気伝導が可能となる、複数のナノスケール配線と、

複数の制御配線であって、各制御配線は、一連の制御可能領域に接続され、該一連の制御可能領域を制御する信号を伝送することの可能な、複数の制御配線と、

を有する装置が提供される。

ナノスケール配線の軸方向に沿って分布する制御可能領域を持つ各ナノスケール配線を提供する手段と、

複数のナノスケール配線から、制御されるナノスケール配線のサブ集合を確率的に選択して、サブ集合を形成する手段と、

ナノスケール配線のサブ集合のナノスケール配線上の制御可能領域を制御して、または制御しないで、ナノスケール配線のサブ集合の中から単一のナノスケール配線を選択する手段と、

を有する装置が提供される。

第1のナノスケール配線組と、

該第1のナノスケール配線組と交差する第2のナノスケール配線組であって、前記第1の組と第2の組の間の交差部がメモリ配置を定める、第2のナノスケール配線組と、

を有するメモリ配列において、

当該メモリ配置は、前記第1のナノスケール配線組のうちいずれか一方のナノスケール配線と、前記第2のナノスケール配線組のうちいずれか一方のナノスケール配線とを選択することによりアドレス指定され、前記第1のナノスケール配線組および前記第2のナノスケール配線組は、ナノスケール配線の軸方向に沿って分布する制御可能領域を持ち、第1の制御可能領域組は第1の物理的特性を示し、第2の制御可能領域組は前記第1の制御可能領域組とは異なる第2の物理的特性を示し、さらに

第1の複数のアドレス配線であって、該第1の複数のアドレス配線の各々は、前記第1のナノスケール配線組の一連の領域に接続された、第1の複数のアドレス配線と、

第2の複数のアドレス配線であって、前記第2の複数のアドレス配線の各々は、前記第2のナノスケール配線組の一連の領域に接続された、第2の複数のアドレス配線と、

を有するメモリ配列が提供される。

ミクロスケールオーム接続であって、各オーム接続は複数のナノスケール配線の異なるサブ集合に接続され複数のナノスケール配線の中の特定のサブ集合を選択する、ミクロスケールオーム接続と、

複数のナノスケール配線の異なるサブ集合に接続され、一旦特定のサブ集合が選択された場合、ナノスケール配線の特定のサブ集合の中からナノスケール配線を選択するアドレス配線と、

を有する回路が提供される。

複数のナノスケール配線と、

該ナノスケール配線と交差する第1のミクロスケール配線組であって、該第1のミクロスケール配線組とナノスケール配線との交差部は、複数のナノスケール配線の中から1または2以上のナノスケール配線をアドレス指定するアドレス指定位置を定める、第1のミクロスケール配線組と、

ナノスケール配線と交差する第2のミクロスケール配線組であって、該第2のミクロスケール配線組とナノスケール配線との交差部はメモリ位置を定める、第2のミクロスケール配線組と、

を有するメモリ配列が提供される。

複数のナノスケール配線層であって、ナノスケール配線の第1の層と、該第1の層と隣接するナノスケール配線の第2の層の交差部はメモリ位置を定める、複数のナノスケール配線層と、

ナノスケール配線の異なるナノスケール配線の層と接続された複数のミクロスケール接続部と、

を有する3次元メモリ配列において、

ナノスケール配線は、ナノスケール配線の軸方向に沿って分布する制御可能領域を有し、第1の制御可能領域組は第1の物理的特性を示し、第2の制御可能領域組は第1の物理的特性とは異なる第2の物理的特性を示すことを特徴とする3次元メモリ配列が提供される。

ミクロスケール配線を提供するステップと、

該ミクロスケール配線のアドレス位置を定めるステップと、

ミクロスケール配線の上部に整列された第1のナノスケール配線組を転写するステップと、

ミクロスケール配線および第1のナノスケール配線組の上部に、該第1のナノスケール配線組と直交するように整列された第2のナノスケール配線組を転写するステップと、

で構成される製造プロセスが提供される。

(確率的組立体)

ナノスケール配線の問題はそれらが極めて接近された間隔で設けられているため、パターン転写配線との直接的な接触で個々のナノワイヤを選択することは難しいことである。しかしながら現在、直交する1組の平行配線に区分化できないナノスケール配線を形成することは可能である。本発明の好適実施例によると、上述の図4および5に示された変調技術でコード化されたナノスケール配線は、最初に相互に混成され、ランダムな秩序のコード化ナノワイヤが形成され、さらに1組の平行配線として形成される。その結果、所与の配列から1組の配線が確率的に選択される。2002年6月25日の仮出願60/398,943において出願人は、ほぼ全てのコードが独立化され得る、そのようなナノスケール配線の十分に大きな集合体からコード化ナノスケール配線を確率的に選択する方法を示している。例えば同じコードを持つ配線数が106であり、その中に10の配線の小さな配列を形成するための、106の異なるコードのコード空間を考慮することができる。1012の全配線から各配線がランダムに選択される場合、全10配線が独立となる99.995%の確率がある。これは少なくとも9の独立配線を得る可能性はより高い。従ってコード化配線をランダムに選定することができ、所望の独立ナノスケールのアドレス指定を行うことができ、特定の配列に含まれるナノスケール配線を選定したいという要望を満たすことができる。

(位置調整)

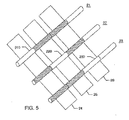

ミクロスケール配線とナノスケール配線間の位置調整は図5に示されている。実際には、ナノスケール配線を相互に完全に揃える方法はない。ナノスケール配線の位置を揃える方法はないが、制御ミクロスケール配線の幅(制御ビットピッチ)のばらつきによって、およびそのようなビットピッチの確率によって、それらは結局非整列となる。従って「ばらつき」および「確率」による非整列の組み合わせとして、各種非整列が生じる。

(制御ビットピッチのばらつきによる非整列)

制御ミクロスケール配線およびナノスケール配線が制御ビットピッチのばらつきによって非整列となった場合、1または2以上の制御ミクロスケール配線は、この非整列を緩和しないと、ナノスケール配線の対応する「1」または「0」ドープ領域のいかなる部分とも「交差」しない。

(ビットピッチの比率による非整列)

ミクロスケール配線でナノスケール配線のコード領域を制御するため、ミクロスケール配線のフィールドとナノスケール配線のドープされた制御可能領域間を重複させる必要がある。

(アドレス制御用のナノワイヤの利用)

別の実施例では、ナノスケール配線はナノスケール配線を制御するように提供され、前述のように全てがナノスケールシステムで構成される。これは、デコーダへのアドレス指定が、ナノPLAのようなナノスケール回路からされるときに有益である。

1)Wbitpitch+2* Woverlap<2*Wbitpitchの長さのコード領域で制御されるナノワイヤを提供するステップ、

2)制御されるナノワイヤのコードを二重化、すなわち制御されるナノワイヤの制御領域を元の間隔の2倍に広げるステップ

3)制御ナノワイヤのコードを用いて、制御されるナノワイヤのコードに生じる「11」を「01」または「10」で置き換え、そのコードを回転したコードを提供するステップ。

(メモリへの利用)

さらに、上述のデコーダによってアドレス指定されるプログラム化メモリが提供される。ナノスケール配線配列の交差部に非揮発性メモリビットを設置する技術は、本願の背景で示したように、既に従来技術として知られている。

(ナノスケールメモリ配列)

図11には、変調ドープアドレスデコーダを用いてインターフェース化されるナノスケールメモリ配列を示す。図には明確化のため数本のナノスケール配線しか示されていない。特に6×6のナノスケール配線配列が示されている。通常配列は、24−30のミクロスケール配線のみによってアドレス指定される100−1000ナノスケール配線を有する。

(ハイブリッド制御メモリ)

上述のメモリの欠点は、メモリが極めて広いアドレス空間を必要とし、極めて大きなコード化ナノスケール配線集合を必要とすることである。例えば500×500の配列の場合、25百万のナノスケール配線のコード空間が必要となる。

(1次元メモリ)

図11の実施例は2次元メモリである。本願ではさらに、図16に示す単一のナノワイヤ層を用いる1次元メモリの実施例を提供する。

(3次元メモリ)

図17および18には、それぞれ3次元メモリの実施例の概略断面図および斜視図を示す。ミクロスケール配線201−204には、第1のナノスケール配線層の組205−207、およびこれと直交する第2のナノスケール配線層の組208−210が設けられる。図11の2次元の場合と同様に、各層のデコード領域が領域211−214に設けられる。領域211−214におけるナノスケール層は酸化層215で被覆され、変調ドープデコード領域が被覆される。

(半径方向変調ドープ)

ナノスケール配線の軸に沿った変調ドープに加えて、ナノスケール配線の半径方向に沿って変調ドープを行う技術が、Lincoln J. Lauhon、Mark S. Gudiksen、Deli Wang、Charles M. Lieberの「エピタキシャルコア殻およびコア−多殻ナノワイヤへテロ構造」、ネーチャー、420巻、p57−612002年11月、で知られている。

(図11のメモリの実施例におけるナノスケール配線構造)

図11に示すナノスケール配線72のような垂直ナノスケール配線を参照することにより、いくつかの別個の領域が観測される:

a)ミクロスケール配線77に電気的に接続される領域、

b)(絶縁体83のような)絶縁体によってミクロスケールアドレス配線CA0−CA3から分離する必要のあるアドレス領域、

c)水平ナノスケール配線61−66と交差する領域のような、記録または読み出し情報を含むコア領域、

d)ミクロスケール配線85から絶縁体によって分離する必要のある制御可能領域、

e)ミクロスケール配線79に電気的に接続される領域。

(軸方向にドープされたナノスケール配線の製作プロセス)

軸方向にドープされたナノスケール配線の場合、上述のように個々の交点はメモリコアとして利用される。軸方向ドープナノスケール配線を有するメモリの製作は、以下のステップからなる。

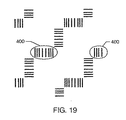

1)シリコンウェハのパターン転写処理により、複数のミクロスケール配線を得るステップ、

2)ミクロスケール配線のアドレス指定部分に酸化物を形成するステップ。図19には、製作プロセスの最初の2のステップ後のミクロワイヤの可能な配置を示す。

3)第1の軸方向ドープナノスケール配線組を混成するステップ。ナノスケール配線同士の接触が生じないように、ナノスケール配線を混成するには、図2の酸化層10のような酸化層を各ナノワイヤの周囲に成長させる。酸化層は、相互に平行に配置された2のナノスケール配線を電気伝導領域に接触しないようにし、ダイオード接続ではなくFET制御が可能となるように酸化バリアとして機能する。

4)第1のナノスケール配線組を配列して、配列された第1の組をミクロスケール配線上に転写させるステップ。図20には4つのステップ後のチップ状態を示す。ナノスケール配線の配列は、例えばラングミュア−ブロドゲットフロー(LBフロー)技術によって行われる。この技術は、例えばUlman A.「有機超薄膜の導入:ラングミュア−ブロドゲットから自己組織化まで」アカデミックプレス、ニューヨーク1991年、またはAlbrecht O.、Matsuda H.、Eguchi K.、Nakagiri T.の「試験的形成のためのLB成膜機構の構成と利用」Thin Solid Film、284/285巻、15、9月1996年、p152−156参照。LBフローは基板上のナノスケール配線の緻密な配線を可能にする。

5)パターン転写エッチング技術によって、構造内に配列軸に対して垂直な遮断部を得るステップ。図21には5のステップ後の製作状態が示されている。

6)第2の軸方向ドープナノスケール配線組を混成するステップ。

7)第2のナノスケール配線組を配列して、回路上に設置された第2の組を、図22に示すように、第1のナノスケール配線組と直交するように転写させるステップ。さらに分子層(図示されていない)がナノワイヤの直交組間に設置される。そのような層は、例えばChristopher L. Brown、Ulrich Jonas、Jon A. Preece、Helmut Ringsdrf、Markus Seitz、J. Fraser Stoddartの「ラングミュア膜およびラングミュア−ブロッドゲット多層膜への2−カテナンの導入。分子情報貯蔵材料の可能な対応」Langmuir16(4)、1924−1930、2000年に示されている。

8)パターン転写エッチング技術によって、構造内に配列軸に対して垂直な遮断部を得るステップ。図23参照。

9)図24のように、オーミック接続の領域に金属を被覆させるステップ。図25の構造が得られる。

(軸方向および半径方向にドープされるナノスケール配線の製作プロセス)

軸方向および半径方向の双方にドープされたナノスケール配線の場合も、製作プロセスは上述のプロセスと同様である。上述の図19−25を参照のこと。しかしながら直行する1組のナノワイヤの間に分子層を設置する必要はない。

Claims (47)

- 第1のナノスケール配線組と、

該第1のナノスケール配線組と交差する第2のナノスケール配線組であって、前記第1の組と第2の組の間の交差部がメモリ配置を定める、第2のナノスケール配線組と、

を有するメモリ配列において、

当該メモリ配置は、前記第1のナノスケール配線組のうちいずれか一方のナノスケール配線と、前記第2のナノスケール配線組のうちいずれか一方のナノスケール配線とを選択することによりアドレス指定され、前記第1のナノスケール配線組および前記第2のナノスケール配線組は、ナノスケール配線の軸方向に沿って分布する制御可能領域を持ち、第1の制御可能領域組は第1の物理的特性を示し、第2の制御可能領域組は前記第1の制御可能領域組とは異なる第2の物理的特性を示し、さらに

第1の複数のアドレス配線であって、該第1の複数のアドレス配線の各々は、前記第1のナノスケール配線組の一連の領域に接続された、第1の複数のアドレス配線と、

第2の複数のアドレス配線であって、前記第2の複数のアドレス配線の各々は、前記第2のナノスケール配線組の一連の領域に接続された、第2の複数のアドレス配線と、

を有するメモリ配列。 - 第1の組の各領域が第1の閾値よりも小さな値の信号で制御された場合、または信号で制御されない場合には、前記第1の制御可能領域組において、ナノスケール配線に沿った電気伝導が可能となることを特徴とする請求項1に記載のメモリ配列。

- 第1の組の各領域が第1の閾値よりも大きな値の信号で制御された場合、前記第1の制御可能領域組において、ナノスケール配線に沿った電気伝導が可能となることを特徴とする請求項1に記載のメモリ配列。

- 第1の物理的特性と第2の物理的特性間の差異は、前記制御可能領域のドーピング量の差に起因することを特徴とする請求項1に記載のメモリ配列。

- 第1の物理的特性と第2の物理的特性間の差異は、制御可能領域の材質の差に起因することを特徴とする請求項1に記載のメモリ配列。

- アドレス配線は、メモリを複数の状態のいずれかに設定することが可能な、請求項1に記載のメモリ配列。

- アドレス配線は、メモリを読み出し状態にすることが可能な、請求項1に記載のメモリ配列。

- メモリが読み出し状態のときにメモリ位置がアドレス指定されることを特徴とする請求項1に記載のメモリ配列。

- メモリが記録状態のときにメモリ位置がアドレス指定されることを特徴とする請求項1に記載のメモリ配列。

- さらに、オーム接続として作用するミクロスケール配線を有することを特徴とする請求項1に記載のメモリ配列。

- さらに、ナノスケール配線に信号を伝送しないミクロスケール配線を有することを特徴とする請求項1に記載のメモリ配列。

- ミクロスケール配線は、FETの制御可能領域を制御することを特徴とする請求項1に記載のメモリ配列。

- メモリ位置は、第1の組および第2の組の間のプログラム化ダイオード式交差部によって定められることを特徴とする請求項1に記載のメモリ配列。

- メモリ位置は、第1の組および第2の組の間のFET式交差部によって定められることを特徴とする請求項1に記載のメモリ配列。

- ナノスケール配線の第1の組および第2の組のうち、いずれかの組のナノスケール配線は、ナノスケール配線の半径方向に沿って分布する制御可能ドープ領域を有し、該半径方向に分布する制御可能ドープ領域は、メモリ位置で情報を記憶させることが可能な、請求項1に記載のメモリ配列。

- 第1および第2の組は、異なる材料で構成されることを特徴とする請求項1に記載のメモリ配列。

- アドレス配線はミクロスケール配線であることを特徴とする請求項1に記載のメモリ配列。

- アドレス配線はナノスケール配線であることを特徴とする請求項1に記載のメモリ配列。

- ナノスケール配線の第1の組は、より大きなナノスケール配線組の一部であり、前記第1の組は、オーム接続として作用するミクロスケール配線によって前記より大きな組から選択されることを特徴とする請求項1に記載のメモリ配列。

- ナノスケール配線の第1の組および第2の組は、より大きなナノスケール配線組の一部であり、前記第1および第2の組は、オーム接続として作用するミクロスケール配線によって前記より大きな組から選択されることを特徴とする請求項1に記載のメモリ配列。

- 複数のナノスケール配線の中から一つのナノスケール配線を選択する回路において、

ミクロスケールオーム接続であって、各オーム接続は複数のナノスケール配線の異なるサブ集合に接続され複数のナノスケール配線の中の特定のサブ集合を選択する、ミクロスケールオーム接続と、

複数のナノスケール配線の異なるサブ集合に接続され、一旦特定のサブ集合が選択された場合、ナノスケール配線の特定のサブ集合の中からナノスケール配線を選択するアドレス配線と、

を有する回路。 - アドレス配線はミクロスケール配線であることを特徴とする請求項21に記載の回路。

- アドレス配線はナノスケール配線であることを特徴とする請求項21に記載の回路。

- ミクロスケールオーム接続は、ミクロスケールオーム接続同士間の間隔が、アドレス指定されないナノワイヤのサブパターン転写寸法間隔よりも小さくなるように設計されることを特徴とする請求項21に記載の回路。

- ミクロスケールオーム接続は互いに千鳥状に設置されることを特徴とする請求項21または24に記載の回路。

- 複数のナノスケール配線と、

該ナノスケール配線と交差する第1のミクロスケール配線組であって、該第1のミクロスケール配線組とナノスケール配線との交差部は、複数のナノスケール配線の中から1または2以上のナノスケール配線をアドレス指定するアドレス指定位置を定める、第1のミクロスケール配線組と、

ナノスケール配線と交差する第2のミクロスケール配線組であって、該第2のミクロスケール配線組とナノスケール配線との交差部はメモリ位置を定める、第2のミクロスケール配線組と、

を有するメモリ配列。 - メモリ位置は、1のナノスケール配線と、第2のミクロスケール配線の組のうち1のミクロスケール配線とを選定することにより選択されることを特徴とする請求項26に記載のメモリ配列。

- ナノスケール配線は、ナノスケール配線の軸方向に沿って分布する制御可能領域を有し、第1の制御可能領域組は、第1の物理的特性を持ち、第2の制御可能領域組は、第1の物理的特性とは異なる第2の物理的特性を持つことを特徴とする請求項26に記載のメモリ配列。

- 第1の物理的特性と第2の物理的特性の間の差異は、前記制御可能領域のドーピング量の差に基づくことを特徴とする請求項26に記載のメモリ配列。

- 第1の物理的特性と第2の物理的特性の間の差異は、前記制御可能領域の材質の差に基づくことを特徴とする請求項28に記載のメモリ配列。

- 第1の制御可能領域組によって、第1の組の各領域が第1の閾値よりも小さな値の信号で制御された場合、あるいは信号で制御されない場合には、ナノスケール配線に沿った電気伝導が可能となることを特徴とする請求項28に記載のメモリ配列。

- 第1の制御可能領域組によって、第1の組の各領域が第1の閾値よりも大きな値の信号で制御された場合、ナノスケール配線に沿った電気伝導が可能となることを特徴とする請求項28に記載のメモリ配列。

- メモリが読み出し状態のときにメモリ位置がアドレス指定されることを特徴とする請求項26に記載のメモリ配列。

- メモリが記録状態のときにメモリ位置がアドレス指定されることを特徴とする請求項26に記載のメモリ配列。

- さらに、ミクロスケールオーム接続を有し、各オーム接続は、複数のナノスケール配線のうち別個のサブ集合に接続され、複数のナノスケール配線の中から特定のサブ集合を選択することを特徴とする請求項26に記載のメモリ配列。

- ミクロスケールオーム接続は、互いに千鳥状に設置されることを特徴とする請求項35に記載のメモリ配列。

- 複数のナノスケール配線層であって、ナノスケール配線の第1の層と、該第1の層と隣接するナノスケール配線の第2の層の交差部はメモリ位置を定める、複数のナノスケール配線層と、

ナノスケール配線の異なるナノスケール配線の層と接続された複数のミクロスケール接続部と、

を有する3次元メモリ配列において、

ナノスケール配線は、ナノスケール配線の軸方向に沿って分布する制御可能領域を有し、第1の制御可能領域組は第1の物理的特性を示し、第2の制御可能領域組は第1の物理的特性とは異なる第2の物理的特性を示すことを特徴とする3次元メモリ配列。 - ナノスケール配線層は隣接する層の組が繰り返されるように設置され、隣接する層の組は、

メモリ位置を定めるナノスケール配線の第1の層と、

メモリ位置を定めるナノスケール配線の第2の層と、

ナノスケール配線を絶縁する層と

を有することを特徴とする請求項37に記載の3次元メモリ配列。 - 異なる層上に配置され、ミクロスケール接続を共有するナノスケール配線は、互いに独立にアドレス指定されることを特徴とする請求項37に記載の3次元メモリ配列。

- ナノスケール配線群は独立してアドレス指定され、配列内のナノワイヤの大部分は、全ナノスケール配線群に含まれることを特徴とする請求項37に記載の3次元メモリ配列。

- ミクロスケール配線とナノスケール配線を有するロジック配置の製造プロセスであって、

ミクロスケール配線を提供するステップと、

該ミクロスケール配線のアドレス位置を定めるステップと、

ミクロスケール配線の上部に整列された第1のナノスケール配線組を転写するステップと、

ミクロスケール配線および第1のナノスケール配線組の上部に、該第1のナノスケール配線組と直交するように整列された第2のナノスケール配線組を転写するステップと、

で構成される製造プロセス。 - ナノスケール配線の第1の組と第2の組の位置合わせは、LBフロー技術によって行われることを特徴とする請求項41に記載のプロセス。

- さらに、ナノスケール配線の軸方向にドーピングを行うステップを有することを特徴とする請求項41に記載のプロセス。

- さらに、ナノスケール配線の半径方向にドーピングを行うステップを有することを特徴とする請求項41に記載のプロセス。

- さらに、ナノスケール配線の軸方向および半径方向にドーピングを行うステップを有することを特徴とする請求項41に記載のプロセス。

- さらに、ナノスケール配線から半径方向にドープされた部分をエッチング除去するステップを有することを特徴とする請求項45に記載のプロセス。

- さらに、ナノスケール配線内の遮断部をエッチング除去するステップを有することを特徴とする請求項41に記載のプロセス。

Applications Claiming Priority (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US39894302P | 2002-07-25 | 2002-07-25 | |

| US40039402P | 2002-08-01 | 2002-08-01 | |

| US41517602P | 2002-09-30 | 2002-09-30 | |

| US42901002P | 2002-11-25 | 2002-11-25 | |

| US44199503P | 2003-01-23 | 2003-01-23 | |

| US46535703P | 2003-04-25 | 2003-04-25 | |

| US46738803P | 2003-05-02 | 2003-05-02 | |

| PCT/US2003/023199 WO2004034467A2 (en) | 2002-07-25 | 2003-07-24 | Sublithographic nanoscale memory architecture |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005539404A true JP2005539404A (ja) | 2005-12-22 |

| JP2005539404A5 JP2005539404A5 (ja) | 2006-09-07 |

Family

ID=32097212

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005508519A Pending JP2006512782A (ja) | 2002-07-25 | 2003-07-24 | サブパターン転写ナノスケールインターフェースの確率的組立体 |

| JP2005501049A Pending JP2005539404A (ja) | 2002-07-25 | 2003-07-24 | サブパターン転写ナノスケールメモリ構造 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005508519A Pending JP2006512782A (ja) | 2002-07-25 | 2003-07-24 | サブパターン転写ナノスケールインターフェースの確率的組立体 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US6963077B2 (ja) |

| EP (3) | EP1758126A3 (ja) |

| JP (2) | JP2006512782A (ja) |

| AT (2) | ATE360873T1 (ja) |

| AU (2) | AU2003298529A1 (ja) |

| DE (2) | DE60325903D1 (ja) |

| WO (2) | WO2004061859A2 (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009525193A (ja) * | 2006-01-27 | 2009-07-09 | ヒューレット−パッカード デベロップメント カンパニー エル.ピー. | ミックススケール電子界面 |

| KR101409310B1 (ko) * | 2007-03-28 | 2014-06-18 | 휴렛-팩커드 디벨롭먼트 컴퍼니, 엘.피. | 3차원 크로스바 어레이 접합에 저장된 정보를 판독 및 기록하기 위한 3차원 크로스바 어레이 시스템 및 방법 |

| JP2018006757A (ja) * | 2016-07-01 | 2018-01-11 | ツィンファ ユニバーシティ | 半導体素子 |

| JP2018006754A (ja) * | 2016-07-01 | 2018-01-11 | ツィンファ ユニバーシティ | ナノヘテロ接合構造 |

| JP2018006755A (ja) * | 2016-07-01 | 2018-01-11 | ツィンファ ユニバーシティ | ナノトランジスタ |

| JP2018006756A (ja) * | 2016-07-01 | 2018-01-11 | ツィンファ ユニバーシティ | ナノヘテロ接合構造 |

Families Citing this family (67)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7301199B2 (en) * | 2000-08-22 | 2007-11-27 | President And Fellows Of Harvard College | Nanoscale wires and related devices |

| US20060175601A1 (en) * | 2000-08-22 | 2006-08-10 | President And Fellows Of Harvard College | Nanoscale wires and related devices |

| KR100995457B1 (ko) * | 2000-08-22 | 2010-11-18 | 프레지던트 앤드 펠로우즈 오브 하버드 칼리지 | 나노센서 제조 방법 |

| DE60135775D1 (de) * | 2000-12-11 | 2008-10-23 | Harvard College | Vorrichtung enthaltend nanosensoren zur ekennung eines analyten und verfahren zu ihrer herstellung |

| US7073157B2 (en) | 2002-01-18 | 2006-07-04 | California Institute Of Technology | Array-based architecture for molecular electronics |

| US6963077B2 (en) | 2002-07-25 | 2005-11-08 | California Institute Of Technology | Sublithographic nanoscale memory architecture |

| EP1388521B1 (en) * | 2002-08-08 | 2006-06-07 | Sony Deutschland GmbH | Method for preparing a nanowire crossbar structure |

| AU2003283973B2 (en) * | 2002-09-30 | 2008-10-30 | Oned Material Llc | Large-area nanoenabled macroelectronic substrates and uses therefor |

| US7135728B2 (en) * | 2002-09-30 | 2006-11-14 | Nanosys, Inc. | Large-area nanoenabled macroelectronic substrates and uses therefor |

| WO2004109706A2 (en) | 2003-06-02 | 2004-12-16 | California Institute Of Technology | Nanoscale wire-based sublithographic programmable logic arrays |

| US7242601B2 (en) | 2003-06-02 | 2007-07-10 | California Institute Of Technology | Deterministic addressing of nanoscale devices assembled at sublithographic pitches |

| WO2005029498A2 (en) | 2003-07-24 | 2005-03-31 | California Institute Of Technology | Nanoscale wire coding for stochastic assembly |

| CN1868002B (zh) * | 2003-08-13 | 2011-12-14 | 南泰若股份有限公司 | 具有多个控件的基于纳米管的开关元件及由其制成的电路 |

| US7018549B2 (en) * | 2003-12-29 | 2006-03-28 | Intel Corporation | Method of fabricating multiple nanowires of uniform length from a single catalytic nanoparticle |

| US20090227107A9 (en) * | 2004-02-13 | 2009-09-10 | President And Fellows Of Havard College | Nanostructures Containing Metal Semiconductor Compounds |

| US7310004B2 (en) | 2004-05-28 | 2007-12-18 | California Institute Of Technology | Apparatus and method of interconnecting nanoscale programmable logic array clusters |

| WO2006107312A1 (en) * | 2004-06-15 | 2006-10-12 | President And Fellows Of Harvard College | Nanosensors |

| JP2008505476A (ja) * | 2004-06-30 | 2008-02-21 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | ナノワイヤによってコンタクトがとられる導電性材料の層を有する電子装置を製造する方法 |

| WO2006137833A1 (en) * | 2004-08-13 | 2006-12-28 | University Of Florida Research Foundation, Inc. | Nanoscale content-addressable memory |

| US7365632B2 (en) * | 2004-09-21 | 2008-04-29 | Nantero, Inc. | Resistive elements using carbon nanotubes |

| EP1831973A2 (en) * | 2004-12-06 | 2007-09-12 | The President and Fellows of Harvard College | Nanoscale wire-based data storage |

| WO2006084128A2 (en) * | 2005-02-04 | 2006-08-10 | Brown University | Apparatus, method and computer program product providing radial addressing of nanowires |

| US8883568B2 (en) | 2008-06-10 | 2014-11-11 | Brown University Research Foundation | Method providing radial addressing of nanowires |

| US7211503B2 (en) * | 2005-02-24 | 2007-05-01 | Hewlett-Packard Development Company, L.P. | Electronic devices fabricated by use of random connections |

| DE102005016244A1 (de) * | 2005-04-08 | 2006-10-19 | Infineon Technologies Ag | Speicherzelle, Speichereinrichtung und Verfahren zu deren Herstellung |

| US7786467B2 (en) * | 2005-04-25 | 2010-08-31 | Hewlett-Packard Development Company, L.P. | Three-dimensional nanoscale crossbars |

| US20100227382A1 (en) * | 2005-05-25 | 2010-09-09 | President And Fellows Of Harvard College | Nanoscale sensors |

| WO2006132659A2 (en) | 2005-06-06 | 2006-12-14 | President And Fellows Of Harvard College | Nanowire heterostructures |

| WO2007002297A2 (en) * | 2005-06-24 | 2007-01-04 | Crafts Douglas E | Temporary planar electrical contact device and method using vertically-compressible nanotube contact structures |

| US9159417B2 (en) * | 2005-12-20 | 2015-10-13 | The Invention Science Fund I, Llc | Deletable nanotube circuit |

| US7989797B2 (en) * | 2005-12-20 | 2011-08-02 | The Invention Science Fund I, Llc | Connectible nanotube circuit |

| US7786465B2 (en) * | 2005-12-20 | 2010-08-31 | Invention Science Fund 1, Llc | Deletable nanotube circuit |

| US7696505B2 (en) * | 2005-12-20 | 2010-04-13 | Searete Llc | Connectible nanotube circuit |

| US20070233761A1 (en) * | 2006-04-03 | 2007-10-04 | Mouttet Blaise L | Crossbar arithmetic processor |

| US8183554B2 (en) * | 2006-04-03 | 2012-05-22 | Blaise Laurent Mouttet | Symmetrical programmable memresistor crossbar structure |

| US7576565B2 (en) * | 2006-04-03 | 2009-08-18 | Blaise Laurent Mouttet | Crossbar waveform driver circuit |

| US7302513B2 (en) * | 2006-04-03 | 2007-11-27 | Blaise Laurent Mouttet | Programmable crossbar signal processor |

| US9965251B2 (en) * | 2006-04-03 | 2018-05-08 | Blaise Laurent Mouttet | Crossbar arithmetic and summation processor |

| WO2008051316A2 (en) | 2006-06-12 | 2008-05-02 | President And Fellows Of Harvard College | Nanosensors and related technologies |

| US7763932B2 (en) * | 2006-06-29 | 2010-07-27 | International Business Machines Corporation | Multi-bit high-density memory device and architecture and method of fabricating multi-bit high-density memory devices |

| TWI307677B (en) * | 2006-07-18 | 2009-03-21 | Applied Res Lab | Method and device for fabricating nano-structure with patterned particle beam |

| US7393739B2 (en) * | 2006-08-30 | 2008-07-01 | International Business Machines Corporation | Demultiplexers using transistors for accessing memory cell arrays |

| US8058640B2 (en) | 2006-09-11 | 2011-11-15 | President And Fellows Of Harvard College | Branched nanoscale wires |

| KR20090075819A (ko) * | 2006-09-19 | 2009-07-09 | 큐나노 에이비 | 나노스케일 전계 효과 트랜지스터의 조립체 |

| US7778061B2 (en) * | 2006-10-16 | 2010-08-17 | Hewlett-Packard Development Company, L.P. | Crossbar-memory systems and methods for writing to and reading from crossbar memory junctions of crossbar-memory systems |

| US8130007B2 (en) * | 2006-10-16 | 2012-03-06 | Formfactor, Inc. | Probe card assembly with carbon nanotube probes having a spring mechanism therein |

| US7968474B2 (en) | 2006-11-09 | 2011-06-28 | Nanosys, Inc. | Methods for nanowire alignment and deposition |

| US8575663B2 (en) | 2006-11-22 | 2013-11-05 | President And Fellows Of Harvard College | High-sensitivity nanoscale wire sensors |

| US9806273B2 (en) * | 2007-01-03 | 2017-10-31 | The United States Of America As Represented By The Secretary Of The Army | Field effect transistor array using single wall carbon nano-tubes |

| US7608854B2 (en) * | 2007-01-29 | 2009-10-27 | Hewlett-Packard Development Company, L.P. | Electronic device and method of making the same |

| US7872334B2 (en) * | 2007-05-04 | 2011-01-18 | International Business Machines Corporation | Carbon nanotube diodes and electrostatic discharge circuits and methods |

| US7492624B2 (en) * | 2007-06-29 | 2009-02-17 | Stmicroelectronics S.R.L. | Method and device for demultiplexing a crossbar non-volatile memory |

| EP2262723A4 (en) * | 2008-04-15 | 2014-05-14 | Qunano Ab | DEVICES FOR NANOFIL WINDING GATES |

| KR20110086089A (ko) * | 2008-10-20 | 2011-07-27 | 더 리젠츠 오브 더 유니버시티 오브 미시건 | 실리콘계 나노스케일 크로스바 메모리 |

| WO2010126468A1 (en) * | 2009-04-30 | 2010-11-04 | Hewlett-Packard Development Company, L.P. | Dense nanoscale logic circuitry |

| JP2012528020A (ja) | 2009-05-26 | 2012-11-12 | ナノシス・インク. | ナノワイヤおよび他のデバイスの電場沈着のための方法およびシステム |

| US9297796B2 (en) | 2009-09-24 | 2016-03-29 | President And Fellows Of Harvard College | Bent nanowires and related probing of species |

| KR101161060B1 (ko) * | 2009-11-30 | 2012-06-29 | 서강대학교산학협력단 | 나노입자를 기둥형태로 조직화시키기 위한 배열장치 및 그 배열방법 |

| US9181089B2 (en) | 2010-01-15 | 2015-11-10 | Board Of Regents Of The University Of Texas System | Carbon nanotube crossbar based nano-architecture |

| WO2011093863A1 (en) | 2010-01-29 | 2011-08-04 | Hewlett-Packard Development Company, L.P. | Three dimensional multilayer circuit |

| US7982504B1 (en) | 2010-01-29 | 2011-07-19 | Hewlett Packard Development Company, L.P. | Interconnection architecture for multilayer circuits |

| US9368599B2 (en) * | 2010-06-22 | 2016-06-14 | International Business Machines Corporation | Graphene/nanostructure FET with self-aligned contact and gate |

| US8872176B2 (en) | 2010-10-06 | 2014-10-28 | Formfactor, Inc. | Elastic encapsulated carbon nanotube based electrical contacts |

| US9273004B2 (en) | 2011-09-29 | 2016-03-01 | International Business Machines Corporation | Selective placement of carbon nanotubes via coulombic attraction of oppositely charged carbon nanotubes and self-assembled monolayers |

| US9442695B2 (en) | 2014-05-02 | 2016-09-13 | International Business Machines Corporation | Random bit generator based on nanomaterials |

| US9720772B2 (en) * | 2015-03-04 | 2017-08-01 | Kabushiki Kaisha Toshiba | Memory system, method for controlling magnetic memory, and device for controlling magnetic memory |

| CN112585152A (zh) * | 2018-07-11 | 2021-03-30 | 加利福尼亚大学董事会 | 基于核酸的电学上可读的只读存储器 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6256767B1 (en) * | 1999-03-29 | 2001-07-03 | Hewlett-Packard Company | Demultiplexer for a molecular wire crossbar network (MWCN DEMUX) |

| WO2002003482A1 (de) * | 2000-07-04 | 2002-01-10 | Infineon Technologies Ag | Feldeffekttransistor |

| US6385075B1 (en) * | 2001-06-05 | 2002-05-07 | Hewlett-Packard Company | Parallel access of cross-point diode memory arrays |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4658329B2 (ja) * | 1999-02-12 | 2011-03-23 | ボード オブ トラスティーズ,オブ ミシガン ステイト ユニバーシティ | 帯電粒子を収容するナノカプセル、その用法及び形成法 |

| US6314019B1 (en) * | 1999-03-29 | 2001-11-06 | Hewlett-Packard Company | Molecular-wire crossbar interconnect (MWCI) for signal routing and communications |

| US6128214A (en) * | 1999-03-29 | 2000-10-03 | Hewlett-Packard | Molecular wire crossbar memory |

| US6383784B1 (en) * | 1999-12-03 | 2002-05-07 | City Of Hope | Construction of nucleoprotein based assemblies comprising addressable components for nanoscale assembly and nanoprocessors |

| US7301199B2 (en) * | 2000-08-22 | 2007-11-27 | President And Fellows Of Harvard College | Nanoscale wires and related devices |

| AU2001297881A1 (en) | 2000-11-01 | 2003-01-02 | James J. Myrick | Nanoelectronic interconnection and addressing |

| JP2004532133A (ja) * | 2001-03-30 | 2004-10-21 | ザ・リージェンツ・オブ・ザ・ユニバーシティ・オブ・カリフォルニア | ナノ構造及びナノワイヤーの組立方法並びにそれらから組立てられた装置 |

| US6777982B2 (en) * | 2001-04-03 | 2004-08-17 | Carnegie Mellon University | Molecular scale latch and associated clocking scheme to provide gain, memory and I/O isolation |

| US6706402B2 (en) * | 2001-07-25 | 2004-03-16 | Nantero, Inc. | Nanotube films and articles |

| US7073157B2 (en) * | 2002-01-18 | 2006-07-04 | California Institute Of Technology | Array-based architecture for molecular electronics |

| US6760245B2 (en) * | 2002-05-01 | 2004-07-06 | Hewlett-Packard Development Company, L.P. | Molecular wire crossbar flash memory |

| US6963077B2 (en) * | 2002-07-25 | 2005-11-08 | California Institute Of Technology | Sublithographic nanoscale memory architecture |

| US6682951B1 (en) * | 2002-09-26 | 2004-01-27 | International Business Machines Corporation | Arrangements of microscopic particles for performing logic computations, and method of use |

-

2003

- 2003-07-24 US US10/627,406 patent/US6963077B2/en not_active Expired - Fee Related

- 2003-07-24 DE DE60325903T patent/DE60325903D1/de not_active Expired - Lifetime

- 2003-07-24 EP EP06022522A patent/EP1758126A3/en not_active Withdrawn

- 2003-07-24 AT AT03796282T patent/ATE360873T1/de not_active IP Right Cessation

- 2003-07-24 JP JP2005508519A patent/JP2006512782A/ja active Pending

- 2003-07-24 AT AT05025371T patent/ATE421147T1/de not_active IP Right Cessation

- 2003-07-24 US US10/627,405 patent/US6900479B2/en not_active Expired - Lifetime

- 2003-07-24 EP EP03796281A patent/EP1525585A2/en not_active Withdrawn

- 2003-07-24 WO PCT/US2003/023198 patent/WO2004061859A2/en active Application Filing

- 2003-07-24 DE DE60313462T patent/DE60313462T2/de not_active Expired - Lifetime

- 2003-07-24 WO PCT/US2003/023199 patent/WO2004034467A2/en active IP Right Grant

- 2003-07-24 EP EP03796282A patent/EP1525586B1/en not_active Expired - Lifetime

- 2003-07-24 AU AU2003298529A patent/AU2003298529A1/en not_active Abandoned

- 2003-07-24 JP JP2005501049A patent/JP2005539404A/ja active Pending

- 2003-07-24 AU AU2003298530A patent/AU2003298530A1/en not_active Abandoned

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6256767B1 (en) * | 1999-03-29 | 2001-07-03 | Hewlett-Packard Company | Demultiplexer for a molecular wire crossbar network (MWCN DEMUX) |

| WO2002003482A1 (de) * | 2000-07-04 | 2002-01-10 | Infineon Technologies Ag | Feldeffekttransistor |

| JP2004503097A (ja) * | 2000-07-04 | 2004-01-29 | インフィネオン テクノロジーズ アクチエンゲゼルシャフト | 電界効果トランジスタ |

| US6385075B1 (en) * | 2001-06-05 | 2002-05-07 | Hewlett-Packard Company | Parallel access of cross-point diode memory arrays |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009525193A (ja) * | 2006-01-27 | 2009-07-09 | ヒューレット−パッカード デベロップメント カンパニー エル.ピー. | ミックススケール電子界面 |

| KR101409310B1 (ko) * | 2007-03-28 | 2014-06-18 | 휴렛-팩커드 디벨롭먼트 컴퍼니, 엘.피. | 3차원 크로스바 어레이 접합에 저장된 정보를 판독 및 기록하기 위한 3차원 크로스바 어레이 시스템 및 방법 |

| JP2018006757A (ja) * | 2016-07-01 | 2018-01-11 | ツィンファ ユニバーシティ | 半導体素子 |

| JP2018006754A (ja) * | 2016-07-01 | 2018-01-11 | ツィンファ ユニバーシティ | ナノヘテロ接合構造 |

| JP2018006755A (ja) * | 2016-07-01 | 2018-01-11 | ツィンファ ユニバーシティ | ナノトランジスタ |

| JP2018006756A (ja) * | 2016-07-01 | 2018-01-11 | ツィンファ ユニバーシティ | ナノヘテロ接合構造 |

Also Published As

| Publication number | Publication date |

|---|---|

| US6900479B2 (en) | 2005-05-31 |

| EP1758126A3 (en) | 2007-03-14 |

| US20040113138A1 (en) | 2004-06-17 |

| DE60325903D1 (de) | 2009-03-05 |

| AU2003298529A8 (en) | 2004-07-29 |

| JP2006512782A (ja) | 2006-04-13 |

| WO2004034467A2 (en) | 2004-04-22 |

| DE60313462T2 (de) | 2008-01-03 |

| EP1758126A2 (en) | 2007-02-28 |

| US6963077B2 (en) | 2005-11-08 |

| ATE421147T1 (de) | 2009-01-15 |

| ATE360873T1 (de) | 2007-05-15 |

| WO2004061859A2 (en) | 2004-07-22 |

| EP1525586B1 (en) | 2007-04-25 |

| US20040113139A1 (en) | 2004-06-17 |

| EP1525586A2 (en) | 2005-04-27 |

| DE60313462D1 (de) | 2007-06-06 |

| AU2003298529A1 (en) | 2004-07-29 |

| WO2004061859A3 (en) | 2005-02-03 |

| EP1525585A2 (en) | 2005-04-27 |

| AU2003298530A8 (en) | 2004-05-04 |

| WO2004034467A3 (en) | 2004-08-26 |

| AU2003298530A1 (en) | 2004-05-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2005539404A (ja) | サブパターン転写ナノスケールメモリ構造 | |

| US6314019B1 (en) | Molecular-wire crossbar interconnect (MWCI) for signal routing and communications | |

| US8183665B2 (en) | Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same | |

| KR101409310B1 (ko) | 3차원 크로스바 어레이 접합에 저장된 정보를 판독 및 기록하기 위한 3차원 크로스바 어레이 시스템 및 방법 | |

| US7733685B2 (en) | Cross point memory cell with distributed diodes and method of making same | |

| US6760245B2 (en) | Molecular wire crossbar flash memory | |

| US7030408B1 (en) | Molecular wire transistor (MWT) | |

| US9443562B2 (en) | Connections for memory electrode lines | |

| Lu et al. | Nanoelectronics from the bottom up | |

| US7500213B2 (en) | Array-based architecture for molecular electronics | |

| JP2009521099A (ja) | ナノスケール電子スイッチングデバイスのための制御層 | |

| JP2010522991A (ja) | カーボンナノチューブ構造素子およびステアリング素子を含むメモリセルおよびそれを形成する方法 | |

| CN102150267A (zh) | 用于制造3d存储器阵列的共享x-线掩模和共享y-线掩模 | |

| US11723288B2 (en) | Quantum bit array | |

| US7692952B2 (en) | Nanoscale wire coding for stochastic assembly | |

| EP1630819B1 (en) | Three-dimensional memory array | |

| US7307345B2 (en) | Crossbar-array designs and wire addressing methods that tolerate misalignment of electrical components at wire overlap points | |

| US7242601B2 (en) | Deterministic addressing of nanoscale devices assembled at sublithographic pitches | |

| WO2010059153A1 (en) | Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same | |

| US7948271B1 (en) | Molecular wire crossbar logic (MWCL) | |

| Ojha | Nano-electronics and nano-computing: status, prospects, and challenges |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060719 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060719 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090306 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100302 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100727 |