JP2005295627A - 全波整流平滑回路およびスイッチング電源装置 - Google Patents

全波整流平滑回路およびスイッチング電源装置 Download PDFInfo

- Publication number

- JP2005295627A JP2005295627A JP2004104224A JP2004104224A JP2005295627A JP 2005295627 A JP2005295627 A JP 2005295627A JP 2004104224 A JP2004104224 A JP 2004104224A JP 2004104224 A JP2004104224 A JP 2004104224A JP 2005295627 A JP2005295627 A JP 2005295627A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- terminal

- capacitor

- power supply

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Rectifiers (AREA)

Abstract

【課題】より少ない損失で交流電圧を全波整流平滑化する。

【解決手段】全波整流平滑回路102の整流素子は、MOSFET181、183、231、および233の4つのnチャネルMOSFETにより構成される。MOSFET181はコンデンサ141の両端の電圧を分圧した駆動電圧によりスイッチングされ、MOSFET231はコンデンサ191の両端の電圧を分圧した駆動電圧によりスイッチングされる。MOSFET183は接続点A2と接続点A4の電圧を分圧した駆動電圧によりスイッチングされ、MOSFET233は接続点A1と接続点A4の電圧を分圧した駆動電圧によりスイッチングされる。本発明は、定電圧直流電源に適用することができる。

【選択図】図2

【解決手段】全波整流平滑回路102の整流素子は、MOSFET181、183、231、および233の4つのnチャネルMOSFETにより構成される。MOSFET181はコンデンサ141の両端の電圧を分圧した駆動電圧によりスイッチングされ、MOSFET231はコンデンサ191の両端の電圧を分圧した駆動電圧によりスイッチングされる。MOSFET183は接続点A2と接続点A4の電圧を分圧した駆動電圧によりスイッチングされ、MOSFET233は接続点A1と接続点A4の電圧を分圧した駆動電圧によりスイッチングされる。本発明は、定電圧直流電源に適用することができる。

【選択図】図2

Description

本発明は、全波整流平滑回路およびスイッチング電源装置に関し、特に、電力損失を低減するようにした全波整流平滑回路およびスイッチング電源装置に関する。

従来より、スイッチング電源装置の小型化、軽量化、および高効率化するために、スイッチング電源装置の電力の損失を低減することが重要な課題となっている。特に、スイッチング電源装置に設けられ、交流電圧を全波整流平滑化する全波整流平滑回路は電力の損失が大きく、全波整流平滑回路の損失の低減は重要な課題となっている。

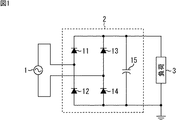

図1は、ダイオードを使用した一般的な全波整流平滑回路の例を示している。

全波整流平滑回路2は、ダイオード11乃至14およびコンデンサ15により構成される。ダイオード11のアノードは、ダイオード12のカソードに接続され、ダイオード11のカソードは、ダイオード13のカソードおよび平滑用のコンデンサ15の一端に接続されている。ダイオード12のアノードは、ダイオード14のアノードおよびコンデンサ15の他の一端に接続され、ダイオード13のアノードは、ダイオード14のカソードに接続されている。

交流電源1の一端はダイオード11のアノードに接続され、交流電源1の他の一端はダイオード14のカソードに接続され、交流電源1は全波整流平滑回路2に交流電圧を供給する。全波整流平滑回路2のコンデンサ15の両端には負荷3が接続され、全波整流平滑回路2の出力電圧、すなわちコンデンサ15の両端電圧が負荷3に印加される。

交流電源1から入力された交流電圧は、ダイオード11のアノードの電位がダイオード13のアノードの電位より高いとき、ダイオード11およびダイオード14を介してコンデンサ15の両端に印加され、ダイオード13のアノードの電位がダイオード11のアノードの電位より高いとき、ダイオード13およびダイオード12を介してコンデンサ15の両端に印加され、入力電圧が全波整流される。さらに、全波整流された電圧はコンデンサ15により平滑化され、脈流を含んだ直流電圧が負荷3に供給される。

しかしながら、ダイオードは順方向の電圧降下が大きく、電力の損失が大きいため、ダイオードの替わりに、オン抵抗が少ないpチャネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor)とnチャネルMOSFETを組み合わせて整流素子に用いた全波整流平滑回路が提案されている(例えば、特許文献1)。

特開平09−131064号公報

一般的に、同一の形状、耐圧、および定格電流のMOSFETでは、nチャネルMOSFETの方が、pチャネルMOSFETよりもオン抵抗が小さいため、全波整流平滑回路をより低損失化するためには、全ての整流素子をnチャネルMOSFETにすることが望ましい。しかしながら、特許文献1に記載されている発明では、pチャネルMOSFETとnチャネルMOSFETを組み合わせた全波整流平滑回路しか開示されていない。

また、特許文献1に記載された発明では、pチャネルMOSFETをnチャネルMOSFETに置き換えようとした場合、nチャネルMOSFETに駆動電圧を供給するためのチャージポンプ回路が必要となり、さらに、チャージポンプ回路に所定の電圧を入力する電源やチャージポンプ回路を入力電圧と同じ周波数で制御するための制御回路などが必要となり、電力の損失が大きくなるとともに、全波整流平滑回路が大きくなってしまうという課題があった。

本発明は、このような状況に鑑みてなされたものであり、全ての整流素子にnチャネルMOSFETを用いて、より少ない損失で入力された交流電圧を全波整流平滑化できるようにしたものである。

本発明の全波整流平滑回路は、交流電源から入力された交流電圧を全波整流平滑化する全波整流平滑回路であって、ソースが交流電源の第1の端子に接続された第1のnチャネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor)と、ドレインが交流電源の第1の端子に接続された第2のnチャネルMOSFETと、ドレインが第1のnチャンネルMOSFETのドレインに接続され、ソースが交流電源の第2の端子に接続された第3のnチャネルMOSFETと、ドレインが交流電源の第2の端子に接続され、ソースが第2のnチャネルMOSFETのソースに接続された第4のnチャネルMOSFETと、第1の端子が第3のnチャネルMOSFETのドレインと接続され、第2の端子が第4のnチャネルMOSFETのソースに接続され、第1乃至第4のnチャネルMOSFETにより全波整流された電圧を平滑化する第1のコンデンサと、第1のコンデンサの第1の端子と交流電源の第1の端子の間の電圧によりチャージされる第2のコンデンサと、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第2のコンデンサの両端の電圧を分圧した第1の駆動電圧を第1のnチャネルMOSFETに印加する第1の駆動回路と、交流電源の第2の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第2の駆動電圧を第2のnチャネルMOSFETに印加する第1の分圧回路と、第1のコンデンサの第1の端子と交流電源の第2の端子の間の電圧によりチャージされる第3のコンデンサと、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第3のコンデンサの両端の電圧を分圧した第3の駆動電圧を第3のnチャネルMOSFETに印加する第2の駆動回路と、交流電源の第1の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第4の駆動電圧を第4のnチャネルMOSFETに印加する第2の分圧回路とを含むことを特徴とする。

第1の駆動回路は、例えば、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧が所定の電圧になったときスイッチングするスイッチング素子を含み、スイッチング素子のオンまたはオフにより駆動電圧を制御するようにすることができる。また、第1の駆動回路は、例えば、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧を所定の電圧と比較して、第1の駆動電圧を出力するコンパレータにより構成される。

第2の駆動回路は、例えば、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧が所定の電圧になったときスイッチングするスイッチング素子を含み、スイッチング素子のオンまたはオフにより駆動電圧を制御するようにすることができる。また、第2の駆動回路は、例えば、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧を所定の電圧と比較して、第3の駆動電圧を出力するコンパレータにより構成される。

本発明の全波整流平滑回路によれば、第1のnチャネルMOSFETのソースが交流電源の第1の端子に接続され、第2のチャネルMOSFETのドレインが交流電源の第1の端子に接続され、第3のnチャネルMOSFETのドレインが第1のnチャンネルMOSFETのドレインに接続され、ソースが交流電源の第2の端子に接続され、第4のnチャネルMOSFETのドレインが交流電源の第2の端子に接続され、ソースが第2のnチャネルMOSFETのソースに接続され、第1のコンデンサの第1の端子が第3のnチャネルMOSFETのドレインと接続され、第2の端子が第4のnチャネルMOSFETのソースに接続され、第1乃至第4のnチャネルMOSFETにより全波整流された電圧が平滑化され、第2のコンデンサが第1のコンデンサの第1の端子と交流電源の第1の端子の間の電圧によりチャージされ、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第2のコンデンサの両端の電圧を分圧した第1の駆動電圧が第1のnチャネルMOSFETに印加され、交流電源の第2の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第2の駆動電圧が第2のnチャネルMOSFETに印加され、第3のコンデンサが第1のコンデンサの第1の端子と交流電源の第2の端子の間の電圧によりチャージされ、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第3のコンデンサの両端の電圧を分圧した第3の駆動電圧が第3のnチャネルMOSFETに印加され、交流電源の第1の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第4の駆動電圧が第4のnチャネルMOSFETに印加される。

従って、全波整流平滑回路の整流素子を全てnチャネルMOSFETにより構成することができ、全波整流平滑回路の電力の損失をより低減することができる。

本発明の全波整流平滑回路は、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧が第1の基準電圧以下になったとき、第1の駆動電圧を第1のnチャネルMOSFETに印加し、第2の駆動回路は、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧が第2の基準電圧以下になったとき、第3の駆動電圧を第3のnチャネルMOSFETに印加するようにすることができる。

従って、第1のnチャネルMOSFETのスイッチングを、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧が第1の基準電圧以下になったか否かにより制御することができるようになる。また、第2のnチャネルMOSFETのスイッチングを、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧が第2の基準電圧以下になったか否かにより制御することができるようになる。

本発明の全波整流平滑回路は、第1の駆動回路は、第1のスイッチング素子を含み、第2の駆動回路は、第2のスイッチング素子を含み、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧を分圧した第5の駆動電圧を第1のスイッチング素子に印加する第3の分圧回路と、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧を分圧した第6の駆動電圧を第2のスイッチング素子に印加する第4の分圧回路とをさらに含み、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧が第1の基準電圧以下となったとき、第5の駆動電圧が第1のスイッチング素子をオフする電圧となり、第1のスイッチング素子がオフされたとき、第1の駆動回路は、第1の駆動電圧を第1のnチャネルMOSFETに印加し、交流電源の第2の端子と第1のコンデンサの第2の端子の間の電圧が第2の基準電圧以下となったとき、第6の駆動電圧が第2のスイッチング素子をオフする電圧となり、第2のスイッチング素子がオフされたとき、第2の駆動回路は、第3の駆動電圧を第3のnチャネルMOSFETに印加するようにすることができる。

第1のスイッチング素子および第2のスイッチング素子は、例えば、MOSFETやバイポーラトランジスタなどにより構成される。

従って、特殊な部品を用いることなく、安価かつ容易に全波整流平滑回路を構成することができる。

本発明のスイッチング電源装置は、交流電源が出力する交流電圧を全波整流平滑化した電圧をスイッチングして出力するスイッチング電源装置であって、ソースが交流電源の第1の端子に接続された第1のnチャネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor)と、ドレインが交流電源の第1の端子に接続された第2のnチャネルMOSFETと、ドレインが第1のnチャンネルMOSFETのドレインに接続され、ソースが交流電源の第2の端子に接続された第3のnチャネルMOSFETと、ドレインが交流電源の第2の端子に接続され、ソースが第2のnチャネルMOSFETのソースに接続された第4のnチャネルMOSFETと、第1の端子が第3のnチャネルMOSFETのドレインと接続され、第2の端子が第4のnチャネルMOSFETのソースに接続され、第1乃至第4のnチャネルMOSFETにより全波整流された電圧を平滑化する第1のコンデンサと、第1のコンデンサの第1の端子と交流電源の第1の端子の間の電圧によりチャージされる第2のコンデンサと、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第2のコンデンサの両端の電圧を分圧した第1の駆動電圧を第1のnチャネルMOSFETに印加する第1の駆動回路と、交流電源の第2の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第2の駆動電圧を第2のnチャネルMOSFETに印加する第1の分圧回路と、第1のコンデンサの第1の端子と交流電源の第2の端子の間の電圧によりチャージされる第3のコンデンサと、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第3のコンデンサの両端の電圧を分圧した第3の駆動電圧を第3のnチャネルMOSFETに印加する第2の駆動回路と、交流電源の第1の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第4の駆動電圧を第4のnチャネルMOSFETに印加する第2の分圧回路とを含むことを特徴とする。

第1の駆動回路は、例えば、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧が所定の電圧になったときスイッチングするスイッチング素子を含み、スイッチング素子のオンまたはオフにより駆動電圧を制御するようにすることができる。また、第1の駆動回路は、例えば、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧を所定の電圧と比較して、第1の駆動電圧を出力するコンパレータにより構成される。

第2の駆動回路は、例えば、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧が所定の電圧になったときスイッチングするスイッチング素子を含み、スイッチング素子のオンまたはオフにより駆動電圧を制御するようにすることができる。また、第2の駆動回路は、例えば、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧を所定の電圧と比較して、第3の駆動電圧を出力するコンパレータにより構成される。

本発明のスイッチング電源によれば、第1のnチャネルMOSFETのソースが交流電源の第1の端子に接続され、第2のチャネルMOSFETのドレインが交流電源の第1の端子に接続され、第3のnチャネルMOSFETのドレインが第1のnチャンネルMOSFETのドレインに接続され、ソースが交流電源の第2の端子に接続され、第4のnチャネルMOSFETのドレインが交流電源の第2の端子に接続され、ソースが第2のnチャネルMOSFETのソースに接続され、第1のコンデンサの第1の端子が第3のnチャネルMOSFETのドレインと接続され、第2の端子が第4のnチャネルMOSFETのソースに接続され、第1乃至第4のnチャネルMOSFETにより全波整流された電圧が平滑化され、第2のコンデンサが第1のコンデンサの第1の端子と交流電源の第1の端子の間の電圧によりチャージされ、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第2のコンデンサの両端の電圧を分圧した第1の駆動電圧が第1のnチャネルMOSFETに印加され、交流電源の第2の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第2の駆動電圧が第2のnチャネルMOSFETに印加され、第3のコンデンサが第1のコンデンサの第1の端子と交流電源の第2の端子の間の電圧によりチャージされ、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第3のコンデンサの両端の電圧を分圧した第3の駆動電圧が第3のnチャネルMOSFETに印加され、交流電源の第1の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第4の駆動電圧が第4のnチャネルMOSFETに印加される。

従って、スイッチング電源装置の整流素子を全てnチャネルMOSFETにより構成することができ、スイッチング電源装置の電力の損失をより低減することができる。

以上のように、本発明の全波整流平滑回路によれば、入力された交流電圧を全波整流平滑化することができる。また、本発明の全波整流平滑回路によれば、電力の損失をより低減することができる。

また、本発明のスイッチング電源によれば、所定の直流電圧を出力することができる。また、本発明のスイッチング電源によれば、電力の損失をより低減することができる。

図2は、本発明を適用した全波整流平滑回路102の回路構成例を示す図である。

全波整流平滑回路102は、交流電源101および負荷103に接続され、全波整流平滑回路102は、交流電源101から入力された交流の入力電圧Vinを全波整流平滑化し、全波整流平滑化した直流の出力電圧Voutを負荷103に出力する。

全波整流平滑回路102は、チャージアップ回路111、分圧回路112、駆動回路113、分圧回路114、スイッチング回路115、チャージアップ回路116、分圧回路117、駆動回路118、分圧回路119、スイッチング回路120、およびコンデンサ121により構成される。

なお、全波整流平滑回路102において、交流電源101の一端、MOSFET181のソース、およびMOSFET183のドレインの接続点を接続点A1、交流電源101の他の一端、MOSFET231のソース、およびMOSFET233のドレインの接続点を接続点A2とする。接続点A1と接続点A2の電位差は、交流電源101から入力される入力電圧Vinと等しい。また、コンデンサ121とMOSFET231のドレインの接続点を接続点A3、コンデンサ121とMOSFET233のソースの接続点を接続点A4とする。接続点A3と接続点A4の電位差は、負荷103に印加される出力電圧Voutと等しい。

また、以下、入力電圧Vinにおいて、接続点A1の電位が接続点A2の電位より高くなるサイクルを正のサイクル、接続点A2の電位が接続点A1の電位より高くなるサイクルを負のサイクル、接続点A1の電位が上昇する方向を正の方向、接続点A2の電位が上昇する方向を負の方向とする。

チャージアップ回路111は、コンデンサ141およびダイオード142により構成される。コンデンサ141の一端は、ダイオード142のカソードおよび駆動回路113の抵抗163の一端に接続されている。コンデンサ141の他の一端は、交流電源101の一端、分圧回路112の抵抗151の一端、駆動回路113のMOSFET161のソースおよび抵抗162の一端、スイッチング回路115のMOSFET181のソース、ダイオード182のアノード、MOSFET183のドレイン、およびダイオード184のカソード、並びに、分圧回路119の抵抗222の一端に接続されている。

ダイオード142のアノードは、分圧回路112の抵抗152の一端、スイッチング回路115のMOSFET181のドレインおよびダイオード182のカソード、スイッチング回路120のMOSFET231のドレインおよびダイオード232のカソード、分圧回路117の抵抗202の一端、チャージアップ回路116のダイオード192のアノード、並びに、コンデンサ121の一端に接続されている。

コンデンサ141と駆動回路113の抵抗163の時定数は、入力電圧Vinの周期に比べて十分大きな値に設計されており、コンデンサ141の放電時間は入力電圧Vinの周期に比べて十分長いため、コンデンサ141は入力電圧Vinのピーク値とほぼ等しい電圧に常にチャージされる。

分圧回路112は、抵抗151および152により構成され、接続点A3と接続点A1の間に印加された電圧を分圧した駆動電圧を駆動回路113のMOSFET161のゲート−ソース間に印加する。抵抗151の一端であって、チャージアップ回路111のコンデンサ141の一端に接続されている一端とは異なる他の一端は、抵抗152の一端であって、分圧回路111のダイオード142のアノードに接続されている一端とは異なる他の一端、および駆動回路113のMOSFET161のゲートに接続されている。

駆動回路113は、MOSFET161および抵抗162乃至164により構成され、スイッチング回路115のMOSFET181のゲート−ソース間に駆動電圧を印加する。MOSFET161はnチャネルMOSFETであり、MOSFET161のドレインは、抵抗163の一端であって、分圧回路111のダイオード142のカソードと接続されている一端とは異なる他の一端、および抵抗164の一端に接続されている。抵抗162の一端であって、分圧回路111のコンデンサ141の一端と接続されている一端とは異なる他の一端は、抵抗164の他の一端、およびスイッチング回路115のMOSFET181のゲートに接続されている。

分圧回路114は、抵抗171および172により構成され、接続点A2と接続点A4の間に印加された電圧を分圧した駆動電圧をMOSFET183のゲート−ソース間に印加する。抵抗171の一端は、抵抗172の一端、およびスイッチング回路115のMOSFET183のゲートに接続されている。抵抗171の他の一端は、スイッチング回路115のMOSFET183のソースおよびダイオード184のアノード、スイッチング回路120のMOSFET233のソースおよびダイオード234のアノード、分圧回路119の抵抗221の一端、およびコンデンサ121の一端であって、チャージアップ回路116のダイオード192のアノードと接続されている一端とは異なる他の一端と接続され、さらに接地されている。

抵抗172の他の一端は、交流電源101の一端であって、チャージアップ回路111のコンデンサ141の一端に接続されている一端とは異なる他の一端、スイッチング回路120のMOSFET231のソース、ダイオード232のアノード、MOSFET233のドレイン、およびダイオード234のカソード、駆動回路118の抵抗212の一端およびMOSFET211のソース、分圧回路117の抵抗201の一端、並びにチャージアップ回路116のコンデンサ191の一端に接続されている。

スイッチング回路115は、MOSFET181および183、並びに、ダイオード182および184により構成される。MOSFET181および183は、nチャネルMOSFETからなる全波整平滑回路102の整流素子である。ダイオード182はMOSFET181のボディダイオードであり、ダイオード184はMOSFET183のボディダイオードである。なお、ダイオード182および184は、MOSFET181および183のボディダイオードではなく、外付けのダイオードとしてもよい。

チャージアップ回路116は、コンデンサ191およびダイオード192により構成される。コンデンサ191の一端であって、分圧回路117の抵抗201の一端に接続されている一端とは異なる他の一端は、ダイオード192のカソード、および駆動回路118の抵抗213の一端と接続されている。

コンデンサ191と駆動回路118の抵抗213の時定数は、入力電圧Vinの周期に比べて十分大きな値に設計されており、コンデンサ191の放電時間は入力電圧Vinの周期に比べて十分長いため、コンデンサ191は入力電圧Vinのピーク値とほぼ等しい電圧に常にチャージされる。

分圧回路117は、抵抗201および202により構成され、接続点A3と接続点A2の間に印加された電圧を分圧した駆動電圧を駆動回路118のMOSFET211のゲート−ソース間に印加する。抵抗201の一端であって、チャージアップ回路116のコンデンサ191の一端に接続されている一端と異なる他の一端は、抵抗202の一端であって、チャージアップ回路116のダイオード192のアノードに接続されている一端とは異なる他の一端、および駆動回路118のMOSFET211のゲートに接続されている。

駆動回路118は、MOSFET211および抵抗212乃至214により構成され、スイッチング回路120のMOSFET231のゲート−ソース間に駆動電圧を印加する。MOSFET211はnチャネルMOSFETであり、MOSFET211のドレインは、抵抗213の一端であって、チャージアップ回路116のダイオード192のカソードと接続されている一端とは異なる他の一端、および抵抗214の一端に接続されている。抵抗212の一端であって、MOSFET211のソースに接続されている一端とは異なる他の一端は、抵抗214の他の一端、およびスイッチング回路120のMOSFET231のゲートに接続されている。

分圧回路119は、抵抗221および抵抗222により構成され、接続点A1と接続点A4の間に印加された電圧を分圧した駆動電圧を、MOSFET233のゲート−ソース間に印加する。抵抗221の一端であって、コンデンサ121の一端に接続されている一端とは異なる他の一端は、抵抗222の一端であって、スイッチング回路115のMOSFET183のドレインに接続されている一端とは異なる他の一端、およびスイッチング回路120のMOSFET233のゲートに接続されている。

スイッチング回路120は、MOSFET231および233、並びに、ダイオード232および234により構成される。MOSFET231および233は、nチャネルMOSFETからなる全波整平滑回路102の整流素子である。ダイオード232はMOSFET231のボディダイオードであり、ダイオード234はMOSFET233のボディダイオードである。なお、ダイオード232および234は、MOSFET231および233のボディダイオードではなく、外付けのダイオードとしてもよい。

コンデンサ121の両端には負荷103が接続されており、コンデンサ101は、交流電源101から入力された入力電圧VinがMOSFET181、183、231、および233により全波整流された電圧を平滑化し、負荷103に供給する。

次に、図3および4を参照して、交流電源101により入力電圧Vinが入力されてから十分な時間が経過した後の全波整流平滑回路102の定常状態における動作について説明する。なお、現時点において、交流電圧101から入力される入力電圧Vinがほぼ0V、かつ正のサイクルに入る前であり、MOSFET161およびMOSFET211がオンされており、コンデンサ121が十分充電され、コンデンサ141およびコンデンサ191が入力電圧Vinのピーク値とほぼ等しい電圧に充電されている状態とする。

入力電圧Vinが正のサイクルに入り、接続点A1の電位が上昇し、接続点A1と接続点A3の電位差が小さくなるに伴い、抵抗151の両端の電圧、すなわち、MOSFET161のゲート−ソース間の電圧が下降する。そして、接続点A1と接続点A3の電位差が所定の電圧(基準電圧)以下となり、抵抗151の両端の電圧がMOSFET161のスレッショルド電圧より小さくなったとき、MOSFET161はオフされる。

MOSFET161がオフされると、コンデンサ141、抵抗163、MOSFET161、コンデンサ141の経路で流れていた電流が流れなくなり、図3の矢印261で示されるように、コンデンサ141、抵抗163、抵抗164、抵抗162、コンデンサ141の経路で流れる電流が増大する。そして、コンデンサ141の両端の電圧を分圧した抵抗162の両端の電圧、すなわち、MOSFET181のゲート−ソース間の電圧が上昇する。このとき、抵抗162の両端の電圧は、MOSFET181のスレッショルド電圧以上かつMOSFET181のゲート−ソース間の定格電圧以下の電圧となるように設計されており、MOSFET181がオンされる。

また、接続点A1の電位の上昇に伴い、接続点A1と接続点A2の電位差(入力電圧Vin)により、図3の矢印262で示されるように、交流電源101、抵抗222、抵抗221、ダイオード234、交流電源101の経路で電流が流れ、抵抗221の両端の電圧、すなわち、MOSFET233のゲート−ソース間の電圧が上昇する。そして、入力電圧Vinが正の方向に上昇するに従い、接続点A1と接続点A4の電位差が所定の電圧以上となり、抵抗221の両端の電圧がMOSFET233のスレッショルド電圧以上になったとき、MOSFET233がオンされる。

さらに入力電圧Vinが正の方向に上昇し、接続点A1の電位が接続点A3の電位を上回ったとき、図3の矢印263で示されるように、交流電源101、MOSFET181、コンデンサ121、MOSFET233、交流電源101の経路で電流が流れ、コンデンサ121が充電される。

また、図3の矢印264で示されるように、交流電源101、MOSFET181、ダイオード192、コンデンサ191、交流電源101の経路で電流が流れ、コンデンサ191が充電される。上述したように、コンデンサ191と抵抗213の時定数は、入力電圧Vinの周期に比べて十分大きな値に設定されており、コンデンサ191の両端の電圧がほとんど降下しないまま、入力電圧Vinのピーク値付近の電圧によりコンデンサ191の充電が繰り返され、コンデンサ191の両端の電圧は、入力電圧Vinのピーク値にほぼ等しい電圧に常にチャージされる。

入力電圧Vinが正のピーク値に達した後、接続点A1の電位が下降し、接続点A1の電位が接続点A3の電位より低くなったとき、上述した図3の矢印263および264の経路の電流は流れなくなる。

そして、接続点A1と接続点A4の電位差が所定の電圧より小さくなり、抵抗221の両端の電圧が、MOSFET233のスレッショルド電圧未満になったとき、MOSFET233がオフされる。

また、接続点A1の電位が下降し、接続点A1と接続点A3の電位差が所定の電圧より大きくなり、抵抗151の両端の電圧がMOSFET161のスレッショルド電圧以上になったとき、MOSFET161がオンされる。MOSFET161がオンされると、コンデンサ141、抵抗163、MOSFET161、コンデンサ141の経路で電流が流れるようになり、MOSFET181のゲート−ソース間がほぼ短絡状態となり、MOSFET181のゲート−ソース間の電圧がほぼ0Vとなり、MOSFET181はオフされる。

次に、入力電圧Vinが負のサイクルに入り、接続点A2の電位が上昇し、接続点A2と接続点A3の電位差が小さくなるに従い、抵抗201の両端の電圧、すなわち、MOSFET211のゲート−ソース間の電圧が下降する。そして、接続点A2と接続点A3の電位差が所定の電圧(基準電圧)以下となり、抵抗201の両端の電圧がMOSFET211のスレッショルド電圧より小さくなったとき、MOSFET211がオフされる。

MOSFET211がオフされると、コンデンサ191、抵抗213、MOSFET211、コンデンサ191の経路で流れていた電流が流れなくなり、図4の矢印271で示されるように、コンデンサ191、抵抗213、抵抗214、抵抗212、コンデンサ191の経路で流れる電流が増大する。そして、コンデンサ191の両端の電圧を分圧した抵抗212の両端の電圧、すなわち、MOSFET231のゲート−ソース間の電圧が上昇する。このとき、抵抗212の両端の電圧はMOSFET231のスレッショルド電圧以上かつMOSFET231のゲート−ソース間の定格電圧以下の電圧となるように設計されており、MOSFET231がオンされる。

また、接続点A2の電位の上昇に伴い、接続点A2と接続点A1の電位差(入力電圧Vin)により、図4の矢印272で示されるように、交流電源101、抵抗172、抵抗171、ダイオード184、交流電源101の経路で電流が流れ、抵抗171の両端の電圧、すなわち、MOSFET183のゲート−ソース間の電圧が上昇する。そして、入力電圧Vinが負の方向に上昇するに従い、接続点A2と接続点A4の電位差が所定の電圧以上となり、抵抗171の両端の電圧がMOSFET183のスレッショルド電圧以上になったとき、MOSFET183がオンされる。

さらに入力電圧Vinが負の方向に上昇し、接続点A2の電位が接続点A3の電位を上回ったとき、図4の矢印273で示されるように、交流電源101、MOSFET231、コンデンサ121、MOSFET183、交流電源101の経路で電流が流れ、コンデンサ121が充電される。

また、図4の矢印274で示されるように、交流電源101、MOSFET231、ダイオード142、コンデンサ141、交流電源101の経路で電流が流れ、コンデンサ141が充電される。上述したように、コンデンサ141と抵抗163の時定数は、入力電圧Vinの周期に比べて十分大きな値に設定されており、コンデンサ141の両端の電圧がほとんど降下しないまま、入力電圧Vinのピーク値付近の電圧によりコンデンサ141の充電が繰り返され、コンデンサ141の両端の電圧は、入力電圧Vinのピーク値にほぼ等しい電圧に常にチャージされる。

入力電圧Vinが負のピーク値に達した後、接続点A2の電位が下降し、接続点A2の電位が接続点A3の電位より低くなったとき、上述した図4の矢印273および274で示される経路の電流は流れなくなる。

そして、接続点A2と接続点A4の電位差が所定の電圧より小さくなり、抵抗171の両端の電圧が、MOSFET183のスレッショルド電圧未満になったとき、MOSFET183がオフされる。

また、接続点A2の電位が下降し、接続点A2と接続点A3の電位差が所定の電圧より大きくなり、抵抗201の両端の電圧がMOSFET211のスレッショルド電圧以上になったとき、MOSFET211がオンされる。MOSFET211がオンされると、コンデンサ191、抵抗213、MOSFET211、コンデンサ191の経路で電流が流れるようになり、MOSFET231のゲート−ソース間がほぼ短絡状態となり、MOSFET231のゲート−ソース間の電圧がほぼ0Vとなり、MOSFET231はオフされる。

上述したようにMOSFET181、183、232、および234により入力電圧Vinが全波整流された電圧は、コンデンサ121により平滑化され、負荷103に出力される。

その後、再び入力電圧Vinが正のサイクルに入り、上述した動作が繰り返される。

このように、全波整流平滑回路102は、整流素子にnチャネルMOSFETのみを用いて、交流電圧を全波整流平滑化することができ、電力の損失を低減することができる。

なお、全波整流平滑回路102の整流素子を、nチャネルMOSFETを2つ以上並列に接続して設けることにより、電力の損失をより低減することができる。また、MOSFET161および211に、pチャネルMOSFETやバイポーラトランジスタなどnチャネルMOSFET以外のトランジスタを用いるようにしてもよい。さらに、分圧回路112、114、117、および119をコンパレータにより構成するようにしてもよい。この場合、例えば、分圧回路112をコンパレータにより構成した場合、コンパレータは接続点A3と接続点A1の電位を比較して、接続点A3と接続点A1の電位差が所定の値になったとき、コンパレータによりMOSFET161に駆動電圧が印加される。

図5は、全波整流平滑回路102を用いたスイッチング電源装置301の回路構成例を示す図である。なお、図5では、図2と対応する部分については同じ符号を付してあり、その説明は繰り返しになるので省略する。

スイッチング電源装置301は、フライバック方式のスイッチング電源装置であり、交流電源101、全波整流平滑回路102、および出力回路311により構成される。

交流電源101から入力された交流電圧は、図3および図4を参照して上述したように、全波整流平滑回路102により全波整流平滑化され、出力回路311に供給される。出力回路311は、全波整流平滑化された電圧を所定の直流電圧に変換して、出力端子327−1および327−2に接続された外部の電力機器に出力する。

出力回路311は、トランス321、ダイオード322、コンデンサ323、制御回路324、駆動回路325、MOSFET326、並びに出力端子327−1および327−2により構成される。

トランス321の一次巻線の一端は、全波整流平滑回路102のコンデンサ121の接地されている一端とは異なる他の一端に接続され、トランス321の一次巻線の他の一端は、MOSFET326のドレインに接続されている。トランス321の二次巻線の一端はダイオード322のアノードに接続され、トランス321の二次巻線の他の一端は、コンデンサ323の一端、および出力端子327−2に接続され、さらに接地されている。トランス321は、スイッチング電源装置301の交流電源101と出力端子327−1および327−2との間を絶縁するとともに、全波整流平滑回路102から出力された電圧を所定の電圧に変圧する。

ダイオード322のカソードは、コンデンサ323の一端であって、トランス321の二次巻線の一端と接続されている一端とは異なる他の一端、および出力端子327−1に接続されている。

制御回路324は、出力端子327−1および327−2に接続され、スイッチング電源装置301の出力電圧を監視し、スイッチング電源装置301の出力電圧が所定の電圧になるように、制御信号を駆動回路325に供給する。

駆動回路325は、制御回路324から供給された制御信号に基づいて、MOSFET326を駆動する駆動信号をMOSFET326のゲートに供給する。

MOSFET326は、nチャネルMOSFETであり、ソースが接地されている。MOSFET326は、駆動回路325から供給された駆動信号により、オンまたはオフにスイッチングされる。なお、MOSFET326に、pチャネルMOSFETやバイポーラトランジスタなどnチャネルMOSFET以外のトランジスタを用いるようにしてもよい。

次に、スイッチング電源装置301の動作について説明する。

交流電源101から入力された入力電圧Vinは、全波整流平滑回路102により全波整流平滑化され、出力回路311に供給される。全波整流平滑回路102から供給された全波整流平滑化された直流電圧は、トランス321により変圧され、出力される。トランス321から出力された電圧は、ダイオード322およびコンデンサ323により平滑化され、出力端子327−1および327−2から、外部の電力機器に出力される。制御回路324は、出力電圧を監視し、出力電圧が所定の直流電圧となるように、駆動回路325に制御信号を供給する。駆動回路325は、制御信号に基づいて、駆動回路325に駆動信号を供給し、MOSFET326は、駆動信号によりオンまたはオフされ、出力電圧が所定の電圧になるように全波整流平滑回路102から出力された直流電圧がスイッチングされる。

このように、スイッチング電源装置に全波整流平滑回路102を適用することにより、スイッチング電源装置の電力の損失を低減することができる。

なお、以上では、本発明を適用した全波整流平滑回路102をフライバック方式のスイッチング電源装置に適用する例を示したが、もちろん、フォワード方式、プッシュプル方式、ハーフブリッジ方式、フルブリッジ方式など、交流電圧を全波整流平滑化した電圧をスイッチングする他の方式のスイッチング電源装置に適用することも可能である。

図6は、図2の全波整流平滑回路102において、MOSFET183および234がオンされるタイミングを遅らせて、MOSFET183および234が同時にオンすることによる短絡状態がより発生しにくくなるようにした全波整流平滑回路401の回路構成例を示している。なお、図6では、図2と対応する部分については同じ符号を付してあり、その説明は繰り返しになるので省略する。

全波整流平滑回路401は、図2の全波整流平滑回路202と比較して、分圧回路114および119が、分圧回路411および412に置き換わっている点が異なる。

分圧回路411は、図2の全波整流平滑回路202の分圧回路114に、ツェナーダイオード421を追加して設けた回路である。ツェナーダイオード421のアノードはMOSFET233のドレインに接続され、ツェナーダイオード421のカソードは抵抗172の一端であって、抵抗171と接続されている一端とは異なる他の一端と接続されている。

分圧回路412は、図2の全波整流平滑回路202の分圧回路119に、ツェナーダイオード431を追加して設けた回路である。ツェナーダイオード431のアノードはMOSFET184のドレインに接続され、ツェナーダイオード431のカソードは抵抗222の一端であって、抵抗221と接続されている一端とは異なる他の一端と接続されている。

全波整流平滑回路401では、入力電圧Vinが正のサイクルのとき、ツェナーダイオード431の働きにより、入力電圧Vinが所定の電圧になるまで、図6の矢印451で示される交流電源101、ツェナーダイオード431、抵抗222、抵抗221、ダイオード234、交流電源101の経路には電流が流れない。従って、抵抗221の両端の電圧、すなわち、MOSFET233のゲート−ソース間に電圧が印加されるのを遅らせることができ、MOSFET233がオンされるタイミングを遅らせることができる。これにより、MOSFET183がオフされる前に、MOSFET233がオンされ、交流電源101、MOSFET233、MOSFET183、交流電源101の経路で短絡電流が流れ、MOSFET183やMOSFET233が破壊されるのを防止することができる。ツェナーダイオード421も、ツェナーダイオード431と同様に、MOSFET183がオンされるタイミングを遅らせる働きをする。

図7は、図6の全波整流平滑回路401において、MOSFET183および233のターンオフをより高速にするようにした全波整流平滑回路501の回路構成例を示している。なお、図7では、図6と対応する部分については同じ符号を付してあり、その説明は繰り返しになるので省略する。

全波整流平滑回路501は、図6の全波整流平滑回路401と比較して、分圧回路411および412が、分圧回路511および512に置き換わっている点が異なる。

分圧回路511は、図6の全波整流平滑回路401の分圧回路411に、抵抗521およびダイオード522を追加して設けた回路である。抵抗521の一端はMOSFET183のゲートに接続され、抵抗521の他の一端はダイオード522のアノードと接続されている。ダイオード522のカソードは、ツェナーダイオード421のアノードと接続されている。

分圧回路512は、図6の全波整流平滑回路401の分圧回路412に、抵抗531およびダイオード532を追加して設けた回路である。抵抗531の一端はMOSFET233のゲートに接続され、抵抗531の他の一端はダイオード532のアノードと接続されている。ダイオード532のカソードは、ツェナーダイオード431のアノードと接続されている。

分圧回路511において、抵抗521とダイオード522を、抵抗172とツェナーダイオード421を並列に接続することにより、ツェナーダイオード421(ダイオード522)の順方向の抵抗値が小さくなる。従って、MOSFET183をオフさせるときに、MOSFET183のゲート−ソース間に蓄積されている電荷をより高速に引き抜くことができるようになり、MOSFET183のターンオフ時間を短くすることができる。なお、分圧回路522も同様に、抵抗531およびダイオード532により、MOSFET233のターンオフ時間をより短くすることができる。

以上のように、第1のnチャネルMOSFETのソースを交流電源の第1の端子に接続し、第2のnチャネルドレインを交流電源の第1の端子に接続し、第3のnチャネルMOSFETのドレインを第1のnチャンネルMOSFETのドレインに接続し、ソースを交流電源の第2の端子に接続し、第4のnチャネルMOSFETのドレインを交流電源の第2の端子に接続し、ソースを第2のnチャネルMOSFETのソースに接続し、第1のコンデンサの第1の端子を第3のnチャネルMOSFETのドレインと接続し、第2の端子を第4のnチャネルMOSFETのソースに接続し、第1のコンデンサにより第1乃至第4のnチャネルMOSFETにより全波整流された電圧を平滑化し、第1のコンデンサの第1の端子と交流電源の第1の端子の間の電圧により第2のコンデンサをチャージし、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第2のコンデンサの両端の電圧を分圧した第1の駆動電圧を第1のnチャネルMOSFETに印加し、交流電源の第2の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第2の駆動電圧を第2のnチャネルMOSFETに印加し、第1のコンデンサの第1の端子と交流電源の第2の端子の間の電圧により第3のコンデンサをチャージし、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第3のコンデンサの両端の電圧を分圧した第3の駆動電圧を第3のnチャネルMOSFETに印加し、交流電源の第1の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第4の駆動電圧を第4のnチャネルMOSFETに印加するようにした場合には、入力された交流電圧を全波整流平滑化することができる。また、電力の損失をより低減することができる。

以上のように、第1のnチャネルMOSFETのソースを交流電源の第1の端子に接続し、第2のnチャネルドレインを交流電源の第1の端子に接続し、第3のnチャネルMOSFETのドレインを第1のnチャンネルMOSFETのドレインに接続し、ソースを交流電源の第2の端子に接続し、第4のnチャネルMOSFETのドレインを交流電源の第2の端子に接続し、ソースを第2のnチャネルMOSFETのソースに接続し、第1のコンデンサの第1の端子を第3のnチャネルMOSFETのドレインと接続し、第2の端子を第4のnチャネルMOSFETのソースに接続し、第1のコンデンサにより第1乃至第4のnチャネルMOSFETにより全波整流された電圧を平滑化し、第1のコンデンサの第1の端子と交流電源の第1の端子の間の電圧により第2のコンデンサをチャージし、交流電源の第1の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第2のコンデンサの両端の電圧を分圧した第1の駆動電圧を第1のnチャネルMOSFETに印加し、交流電源の第2の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第2の駆動電圧を第2のnチャネルMOSFETに印加し、第1のコンデンサの第1の端子と交流電源の第2の端子の間の電圧により第3のコンデンサをチャージし、交流電源の第2の端子と第1のコンデンサの第1の端子の間の電圧に基づいて、第3のコンデンサの両端の電圧を分圧した第3の駆動電圧を第3のnチャネルMOSFETに印加し、交流電源の第1の端子と第1のコンデンサの第2の端子の間の電圧を分圧した第4の駆動電圧を第4のnチャネルMOSFETに印加するようにした場合には、所定の直流電圧を出力することができる。また、電力の損失をより低減することができる。

2 全波整流平滑回路

101 交流電源

102 全波整流平滑回路

111 チャージアップ回路

112 分圧回路

113 駆動回路

114 分圧回路

115 スイッチング回路

116 チャージアップ回路

117 分圧回路

118 駆動回路

119 分圧回路

120 スイッチング回路

121 コンデンサ

142 ダイオード

151,152 抵抗

161 MOSFET

162,163,164,171,172 抵抗

181 MOSFET

182 ダイオード

183 MOSFET

184 ダイオード

191 コンデンサ

192 ダイオード

201,202 抵抗

211 MOSFET

212,213,214,221,222 抵抗

231 MOSFET

232 ダイオード

233 MOSFET

234 ダイオード

301 スイッチング電源装置

311 出力回路

321 トランス

322 ダイオード

323 コンデンサ

324 制御回路

325 駆動回路

326 MOSFET

327 出力端子

401 全波整流平滑回路

411,412 分圧回路

421,431 ツェナーダイオード

501 全波整流平滑回路

511,512 分圧回路

522,532 ダイオード

101 交流電源

102 全波整流平滑回路

111 チャージアップ回路

112 分圧回路

113 駆動回路

114 分圧回路

115 スイッチング回路

116 チャージアップ回路

117 分圧回路

118 駆動回路

119 分圧回路

120 スイッチング回路

121 コンデンサ

142 ダイオード

151,152 抵抗

161 MOSFET

162,163,164,171,172 抵抗

181 MOSFET

182 ダイオード

183 MOSFET

184 ダイオード

191 コンデンサ

192 ダイオード

201,202 抵抗

211 MOSFET

212,213,214,221,222 抵抗

231 MOSFET

232 ダイオード

233 MOSFET

234 ダイオード

301 スイッチング電源装置

311 出力回路

321 トランス

322 ダイオード

323 コンデンサ

324 制御回路

325 駆動回路

326 MOSFET

327 出力端子

401 全波整流平滑回路

411,412 分圧回路

421,431 ツェナーダイオード

501 全波整流平滑回路

511,512 分圧回路

522,532 ダイオード

Claims (4)

- 交流電源から入力された交流電圧を全波整流平滑化する全波整流平滑回路において、

ソースが前記交流電源の第1の端子に接続された第1のnチャネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor)と、

ドレインが前記交流電源の前記第1の端子に接続された第2のnチャネルMOSFETと、

ドレインが前記第1のnチャンネルMOSFETのドレインに接続され、ソースが前記交流電源の第2の端子に接続された第3のnチャネルMOSFETと、

ドレインが前記交流電源の前記第2の端子に接続され、ソースが前記第2のnチャネルMOSFETのソースに接続された第4のnチャネルMOSFETと、

第1の端子が前記第3のnチャネルMOSFETのドレインと接続され、第2の端子が前記第4のnチャネルMOSFETのソースに接続され、前記第1乃至第4のnチャネルMOSFETにより全波整流された電圧を平滑化する第1のコンデンサと、

前記第1のコンデンサの前記第1の端子と前記交流電源の前記第1の端子の間の電圧によりチャージされる第2のコンデンサと、

前記交流電源の前記第1の端子と前記第1のコンデンサの前記第1の端子の間の電圧に基づいて、前記第2のコンデンサの両端の電圧を分圧した第1の駆動電圧を前記第1のnチャネルMOSFETに印加する第1の駆動回路と、

前記交流電源の第2の端子と前記第1のコンデンサの前記第2の端子の間の電圧を分圧した第2の駆動電圧を前記第2のnチャネルMOSFETに印加する第1の分圧回路と、

前記第1のコンデンサの前記第1の端子と前記交流電源の前記第2の端子の間の電圧によりチャージされる第3のコンデンサと、

前記交流電源の前記第2の端子と前記第1のコンデンサの前記第1の端子の間の電圧に基づいて、前記第3のコンデンサの両端の電圧を分圧した第3の駆動電圧を前記第3のnチャネルMOSFETに印加する第2の駆動回路と、

前記交流電源の第1の端子と前記第1のコンデンサの前記第2の端子の間の電圧を分圧した第4の駆動電圧を前記第4のnチャネルMOSFETに印加する第2の分圧回路と

を含むことを特徴とする全波整流平滑回路。 - 前記第1の駆動回路は、前記交流電源の前記第1の端子と前記第1のコンデンサの前記第1の端子の間の電圧が第1の基準電圧以下になったとき、前記第1の駆動電圧を前記第1のnチャネルMOSFETに印加し、

前記第2の駆動回路は、前記交流電源の前記第2の端子と前記第1のコンデンサの前記第1の端子の間の電圧が第2の基準電圧以下になったとき、前記第3の駆動電圧を前記第3のnチャネルMOSFETに印加する

ことを特徴とする請求項1に記載の全波整流平滑回路。 - 前記第1の駆動回路は、第1のスイッチング素子を含み、

前記第2の駆動回路は、第2のスイッチング素子を含み、

前記交流電源の前記第1の端子と前記第1のコンデンサの前記第1の端子の間の電圧を分圧した第5の駆動電圧を前記第1のスイッチング素子に印加する第3の分圧回路と、

前記交流電源の前記第2の端子と前記第1のコンデンサの前記第1の端子の間の電圧を分圧した第6の駆動電圧を前記第2のスイッチング素子に印加する第4の分圧回路とをさらに含み、

前記交流電源の前記第1の端子と前記第1のコンデンサの前記第1の端子の間の電圧が前記第1の基準電圧以下となったとき、前記第5の駆動電圧が前記第1のスイッチング素子をオフする電圧となり、前記第1のスイッチング素子がオフされたとき、前記第1の駆動回路は、前記第1の駆動電圧を前記第1のnチャネルMOSFETに印加し、

前記交流電源の前記第2の端子と前記第1のコンデンサの前記第2の端子の間の電圧が前記第2の基準電圧以下となったとき、前記第6の駆動電圧が前記第2のスイッチング素子をオフする電圧となり、前記第2のスイッチング素子がオフされたとき、前記第2の駆動回路は、前記第3の駆動電圧を前記第3のnチャネルMOSFETに印加する

ことを特徴とする請求項2に記載の全波整流平滑回路。 - 交流電源が出力する交流電圧を全波整流平滑化した電圧をスイッチングして出力するスイッチング電源装置において、

ソースが前記交流電源の第1の端子に接続された第1のnチャネルMOSFETと、

ドレインが前記交流電源の前記第1の端子に接続された第2のnチャネルMOSFETと、

ドレインが前記第1のnチャンネルMOSFETのドレインに接続され、ソースが前記交流電源の第2の端子に接続された第3のnチャネルMOSFETと、

ドレインが前記交流電源の前記第2の端子に接続され、ソースが前記第2のnチャネルMOSFETのソースに接続された第4のnチャネルMOSFETと、

第1の端子が前記第3のnチャネルMOSFETのドレインと接続され、第2の端子が前記第4のnチャネルMOSFETのソースに接続され、前記第1乃至第4のnチャネルMOSFETにより全波整流された電圧を平滑化する第1のコンデンサと、

前記第1のコンデンサの前記第1の端子と前記交流電源の前記第1の端子の間の電圧によりチャージされる第2のコンデンサと、

前記交流電源の前記第1の端子と前記第1のコンデンサの前記第1の端子の間の電圧に基づいて、前記第2のコンデンサの両端の電圧を分圧した第1の駆動電圧を前記第1のnチャネルMOSFETに印加する第1の駆動回路と、

前記交流電源の第2の端子と前記第1のコンデンサの前記第2の端子の間の電圧を分圧した第2の駆動電圧を前記第2のnチャネルMOSFETに印加する第1の分圧回路と、

前記第1のコンデンサの前記第1の端子と前記交流電源の前記第2の端子の間の電圧によりチャージされる第3のコンデンサと、

前記交流電源の前記第2の端子と前記第1のコンデンサの前記第1の端子の間の電圧に基づいて、前記第3のコンデンサの両端の電圧を分圧した第3の駆動電圧を前記第3のnチャネルMOSFETに印加する第2の駆動回路と、

前記交流電源の第1の端子と前記第1のコンデンサの前記第2の端子の間の電圧を分圧した第4の駆動電圧を前記第4のnチャネルMOSFETに印加する第2の分圧回路と

を含むことを特徴とするスイッチング電源装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104224A JP2005295627A (ja) | 2004-03-31 | 2004-03-31 | 全波整流平滑回路およびスイッチング電源装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104224A JP2005295627A (ja) | 2004-03-31 | 2004-03-31 | 全波整流平滑回路およびスイッチング電源装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005295627A true JP2005295627A (ja) | 2005-10-20 |

Family

ID=35327965

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004104224A Pending JP2005295627A (ja) | 2004-03-31 | 2004-03-31 | 全波整流平滑回路およびスイッチング電源装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005295627A (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008061412A (ja) * | 2006-08-31 | 2008-03-13 | Daikin Ind Ltd | 空調機のコンバータ装置 |

| JP2010178519A (ja) * | 2009-01-30 | 2010-08-12 | Omron Corp | 全波整流回路 |

| US8400801B2 (en) | 2009-04-27 | 2013-03-19 | Murata Manufacturing Co., Ltd. | Wireless power transfer terminal |

| JP2015109753A (ja) * | 2013-12-04 | 2015-06-11 | オムロン株式会社 | 全波整流回路 |

| WO2023095478A1 (ja) * | 2021-11-24 | 2023-06-01 | 株式会社日立パワーデバイス | 整流回路およびそれを用いた電源 |

| JP2023163197A (ja) * | 2022-04-28 | 2023-11-10 | 株式会社 日立パワーデバイス | 整流回路およびそれを用いた電源 |

| JP7817553B2 (ja) | 2022-04-28 | 2026-02-19 | ミネベアパワーデバイス株式会社 | 整流回路およびそれを用いた電源 |

-

2004

- 2004-03-31 JP JP2004104224A patent/JP2005295627A/ja active Pending

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008061412A (ja) * | 2006-08-31 | 2008-03-13 | Daikin Ind Ltd | 空調機のコンバータ装置 |

| JP2010178519A (ja) * | 2009-01-30 | 2010-08-12 | Omron Corp | 全波整流回路 |

| US8400801B2 (en) | 2009-04-27 | 2013-03-19 | Murata Manufacturing Co., Ltd. | Wireless power transfer terminal |

| JP2015109753A (ja) * | 2013-12-04 | 2015-06-11 | オムロン株式会社 | 全波整流回路 |

| WO2023095478A1 (ja) * | 2021-11-24 | 2023-06-01 | 株式会社日立パワーデバイス | 整流回路およびそれを用いた電源 |

| JP2023163197A (ja) * | 2022-04-28 | 2023-11-10 | 株式会社 日立パワーデバイス | 整流回路およびそれを用いた電源 |

| JP7817553B2 (ja) | 2022-04-28 | 2026-02-19 | ミネベアパワーデバイス株式会社 | 整流回路およびそれを用いた電源 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10158282B1 (en) | Switching power supply device | |

| TWI740837B (zh) | 自動增強自驅動同步整流控制電路、主動箝位順向轉換器及主動箝位功率轉換器 | |

| US7778048B2 (en) | Switching power supply apparatus | |

| US10530269B2 (en) | AC-DC converter | |

| US8374002B2 (en) | Isolated switching power supply apparatus | |

| US20170098993A1 (en) | Circuitry for power factor correction and methods of operation | |

| JP5910395B2 (ja) | ドライブ回路 | |

| JP6281748B2 (ja) | Dc−dcコンバータ | |

| JP6012822B1 (ja) | 電力変換装置 | |

| JP2006129548A (ja) | 電力変換装置 | |

| JP4439979B2 (ja) | 電源装置 | |

| US20120014149A1 (en) | Power conversion apparatus and method | |

| US11451161B2 (en) | Power switcher, power rectifier, and power converter including cascode-connected transistors | |

| KR102482820B1 (ko) | 절연형 스위칭 전원 | |

| US9564819B2 (en) | Switching power supply circuit | |

| US10530244B2 (en) | Switch circuit with active snubber circuit and DC-DC converter | |

| US9178435B2 (en) | Switching power supply | |

| CN110999057B (zh) | 开关电源装置 | |

| JP7591388B2 (ja) | 絶縁型dc/dcコンバータ及びac/dcコンバータ | |

| US9431920B2 (en) | Non-isolated DC/DC converter with 2 inductors and zero voltage switching | |

| US10069429B2 (en) | Push-pull type isolated DC/DC converter including zero voltage switching | |

| JP2005295627A (ja) | 全波整流平滑回路およびスイッチング電源装置 | |

| US11190107B2 (en) | Auxiliary power supply circuit, power supply apparatus, and power supply circuit | |

| JP4465713B2 (ja) | スイッチング電源装置及び同期整流回路 | |

| KR102525753B1 (ko) | 절연형 스위칭 전원 공급 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060927 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090915 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090917 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100202 |