JP2005293489A - 乱数発生回路 - Google Patents

乱数発生回路 Download PDFInfo

- Publication number

- JP2005293489A JP2005293489A JP2004111230A JP2004111230A JP2005293489A JP 2005293489 A JP2005293489 A JP 2005293489A JP 2004111230 A JP2004111230 A JP 2004111230A JP 2004111230 A JP2004111230 A JP 2004111230A JP 2005293489 A JP2005293489 A JP 2005293489A

- Authority

- JP

- Japan

- Prior art keywords

- random number

- number generation

- negative differential

- differential resistance

- generation circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Abstract

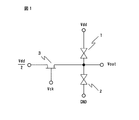

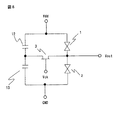

【解決手段】直列に接続した2つの負性微分抵抗素子の接続点に電源電圧の1/2の電圧を印加することにより、これら負性微分抵抗素子回路の不安定点に一致させて初期状態とする。次に駆動用トランジスタをOFF状態としてこの電圧を取り除くと、出力点が上記不安定点から論理1または0のどちらかの安定点に遷移することを利用して乱数を発生させる構成とした。

【選択図】図1

Description

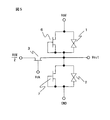

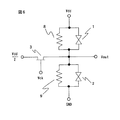

共鳴トンネルダイオード1および2を直列に接続し、この直列接続した回路の両端に直流電圧Vddを印加し、その一端にこの直流電圧の高電位側を接続し、他の一端にはを同じ直流電圧の低電位側、例えば接地電位(GND)を接続し、駆動用トランジスタ3のドレインにはVdd/2の直流電圧を印加し、ゲートには駆動用のクロック(Vck)を印加する。図2(a)および(b)は、この回路の動作原理を示すための直列接続した負性微分抵抗素子の電流(I)−電圧(V)特性である。図2(a)および(b)における負荷曲線4は共鳴トンネルダイオード1に、負荷曲線5は共鳴トンネルダイオード2に対応している。

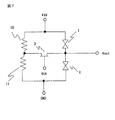

なお、駆動用トランジスタヘの印加電圧Vdd/2を確保するためには、図7に示すように、抵抗体10および11を直列接続し、その接続点から電圧Vdd/2を得る抵抗分割回路、あるいは図8に示すようにキャパシタ12および13を直列接続し、その接続点からVdd/2に相当する電圧を得る容量分割回路を用いてもよい。

さらに、図1に示す回路を複数個並列に用意し、所望のbit数の並列データ出力としての乱数を得ることも可能である。また、例えば負性微分抵抗素子として共鳴トンネルダイオードを用いれば、回路の高速性を活かすことで、一つの回路で複数回のサンプリングを行い、所望のbit数の直列データ出力としての乱数を得ることも可能である。

3:駆動用トランジスタ

4、5:負荷曲線(I−V特性)

6、7:トランジスタ

8、9、10、11:抵抗体

12、13:キャパシタ

Claims (12)

- 二つの負性微分抵抗素子を直列に接続して得られる回路の両端に直流電圧Vddを第一の電圧として印加し、

前記回路の一方の端子には前記直流電圧Vddの高電位側を接続し、

他方の端子には前記直流電圧Vddの低電位側を接続し、

前記二つの負性微分抵抗素子の接続点に電界効果型トランジスタの第一の電極としてのソース電極を接続し、

前記電界効果型トランジスタの第二の電極としてのドレイン電極に前記直流電圧Vddの2分の1の電圧すなわちVdd/2を第二の電圧として印加し、

前記接続点を出力電圧Voutの出力点とし、

前記電界効果型トランジスタの第三の電極としてのゲート電極に、振動電圧を印加することで、前記電界効果型トランジスタのON/OFFを制御し、

前記電界効果型トランジスタがONの時に前記接続点に前記第2の電圧を印加し、

前記電界効果型トランジスタがOFFの時に、前記接続点に印加されている第二の電圧を遮断し、この際、不可避的に加わる負性微分抵抗素子特性の熱揺らぎによって決定される出力を前記出力点から出力し、それを自然乱数として用いることを特徴とする乱数発生回路。 - 請求項1に記載の乱数発生回路において、

電界効果型トランジスタの代わりにバイポーラトランジスタを用い、電界効果型トランジスタのゲート、ドレイン、ソースの各電極を、それぞれバイポーラトランジスタのべース、コレクタ、エミッタの各電極と置き換えることを特徴とする乱数発生回路。 - 請求項1または請求項2に記載の乱数発生回路おいて、

前記負性微分抵抗素子の少なくとも一方について、抵抗体を前記負性微分抵抗素子に並列に接続して得られる回路を複合負性微分抵抗素子として置き換えたことを特徴とする乱数発生回路。 - 請求項1または請求項2に記載の乱数発生回路において、

前記負性微分抵抗素子の少なくとも一方について、トランジスタを前記負性微分抵抗素子に並列に接続して得られる回路を複合負性微分抵抗素子として置き換えたことを特徴とする乱数発生回路。 - 請求項1または請求項2に記載の乱数発生回路において、

前記負性微分抵抗素子の少なくとも一方について、抵抗体とトランジスタとを前記負性微分抵抗素子に並列に接続して得られる複合負性微分抵抗素子に置き換えたことを特徴とする乱数発生回路。 - 請求項1乃至請求項5の何れかに記載の乱数発生回路において、

前記負性微分抵抗素子として共鳴トンネルダイオードを用いることを特徴とする乱数発生回路。 - 請求項1乃至請求項5の何れかに記載の乱数発生回路において、

前記負性微分抵抗素子としてエサキダイオードを用いることを特徴とする乱数発生回路。 - 請求項1乃至請求項5の何れかに記載の乱数発生回路において、

前記負性微分抵抗素子としてトランジスタで構成される負性微分抵抗特性を有する回路を用いることを特徴とする乱数発生回路。 - 請求項1乃至請求項8の何れかに記載の乱数発生回路を複数個使用し、

前記複数の乱数発生回路を並列に設置し、

並列データ構成の乱数出力を得ることを特徴とする乱数発生回路。 - 請求項1乃至請求項8の何れかに記載の乱数発生回路を用い、

単一の乱数発生回路を複数回サンプリングすることにより直列データ出力を得ることを特徴とする乱数発生回路。 - 請求項1乃至請求項8の何れかに記載の乱数発生回路において、

前記電界効果型トランジスタまたは前記バイポーラトランジスタの前記第2の電極に前記第二の電圧Vdd/2を印加する方法として、

前記二つの負性微分抵抗素子の直列接続回路への前記第一の電圧Vddと接地との間に同じ大きさの2本の抵抗体を直列に接続し、該2本の抵抗体の接続点から、前記第二の電圧Vdd/2を得、該第二の電圧Vdd/2を前記電界効果型トランジスタまたは前記バイポーラトランジスタの前記第二の電極に供給することを特徴とする乱数発生回路。 - 請求項11に記載の乱数発生回路において、

前記抵抗体の代わりに2個の直列接続したキャパシタを用い、該キャパシタの接続点から前記第二の電圧Vdd/2に相当する電圧を発生せしめることを特徴とする乱数発生回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004111230A JP4252924B2 (ja) | 2004-04-05 | 2004-04-05 | 乱数発生回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004111230A JP4252924B2 (ja) | 2004-04-05 | 2004-04-05 | 乱数発生回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005293489A true JP2005293489A (ja) | 2005-10-20 |

| JP4252924B2 JP4252924B2 (ja) | 2009-04-08 |

Family

ID=35326314

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004111230A Expired - Fee Related JP4252924B2 (ja) | 2004-04-05 | 2004-04-05 | 乱数発生回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4252924B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2543125A (en) * | 2016-07-27 | 2017-04-12 | Quantum Base Ltd | Generating a unique response to a challenge |

| GB2543126A (en) * | 2016-07-27 | 2017-04-12 | Quantum Base Ltd | Generating a nondeterministic response to a challenge |

| GB2548428A (en) * | 2016-08-08 | 2017-09-20 | Quantum Base Ltd | Nondeterministic response to a challenge |

-

2004

- 2004-04-05 JP JP2004111230A patent/JP4252924B2/ja not_active Expired - Fee Related

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2543125A (en) * | 2016-07-27 | 2017-04-12 | Quantum Base Ltd | Generating a unique response to a challenge |

| GB2543126A (en) * | 2016-07-27 | 2017-04-12 | Quantum Base Ltd | Generating a nondeterministic response to a challenge |

| GB2543125B (en) * | 2016-07-27 | 2017-10-18 | Quantum Base Ltd | Generating a unique response to a challenge |

| GB2543126B (en) * | 2016-07-27 | 2017-10-25 | Quantum Base Ltd | Generating a nondeterministic response to a challenge |

| US11295003B2 (en) * | 2016-07-27 | 2022-04-05 | Quantum Base Limited | Generating a unique response to a challenge |

| GB2548428A (en) * | 2016-08-08 | 2017-09-20 | Quantum Base Ltd | Nondeterministic response to a challenge |

| WO2018029440A1 (en) * | 2016-08-08 | 2018-02-15 | Quantum Base Limited | Nondeterministic response to a challenge |

| GB2548428B (en) * | 2016-08-08 | 2018-05-16 | Quantum Base Ltd | Nondeterministic response to a challenge |

| US11061647B2 (en) | 2016-08-08 | 2021-07-13 | Quantum Base Limited | Nondeterministic response to a challenge |

| AU2017310491B2 (en) * | 2016-08-08 | 2021-09-09 | Quantum Base Limited | Nondeterministic response to a challenge |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4252924B2 (ja) | 2009-04-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5171908B2 (ja) | 電源回路 | |

| JP4921106B2 (ja) | バッファ回路 | |

| US20030132872A1 (en) | Tail current node equalization for a variable offset amplifier | |

| JP2012048452A (ja) | 半導体チップ | |

| JP2009198476A (ja) | 電圧検出回路 | |

| US20170323669A1 (en) | Device and method for data-writing | |

| JP2010232959A (ja) | 電子回路 | |

| CN101465157A (zh) | 用于1t1c铁电存储器的动态自适应参考产生电路 | |

| JP4252924B2 (ja) | 乱数発生回路 | |

| EP2599218A1 (en) | Low phase noise buffer for crystal oscillator | |

| US20110210794A1 (en) | Voltage sensing circuit capable of controlling a pump voltage stably generated in a low voltage environment | |

| JP4118754B2 (ja) | 乱数発生回路 | |

| Uddin et al. | A practical sense amplifier design for memristive crossbar circuits (PUF) | |

| KR20050041592A (ko) | 온도 보상이 가능한 내부전압 발생장치 | |

| JP2009015972A (ja) | 半導体記憶装置 | |

| KR20220170243A (ko) | 3진수 논리회로 | |

| CN115440277A (zh) | 一种基于忆阻器的异或逻辑电路 | |

| JP2006189946A (ja) | 乱数生成回路及び半導体集積回路 | |

| WO2008039624A2 (en) | Sense amplifier circuit for low voltage applications | |

| JP2006067497A (ja) | 信号制御回路及びそれを搭載した装置 | |

| US20080238517A1 (en) | Oscillator Circuit and Semiconductor Device | |

| JP2013222474A (ja) | 不揮発性メモリ回路、半導体装置、及び読出し方法 | |

| CN102201806A (zh) | 具有电流控制机制的电路及电流控制方法 | |

| JP2014154189A (ja) | 抵抗変化型メモリカウンタベース読み出し回路 | |

| JP2008004153A (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060714 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090120 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090122 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120130 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130130 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |