JP2005244788A - 同時双方向送受信システム - Google Patents

同時双方向送受信システム Download PDFInfo

- Publication number

- JP2005244788A JP2005244788A JP2004054179A JP2004054179A JP2005244788A JP 2005244788 A JP2005244788 A JP 2005244788A JP 2004054179 A JP2004054179 A JP 2004054179A JP 2004054179 A JP2004054179 A JP 2004054179A JP 2005244788 A JP2005244788 A JP 2005244788A

- Authority

- JP

- Japan

- Prior art keywords

- transmission

- output

- signal

- circuit

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 230000005540 biological transmission Effects 0.000 title claims abstract description 319

- 230000002457 bidirectional effect Effects 0.000 title claims abstract description 42

- 238000004891 communication Methods 0.000 claims abstract description 17

- 238000001514 detection method Methods 0.000 claims description 61

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 claims description 23

- 230000001360 synchronised effect Effects 0.000 claims description 16

- 230000001629 suppression Effects 0.000 claims description 7

- 239000000872 buffer Substances 0.000 description 95

- 238000000034 method Methods 0.000 description 18

- 238000006243 chemical reaction Methods 0.000 description 16

- 238000010586 diagram Methods 0.000 description 15

- 241000896693 Disa Species 0.000 description 13

- 239000003990 capacitor Substances 0.000 description 10

- 230000007423 decrease Effects 0.000 description 4

- 230000003111 delayed effect Effects 0.000 description 4

- 238000007599 discharging Methods 0.000 description 4

- 238000005070 sampling Methods 0.000 description 4

- 239000000284 extract Substances 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 230000010355 oscillation Effects 0.000 description 2

- 238000011084 recovery Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 1

- 230000010363 phase shift Effects 0.000 description 1

Images

Landscapes

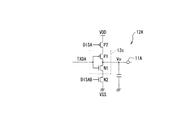

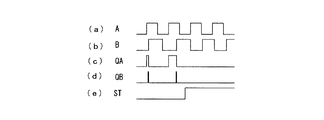

- Manipulation Of Pulses (AREA)

- Electronic Switches (AREA)

- Logic Circuits (AREA)

- Bidirectional Digital Transmission (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004054179A JP2005244788A (ja) | 2004-02-27 | 2004-02-27 | 同時双方向送受信システム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004054179A JP2005244788A (ja) | 2004-02-27 | 2004-02-27 | 同時双方向送受信システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005244788A true JP2005244788A (ja) | 2005-09-08 |

| JP2005244788A5 JP2005244788A5 (enExample) | 2006-11-02 |

Family

ID=35026003

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004054179A Withdrawn JP2005244788A (ja) | 2004-02-27 | 2004-02-27 | 同時双方向送受信システム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005244788A (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7351576B1 (ja) * | 2023-02-14 | 2023-09-27 | 秀治 小池 | 双方向データ伝送回路 |

-

2004

- 2004-02-27 JP JP2004054179A patent/JP2005244788A/ja not_active Withdrawn

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7351576B1 (ja) * | 2023-02-14 | 2023-09-27 | 秀治 小池 | 双方向データ伝送回路 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5600237B2 (ja) | 集積回路 | |

| US7302026B2 (en) | Clock recovery circuit and electronic device using a clock recovery circuit | |

| US7016613B2 (en) | Linear half-rate phase detector and clock and data recovery circuit | |

| US6642760B1 (en) | Apparatus and method for a digital delay locked loop | |

| US6374361B1 (en) | Skew-insensitive low voltage differential receiver | |

| US8232844B2 (en) | Synchronous oscillator, clock recovery apparatus, clock distribution circuit, and multi-mode injection circuit | |

| US10396805B2 (en) | Wide capture range reference-less frequency detector | |

| US8023605B2 (en) | Oversampling circuit and oversampling method | |

| JP5332328B2 (ja) | クロック及びデータ復元回路 | |

| CN101145898A (zh) | 时钟和数据恢复电路和恢复时钟和数据的方法 | |

| CN110391893B (zh) | 用于检测信号状态转变的设备和方法 | |

| CN104639157A (zh) | 定时调整电路和半导体集成电路装置 | |

| US5052022A (en) | Repeater and PLL circuit | |

| EP1343269B1 (en) | Method and apparatus for statistical loss of signal detection providing low capacitive load on input signals | |

| US10056883B2 (en) | SR latch circuit with single gate delay | |

| JP2005244788A (ja) | 同時双方向送受信システム | |

| US7750711B2 (en) | Phase select circuit with reduced hysteresis effect | |

| JP2019193245A (ja) | 半導体回路、データ伝送システム及び半導体回路の動作方法 | |

| US7760030B2 (en) | Phase detection circuit and method thereof and clock recovery circuit and method thereof | |

| KR100473395B1 (ko) | 위상선택 방법을 이용한 2엑스-오버샘플링 클록 및 데이터복원회로 | |

| US7016448B2 (en) | Synchronization state detector | |

| US6498824B1 (en) | Phase control signals for clock recovery circuits | |

| US8823429B1 (en) | Data transition density normalization for half rate CDRs with bang-bang phase detectors | |

| JP5286414B2 (ja) | 半導体記憶回路 | |

| CN118677591A (zh) | 信号接收电路、信号接收装置及接收信号的时钟恢复方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060913 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060913 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20070403 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081121 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090203 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20090402 |