JP2004046891A - データ処理システム、データ処理装置、外部装置及びデータ伝送方法 - Google Patents

データ処理システム、データ処理装置、外部装置及びデータ伝送方法 Download PDFInfo

- Publication number

- JP2004046891A JP2004046891A JP2003294636A JP2003294636A JP2004046891A JP 2004046891 A JP2004046891 A JP 2004046891A JP 2003294636 A JP2003294636 A JP 2003294636A JP 2003294636 A JP2003294636 A JP 2003294636A JP 2004046891 A JP2004046891 A JP 2004046891A

- Authority

- JP

- Japan

- Prior art keywords

- data

- data processing

- terminal

- memory card

- processing device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

Images

Landscapes

- Information Transfer Systems (AREA)

- Communication Control (AREA)

Abstract

【課題】 主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子を有することから、主データをシリアル通信を行うほか、リザーブ端子との組み合わせで更に他の機能を付加することができる。

【解決手段】 メモリカード20とデータの伝送を行なうデータ処理装置10とを含むデータ処理システムにおいて、データ処理装置10は、メモリカード20へのコマンドを生成し、メモリカード20からデータを受けるコントローラおよびメモリカードと通信するための複数の端子を有する。また、メモリカード10は、略カードの形状、データ処理装置10からのコマンドを受けるコントローラ、およびデータ処理装置10と通信するための複数の端子を有し、端子は、データ処理装置10が主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有する。

【選択図】 図1

【解決手段】 メモリカード20とデータの伝送を行なうデータ処理装置10とを含むデータ処理システムにおいて、データ処理装置10は、メモリカード20へのコマンドを生成し、メモリカード20からデータを受けるコントローラおよびメモリカードと通信するための複数の端子を有する。また、メモリカード10は、略カードの形状、データ処理装置10からのコマンドを受けるコントローラ、およびデータ処理装置10と通信するための複数の端子を有し、端子は、データ処理装置10が主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有する。

【選択図】 図1

Description

本発明は、少なくともシリアルインターフェースを用いて外部装置とデータの伝送を行うデータ処理システム、データ処理装置、外部装置及びデータ伝送方法に関する。

に関する。

に関する。

従来、フラッシュメモリ等の記憶媒体を内蔵するメモリカードが接続されるデータ処理装置が知られている。この種のデータ処理装置と、このデータ処理装置に接続されるメモリカードについて図面を用いて説明する。

データ処理装置100は、図11に示すように、データ処理部101と、レジスタ102と、ホスト側シリアルインターフェース回路103と、ホスト側コントローラ104とを備えている。また、メモリカード110は、メモリ111と、レジスタ112と、カード側シリアルインターフェース回路113と、カード側コントローラ114とを備えている。

データ処理装置100のデータ処理部101は、メモリカード110に記憶したデータを読み出して各種データ処理を行い、各種データ処理をしてメモリカード110に書き込むデータを生成する。すなわち、データ処理部101は、メモリカード110を用いる各種装置のデータ処理回路となる。

レジスタ102は、データ処理部101とホスト側シリアルインターフェース103とのバッファである。すなわち、データ処理装置100は、データ処理部101からホスト側シリアルインターフェース回路103にデータを供給する場合は、このレジスタ102に一時データを格納した後にホスト側シリアルインターフェース回路103に供給する。同様に、データ処理装置100は、ホスト側シリアルインターフェース回路103からデータ処理部101にデータを供給する場合は、このレジスタ102に一時データを格納した後にデータ処理部101に供給する。

ホスト側シリアルインターフェース回路103は、データ処理部101からレジスタ102を介して供給されるデータ及びカード側コントローラ114から供給されるコマンドをシリアル信号に変換してメモリカード110に供給する。また、ホスト側シリアルインターフェース回路103は、メモリカード110から供給されたシリアル信号のデータ及びコマンドをパラレル信号に変換して、データ処理部101及びカード側コントローラ114に供給する。

また、ホスト側シリアルインターフェース回路103は、データ及びコマンドの同期信号(CLK)及びチップセレクト信号(CS)をメモリカード110に供給する。さらに、ホスト側シリアルインターフェース回路103は、メモリカード110から供給されるビジー信号(BUSY)及びインタラプト信号(INTERRUPT)を取得する。

ホスト側コントローラ104は、データ処理部101のデータ処理動作、ホスト側シリアルインターフェース回路103の各データの伝送動作の制御を行う。また、ホスト側コントローラ104は、メモリカード110への制御命令となるコマンドをレジスタ112を介してメモリカード110に供給する。

一方、メモリカード110のメモリ111は、例えば、フラッシュメモリ等からなりデータ処理部101から供給されたデータを記憶する。

レジスタ112は、メモリ111とカード側シリアルインターフェース回路113とのバッファである。すなわち、メモリカード110は、メモリ111がデータ処理装置100からのデータを書き込む場合は、このレジスタ102に一時データを格納した後に書き込むデータをメモリ111に供給する。同様に、メモリカード110は、データ処理装置100がメモリ111からデータを読み出す場合は、このレジスタ102に一時データを格納した後に読み出すデータをカード側シリアルインターフェース回路113に供給する。このレジスタ112は、フラッシュメモリのページバッファの機能等を果たす回路である。

カード側シリアルインターフェース回路113は、カード側コントローラ114の制御に基づき、メモリ111から供給されるパラレル信号のデータ及びカード側コントローラ114から供給されるコマンドをシリアル信号に変換してデータ処理装置100に供給する。また、カード側シリアルインターフェース回路113は、データ処理装置100から供給されるシリアル信号のデータ及びコマンドをパラレル信号に変換して、メモリ111及びカード側コントローラ114に供給する。

さらに、カード側シリアルインターフェース回路113は、データ及びコマンドの同期信号(CLK)及びチップセレクト信号(CS)をデータ処理装置100から取得する。さらにまた、カード側シリアルインターフェース回路113は、ビジー信号(BUSY)及びインタラプト信号(INTERRUPT)をデータ処理装置100に供給する。

カード側コントローラ114は、メモリ111のデータの記憶動作、読み出し動作及び消去動作等をデータ処理装置100から供給されるコマンド等に基づき制御する。また、カード側コントローラ114は、カード側シリアルインターフェース回路113の各データの伝送動作の制御を行う。また、ホスト側コントローラ104は、メモリカード110のステータス信号となるビジー信号やインタラプト信号をメモリカード110から取得する。

以上のようなデータ処理装置100及びメモリカード110の間のデータの伝送は、ホスト側シリアルインターフェース回路103とカード側シリアルインターフェース回路113との間に設けられた伝送ラインを介して行われる。

データ処理装置100のカード側シリアルインターフェース回路113と、メモリカード110のカード側シリアルインターフェース回路113の間には、CLKラインとCSラインとDTラインとBUSYラインとINTラインとの5本の信号ラインが設けられている。

DTラインには、主データであるデータ処理部101によりデータ処理をしてメモリ111に書き込むデータ及びメモリ111からデータ処理部101に読み出すデータが伝送される。また、DTラインには、データ処理装置100からメモリカード110に供給する制御命令となるコマンドと、メモリカード110からデータ処理装置100に供給されるコマンドが伝送される。すなわち、DTラインには、主データ及びコマンドがシリアル信号で双方向伝送される。

CLKラインには、上述したDTラインに伝送される主データ及びコマンドの同期信号がデータ処理装置100からメモリカード110に供給される。

CSラインには、いわゆるチップセレクト信号がデータ処理装置100からメモリカード110に供給される。このチップセレクト信号は、例えばハイとなっている期間、上述した主データ、コマンド及び同期信号が有効であることを示している。

BUSYラインには、メモリカード110が処理を行っていることを示すビジー信号が伝送される。例えば、メモリカード110が書き込み処理を行っている場合であって、データ処理装置100からのアクセスを禁止するときには、このビジー信号がメモリカード110からデータ処理装置100に供給される。

INTラインには、メモリカード110からデータ処理装置100に対しての割り込みを示すインタラプト信号がメモリカード110からデータ処理装置100に供給される。

このような伝送ラインに伝送される各種信号のタイムチャートは、図12に示すようになる。この図12に示すタイムチャートを用いて、メモリカード110に記憶するデータを読み出す場合について説明する。

まず、時刻t11において、データ処理装置100は、CSラインを介してチップセレクト信号をメモリカード110に供給する。データ処理装置100は、このチップセレクト信号とともに同期信号をCLKラインを介して供給する。メモリカード110は、このチップセレクト信号を取得することにより、データ処理装置100から供給されるコマンドを取得する準備をする。そして、データ処理装置100は、このチップセレクト信号を供給すると、DTラインを介して読み出し命令を示すコマンドとそのアドレスをメモリカード110に供給する。

データ処理装置100は、この読み出しコマンド等を供給し終えると、時刻t12において、このコマンドと同期信号の供給を停止する。メモリカード110は、コマンドの取得をし終えると、この供給されたコマンドに基づく制御を行うため、ビジー信号をデータ処理装置100に供給する。すなわち、メモリカード110は、指定されたアドレスの主データをメモリ111からレジスタ112に読み出す制御を行う。なお、このとき、データ処理装置100は、チップセレクト信号の供給は停止しない。

メモリカード110は、レジスタ112に主データを読み出すと、時刻t13においてビジー信号の供給を停止する。すなわち、データ処理装置100に対して主データを伝送する準備ができたことを示すレディー状態を知らせる。

データ処理装置100は、ビジー信号の供給が停止したことを知ると、メモリカード110が供給したコマンドに基づく制御が終了したと判断して、時刻t14において同期信号をメモリカード110に供給する。そして、メモリカード110は、主データをDTラインを介してデータ処理装置100に伝送する。

そして、メモリカード110が主データの伝送を終了すると、データ処理装置100は、時刻t15において同期信号とチップセレクト信号の供給を停止する。

なお、メモリカード110は、この読み出し処理をした結果等により、メモリカード110の内部状態に変化が生じた場合、時刻t16に示すように、INTラインを介して割り込みを示すインタラプト信号をデータ処理装置100に供給する。データ処理装置100は、このインタラプト信号が供給されると、この割り込み要因をメモリカード110から取得するため、チップセレクト信号とともに所定のコマンドをメモリカード110に供給する。

以上のように、データ処理装置100は、主データ及びコマンドを伝送するDTライン及び同期信号を供給するCLKラインとともに、チップセレクト信号を供給するCSライン、ビジー信号を取得するBUSYライン及びインタラプト信号を取得するINTラインを設けてメモリカード110とのデータの伝送を実現している。

ところで、上述した外部記憶装置であるメモリカード110の小型化等を考えた場合、データ処理装置100とメモリカード110との信号ラインの数を少なくする必要が生じる。

本発明は、このような実情を鑑みてなされたものであり、主データをシリアル通信するためのデータ端子のほかに予備の端子であるリザーブ端子を設けることで、主データをシリアル通信を行うほか、リザーブ端子との組み合わせで更に他の機能を付加することができるデータ処理システム、データ処理装置、外部装置及びデータ伝送方法を提供することを目的とする。

本発明に係るデータ処理システムは、外部装置とデータの伝送を行なうデータ処理装置とを含むデータ処理システムにおいて、データ処理装置は、外部装置へのコマンドを生成し、外部装置からデータを受けるコントローラおよび上記外部装置と通信するための複数の端子を有し、外部装置は、略カードの形状、上記データ処理装置からのコマンドを受けるコントローラ、および上記データ処理装置と通信するための複数の端子を有し、上記外部装置の上記端子は、上記外部装置と上記データ処理装置が主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有する。

本発明に係るデータ処理装置は、外部装置とデータ伝送を行うデータ処理装置において、上記外部装置へのコマンドを生成し、上記外部装置からデータを受けるコントローラおよび上記外部装置と通信するための複数の端子を有し、上記複数の端子は、上記外部装置と主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有する。

本発明に係る外部装置は、データ処理装置とデータ伝送を行う外部装置において、略カードの形状、上記データ処理装置からのコマンドを受けるコントローラ、および上記データ処理装置と通信するための複数の端子を有し、上記端子は、上記外部装置と上記データ処理装置が主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有する。

本発明に係るデータ伝送方法は、外部装置とデータ処理装置との間でデータ伝送を行うデータ伝送方法において、データ処理装置は、外部装置へのコマンドを生成し、外部装置からデータを受けるコントローラおよび上記外部装置と通信するための複数の端子を有し、外部装置は、略カードの形状、上記データ処理装置からのコマンドを受けるコントローラ、および上記データ処理装置と通信するための複数の端子を有し、上記外部装置の上記端子は、上記外部装置と上記データ処理装置が主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有し、上記データ処理装置で生成されたコマンドに応じて上記外部装置と上記データ処理装置との間で主データのシリアル通信を行う。

上述したように、本発明は、主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子を有することから、主データをシリアル通信を行うほか、リザーブ端子との組み合わせで更に他の機能を付加することができる。

以下、本発明に係るデータ処理装置及びデータ伝送方法に用いられるデータ処理装置とこのデータ処理装置に用いられる外部記憶装置であるメモリカードについて、図面を参照しながら説明する。

まず、本発明にデータ処理システムを構成するデータ処理装置を説明すると、このデータ処理装置10は、図1に示すように、データ処理部11と、レジスタ12と、ホスト側シリアルインターフェース回路13と、ホスト側コントローラ14とを備えている。また、メモリカード20は、外観がカード状の記憶媒体であり、データ処理装置10に接続されて外部記憶装置として用いられる。メモリカード20は、メモリ21とレジスタ22とカード側シリアルインターフェース回路23とカード側コントローラ24とを備えている。

データ処理装置10のデータ処理部11は、メモリカード20に記憶したデータを読み出して各種データ処理を行い、各種データ処理をしてメモリカード20に書き込むデータを生成する。このデータ処理部11は、メモリカード20を用いる例えばコンピュータ装置や、デジタルオーディオ信号の記録再生装置、カメラ装置等のオーディオビジュアル機器のデータ処理回路となる。

レジスタ12は、データ処理部11とホスト側シリアルインターフェース13とのバッファである。すなわち、データ処理装置10は、データ処理部11からホスト側シリアルインターフェース回路13にデータを供給する場合は、データをこのレジスタ12に一時格納した後にホスト側シリアルインターフェース回路13に供給する。同様に、データ処理装置10は、ホスト側シリアルインターフェース回路13からデータ処理部11にデータを供給する場合は、データをこのレジスタ12に一時格納した後にデータ処理部11に供給する。

ホスト側シリアルインターフェース回路13は、データ処理部11からレジスタ12を介して供給されたデータ及びカード側コントローラ24から供給されるコマンドをシリアル信号に変換してメモリカード20に供給する。また、ホスト側シリアルインターフェース回路13は、メモリカード20から供給されたシリアル信号のデータ及びコマンドをパラレル信号に変換してデータ処理部11及びカード側コントローラ24に供給する。

また、ホスト側シリアルインターフェース回路13は、各種データ及びコマンドの同期信号(CLK)等をメモリカード20に供給する。さらに、ホスト側シリアルインターフェース回路13は、メモリカード20から供給されこのメモリカード20の動作状態を示すステータス(STATUS)信号を取得する。

ホスト側コントローラ14は、データ処理部11のデータ処理動作、ホスト側シリアルインターフェース回路13の各データの伝送動作の制御を行う。また、ホスト側コントローラ14は、メモリカード20への制御命令となるコマンドをレジスタ22を介してメモリカード20に供給する。

一方、メモリカード20のメモリ21は、例えば、フラッシュメモリ等からなり、データ処理部11から供給されたデータを記憶する。

レジスタ22は、メモリ21とカード側シリアルインターフェース回路23とのバッファであり、メモリ21がデータ処理装置10からのデータを書き込む場合は、このレジスタ12に一時データを格納した後に書き込むデータをメモリ21に供給する。同様に、データ処理装置10がメモリ21からデータを読み出す場合は、このレジスタ12に一時データを格納した後に読み出すデータをカード側シリアルインターフェース回路23に供給する。すなわち、このレジスタ22は、フラッシュメモリのいわゆるページバッファの機能等を果たす回路である。

カード側シリアルインターフェース回路23は、カード側コントローラ24の制御に基づきメモリ21から供給されるパラレル信号のデータ及びカード側コントローラ24から供給されるコマンドをシリアル信号に変換してデータ処理装置10に供給する。また、カード側シリアルインターフェース回路23は、データ処理装置10から供給されるシリアル信号のデータ及びコマンドをパラレル信号に変換してメモリ21及びカード側コントローラ24に供給する。

また、カード側シリアルインターフェース回路23は、各種データ及びコマンドの同期信号(CLK)等をデータ処理装置10から取得する。さらに、カード側シリアルインターフェース回路23は、ステータス信号をデータ処理装置10に供給する。

カード側コントローラ24は、メモリ21のデータの記憶動作、読み出し動作及び消去動作等をデータ処理装置10から供給されるコマンド等に基づき制御する。また、カード側コントローラ24は、カード側シリアルインターフェース回路23の各データの伝送動作の制御を行う。さらに、ホスト側コントローラ14は、メモリカード20へのステータス信号をメモリカード20に供給する制御を行う。

以上のようなデータ処理装置10及びメモリカード20の間のデータの伝送は、ホスト側シリアルインターフェース回路13とカード側シリアルインターフェース回路23との間に設けられた伝送ラインを介して行われる。

データ処理装置10のカード側シリアルインターフェース回路23と、メモリカード20のカード側シリアルインターフェース回路23の間には、CLKライン31とコントロールライン32とDTライン33との3本の信号ラインが設けられている。

DTライン33には、主データであるデータ処理部11によりデータ処理をしてメモリ21に書き込むデータ及びメモリ21からデータ処理部11に読み出すデータが伝送される。このDTライン33には、データ処理装置10からメモリカード20に供給する制御命令となるコマンドと、メモリカード20からデータ処理装置10に供給されるコマンドが伝送される。すなわち、DTライン33には、主データ及びコマンドがシリアル信号で双方向伝送される。

さらに、DTライン33には、一端が接地された抵抗33aが取り付けられている。この抵抗33aは、いわゆるプルダウン抵抗であり、ホスト側シリアルインターフェース回路13とカード側シリアルインターフェース回路23との間でのDTライン33による信号の送受信がなされていないとき、DTライン33の信号レベルはローレベルとなる。換言すれば、DTライン33による信号の送受信がなされていないとき、DTライン33の信号レベルは抵抗33aの抵抗値等によって定まる一定のレベルとなる。

なお、ここで、抵抗33aとしていわゆるプルダウン抵抗を採用し、DTライン33による信号の送受信がなされていないとき、DTライン33の信号レベルがローレベルとなるようにしたが、抵抗33aとしていわゆるプルアップ抵抗を採用し、DTライン33による信号の送受信がなされていないとき、DTライン33の信号レベルがハイレベルとなるようにしてもよい。

CLKライン31には、上述したDTライン33に伝送される主データ及びコマンドの同期信号がデータ処理装置10からメモリカード20に伝送される。

コントロールライン32には、コントロール信号がデータ処理装置10からメモリカード20に伝送される。このコントロール信号が供給されている期間、例えばハイとなっている期間上述した主データ及びコマンドが伝送される。

ここで、上述したDTライン33には、主データ及びコマンドに加えて、メモリカード20の動作状態を示すステータス(STATUS)信号がメモリカード20からデータ処理装置10に供給される。このメモリカード20からのステータス信号は、DTライン33に主データ及びコマンドが伝送されていない期間、すなわち、コントロール信号が供給されていない期間、例えばローの期間に供給される。このステータス信号には、メモリカード20が処理を行っていることを示すビジー(BUSY)信号がある。例えば、メモリカード20が書き込み処理を行っている場合であってデータ処理装置10からのアクセスを禁止するときには、ビジー信号がメモリカード20からデータ処理装置10に供給される。

また、ステータス信号には、メモリカード20からデータ処理装置10に対しての割り込みを示すインタラプト(INTERRPUT)信号がある。例えば、メモリカード20からデータ処理装置10に対して割り込み命令を要求するときには、このインタラプト信号が供給される。なお、このビジー信号やインタラプト信号は一例であり、ステータス信号としてメモリカード20の動作状態を示す信号であればどのような信号であってもよい。

このように、コントロール信号が供給されていない期間にステータス信号を供給するには、図2に示すような出力回路をメモリカード20に設ければよい。

メモリカード20の出力回路25は、カード側シリアルインターフェース回路23とDTライン33の入出力端子との間に設けられ、入力バッファ26と出力バッファ27と切換スイッチ28とオア回路29とからなる。

入力バッファ26は、DTライン33と接続され、データ処理装置10から供給されたシリアル信号が入力されこのシリアル信号をカード側シリアルインターフェース回路23に供給する。

出力バッファ27は、切換スイッチ28を介して供給されるシリアル信号、ビジー信号及びインタラプト信号をDTライン33に出力する。

また、カード側コントローラ24から供給されるビジー信号及びインタラプト信号は、オア回路23により論理和がとられ、切換スイッチ28の端子28bに供給される。また、カード側シリアルインターフェース回路23から供給されるシリアル信号は、切換スイッチ28の端子28aに供給される。

切換スイッチ28は、コントロール信号がハイのときは、端子28a側に切り換えられる。切換スイッチ28が端子28a側に切り換えられると、カード側シリアルインターフェース回路23からのシリアル信号が、出力バッファ27に供給される。また、切換スイッチ28は、コントロール信号がローのときは、端子28b側に切り換えられる。切換スイッチ28が端子28b側に切り換えられると、カード側コントローラ24からのビジー信号及びインタラプト信号等のステータス信号は出力バッファ27に供給される。

このような伝送ラインに伝送される各種信号のタイムチャートは、図3に示すようになる。この図3に示すタイムチャートを用いて、メモリカード20に記憶する主データを読み出す場合について説明する。

まず、時刻t21において、データ処理装置10は、コントロールライン32を介してコントロール信号をメモリカード20に供給する。メモリカード20は、このコントロール信号を取得することによりデータ処理装置10から供給されるコマンドを取得する準備をする。データ処理装置10は、このコントロール信号を供給するとともに、DTライン33を介して読み出し命令を示すコマンド等をメモリカード20に供給する。また、データ処理装置10は、このコマンド等とともにCLKライン31を介して同期信号をメモリカード20に供給する。

データ処理装置10は、この読み出しコマンド等を供給し終えると、時刻t22において、コマンド、コントロール信号及び同期信号の供給を停止する。なお、同期信号は、この時刻t22において供給を停止しなくてもよい。

メモリカード20は、コマンドの取得をし終えると、この供給されたコマンドに基づく制御を行うため、ビジー信号をDTライン33を介してデータ処理装置10に供給する。データ処理装置10は、この時点でコントロール信号を供給していないため、メモリカード20から供給された信号がビジー信号であるということを判断することができる。メモリカード20は、ビジー信号を供給すると、指定されたアドレスの主データをメモリ21からレジスタ22に読み出す。

メモリカード20は、レジスタ22に主データを読み出すと、時刻t23においてDTライン33を介してビジー信号の供給を停止する。すなわち、データ処理装置10に対して主データを供給する準備ができたことを示すレディー状態を知らせる。

データ処理装置10は、時刻t24において、ビジー信号の供給が停止したことを知ると、メモリカード20が供給したコマンドに基づく制御が終了したと判断してコントロール信号と同期信号の供給をする。メモリカード20は、コントロール信号が供給されたことに基づき主データをDTライン33を介してこの供給された同期信号に同期させてデータ処理装置10に伝送する。

メモリカード20が主データの伝送を終了すると、データ処理装置10は、時刻t25において同期信号とコントロール信号の供給を停止する。

なお、メモリカード20は、この読み出し処理をした結果等により、メモリカード20の内部状態に変化が生じた場合は、必要に応じて時刻t26に示すようにDTライン33を介して割り込みを示すインタラプト信号をデータ処理装置10に供給する。データ処理装置10は、コントロール信号を供給していないことからメモリカード20から供給された信号がインタラプト信号であると判断でき、このインタラプト信号が供給されると、例えば、この割り込み要因をメモリカード20から取得するためコントロール信号を供給して対応したコマンドの供給を行う。

以上のように、データ処理装置10及びメモリカード20では、メモリカード20からのステータス信号をDTライン33を用いて伝送することにより信号ラインを少なくすることができる。従って、ビジー信号やインタラプト信号のための信号ラインを特別に設ける必要がなく、簡単な構成で確実なデータの伝送をすることができる。また、インタラプト信号を設けずにデータ処理装置とメモリカードの間でデータの伝送を行った場合には、必ず一定時間毎ポーリングを行わなければならなかったが、このデータ処理装置10ではポーリングの必要がない。

ところで、以上のようなデータ処理装置10とメモリカード20との間のデータ伝送の場合、データ処理装置10からメモリカード20に供給するコマンドの内容、又はメモリカード20からデータ処理装置10に供給するコマンドの内容は予めホスト側コントローラ14やカード側コントローラ24により定められている。例えば、書き込みコマンド、読み出しコマンド又は消去コマンド等が予め定められている。これらのコマンドがDTライン33を介して伝送された場合、この後にDTライン33に伝送されるデータやコマンド、あるいは、ステータス信号の順序は必ず決定される。

具体的には、データ処理装置10からメモリカード20に対して書き込みコマンドが伝送された場合には、この書き込みコマンドの後にメモリカード20に書き込もうとする主データがデータ処理装置10からメモリカード20に伝送される。書き込みコマンド及び主データが伝送されたメモリカード20は、当該主データの書き込み処理を行っている間、ビジー信号をデータ処理装置10へ出力し、当該主データの書き込み処理が完了したらレディ信号をデータ処理装置10へ出力する。また、データ処理装置10からメモリカード20に対して読み出しコマンドが伝送された場合、メモリカード20は、当該読み出しコマンドに応じた主データの読み出し処理を行う。この読み出し処理を行っている間メモリカード20はビジー信号をデータ処理装置10へ出力し、読み出し処理が完了したらメモリカード20はレディ信号をデータ処理装置10へ出力する。データ処理装置10がレディ信号を受け取った後、メモリカード20からデータ処理装置10に対して主データが伝送され、これにより主データの読み出しが行われる。

そこで、以下に第2のデータ伝送方法として、このようにDTライン33によって伝送されるデータの内容やその順序等がコマンドにより予め定められている場合について説明する。

この第2のデータ伝送方法では、コントロール信号を切り換えることによって、DTライン33を伝送するデータの状態を設定する。すなわち、コントロール信号を切り換えることによって、伝送するデータの状態を確定してデータの伝送を行う。

DTライン33によって伝送されるデータの状態は、以下のように設定される。まず、データ処理装置10からメモリカード20に対して何等制御命令すなわちコマンドを供給せず、また、メモリカード20が何等処理をしていない状態を初期状態として“状態0”とする。続いて、データ処理装置10からメモリカード20に対してコマンドを供給している状態、例えば、書き込みコマンド、読み出しコマンド又は消去コマンド等をDTライン33を介して供給している状態を“状態1”とする。その後、“状態1”で供給したコマンドに応じた処理が行われる“状態2”“状態3”へと推移し、“状態3”の後に“状態0”へと戻る。

そして、コントロール信号は、このような“状態0”から“状態3”までの状態を切り換える。すなわち、“状態0”では、このコントロール信号はローとなっており、この“状態0”の状態からコントロール信号がハイとなると、“状態1”に切り換わる。続いて、“状態1”の状態からコントロール信号がローとなると“状態2”に切り換わる。続いて、“状態2”の状態からコントロール信号がハイとなると、“状態3”に切り換わる。最後に、“状態3”の状態からコントロール信号がローとなると、“状態0”に切り換わる。

このように、コントロール信号を切り換えることで、DTライン33によって伝送されるデータの内容を切り換える。そして、データ処理装置10及びメモリカード20は、“状態1”において伝送されたコマンドの内容に応じて、次の“状態2”、“状態3”に伝送するデータの内容を確定しそれぞれの状態に応じた処理を行う。

具体的には、例えば、メモリカード20からの主データの読み出しを行う場合には、まず、“状態1”とされ、データ処理装置10からメモリカード20へ読み出しコマンドが伝送される。次に、“状態2”となり、読み出しコマンドに応じてメモリカード20によって主データの読み出し処理が行われる。この処理を行っている間、メモリカード20からデータ処理装置10にビジー信号が伝送され、当該処理が完了したら、メモリカード20からデータ処理装置10にレディ信号が伝送される。そして、データ処理装置10によってレディ信号が検出されたら“状態3”となり、メモリカード20から読み出された主データがDTライン33を介してメモリカード20からデータ処理装置10へ伝送される。そして、主データの伝送が完了したら“状態0”へ戻る。

あるいは、例えば、メモリカード20への主データの書き込みを行う場合には、まず、“状態1”とされ、データ処理装置10からメモリカード20へ書き込みコマンドが伝送される。次に、“状態2”となり、メモリカード20へ書き込む主データがDTライン33を介してデータ処理装置10からメモリカード20に伝送される。次に、“状態3”となり、書き込みコマンドに応じてメモリカード20によって主データの書き込み処理が行われる。この処理を行っている間、メモリカード20からデータ処理装置10へビジー信号が伝送され、当該処理が完了したら、メモリカード20からデータ処理装置10へレディ信号が伝送される。そして、データ処理装置10によってレディ信号が検出されたら“状態0”へ戻る。

あるいは、例えば、メモリカード20に書き込まれている主データの消去を行う場合には、まず、“状態1”のときに、データ処理装置10からメモリカード20へ消去コマンドが伝送される。次に、“状態2”となり、消去コマンドに応じてメモリカード20によって主データの消去処理が行われる。この処理を行っている間、メモリカード20からデータ処理装置10にビジー信号が伝送され、当該処理が完了したら、メモリカード20からデータ処理装置10にレディ信号が伝送される。そして、データ処理装置10によってレディ信号が検出されたら“状態0”へ戻る。

このように、DTライン33に伝送されるデータに応じてコントロール信号を切り換えることにより、データ伝送の状態を制御する第2のデータ伝送方法について、図4及び図5のタイムチャートを参照して更に詳細に説明する。ここで、図4に示すタイムチャートは、データ処理装置10によってメモリカード20に書き込まれている主データを読み出すときのタイムチャートの一例である。また、図5に示すタイムチャートは、データ処理装置10によってメモリカード20に主データを書き込むときのタイムチャートの一例である。

まず、図4を参照して主データの読み出しについて説明する。

データ処理装置10とメモリカード20との間で何等データの伝送が行われていない状態では、コントロール信号がローとなっており、“状態0”の初期状態となっている。そして、主データの読み出しに関する処理は、この“状態0”の初期状態から開始される。

主データの読み出しに関する処理を開始する時刻t31において、データ処理装置10は、コントロールライン32を介してメモリカード20に供給されるコントロール信号をローからハイに切り換える。従って、DTライン33に伝送されるデータの状態は、“状態0”から“状態1”に切り換えられる。メモリカード20は、このコントロール信号を取得することにより、“状態0”から“状態1”となったことを判断して、データ処理装置10から供給されるコマンドを取得する準備をする。そして、データ処理装置10は、この“状態1”のときに、DTライン33を介して読み出しコマンドをメモリカード20に供給するとともに、その同期信号をCLKライン31を介してメモリカード20に供給する。ここで、メモリカード20は、この“状態1”の状態で読み出しコマンドを取得することにより、後の“状態2”及び“状態3”でDTライン33を介して伝送されるデータの内容を確定する。

データ処理装置10は、読み出しコマンドの供給が完了した時刻t32においてコントロール信号をハイからローに切り換える。すなわち、“状態1”から“状態2”に切り換える。

“状態2”となったら、メモリカード20は、“状態1”のときに供給された読み出しコマンドに基づく処理、具体的には、読み出しコマンドで指定されたアドレスの主データをメモリ21からレジスタ22に読み出す処理を行う。この処理を行っている間、メモリカード20は、ステータス信号としてビジー信号をDTライン33を介してデータ処理装置10に供給する。すなわち、“状態2”のとき、メモリカード20は、まず、ステータス信号としてビジー信号を出力する。このとき、データ処理装置10は、メモリカード20に供給したコマンドが読み出しコマンドであり、且つ現在の状態が“状態2”であることから、メモリカード20から出力されている信号がステータス信号であると判断する。

その後、レジスタ22への主データの読み出しが完了したら、メモリカード20は、レジスタ22への主データの読み出しが完了した時刻t33において、DTライン33を介してステータス信号としてビジー信号の出力を停止してデータ処理装置10に対して主データを供給する準備ができたことを示すレディー信号の出力を開始する。すなわち、“状態2”のとき、メモリカード20は、レジスタ22への主データの読み出しが完了したらステータス信号としてレディ信号を出力する。

なお、本例では、“状態2”のときに、DTライン33を介してメモリカード20から出力される信号がハイのときをビジー信号として、ローのときをレディ信号としている。この“状態2”のとき、データ処理装置10は、メモリカード20に供給したコマンドが読み出しコマンドであり、且つ現在の状態が“状態2”であることから、メモリカード20から出力されている信号がステータス信号であると判断することができる。したがって、メモリカード20からDTライン33を介して出力される信号をハイからローに切り換えるだけでも、データ処理装置10は、当該信号がビジー信号からレディ信号に切り換わったことを検出することができる。

データ処理装置10は、メモリカード20からレディ信号を受け取ったら、読み出しコマンドに基づくメモリカード20の処理が完了したと判断する。そして、読み出しコマンドに基づくメモリカード20の処理が完了したと判断された時刻t34においてコントロール信号をローからハイに切り換える。すなわち、“状態2”から“状態3”に切り換える。

そして、“状態3”となったら、メモリカード20は、“状態2”のときにレジスタ22へ読み出した主データをDTライン33を介してデータ処理装置10に伝送する。その後、メモリカード20からデータ処理装置10への主データの伝送が完了した時刻t35において、データ処理装置10は、同期信号の供給を止めるとともにコントロール信号をハイからローに切り換える。すなわち、主データの伝送を行う“状態3”から、初期状態の“状態0”へと状態が戻される。

なお、以上のような読み出し処理の影響等により、メモリカード20の内部状態に変化が生じて何らかの割り込み処理を行う必要が生じた場合、メモリカード20は、時刻t36に示すように、“状態0”のときに割り込みを示すインタラプト信号をDTライン33を介してデータ処理装置10に供給する。ここで、データ処理装置10は、“状態0”のときにメモリカード20からDTライン33を介して信号が供給されたときには当該信号がインタラプト信号であると判別するように予め設定しておく。これにより、この信号は、データ処理装置10によってインタラプト信号であると判断される。このインタラプト信号を受け取ったデータ処理装置10は、当該インタラプト信号に基づいて必要な処理を行う。

次に、図5を参照して主データの書き込みについて説明する。

データ処理装置10とメモリカード20との間で何等データの伝送が行われていない状態では、コントロール信号がローとなっており、“状態0”の初期状態となっている。主データの書き込みに関する処理は、この“状態0”の初期状態から開始される。

主データの書き込みに関する処理を開始する時刻t41において、データ処理装置10は、コントロールライン32を介してメモリカード20に供給されるコントロール信号をローからハイに切り換える。従って、DTライン33に伝送されるデータの状態は、“状態0”から“状態1”に切り換えられる。メモリカード20は、このコントロール信号を取得することにより、“状態0”から“状態1”となったことを判断して、データ処理装置10から供給されるコマンドを取得する準備をする。そして、データ処理装置10は、この“状態1”のときに、DTライン33を介して書き込みコマンドをメモリカード20に供給するとともに、その同期信号をCLKライン31を介してメモリカード20に供給する。ここで、メモリカード20は、この“状態1”の状態で書き込みコマンドを取得することにより、後の“状態2”及び“状態3”でDTライン33を介して伝送されるデータの内容を確定する。

データ処理装置10は、書き込みコマンドの供給が完了した時刻t42において、コントロール信号をハイからローに切り換える。すなわち、“状態1”から“状態2”に切り換える。

“状態2”のとき、データ処理装置10は、メモリカード20に書き込もうとする主データをDTライン33を介してメモリカード20へ伝送し、この主データのメモリカード20への伝送が完了した時刻t43においてコントロール信号をローからハイに切り換える。すなわち、“状態2”から“状態3”に切り換える。

“状態3”となったら、メモリカード20は、“状態1”のときに供給された書き込みコマンドに基づく処理、具体的には、“状態2”のときにデータ処理装置10から伝送された主データをメモリ21に書き込む処理を行う。この処理を行っている間、メモリカード20は、ステータス信号としてビジー信号をDTライン33を介してデータ処理装置10に供給する。すなわち、“状態3”のとき、メモリカード20は、まず、ステータス信号としてビジー信号を出力する。このとき、データ処理装置10は、メモリカード20に供給したコマンドが書き込みコマンドであり、且つ現在の状態が“状態3”であることから、メモリカード20から出力されている信号がステータス信号であると判断する。

その後、レジスタ22への主データの書き込みが完了したら、メモリカード20は、レジスタ22への主データの書き込みが完了した時刻t44において、ステータス信号として、ビジー信号の出力を停止して、主データの書き込みが完了したことを示すレディー信号の出力を開始する。すなわち、“状態3”のとき、メモリカード20は、レジスタ22への主データの書き込みが完了したらステータス信号としてレディ信号を出力する。

なお、本例では、“状態3”のときに、DTライン33を介してメモリカード20から出力される信号がハイのときをビジー信号として、ローのときをレディ信号としている。この“状態3”のとき、データ処理装置10は、メモリカード20に供給したコマンドが書き込みコマンドであり、且つ現在の状態が“状態3”であることからメモリカード20から出力されている信号がステータス信号であると判断することができる。したがって、メモリカード20からDTライン33を介して出力される信号をハイからローに切り換えるだけでも、データ処理装置10は、当該信号がビジー信号からレディ信号に切り換わったことを検出することができる。

データ処理装置10は、メモリカード20からレディ信号を受け取ったら書き込みコマンドに基づくメモリカード20の処理が完了したと判断する。そして、書き込みコマンドに基づくメモリカード20の処理が完了したと判断された時刻t45において、データ処理装置10は、同期信号の供給を止めるとともに、コントロール信号をハイからローに切り換える。すなわち、主データの書き込みを行っている状態である“状態3”から、初期状態の“状態0”へと状態が戻される。

なお、以上のような書き込み処理の影響等により、メモリカード20の内部状態に変化が生じて、何らかの割り込み処理を行う必要が生じた場合、メモリカード20は、時刻t46に示すように、“状態0”のときに割り込みを示すインタラプト信号をDTライン33を介してデータ処理装置10に供給する。ここで、データ処理装置10は、“状態0”のときにメモリカード20からDTライン33を介して信号が供給されたときには、当該信号がインタラプト信号であると判別するように予め設定しておく。これにより、この信号は、データ処理装置10によってインタラプト信号であると判断される。そして、このインタラプト信号を受け取ったデータ処理装置10は、当該インタラプト信号に基づいて必要な処理を行う。

以上のように、本発明を適用したデータ処理装置10及びメモリカード20では、コントロール信号を切り換えてDTライン33に伝送するデータの内容を確定するようにしており、これにより、DTライン33によってコマンドや主データだけでなくステータス信号やインタラプト信号も伝送することが可能となっている。そのため、データ処理装置10とメモリカード20との間の信号ラインを少なくすることができる。従って、ビジー信号やインタラプト信号のための信号ラインを特別に設ける必要がなく、簡単な構成で確実なデータの伝送をすることができる。また、DTライン33に伝送させるデータの切り換えのオーバーヘッドを少なくすることもでき、データの伝送の効率が高くなる。

なお、上述の例ではデータ処理装置10とメモリカード20の場合を挙げて説明したが、本発明をメモリカード20ではなく、他のデータ処理装置に適用することができる。この場合は、予め、伝送されるコマンド等を他のデータ処理装置に設定しておくことが必要となるが、メモリカード20に対するコマンドのみならず、あらゆるコマンドを伝送することができる。

また、データ処理装置10とメモリカード20との間の第2のデータの伝送方法の説明では、コントロール信号で切り換えるDTライン33の伝送データの内容を、状態0、状態1、状態2、状態3の4パターンについて例示して説明したが、この4パターンに限らず伝送するコマンドの内容に応じてこれ以上のパターンに切り換えてもよい。

さらに、データ処理装置10とメモリカード20との間の第2のデータの伝送方法の説明では、DTライン33の伝送データの状態をコントロール信号のオンオフで切り換える場合について説明したが、図6や図7に示すように、パルス信号で切り換えるようにしてもよい。なお、図6及び図7は、コントロール信号としてパルス信号を用いたときのタイムチャートであり、図6は、図4と同様にデータ処理装置10によってメモリカード20に書き込まれている主データを読み出すときのタイムチャート、図7は、図5と同様にデータ処理装置10によってメモリカード20に主データを書き込むときのタイムチャートである。

さらに、以上説明したメモリカード20には、例えば、CLKライン31、コントロールライン32及びDTライン33の他に、1本の電源ライン、3本のグランドライン及び3本のリザーブラインを設けて合計10本の信号ラインを有している。なお、3本のリザーブラインを設けたときには、これら3本のリザーブラインをDTラインとして使用して先のDTライン33と合わせてDTラインを4本とし、これら4本のDTラインをパラレルに使用するようにしてもよい。また、3本のリザーブラインを設けたときには、これら3本のリザーブラインをそれぞれCLKライン、コントロールライン及びDTラインとして使用して、先のCLKライン31、コントロールライン32及びDTライン33と合わせて、CLKライン、コントロールライン及びDTラインの組みを2つ設けるようにしてもよい。

ところで、以上の説明で挙げた第2のデータ伝送方法において、DTライン33で伝送されるコマンドや主データについては、エラー訂正コード等を一緒に伝送することで、外部からのノイズ等に対処できるが、コントロールライン31で伝送されるコントロール信号については、ハイからローへの切り換え、又はローからハイへの切り換えだけで、“状態0”、“状態1”、“状態2”、“状態3”の推移を示すようにしているので外部からのノイズ等の影響を受けるおそれがある。

例えば、図4及び図5に挙げた例では、“状態0”及び“状態2”のときにコントロール信号をローとして、“状態1”及び“状態3”のときにコントロール信号をハイとしている。そして、“状態0”と“状態2”との判別や、“状態1”と“状態3”との判別は、それらの状態の推移を追うことにより判別するようにしている。したがって、状態の推移が正しく検出されないと、メモリカード20は、“状態0”と“状態2”とを間違えて判断してしまったり、“状態1”と“状態3”とを間違えて判断してしまったりするおそれがある。

例えば、図4に示すように主データの読み出しを行う際に、コントロール信号にノイズがのり、メモリカード20が“状態1”と“状態3”とを間違えて判断してしまうと、データ処理装置10からメモリカード20に送られるコマンドとメモリカード20から読み出された主データとがDTライン33上でぶつかってしまう可能性がある。

また、図4に示すように主データの読み出しを行う際に、コントロール信号にノイズがのり、メモリカード20が“状態0”と“状態2”とを間違えて判断してしまうと、“状態2”のときに出力すべきビジー信号やレディ信号が“状態0”のときに送出されてしまったり、“状態0”のときに出力すべきインタラプト信号が“状態2”のときに送出されてしまったりする可能性がある。

さらに、図5に示すように主データの書き込みを行う際に、コントロール信号にノイズがのり、メモリカード20が“状態1”と“状態3”とを間違えて判断してしまうと、データ処理装置10からメモリカード20に送られるコマンドとメモリカード20から出力されるステータス信号とがDTライン33上でぶつかってしまう可能性がある。あるいは、データ処理装置10の側はメモリカード20からのレディ信号を待ち、メモリカード20の側はデータ処理装置10からのコマンドを待つような状態となり、DTライン33でのデータの送受信が止まってしまう可能性もある。

さらにまた、図5に示すように主データの書き込みを行う際に、コントロール信号にノイズがのり、メモリカード20が“状態0”と“状態2”とを間違えて判断してしまうと、データ処理装置10からメモリカード20に送られる主データとメモリカード20から出力されたインタラプト信号がDTライン33上でぶつかってしまう可能性がある。

以上のような問題を回避するには、例えば、レディ信号を所定の周期にて信号レベルの変化が繰り返される信号とし、メモリカード20からの信号出力がない状態をビジー信号として検出するようにすればよい。以下、このようにレディ信号及びビジー信号を検出するようにした例について具体的に説明する。

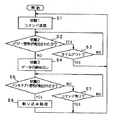

なお、以下の説明では、メモリカード20に書き込まれている主データを読み出す場合を例に挙げ、図8のタイムチャート、図9及び図10のフローチャートを参照して説明する。ここで、図8は、図4と同様にメモリカード20に書き込まれている主データを読み出すときのタイムチャートであるが、本例ではビジー信号やレディ信号の内容が図4の例とは異なる。また、図9は、メモリカード20に書き込まれている主データを読み出す際のデータ処理装置10の側の処理の流れを示すフローチャートであり、図10は、メモリカード20に書き込まれている主データを読み出す際のメモリカード20の側の処理の流れを示すフローチャートである。

まず、図8及び図9を参照しながら、データ処理装置10側の処理について説明する。

メモリカード20から主データを読み出すとき、データ処理装置10は、まず、メモリカード20からの主データの読み出しを指示するコマンドである読み出しコマンドをレジスタ12に書き込む。その後、ステップS1に示すように、データ処理装置10は、ホスト側コントローラ14の制御により、ホスト側シリアルインターフェース回路13から出力されるコントロール信号をハイにして“状態1”にする(図8の時刻t51)。また、この“状態1”のとき、データ処理装置10は、レジスタ12からホスト側シリアルインターフェース回路13へ読み出しコマンドを読み出し、当該読み出しコマンドにエラー訂正コード等を付けた上で当該読み出しコマンドをDTライン33を介してメモリカード20へ送出する。

読み出しコマンドの送出が完了したら、データ処理装置10は、ホスト側コントローラ14の制御により、ホスト側シリアルインターフェース回路13から出力されるコントロール信号をローにして“状態2”にする(図8の時刻t52)。この“状態2”のとき、データ処理装置10は、メモリカード20から送られてくるステータス信号の検出を行う。そして、ステップS2において、データ処理装置10は、ビジー信号が検出されたか否かを判断する。

このとき、ホスト側シリアルインターフェース回路13は、DTライン33を介して送られてくる信号が信号レベルに特別な変化のないほぼ一定の信号(以下、DC信号と称する。)の場合には、当該DC信号がメモリカード20が信号の入力を受け付けない状態であることを示すビジー信号であると判断する。また、DTライン33を介して送られてくる信号が所定の周期にて信号レベルの変化が繰り返される信号(以下、AC信号と称する。)の場合には、当該信号がメモリカード20が信号の入力待ち状態であることを示すレディ信号であると判断する。

このとき、ホスト側シリアルインターフェース回路13は、DTライン33を介して送られてくる信号がDC信号であるかAC信号であるかを判断するだけである。したがって、ホスト側シリアルインターフェース回路13は、メモリカード20から一定のレベルの信号が送られているときに、当該信号をビジー信号として検出するだけでなく、メモリカード20が信号の出力を停止しているときもステータス信号がビジー信号になっていると判断する。

そして、ステップS2において、ビジー信号が検出された場合には、ステップS3へ進む。ステップS3において、データ処理回路10はビジー信号が予め規定された所定時間以上続いているか否かを判断する。ビジー信号が予め規定された所定時間以上続いている場合には、タイムアウトが発生したものとしてステップS1へ戻って処理を繰り返す。すなわち、ビジー信号が予め規定された所定時間以上続いている場合、データ処理回路10は、メモリカード20の側で何らかのエラーが発生したものと判断して、もう一度“状態1”に戻って読み出しコマンドの送出をやり直す。

一方、ビジー信号が予め規定された所定時間に達していない場合には、ステップS2へ戻って処理を繰り返す。すなわち、メモリカード20からのステータス信号がビジー信号からレディ信号に変わるまで、データ処理回路10は、ステップS2及びステップS3の処理を繰り返す。

なお、後述するように、メモリカード20は、何らかのエラーが発生したときには信号の出力を止めるようになっている。このとき、DTライン33の信号レベルは、いわゆるプルダウン抵抗として作用する抵抗33aがDTライン33に接続されているので、直前の状態がローのときにはローの状態が維持され、直前の状態がハイのときには徐々にローの状態へと変化する。これらの状態は、いずれの場合も、データ処理装置10にはDC信号として、すなわちビジー信号として検出される。すなわち、メモリカード20の側でエラーが発生した場合には、ビジー信号が継続されることとなる。したがって、メモリカード20の側でエラーが発生した場合には、ステップS2及びステップS3での判断により当該エラーの発生を検出することができる。

換言すれば、このデータ処理装置10及びメモリカード20では、メモリカード20にエラーが発生した場合、エラーの発生を示す特別な信号をメモリカード20からデータ処理装置10に送出することなくデータ処理装置10によってエラーの発生が検出されるようになっている。

一方、メモリカード20の処理にエラーが発生することなく無事に処理が完了して、メモリカード20が外部からの信号入力を受け付ける状態となると、メモリカード20から出力されるステータス信号は、ビジー信号からレディ信号に変わる(図8の時刻t53)。ここで、レディ信号は、上述したように、所定の周期にて信号レベルの変化が繰り返されるAC信号である。このレディ信号は、データ処理装置10によって速やか且つ確実に検出されるように同期信号の周波数以下の周波数で信号レベルが変化するような信号としておくことが好ましい。具体的には、例えば、同期信号の1/2の周波数で、信号レベルがハイ、ロー、ハイ、ローと反転を繰り返すような信号とする。

そして、ステップS2において、ビジー信号が検出されなくなったら、すなわちレディ信号が検出されたらステップS4へ進む。ステップS4において、データ処理装置10は、ホスト側コントローラ14の制御によりホスト側シリアルインターフェース回路13から出力されるコントロール信号をハイにして“状態3”にする(図8の時刻t54)。この“状態3”のとき、データ処理装置10は、メモリカード20から読み出された主データを、ホスト側シリアルインターフェース回路13によって受信する。ホスト側シリアルインターフェース回路13によって受信された主データは、ホスト側コントローラ14の制御によりレジスタ12を介してデータ処理部11へ転送される。

メモリカード20から読み出された主データの受信が完了したら、データ処理装置10は、ホスト側コントローラ14の制御によりホスト側シリアルインターフェース回路13から出力されるコントロール信号をローにして“状態0”にする(図8の時刻t55)。

その後、ステップS5において、データ処理装置10は、インタラプト信号が検出されたか否かを判断する。ここで、インタラプト信号は、メモリカード20が何らかの割り込み処理を要求していることを示す信号である。インタラプト信号が検出されたら、ステップS6へ進む(図8の時刻t56)。ステップS6において、データ処理装置10は、検出されたインタラプト信号をデータ処理部11に送り、その後、当該インタラプト信号に応じた割り込み処理を行うためにステップS1へ戻って処理を繰り返す。

一方、ステップS5でインタラプト信号が検出されていない場合には、ステップS7へ進む。ステップS7において、データ処理装置10は、メモリカード20に対して行うべき何らかの処理があるか否か、すなわち、メモリカード20に送出すべきコマンドがあるか否かを判断する。そして、データ処理装置10は、メモリカード20に送出すべきコマンドがない場合はステップS5へ戻って処理を繰り返し、メモリカード20に送出すべきコマンドがある場合はステップS1へ戻ってコマンドの送出から処理を繰り返す。すなわち、インタラプト信号が発生する前にメモリカード20に対する何らかの処理の要求、例えばメモリカード20の内部のステータスを検出する処理の要求等があったらステップS1へ戻って、当該処理に対応したコマンドの送出を行う。

次に、図8及び図10を参照しながら、メモリカード20の側の処理について説明する。

データ処理装置10によって主データが読み出されるとき、メモリカード20は、まず、ステップS11において、ホスト側シリアルインターフェース回路13から出力されるコントロール信号がハイであり、且つ、現在の状態が“状態1”であるとメモリカード20が認識しているときにホスト側シリアルインターフェース回路13からDTライン33を介して送られてきたデータをコマンドとして受け取る(図8の時刻t51)。なお、データ処理装置10からのデータの送出が完了すると、コントロール信号はローからハイに切り換わる。

次に、ステップS12において、ステップS11におけるコマンドの受信時にエラーが生じたか否かを判断する。このとき、エラーが生じるのは、例えば、メモリカード20の側は“状態1”であると認識していたが、データ処理装置10の側は“状態3”であると認識しており、送られてきたデータがコマンドではなかった場合である。

コマンドの受信時にエラーが生じた場合にはステップS13に進み、メモリカード20からの信号出力を停止した上で、ステップS11へ戻ってデータ処理装置10からのコマンドの再入力の待ち状態となる。すなわち、カード側シリアルインターフェース回路23は、ホスト側シリアルインターフェース回路13からのコマンドの受信時にエラーが生じたときには信号の出力を停止して新たなコマンドの入力待ち状態となる。なお、メモリカード20からの信号出力が停止しているとき、データ処理装置10の側はビジー信号を検出している状態となる。

一方、コマンドの受信時にエラーが生じていない場合には、“状態2”に移行する(図8の時刻t52)。そして、ステップS14へ進んで、メモリカード20は、ステップS11で受信したコマンドに応じた処理を行うとともに、データ処理装置10への主データの送出の準備が完了したか否かを判別する。準備が完了していなければステップS15へ進み、準備が完了したらステップS16へ進む。

ステップS15において、カード側シリアルインターフェース回路23は、信号レベルが一定のビジー信号を出力し、その後、ステップS14に戻ってデータ処理装置10への主データの送出の準備が完了したか否かの判別を繰り返す。すなわち、カード側シリアルインターフェース回路23は、データ処理装置10への主データの送出の準備が完了するまで信号レベルが一定のビジー信号の出力を継続する。

データ処理装置10への主データの送出の準備が完了したらステップS16へ進み、ステップS16において、カード側シリアルインターフェース回路23は、ホスト側シリアルインターフェース回路13へレディ信号を送出する(図8の時刻t53)。ここで、レディ信号は、上述したように、例えば、同期信号の1/2の周波数の信号である。

レディ信号がデータ処理装置10によって検出されると、コントロール信号がローからハイに切り換わる。すなわち、“状態2”から“状態3”に切り換わる(図8の時刻t54)。“状態3”となったら、ステップS17において、カード側コントローラ24は、ステップS11で受信したコマンドによって読み出すように指示された主データを、カード側シリアルインターフェース回路23を介してDTライン33によりホスト側シリアルインターフェース回路13へCLKラインによって伝送されている同期信号に同期させて送出する。この主データ全てがデータ処理装置10によって受信されると、コントロール信号はハイからローに切り換わる。すなわち、“状態3”から“状態0”に切り換わる(図8の時刻t55)。

次に、ステップS18において、カード側コントローラ24は、何らかの割り込み処理の要求があるか否かを判断する。割り込み処理の要求がない場合はステップS19へ進み、割り込み処理の要求がある場合はステップS20へ進む。

ステップS19において、カード側コントローラ24は、ホスト側シリアルインターフェース回路13から供給されるコントロール信号がローからハイに切り換わったか否か、すなわち、“状態0”から“状態1”に切り換わったか否かを判断する。そして、“状態1”に切り換わったならば、ステップS11へ戻って、コマンドの受信から処理を繰り返す。一方、“状態0”のままならば、ステップS18へ戻って処理を繰り返す。すなわち、このメモリカード20は、割り込み処理が発生するか、あるいは状態が“状態0”から“状態1”に切り換わるまで、ステップS18及びステップS19の処理を繰り返す。

一方、ステップS18において、割り込み処理の要求があると判断されたら、ステップS20及びステップ21に示すように、カード側シリアルインターフェース回路は、状態が“状態0”から“状態1”に切り換わるまでインタラプト信号を出力する。このとき、データ処理装置20によってインタラプト信号が検出されると、ホスト側シリアルインターフェース回路13から供給されるコントロール信号がローからハイに切り換わり、状態が“状態0”から“状態1”に切り換わることとなる。そして、状態が“状態0”から“状態1”に切り換わったらステップS11へ戻り、メモリカード20は、コマンドの受信から処理を繰り返す。なお、このときは、ステップS20で送出したインタラプト信号に応じた処理を行うコマンドを受信することとなる。

以上のように、メモリカード20が実際に処理を行っているときに出力される信号をビジー信号とするだけでなく、メモリカード20からの信号出力がない状態のときもビジー信号として検出するようにすることによりメモリカード20が状態を誤って判断したままデータ伝送の処理が進むようなことがなくなる。したがって、メモリカード20から出力されるデータとデータ処理装置10から出力されるデータとがぶつかってしまったり、メモリカード20とデータ処理装置10との間で誤ったデータのやり取りがなされたり、メモリカード20とデータ処理装置10とが互いに待ち状態となってデータの伝送がされなくなってしまったりするようなことがなくなる。

10 データ処理装置、 11 データ処理部、 12 レジスタ、 13ホスト側シリアルインターフェース回路、 14 ホスト側コントローラ、 20 メモリカード、 21 メモリ、 22 レジスタ、 23 カード側シリアルインターフェース回路、 24 カード側コントローラ、 31 CLKライン、 32 コントロールライン、 33 DTライン

Claims (16)

- 外部装置とデータの伝送を行なうデータ処理装置とを含むデータ処理システムにおいて、

データ処理装置は、外部装置へのコマンドを生成し、外部装置からデータを受けるコントローラおよび上記外部装置と通信するための複数の端子を有し、

外部装置は、略カードの形状、上記データ処理装置からのコマンドを受けるコントローラ、および上記データ処理装置と通信するための複数の端子を有し、

上記外部装置の上記端子は、上記外部装置と上記データ処理装置が主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有することを特徴とするデータ処理システム。 - 上記リザーブ端子は、データ線として使用することが可能であり、上記データ端子と合わせてパラレルに使用されることを特徴とする請求項1記載のデータ処理システム。

- 上記リザーブ端子は3本設けられており、上記データ端子と合わせて4本のデータ線として使用することが可能なことを特徴とする請求項1記載のデータ処理システム。

- 上記複数の端子は、さらにクロック端子とコントロール端子とを有し、上記リザーブ端子は、クロック端子、コントロール端子、およびデータ端子として使用することが可能であり、先のクロック端子、コントロール端子およびデータ端子と合わせて、クロック端子、コントロール端子およびデータ端子の組を2つ設けることを特徴とする請求項1記載のデータ処理システム。

- 外部装置とデータ伝送を行うデータ処理装置において、

上記外部装置へのコマンドを生成し、上記外部装置からデータを受けるコントローラおよび上記外部装置と通信するための複数の端子を有し、

上記複数の端子は、上記外部装置と主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有することを特徴とするデータ処理装置。 - 上記リザーブ端子は、データ線として使用することが可能であり、上記データ端子と合わせてパラレルに使用されることを特徴とする請求項5記載のデータ処理装置。

- 上記リザーブ端子は3本設けられており、上記データ端子と合わせて4本のデータ線として使用することが可能なことを特徴とする請求項5記載のデータ処理装置。

- 上記複数の端子は、さらにクロック端子とコントロール端子とを有し、上記リザーブ端子は、クロック端子、コントロール端子、およびデータ端子として使用することが可能であり、先のクロック端子、コントロール端子およびデータ端子と合わせて、クロック端子、コントロール端子およびデータ端子の組を2つ設けることを特徴とする請求項5記載のデータ処理装置。

- データ処理装置とデータ伝送を行う外部装置において、

略カードの形状、上記データ処理装置からのコマンドを受けるコントローラ、および上記データ処理装置と通信するための複数の端子を有し、

上記端子は、上記外部装置と上記データ処理装置が主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有することを特徴とする外部装置。 - 上記リザーブ端子は、データ線として使用することが可能であり、上記データ端子と合わせてパラレルに使用されることを特徴とする請求項9記載の外部装置。

- 上記リザーブ端子は3本設けられており、上記データ端子と合わせて4本のデータ線として使用することが可能なことを特徴とする請求項9記載の外部装置。

- 上記複数の端子は、さらにクロック端子とコントロール端子とを有し、上記リザーブ端子は、クロック端子、コントロール端子、およびデータ端子として使用することが可能であり、先のクロック端子、コントロール端子およびデータ端子と合わせて、クロック端子、コントロール端子およびデータ端子の組を2つ設けることを特徴とする請求項9記載の外部装置。

- 外部装置とデータ処理装置との間でデータ伝送を行うデータ伝送方法において、

データ処理装置は、外部装置へのコマンドを生成し、外部装置からデータを受けるコントローラおよび上記外部装置と通信するための複数の端子を有し、

外部装置は、略カードの形状、上記データ処理装置からのコマンドを受けるコントローラ、および上記データ処理装置と通信するための複数の端子を有し、

上記外部装置の上記端子は、上記外部装置と上記データ処理装置が主データをシリアル通信するためのデータ端子と、予備の端子であるリザーブ端子とを有し、

上記データ処理装置で生成されたコマンドに応じて上記外部装置と上記データ処理装置との間で主データのシリアル通信を行うことを特徴とするデータ伝送方法。 - 上記リザーブ端子は、データ線として使用することが可能であり、上記データ端子と合わせてパラレルに使用されることを特徴とする請求項13記載のデータ伝送方法。

- 上記リザーブ端子は3本設けられており、上記データ端子と合わせて4本のデータ線として使用することが可能なことを特徴とする請求項13記載のデータ伝送方法。

- 上記複数の端子は、さらにクロック端子とコントロール端子とを有し、上記リザーブ端子は、クロック端子、コントロール端子、およびデータ端子として使用することが可能であり、先のクロック端子、コントロール端子およびデータ端子と合わせて、クロック端子、コントロール端子およびデータ端子の組を2つ設けることを特徴とする請求項13記載のデータ伝送方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003294636A JP2004046891A (ja) | 1997-06-04 | 2003-08-18 | データ処理システム、データ処理装置、外部装置及びデータ伝送方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP14691697 | 1997-06-04 | ||

| JP2003294636A JP2004046891A (ja) | 1997-06-04 | 2003-08-18 | データ処理システム、データ処理装置、外部装置及びデータ伝送方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000150585A Division JP2000357062A (ja) | 1997-06-04 | 2000-05-22 | データ処理装置、外部記憶装置、データ処理システム及びデータ伝送方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2004046891A true JP2004046891A (ja) | 2004-02-12 |

Family

ID=31719024

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003294636A Abandoned JP2004046891A (ja) | 1997-06-04 | 2003-08-18 | データ処理システム、データ処理装置、外部装置及びデータ伝送方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2004046891A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8171213B2 (en) | 2007-04-20 | 2012-05-01 | Sony Corporation | Information processing apparatus and method, and program |

| US8468273B2 (en) | 2006-06-30 | 2013-06-18 | Sony Corporation | Information storage apparatus, information transfer method, information transfer system, program, and storage medium |

| JP2015133732A (ja) * | 2015-02-25 | 2015-07-23 | ソニー エスパナ,エス.エー. | 受信装置および信号受信方法 |

| US9462331B2 (en) | 2007-11-13 | 2016-10-04 | Sony Corporation | Display apparatus, video signal transmission method for display apparatus, transmitting apparatus, and transmission method of video signal |

-

2003

- 2003-08-18 JP JP2003294636A patent/JP2004046891A/ja not_active Abandoned

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8468273B2 (en) | 2006-06-30 | 2013-06-18 | Sony Corporation | Information storage apparatus, information transfer method, information transfer system, program, and storage medium |

| US8171213B2 (en) | 2007-04-20 | 2012-05-01 | Sony Corporation | Information processing apparatus and method, and program |

| US9462331B2 (en) | 2007-11-13 | 2016-10-04 | Sony Corporation | Display apparatus, video signal transmission method for display apparatus, transmitting apparatus, and transmission method of video signal |

| US9668017B2 (en) | 2007-11-13 | 2017-05-30 | Sony Corporation | Display apparatus, video signal transmission method for display apparatus, transmitting apparatus, and transmission method of video signal |

| JP2015133732A (ja) * | 2015-02-25 | 2015-07-23 | ソニー エスパナ,エス.エー. | 受信装置および信号受信方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3134819B2 (ja) | データ処理装置 | |

| KR102910362B1 (ko) | 스토리지 장치 및 스토리지 장치의 동작 방법 | |

| US6681269B2 (en) | Data processing apparatus, external storage apparatus, data processing system and data transmitting method | |

| US7725621B2 (en) | Semiconductor device and data transfer method | |

| KR100440972B1 (ko) | 카드 삽입 인식에 의한 데이터 전송 상태 자동 설정 장치및 방법 | |

| KR20080078977A (ko) | Mmc 또는 sd 프로토콜을 사용하는 다수의 메모리장치들을 인터페이스하는 방법 및 시스템 | |

| US20040225836A1 (en) | Portable USB storage device capable of being set to device mode or host mode | |

| JPWO2002069127A1 (ja) | 記憶媒体制御方法、記憶媒体制御装置、および記憶媒体アダプタ | |

| US5247640A (en) | Dual access control system including plural magnetic disk control units and contention control circuitry | |

| JP2004046891A (ja) | データ処理システム、データ処理装置、外部装置及びデータ伝送方法 | |

| JP3241034B2 (ja) | 外部記憶装置 | |

| JP3395762B2 (ja) | データ処理システム及びデータ伝送方法 | |

| JP5010065B2 (ja) | マイクロコンピュータ | |

| JP4431768B2 (ja) | 携帯型電子装置、読み出し方法及び書き込み方法 | |

| JP2000357062A (ja) | データ処理装置、外部記憶装置、データ処理システム及びデータ伝送方法 | |

| JP2009123141A (ja) | I/oデバイス、ホストコントローラおよびコンピュータシステム | |

| JP3134256B2 (ja) | プリンタの双方向通信方法 | |

| JPH10198524A (ja) | ハードディスク制御装置 | |

| JP2006024143A (ja) | 情報処理装置、外部装置、ホスト装置、及び通信方法 | |

| JP3300016B2 (ja) | 通信インターフェイス及び記録装置及び通信制御方法 | |

| JP3947223B2 (ja) | 送信パケットを重ねることによりインタフェース上の待ち時間を短縮するための方法および装置 | |

| KR100531729B1 (ko) | 피씨 병렬포트를 이용한 주변기기와의 인터페이스 장치 및그 방법 | |

| JPH0991100A (ja) | データ伝送制御装置 | |

| JPS5916067A (ja) | デ−タチエツク方式 | |

| JPH10334044A (ja) | シリアルインタフェース方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060207 |

|

| A762 | Written abandonment of application |

Free format text: JAPANESE INTERMEDIATE CODE: A762 Effective date: 20060410 |