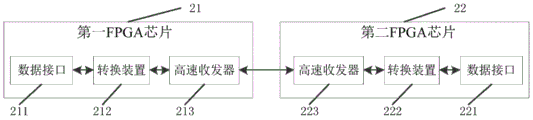

CN107786471B - 多fpga芯片间数据处理方法及转换装置 - Google Patents

多fpga芯片间数据处理方法及转换装置 Download PDFInfo

- Publication number

- CN107786471B CN107786471B CN201710994136.2A CN201710994136A CN107786471B CN 107786471 B CN107786471 B CN 107786471B CN 201710994136 A CN201710994136 A CN 201710994136A CN 107786471 B CN107786471 B CN 107786471B

- Authority

- CN

- China

- Prior art keywords

- data

- signal data

- specific type

- signal

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/10—Packet switching elements characterised by the switching fabric construction

- H04L49/109—Integrated on microchip, e.g. switch-on-chip

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0061—Error detection codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

- H04L49/9057—Arrangements for supporting packet reassembly or resequencing

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Communication Control (AREA)

Abstract

Description

Claims (32)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201710994136.2A CN107786471B (zh) | 2017-10-23 | 2017-10-23 | 多fpga芯片间数据处理方法及转换装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201710994136.2A CN107786471B (zh) | 2017-10-23 | 2017-10-23 | 多fpga芯片间数据处理方法及转换装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN107786471A CN107786471A (zh) | 2018-03-09 |

| CN107786471B true CN107786471B (zh) | 2021-03-16 |

Family

ID=61434990

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201710994136.2A Active CN107786471B (zh) | 2017-10-23 | 2017-10-23 | 多fpga芯片间数据处理方法及转换装置 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN107786471B (zh) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN109446143B (zh) * | 2018-10-16 | 2021-05-25 | 武汉精立电子技术有限公司 | 一种基于fpga的数据串行传输控制系统及方法 |

| CN111949590B (zh) * | 2020-08-11 | 2022-05-06 | 国微集团(深圳)有限公司 | 一种可跨fpga平台的高速通讯方法 |

| CN111740847B (zh) * | 2020-08-24 | 2020-12-11 | 常州楠菲微电子有限公司 | 一种基于fpga的高速网络数据传输系统及方法 |

| CN113595932B (zh) * | 2021-08-06 | 2024-05-14 | 上海金仕达软件科技股份有限公司 | 数据乱序报文的处理方法及专用集成电路 |

| CN113923173B (zh) * | 2021-10-22 | 2023-12-15 | 深圳市风云实业有限公司 | 网络交换设备数据面快速启动恢复方法 |

| CN116418752B (zh) * | 2021-12-30 | 2025-09-30 | 苏州盛科通信股份有限公司 | 报文的处理方法、装置、存储介质和电子装置 |

| CN118363919B (zh) * | 2024-04-19 | 2025-05-06 | 中国人民解放军国防科技大学 | 用于多fpga平台的全透明波形编解码和恢复重建方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11284503A (ja) * | 1998-03-30 | 1999-10-15 | Rohm Co Ltd | プログラマブルゲートアレイ |

| CN101610253A (zh) * | 2009-07-22 | 2009-12-23 | 天津市电力公司 | 一种可以实现保护设备数据分类传输的处理方法 |

| CN101977162A (zh) * | 2010-12-03 | 2011-02-16 | 电子科技大学 | 一种高速网络的负载均衡方法 |

| CN104660462A (zh) * | 2015-01-15 | 2015-05-27 | 北京奥普维尔科技有限公司 | 一种万兆以太网测试设备的组包系统及方法 |

| CN105955920A (zh) * | 2016-04-25 | 2016-09-21 | 浪潮电子信息产业股份有限公司 | 一种片上网络中基于Credit的流控机制的设计方法 |

| CN106502932A (zh) * | 2016-09-20 | 2017-03-15 | 中国科学院自动化研究所 | 基于分层结构的片间互联接口及其写操作和读操作的方法 |

| CN106844256A (zh) * | 2017-02-22 | 2017-06-13 | 天津大学 | 一种基于多fpga的有源配电网实时仿真器内部接口设计方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1224216C (zh) * | 2003-06-30 | 2005-10-19 | 港湾网络有限公司 | 宽带通信逻辑仿真平台设计的验证方法 |

| CN101286867B (zh) * | 2007-05-29 | 2011-10-05 | 深圳市同洲电子股份有限公司 | 一种网络设备的软件升级方法与系统 |

| CN101969359B (zh) * | 2010-09-29 | 2012-11-14 | 航天东方红卫星有限公司 | 小卫星电子载荷任务上注及处理方法 |

-

2017

- 2017-10-23 CN CN201710994136.2A patent/CN107786471B/zh active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11284503A (ja) * | 1998-03-30 | 1999-10-15 | Rohm Co Ltd | プログラマブルゲートアレイ |

| CN101610253A (zh) * | 2009-07-22 | 2009-12-23 | 天津市电力公司 | 一种可以实现保护设备数据分类传输的处理方法 |

| CN101977162A (zh) * | 2010-12-03 | 2011-02-16 | 电子科技大学 | 一种高速网络的负载均衡方法 |

| CN104660462A (zh) * | 2015-01-15 | 2015-05-27 | 北京奥普维尔科技有限公司 | 一种万兆以太网测试设备的组包系统及方法 |

| CN105955920A (zh) * | 2016-04-25 | 2016-09-21 | 浪潮电子信息产业股份有限公司 | 一种片上网络中基于Credit的流控机制的设计方法 |

| CN106502932A (zh) * | 2016-09-20 | 2017-03-15 | 中国科学院自动化研究所 | 基于分层结构的片间互联接口及其写操作和读操作的方法 |

| CN106844256A (zh) * | 2017-02-22 | 2017-06-13 | 天津大学 | 一种基于多fpga的有源配电网实时仿真器内部接口设计方法 |

Non-Patent Citations (2)

| Title |

|---|

| 《多FPGA验证平台引脚限制的解决方案》;胡文彬,吴剑旗,洪一;《合肥工业大学学报(自然科学版)》;20101031;第33卷(第10期);全部 * |

| Qingshan Tang;Habib Mehrez;Matthieu Tuna.《Multi-FPGA prototyping board issue: the FPGA I/O bottleneck》.《2014 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS XIV)》.2014,全部. * |

Also Published As

| Publication number | Publication date |

|---|---|

| CN107786471A (zh) | 2018-03-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107786471B (zh) | 多fpga芯片间数据处理方法及转换装置 | |

| EP3827356B1 (en) | Unified address space for multiple hardware accelerators using dedicated low latency links | |

| JP5348263B2 (ja) | データ伝送装置、データ伝送システムおよびデータ伝送方法 | |

| US5553302A (en) | Serial I/O channel having independent and asynchronous facilities with sequence recognition, frame recognition, and frame receiving mechanism for receiving control and user defined data | |

| KR102882297B1 (ko) | 라인 코딩 방법 및 장치 | |

| US8953463B2 (en) | Channel interleaved multiplexed databus | |

| CN109426636B (zh) | 一种fpga片间高位宽数据传输的方法及装置 | |

| CN103780322B (zh) | 低成本高可靠性的高速网络通讯芯片测试方法与电路 | |

| WO2020026194A1 (en) | Serial interface for semiconductor package | |

| US11101923B2 (en) | Receiver circuitry for physical coding sublayer | |

| US20190179791A1 (en) | High speed memory interface | |

| CN106603420A (zh) | 一种具有实时和容错特性的片上网络路由器 | |

| CN104660462A (zh) | 一种万兆以太网测试设备的组包系统及方法 | |

| US6880111B2 (en) | Bounding data transmission latency based upon a data transmission event and arrangement | |

| JP2013034133A (ja) | 送信装置、送受信システムおよび制御方法 | |

| US9122411B2 (en) | Signal order-preserving method and apparatus | |

| JP3757204B2 (ja) | エラー検出/訂正方式及び該方式を用いた制御装置 | |

| CN102394720A (zh) | 一种信息安全校验处理器 | |

| EP0353249A4 (en) | Parallel networking architecture | |

| US11782636B2 (en) | Method for data processing of an interconnection protocol to support multiple lanes, controller, and storage device | |

| CN106209307A (zh) | 多颗fpga片间互联方法与系统 | |

| CN117221036A (zh) | 一种串行总线双链路冗余通信模块、系统和方法 | |

| JP2016042218A (ja) | エラー検出装置及びエラー検出方法 | |

| Sobhani et al. | Inter-node Communication in Multi-FPGA-based Computational Neuroscience Simulators: PHY-to-Link | |

| US20240311219A1 (en) | Dynamic random access memory (dram) device with write error protection |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| CB03 | Change of inventor or designer information |

Inventor after: Wang Kefei Inventor after: Chen Li Inventor after: Wang Zhiqi Inventor after: Zhu Feng Inventor after: Zhan Jinchuan Inventor before: Wang Kefei Inventor before: Qi Xingyun Inventor before: Chen Li Inventor before: Wang Zhiqi Inventor before: Zhu Feng Inventor before: Zhan Jinchuan |

|

| CB03 | Change of inventor or designer information | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20210526 Address after: 518057 Room 201, 2 / F, Yinhe building, 25 Gaoxin North 6 road, North Science Park, Nanshan District, Shenzhen City, Guangdong Province Patentee after: SHENZHEN NETFORWARD MICROELECTRONIC Co.,Ltd. Address before: 5b2, 3B2, 4b1, Tianji building, chegongmiao Tian'an Industrial Park, Futian District, Shenzhen, Guangdong 518040 Patentee before: SHENZHEN FORWARD INDUSTRIAL Co.,Ltd. |

|

| TR01 | Transfer of patent right | ||

| CP03 | Change of name, title or address |

Address after: Jiangsu Province Nanjing City Nanshan District Xili Street Songpingshan Community Gaoxin North 6th Road No. 25 Fengyun Building 2nd Floor Patentee after: Shenzhen Nanfei Microelectronics Co., Ltd. Country or region after: China Address before: 518057 Room 201, 2 / F, Yinhe building, 25 Gaoxin North 6 road, North Science Park, Nanshan District, Shenzhen City, Guangdong Province Patentee before: SHENZHEN NETFORWARD MICROELECTRONIC CO.,LTD. Country or region before: China |

|

| CP03 | Change of name, title or address | ||

| CP03 | Change of name, title or address |

Address after: 518057, No. 25, Gaoxin Bei Liu Dao, Xili Street, Nanshan District, Shenzhen City, Guangdong Province, 2nd floor of Fengyun Building, Songpingshan Community Patentee after: Shenzhen Nanfei Microelectronics Co.,Ltd. Country or region after: China Address before: 2nd Floor, Fengyun Building, No. 25 Gaoxin North 6th Road, Songpingshan Community, Xili Street, Nanshan District, Nanjing City, Jiangsu Province Patentee before: Shenzhen Nanfei Microelectronics Co.,Ltd. Country or region before: China |

|

| CP03 | Change of name, title or address |