CN102946293A - 一种基于ds编码的并行接收方法及其装置 - Google Patents

一种基于ds编码的并行接收方法及其装置 Download PDFInfo

- Publication number

- CN102946293A CN102946293A CN2012103629834A CN201210362983A CN102946293A CN 102946293 A CN102946293 A CN 102946293A CN 2012103629834 A CN2012103629834 A CN 2012103629834A CN 201210362983 A CN201210362983 A CN 201210362983A CN 102946293 A CN102946293 A CN 102946293A

- Authority

- CN

- China

- Prior art keywords

- data

- signal

- clock

- state

- parallel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Synchronisation In Digital Transmission Systems (AREA)

Abstract

本发明提供了一种基于DS编码的并行接收方法及其装置,数据信号经过时钟恢复电路恢复出时钟信号,将数据信号和时钟信号同时送入串并数据转换器,输出N位的数据信号和一位数据有效指示信号,经过接收装置系统工作时钟的三级寄存器同步后完成异步时钟域内数据正确交互,将同步后的数据信号和数据有效指示信号同时送入并行数据接收器进行数据解码接收。本发明在不增加系统锁相环资源的情况下用简单逻辑电路实现了用低速系统时钟接收高速发送数据的功能,减小了设计的复杂程度,同时会降低工艺的复杂度,提高成品率,采用低速时钟实现了接收较高速率的数据,提高了通讯速率。

Description

技术领域

本发明涉及一种基于DS编码的并行接收方法,实现了一种应用在Spacewire节点控制器中的4位串并数据转换器和4位并行数据接收器。

背景技术

随着航天技术的发展以及航天应用的进一步深入,对航天器的在轨数据处理及交互能力提出了越来越高的要求。Spacewire是欧空局(ESA)为了解决上述需求而推出的一种总线标准,具有高性能、低功耗、高可靠等特点,目前己经成功地应用在多个空间任务中。Spacewire采用Data-Strobe(DS)编码技术,发送时数据由Data信号直接传输,每相邻两位Data信号相同时Strobe信号发生变化。接收时Data信号与Strobe信号相异或得到的时钟信号作为接收数据信号的时钟。采用DS编码之后,解码器的两种主流解决方案:一种是采用符合采样定理的传统的采样方法即高频时钟信号采样低频数据信号,但需要一个高频的时钟,一般是通过锁相环来提供,增加时钟锁相环资源会增加系统的资源增大设计复杂度;另外一种是通过时钟恢复技术。目前普遍采用的是时钟恢复技术。采样这种技术必然面临两个问题,一个是数据在异步时钟域中交互的可靠性问题,另一个是将数据变为并行数据后的解码问题。

发明内容

为了克服时钟恢复技术在异步时钟域中交互的可靠性问题的不足,本发明提供一种基于DS编码的并行接收方法,在系统不增加时钟锁相环资源的情况下,用低频的系统时钟来接收高频的发送数据。

本发明解决其技术问题所采用的技术方案包括以下步骤:

1)将一个Data-Strobe(DS)码流中的Data信号和Strobe信号相异或生成时钟信号,该时钟信号作为采样数据信号的时钟;

2)用DS异或生成的时钟信号的上升沿对数据信号进行采样,每采样N位为一组数据;用时钟信号的下降沿对数据信号进行采样,每采样N位为一组数据;用一个模N的计数器做采样标识;对于数据分组是根据数据指令编码的格式来确定N为几,对于Spacewire节点控制器的解码器来说,最小的控制字符为4,所以本发明中的串并转换器是4位的;

3)将上升沿采样和下降沿采样的数据按照先后顺序位与位交替存储,存储后以2N位为一组数据;通过上述的模N计数器将这2N位的数据分为每N位一组;

4)将交替存储后分解的N位数据通过接收装置的系统工作时钟和三级寄存器进行三级同步,消除异步时钟域中数据交换的亚稳态;

5)在所述的计数器非零时生成一个数据有效指示信号;

6)将该数据有效指示信号通过接收装置系统工作时钟经过三级寄存器进行三级同步;

7)将同步后的数据信号和数据有效指示信号进行并行数据解码接收,通过一个状态机实现。

状态机的第一个状态是Detect_CtrlChar,也就是复位后初始状态,如果接收到的4位数据是控制字符(ESC、FCT、EOP或EEP)则,仍然保持在该状态,其他情况跳转到下一状态CargoBit4;

状态机的第二个状态是CargoBit4:表示节点已经接收到4个字符位;该状态下①若在前一状态CargoBit10时检测到数据字符,则不做任何操作,直接转移至CargoBit8,②若停留在该状态期间检测到数据或时间码,也不做任何操作,直接转移至CargoBit8,③若检测到控制字符,则停留在该状态;可能接收到控制字符,不可能接收到数据和时间码;可以检测所有字符;

CargoBit8:表示节点已经收到8个字符位;该状态下,收到的8个字符位是数据字符(或时间码的数据部分)的前8位,从而必然接收到数据或时间码,不可能接收到控制字符;检测到数据或控制字符(但不知是什么控制字符,因为只检测到控制位'1',下同),不可能检测到时间码;无条件转移到CargoBit2;

CargoBit2:表示节点收到2个字符位;该状态下①若在前一状态CargoBit8时检测到数据字符,则不做任何操作,直接转移至CargoBit6,②若检测到控制字符(但不知是什么控制字符),则停留在该状态,③若检测到数据或时间码,则转移至CargoBit6;若检测到控制字符(但不知是什么控制字符),则对具体是什么控制字符不做检测,直接接收;不可能接收到数据或时间码;

CargoBit6:表示节点收到6个字符位;该状态下,必是节点已经检测到数据或时间码,收到的6个字符位是数据字符(或时间码的数据部分)的前6位;不做任何操作,无条件转移至CargoBit10;

CargoBit10:表示已经接收到10个字符位;该状态下,必接收到数据或时间码,不可能接收到控制字符;检测到数据或控制字符,不可能检测到时间码、NULL字符(此状态ESC_Observed必为′0′);无条件转移到CargoBit4。

所述的N为任意偶数。

本发明还提供一种实现上述方法的装置,包括时钟恢复电路、串并数据转换单元和并行数据接收器,数据信号经过时钟恢复电路,恢复出时钟信号,将数据信号和时钟信号同时送入串并数据转换器。该串并数据转换器的输入信号有Data信号、Strbdn信号,需要转换的串行数据是1位的Data信号。该转换器的输出信号是N位的数据信号,和一位数据有效指示信号。输出的N位数据和一位数据有效指示信号,经过接收装置系统工作时钟的三级寄存器同步后完成异步时钟域内数据正确交互,将同步后的数据信号和数据有效指示信号同时送入并行数据接收器进行数据解码接收。

本发明的有益效果是:本发明在不增加系统锁相环资源的情况下用简单逻辑电路实现了用低速系统时钟接收高速发送数据的功能。由于未增加时钟锁相环资源,也就是减少了系统资源开销,减小了设计的复杂程度,同时会降低工艺的复杂度,提高成品率。采用低速时钟实现了接收较高速率的数据,提高了通讯速率。

附图说明

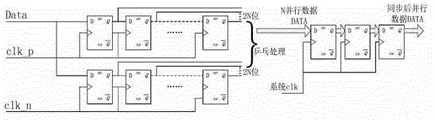

图1为本发明基于DS编码的并行接收技术的构架框图;

图2为本发明中的DS时钟恢复单元实施电路原理简图;

图3为DS恢复时钟采样串行数据到并行数据的实现原理图;

图4为N位串并转换数据拼接原理图;

图5为DS恢复正沿时钟采样数据时序图;

图6为根据本发明实施的一个N为4的4位串并转换的时序图;

图7为本发明在Spacewire节点控制器中实现4位并行数据接收器的状态图。

具体实施方式

本发明提供一种基于DS编码的并行接收方法,该方法就是首先将一个DS码流所传送的数据信号通过DS信号恢复出的时钟信号进行采样,采样后的串行数据拼为一个N位的并行数据;然后将该并行数据经过三级同步处理,可靠地传送到系统时钟域中做数据接收的解码;最后就是为了保证数据接收的及时性,直接对该并行数据进行解码接收。

本发明实现的基于DS编码的并行接收装置包括:(1)一个将串行数据码流转换为一个N位字符流的串并转换电路,该电路不是简单的将串行数据通过移位寄存器变成一个并行数据,因为接收到的数据不是一个简单的顺序数据流;(2)一个N位的并行数据接收器,在本发明依据SpaceWire协议的字符特点设计一个4位的并行数据接收器。当应用在其他系统中,N可以是任意偶数,可以扩展为2、4、8等。

1.串并数据转换单元

在数据信号到达该该单元前先经过如图2所示的时钟恢复电路,将Data信号和DS时钟同时送入该串并数据装换器。本发明的关键技术就在串并数据转换单元,简单的通过DS时钟采样到的数据直接送到接收器中进行解码接收存在异步时钟域中数据交互问题,很难保证数据完备,解码正确。本电路可以实现N位数据串并转换,经过三级同步完成异步时钟域内数据正确交互。

实现步骤:

1)数据信号用DS时钟的上升沿进行采样,用一个模N的计数器做采样标识,N位为一组;

2)数据信号用DS时钟的下降沿进行采样,用一个模N的计数器做采样标识,N位为一组;

3)上升沿采样和下降沿采样的数据交替存入一个N位寄存器中;

4)将该N位数据通过系统时钟进行三级同步;

5)上述模N的计数器在非零时生成一个数据有效指示信号;

6)将该数据有效信号通过系统时钟进行三级同步;

7)将同步后的数据信号和数据有效指示信号同时送入下一个并行接收单元进行数据解码接收。

2.并行接收器单元

并行接收器单元,也就是并行数据处理器单元,确定N的值是接收器的设计的关键点。N的确定要根据传输字符的特点来定。如果N路并行信号输入是分析器能够允许的最高位宽,则采用fMHz的时钟可以解码 或者更高速率的数据,但最高可以接收的数据速率不超过NfMbps。

本发明为Spacewire节点控制器设计的4路并行接收器,Spacewire协议是根据 1355-1995协议来制定的,并在其基础上提供了Time-codes来支持在网络层传播系统时间。SpaceWire协议中有三种类型的字符,数据字符、控制字符和连接字符。

分析SpaceWire字符层协议字符层特性,其中最小的字符是4位,亦是解码的最小位宽为4位。所以4路并行信号输入是Spacewire接收解码器能够允许的最高位宽。4路并行输入接收器分析器对由DS信号恢复出的数据进行分析,每个时钟周期可以处理4路并行信号。

下面结合附图和实施例对本发明进一步说明。

如图2所示,来自PAD的信号Data和Strobd经过异或生成DS时钟clkds,clk_p的上升沿和clk_n的上升沿分别是clkds的上升沿和下降沿;生成的clk_p和clk_n两个输入,它们均是与系统时钟异步的时钟信号。如果只用异或产生的时钟上升沿对Data信号进行采样的话,只能得到一半Data信号,所以异或产生的时钟信号要用到上升沿和下降沿交替对Data信号进行采样,可以保证数据的完整性。时钟信号经过逻辑门后对Data信号进行采样,由门延时保证时钟可以正确采样到数据。

如图3所示输入的数据信号通过恢复出的正时钟clk_p和负时钟clk_n采样到数据存入两个2N位的移位寄存器中。当接收到2N位后可通过系统时钟采样移位寄存器交叉拼接数据存入2N位寄存器中,经过3级的系统钟同步采样后,用2拍输出N位并行数据。其中用到两个2N位的寄存器,做乒乓处理交替送出数据。也就是由于用fMHz的时钟无法正确解码fMbps的DS信号,用DS信号恢复出来的时钟clkds,将码速率为fMbps的DS编码信号分为两路码速率为f/2Mbps的信号。

如图4所示,图中只画出了clkds的上升沿clkp对D信号的采样。信号PEn是对clkds的二分频,作为信号DataP的使能信号,在PEn的上升沿和下降沿都有一个有效数据位。同步时钟对PEn进行采样,检测到PEn的沿时对DataP进行采样,得到有效数据位,得到原DS信号携带的一半信存入clk_p的移位寄存器中。DS信号携带的另一半信息同样的方法存入另一个移位寄存器中。其中两个移位寄存器数据交替拼接存入到寄存器。

图6是一个N为4位的串并转换时序图,其中应用了一个模4的计数器来控制采样和生成输出数据的使能信号。

并行解码分析器主要结构为一个状态机,如图7所示,Detect_CtrlChar表示节点在该状态下检测到控制字符(ESC、FCT、EOP或EEP)。CargoBit10:表示已经接收 到10个字符位;该状态下,必接收到数据或时间码,不可能接收到控制字符;检测到数据或控制字符,不可能检测到时间码、NULL字符(此状态ESC_Observed必为′0′);无条件转移到CargoBit4;CargoBit4:表示节点已经接收到4个字符位;该状态下①若在前一状态CargoBit10时检测到数据字符,则不做任何操作,直接转移至CargoBit8,②若停留在该状态期间检测到数据或时间码,也不做任何操作,直接转移至CargoBit8,③若检测到控制字符,则停留在该状态;可能接收到控制字符,不可能接收到数据和时间码;可以检测所有字符;CargoBit8:表示节点已经收到8个字符位;该状态下,收到的8个字符位是数据字符(或时间码的数据部分)的前8位,从而必接收到数据或时间码,不可能接收到控制字符;检测到数据或控制字符(但不知是什么控制字符,因为只检测到控制位′1′,下同),不可能检测到时间码;无条件转移到CargoBit2;CargoBit2:表示节点收到2个字符位;该状态下①若在前一状态CargoBit8时检测到数据字符,则不做任何操作,直接转移至CargoBit6,②若检测到控制字符(但不知是什么控制字符),则停留在该状态,③若检测到数据或时间码,则转移至CargoBit6;若检测到控制字符(但不知是什么控制字符),则对具体是什么控制字符不做检测,直接接收;不可能接收到数据或时间码;CargoBit6:表示节点收到6个字符位;该状态下,必是节点已经检测到数据或时间码,收到的6个字符位是数据字符(或时间码的数据部分)的前6位;不做任何操作,无条件转移至CargoBit10。

Claims (5)

1.一种基于DS编码的并行接收方法,其特征在于包括下述步骤:

1)将一个DS码流中的Data信号和Strobe信号相异或生成时钟信号,该时钟信号作为采样数据信号的时钟;

2)用时钟信号的上升沿对数据信号进行采样,每采样N位为一组数据;用时钟信号的下降沿对数据信号进行采样,每采样N位为一组数据;用一个模N的计数器做采样标识;

3)将上升沿采样和下降沿采样的数据按照先后顺序位与位交替存储,存储后以2N位为一组数据;通过上述的模N计数器将这2N位的数据分为每N位一组;

4)将交替存储后分解的N位数据通过接收装置的系统工作时钟和三级寄存器进行三级同步,消除异步时钟域中数据交换的亚稳态;

5)在所述的计数器非零时生成一个数据有效指示信号;

6)将该数据有效指示信号通过接收装置系统工作时钟经过三级寄存器进行三级同步;

7)将同步后的数据信号和数据有效指示信号进行并行数据解码接收,通过一个状态机实现。

2.根据权利要求1所述的基于DS编码的并行接收方法,其特征在于:所述的N为任意偶数。

3.根据权利要求1所述的基于DS编码的并行接收方法,其特征在于:所述的N为4。

4.根据权利要求1所述的基于DS编码的并行接收方法,其特征在于:所述的状态机的第一个状态是Detect_CtrlChar,也就是复位后初始状态,如果接收到的4位数据是控制字符,则仍然保持在该状态,其他情况跳转到下一状态CargoBit4;

CargoBit4:该状态下若在前一状态CargoBit10时检测到数据字符,则不做任何操作,直接转移至CargoBit8;若停留在该状态期间检测到数据或时间码,也不做任何操作,直接转移至CargoBit8;若检测到控制字符,则停留在该状态;

CargoBit8:该状态下检测到数据或控制字符,无条件转移到CargoBit2;

CargoBit2:该状态下若在前一状态CargoBit8时检测到数据字符,则不做任何操作,直接转移至CargoBit6;若检测到控制字符,则停留在该状态;若检测到数据或时间码,则转移至CargoBit6;若检测到控制字符,则直接接收;

CargoBit6:该状态下不做任何操作,无条件转移至CargoBit10;

CargoBit10:该状态下检测到数据或控制字符,无条件转移到CargoBit4。

5.一种实现权利要求1所述基于DS编码的并行接收方法的装置,包括时钟恢复电路、串并数据转换单元和并行数据接收器,其特征在于:数据信号经过时钟恢复电路恢复出时钟信号,将数据信号和时钟信号同时送入串并数据转换器,输出N位的数据信号和一位数据有效指示信号,经过接收装置系统工作时钟的三级寄存器同步后完成异步时钟域内数据正确交互,将同步后的数据信号和数据有效指示信号同时送入并行数据接收器进行数据解码接收。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201210362983.4A CN102946293B (zh) | 2012-09-26 | 2012-09-26 | 一种基于ds编码的并行接收方法及其装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201210362983.4A CN102946293B (zh) | 2012-09-26 | 2012-09-26 | 一种基于ds编码的并行接收方法及其装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN102946293A true CN102946293A (zh) | 2013-02-27 |

| CN102946293B CN102946293B (zh) | 2015-09-23 |

Family

ID=47729205

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201210362983.4A Active CN102946293B (zh) | 2012-09-26 | 2012-09-26 | 一种基于ds编码的并行接收方法及其装置 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN102946293B (zh) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108073539A (zh) * | 2017-12-27 | 2018-05-25 | 上海集成电路研发中心有限公司 | 一种mipi接口的d-phy电路 |

| CN108462620A (zh) * | 2018-02-11 | 2018-08-28 | 北京控制工程研究所 | 一种吉比特级SpaceWire总线系统 |

| CN113640654A (zh) * | 2021-07-30 | 2021-11-12 | 四川芯测电子技术有限公司 | 一种高速状态分析方法及系统 |

| CN118381583A (zh) * | 2024-06-26 | 2024-07-23 | 山东云海国创云计算装备产业创新中心有限公司 | 一种信号传输方法、装置、设备、介质及计算机程序产品 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6397312B1 (en) * | 1997-07-04 | 2002-05-28 | Fujitsu Limited | Memory subsystem operated in synchronism with a clock |

| CN101053232A (zh) * | 2003-11-25 | 2007-10-10 | 高通股份有限公司 | 具有改进链路同步的高数据速率接口 |

-

2012

- 2012-09-26 CN CN201210362983.4A patent/CN102946293B/zh active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6397312B1 (en) * | 1997-07-04 | 2002-05-28 | Fujitsu Limited | Memory subsystem operated in synchronism with a clock |

| CN101053232A (zh) * | 2003-11-25 | 2007-10-10 | 高通股份有限公司 | 具有改进链路同步的高数据速率接口 |

Non-Patent Citations (1)

| Title |

|---|

| 罗学平: "应用于航天器的高速数据传输技术的研究", 《中国会议》, 1 October 2006 (2006-10-01) * |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108073539A (zh) * | 2017-12-27 | 2018-05-25 | 上海集成电路研发中心有限公司 | 一种mipi接口的d-phy电路 |

| CN108462620A (zh) * | 2018-02-11 | 2018-08-28 | 北京控制工程研究所 | 一种吉比特级SpaceWire总线系统 |

| CN108462620B (zh) * | 2018-02-11 | 2020-10-20 | 北京控制工程研究所 | 一种吉比特级SpaceWire总线系统 |

| CN113640654A (zh) * | 2021-07-30 | 2021-11-12 | 四川芯测电子技术有限公司 | 一种高速状态分析方法及系统 |

| CN113640654B (zh) * | 2021-07-30 | 2024-02-20 | 深圳速跃芯仪科技有限公司 | 一种高速状态分析方法及系统 |

| CN118381583A (zh) * | 2024-06-26 | 2024-07-23 | 山东云海国创云计算装备产业创新中心有限公司 | 一种信号传输方法、装置、设备、介质及计算机程序产品 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102946293B (zh) | 2015-09-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Nowick et al. | Asynchronous design—Part 1: Overview and recent advances | |

| CN104954096B (zh) | 一种一主多从的高速同步串行通信数据传输方法 | |

| JPH10117185A (ja) | データを転送するためのシンクロナイザ、方法及びシステム | |

| CN103141066A (zh) | 发送电路、接收电路、发送方法、接收方法、通信系统及其通信方法 | |

| US10103830B2 (en) | Latency-optimized physical coding sublayer | |

| CN86106695A (zh) | 一种具有合作能力的同构型多计算机系统及其合作方法 | |

| US9054941B2 (en) | Clock and data recovery using dual manchester encoded data streams | |

| CN102946293B (zh) | 一种基于ds编码的并行接收方法及其装置 | |

| US4694196A (en) | Clock recovery circuit | |

| WO2012083279A2 (en) | Low power serial to parallel converter | |

| CN102710240A (zh) | 信号处理装置、方法、serdes 和处理器 | |

| US8675798B1 (en) | Systems, circuits, and methods for phase inversion | |

| CN103078667A (zh) | 一种基于超五类线的lvds高速数据传输方法 | |

| CN1161901C (zh) | 光通信系统中上行高速数据的同步接收方法与电路 | |

| CN105468561A (zh) | 一种高速异步串行通信方法 | |

| CN204362064U (zh) | 数据接收器、数据接收系统和数据传输系统 | |

| CN101026448A (zh) | 一种同步通信系统时钟再生方法及系统 | |

| CN103279442A (zh) | 一种高速互联总线的报文过滤系统及方法 | |

| CN102754407B (zh) | 串行接收机及其方法与通信系统 | |

| CN101577598A (zh) | 多路信号复用、解复用的方法、装置和系统 | |

| CN105389155B (zh) | 一种利用spi接口实现tdm音频数据接收的方法及系统 | |

| CN103067114A (zh) | 一种传输系统异步映射时钟恢复方法及设备 | |

| US6650696B1 (en) | System and method for communicating data among a plurality of digital signal processors | |

| CN204244256U (zh) | 一种多路e1解帧系统 | |

| CN100505765C (zh) | 多通道数据处理的方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |