CN100343875C - 阶层式滤波器 - Google Patents

阶层式滤波器 Download PDFInfo

- Publication number

- CN100343875C CN100343875C CNB028105141A CN02810514A CN100343875C CN 100343875 C CN100343875 C CN 100343875C CN B028105141 A CNB028105141 A CN B028105141A CN 02810514 A CN02810514 A CN 02810514A CN 100343875 C CN100343875 C CN 100343875C

- Authority

- CN

- China

- Prior art keywords

- state variable

- stream

- totalizer

- signal samples

- filter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T1/00—General purpose image data processing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F17/00—Digital computing or data processing equipment or methods, specially adapted for specific functions

- G06F17/10—Complex mathematical operations

- G06F17/14—Fourier, Walsh or analogous domain transformations, e.g. Laplace, Hilbert, Karhunen-Loeve, transforms

- G06F17/148—Wavelet transforms

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H17/00—Networks using digital techniques

- H03H17/02—Frequency selective networks

- H03H17/06—Non-recursive filters

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Theoretical Computer Science (AREA)

- Computational Mathematics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Data Mining & Analysis (AREA)

- Databases & Information Systems (AREA)

- Software Systems (AREA)

- General Engineering & Computer Science (AREA)

- Algebra (AREA)

- Image Processing (AREA)

- Lubrication Details And Ventilation Of Internal Combustion Engines (AREA)

- Filtering Materials (AREA)

- Facsimile Image Signal Circuits (AREA)

- Control Of Motors That Do Not Use Commutators (AREA)

- Filters And Equalizers (AREA)

Abstract

说明阶层式滤波器的实施例。

Description

技术领域

本公开涉及阶层式滤波器。

背景技术

在图像处理中,经常希望将例如扫描彩色图像的图像分解成两个或两个以上不同的图像表示。在本上下文中,这些图像表示称为背景和前景图像。例如,彩色或灰度文件图像可以分解成背景和前景图像,以便进行有效的图像处理操作,如典型复印机或扫描仪中所用的增强、压缩等图像处理操作。在本说明书中,这种操作常常被称为去网纹(descreen)操作。这种去网纹有时也用于消除可能存在于原始扫描图像中的半色调图案。例如,这些半色调图案如果未被正确删除,则可能引起令人眼不舒服的人造图像(artifact)。用于这种分解或去网纹操作的传统方法是对彩色图像进行滤波以便使之模糊。然后将这些模糊化的结果用于协助确定使图像模糊和锐化到何种程度以便得到分解结果。一般而言,这种模糊化可以利用“对称阶层式”滤波器实现。对称阶层式有限脉冲响应(FIR)滤波器是众所周知的。

不过,这种图像处理技术的缺点之一是,当把许多不同大小的阶层式滤波器并行用于生成多个模糊化的图像以便应用刚才所述的技术时,复杂性会增加很多倍。实现这种多阶层滤波的一种蛮力方法(brute forceapproach)是采用多个并行的FIR滤波器,如图1所示。这种方法表明,设计和实现快速“对称阶层式滤波”体系结构以便由一个源图像并行产生不同的模糊图像可能是理想的。

图1所示各FIR块的括号中给出的数字表示对应长度的阶层式滤波器。例如,(1,2,1)是阶或长度为3的对称阶层式有限脉冲响应(FIR)滤波器的滤波系数。同样地,(1,2,3,2,1)是阶为5的FIR阶层式滤波器的系数,依此类推。

不幸的是,图1所示的方法存在一些缺点。例如,冗余计算可能导致低效率。而且,FIR实现常常使用乘法器电路。虽然存在减少或避免使用乘法器的实现方式,如利用移位和求和电路,但这可能导致增加的定时,从而降低电路吞吐量。因此存在改进阶层式滤波实现方式或体系结构的需要。

发明内容

本发明的目的是改进阶层式滤波的实现方式或体系结构。

根据本发明,提供了一种集成电路,包括:阶层式滤波器;所述阶层式滤波器包括卷式加法滤波器,其特征在于,所述加法滤波器包括一系列级联单元,每个所述单元生成不同阶的状态变量信号样本流,其中所述单元包括无乘法器单元。

本发明还提供了一种滤波器部件,包括:三个延迟单元和一个加法器,所述延迟单元和加法器以便被连接产生高阶状态变量信号样本流,其中所述延迟单元将输入信号样本流和低阶状态变量信号样本流提供到所述加法器以产生所述高阶状态变量信号样本流,其中所述三个延迟单元和一个加法器是无乘法器单元。

本发明还提供了一种用于产生第一阶的滤波状态变量信号样本流的方法,包括:利用无乘法器单元,使第二阶的滤波状态变量信号样本流延迟,所述第二阶小于第一阶;对延迟的状态变量信号样本流、输入信号样本流和所述输入信号样本流的延迟版本求和。

本发明还提供了一种图像处理系统,包括:用于滤波扫描彩色图像的图形处理单元;所述图形处理单元包括至少一个阶层式滤波器;所述至少一个阶层式滤波器包括卷式加法滤波器,所述卷式加法滤波器包括一序列的级联单元,每个所述级联单元生成不同阶的状态变量信号样本流,其中,所述级联单元包括无乘法器单元。

附图简述

本说明书的结论部分特别指出有关主题并明确要求对有关主题的权利。但是,所要求的主题(有关其结构和操作方法)及其目的、特征和优点可以通过参照如下详细说明书,并在阅读时参考附图而获得最佳的理解。

图1是说明用于实现有限脉冲响应(FIR)多阶层式滤波体系结构的蛮力方法的框图;

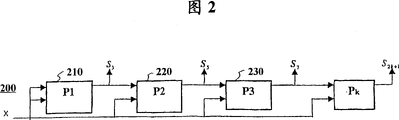

图2是卷式加法滤波器(rolling summation filter-RSF)的一个实施例的一部分;

图3是图2所示部件或子部件的一个实施例;

图4是一个无乘法器阶层式滤波器实施例中图2所示的实施例;

图5是显示卷式加法滤波器的一种实现的按时间顺序排列的状态变量信号样本序列的表格;以及

图6是显示阶层式滤波器的一种实现的按时间顺序排列的滤波输出信号样本序列的表格。

具体实施方式

在如下详细说明中,给出了各种具体细节以便提供对所要求主题的彻底理解。但是,本专业的技术人员要理解,所要求的主题可以无需这些具体细节就得以实施。在其它情况下,不详细描述熟知的方法、过程、部件和电路以免使所要求的主题模糊。

如前所述,阶层式滤波器,尤其是对称阶层式滤波可配合彩色图像或彩色图像处理使用,以对图像进行分解(例如分解成背景和前景图像)或者消除其网纹。尽管所要求的主题范围上不限于此方面,但在这种情形中,减少计算复杂度或处理和/或硬件成本的阶层式滤波体系结构尤其理想。同样,无乘法器的实现方案,即实现时不需要利用乘法运算的实现方案通常也是理想的,这是因为这种实现方案或实施方式实现起来比那些使用或包括乘法电路的实现更经济。因此,甚至采用了较少乘法运算的实现也是理想的。

图2说明可用于实现随后将作详述的所推荐的阶层式滤波器的“卷式加法滤波器”即RSF体系结构的一个实施例200,虽然所要求的主题的范围并不限于此。实施例200包括统一的级联卷式加法滤波体系结构,以便具有不同阶(如长度分别为3、5、7等等)的加法滤波器系列产生多个和状态变量(summed state variable)信号流S2、S3、S4、…S7,这些状态变量信号流的产生是并行进行的。虽然所要求的主题的范围同样不限于此特定实施例,但在此实施例中,所要实现的不同阶的每个滤波器在每个时钟周期产生滤波状态变量信号(filtered state variable signal)流。因此,除了计算效率高,此特定实施例还具有很好的吞吐量。可以利用状态变量信号流来产生如图4所示的阶层式滤波输出信号流,随后将会对此作更为详细的说明。

在具体符号上下文中来理解图2。例如,输入源信号X可以如下表示为:

X=(x0,x1,…,xi-2,xi-1,xi,xi+1,xi+2,…)

在数字或离散信号处理中,滤波可以表示为输入信号X和滤波器F的卷积,在此上下文中滤波器F是称为有限脉冲响应(FIR)滤波器的有限长度数字滤波器。因此,滤波输出信号流可以如下表示为:

Y=XF

如前所述,此特定实施例采用了阶层式滤波器。这些滤波器一般用长度或阶为奇数,如3,5,7,9等的数字滤波器来实现。这可以表示为M=2N+1,其中,N是大于1的正整数。这种数字滤波器的一些实例如下:

F3=(1,2,1)

F5=(1,2,3,2,1)

F7=(1,2,3,4,3,2,1)

F9=(1,2,3,4,5,4,3,2,1)

…

FM=(1,2,3,…,N,…,3,2,1)

对于前述滤波器,滤波输出信号或输出信号流可以如下表示为:

B3=XF3=(b0 3,b1 3,…,bi-1 3,bi 3,bi+1 3,…),即输入信号X被F3滤波之后的结果;

B5=XF5=(b0 5,b1 5,…,bi-1 5,bi 5,bi+1 5,…),即输入信号X被F5滤波之后的结果;

B7=XF7=(b0 7,b1 7,…,bi-1 7,bi 7,bi+1 7,…),即输入信号X被F7滤波之后的结果;

B9=XF9=(b0 9,b1 9,…,bi-1 9,bi 9,bi+1 9,…),即输入信号X被F9滤波之后的结果;

…

BM=XFM=(b0 M,b1 M,…,bi-1 M,bi M,bi+1 M,…),即输入信号X被FM滤波之后的结果。

表示这些滤波输出信号样本的另一种经验性方法如下所示:

bi 3=xi-2+2xi-1+xi

bi 5=xi-4+2xi-3+3xi-2+2xi-1+xi

bi 7=xi-6+2xi-5+3xi-4+4xi-3+3xi-2+2xi-1+xi

bi 9=xi-8+2xi-7+3xi-6+4xi-5+5xi-4+4xi-3+3xi-2+2xi-1+xi

同样地,通过引入在此上下文中称为状态变量的变量,上述表达式可以重新表示如下:

bi 3=xi-1+si 3,其中,si 3=xi-2+xi-1+xi

bi 5=bi-1 3+si 5,其中,si 5=xi-4+xi-3+xi-2+xi-1+xi

bi 7=bi-1 5+si 7,其中,si 7=xi-6+xi-5+xi-4+xi-3+xi-2+xi-1+xi

bi 9=bi-1 7+si 9,其中,si 9=xi-8+xi-7+xi-6+xi-5+xi-4+xi-3+xi-2+xi-1+xi

如下将会详述,对图4的研究表明,计算得到的输出信号流B3、B5、B7、B9等等可以利用作为图4所示实施例的一部分的图2所示的实施例来产生。

图5是说明如图2所示以及如联系图3所作的更为详细的描述那样分别产生的按时间先后顺序排列的状态变量信号序列,即状态变量信号流S2、S3、S4、…、S7。同样,图6是说明滤波输出信号流B3、B5、B7等等的按时间先后顺序排列的序列的表格。如图4所示,这些输出信号是通过采用例如加法器和例如延迟器而得以产生的。

除了提供滤波输出信号流B3、B5、B7,图6中的表格说明按照加到图2所示阶层式滤波器体系结构实施例上的定时的时间顺序产生这些滤波输出信号流,以产生状态变量信号样本流。如前所述,输出信号流可从信号样本(例如xi和si)产生,即从输入信号样本和状态变量信号样本产生,随后将对此作更为详细的说明。

图6所示的表格说明bi 7是通过根据以上提供的等式将输入信号bi 5加到si 7中而产生的。信号bi 5被延迟一个时钟周期。这是由例如图4中的延迟单元,即数字延迟单元来完成的。因此,延迟一个时钟周期的输出信号样本B5与状态变量信号样本S7相加以产生输出信号样本B7。同样地,数字延迟单元可用于产生输出信号样本流B5。同样地,输入信号样本流X可以被延迟并与S3相加以生成阶层式滤波器输出信号样本流B3。

应注意,图2所示的RSF体系结构实施例包括部件或子部件的实施例,例如图3所示的300。图3所示的实施例300包括一个部件,该部件包括三个延迟单元320、330和340以及一个三输入端的加法器310。此特定实施例中采用三输入端加法器是为了提供高速实现。

在此特定实施例中,连接延迟单元和加法器以便从输入信号样本或信号样本流和低阶滤波状态变量信号样本或信号样本流生成高阶滤波状态变量信号样本或信号样本流。例如,参照图3所示实施例,xi包括输入信号样本或信号样本流,si 2k-1包括低阶RSF滤波状态变量信号样本或信号样本流,以及si 2k+1表示高阶RSF滤波状态变量信号样本或信号样本流。因此,在此特定实施例中,高阶和低阶状态变量信号样本或信号样本流之间的阶之差为2,不过,本发明所要求的主题并不受此限制。

图4是包括图2所示RSF体系结构的实施例的阶层式滤波器的实施例的示意图。在图4中,RSF体系结构实施例标记为200。因此,虽然图4中未示出,但200包括一些部件或子部件,例如图2所示的210、220或230。应注意,图4所示的实施例在集成电路400上实现,但本发明所要求的主题并不受此限制。

当然,应理解,虽然已对本发明的特定实施例作了说明,但所要求的主题范围并不局限于特定的实施例或实现方式。例如,一个实施例可以采用硬件,而另一个实施例则可采用软件。同样,实施例可以采用例如固件或硬件、软件或固件的任意组合形式。同样,一个实施例可以包括一种产品,如存储媒体,虽然所要求的主题范围并不受此限制。可以在诸如CD-ROM或盘之类的存储媒体中存储一种指令,该指令在由诸如计算机系统或平台或成像系统之类的系统执行时可实现例如前述的对图像或视频滤波或处理的方法的实施例。例如,图像处理平台或成像处理系统可包括图像处理单元、视频或图像输入/输出设备和/或存储器。

虽然已对本发明的某些特征作了图示和说明,本领域的技术人员现在可能想到许多修改、替代、变化和等效方案。因此,应理解,所附权利要求书旨在涵盖属于所要求主题的真实精神范围内的所有这些修改和变化。

Claims (15)

1.一种集成电路,包括:

阶层式滤波器;

所述阶层式滤波器包括卷式加法滤波器,其特征在于,所述加法滤波器包括一系列级联单元,每个所述单元生成不同阶的状态变量信号样本流,其中所述单元包括无乘法器单元。

2.如权利要求1所述的集成电路,其特征在于,至少一个所述无乘法器单元包括三个延迟单元和一个加法器,所述延迟单元和所述加法器被连接以便产生高阶状态变量信号样本流,其中所述延迟单元将输入信号样本流和低阶状态变量信号样本流提供到所述加法器以产生所述高阶状态变量信号样本流。

3.如权利要求2所述的集成电路,其特征在于,所述加法器包括三输入端加法器。

4.如权利要求2所述的集成电路,其特征在于,所述高阶和低阶状态变量信号样本流之间的阶之差为2。

5.一种滤波器部件,包括:

三个延迟单元和一个加法器,所述延迟单元和加法器以便被连接产生高阶状态变量信号样本流,其中所述延迟单元将输入信号样本流和低阶状态变量信号样本流提供到所述加法器以产生所述高阶状态变量信号样本流,其中所述三个延迟单元和一个加法器是无乘法器单元。

6.如权利要求5所述的滤波器部件,其特征在于,所述高阶和低阶状态变量信号样本流之间的阶之差为2。

7.如权利要求5所述的滤波器部件,其特征在于,所述加法器包括三输入端加法器。

8.如权利要求5所述的滤波器部件,其特征在于,所述滤波器部件被连接为形成卷式加法滤波器。

9.一种用于产生第一阶的滤波状态变量信号样本流的方法,包括:

利用无乘法器单元,使第二阶的滤波状态变量信号样本流延迟,所述第二阶小于第一阶;

对延迟的状态变量信号样本流、输入信号样本流和所述输入信号样本流的延迟版本求和。

10.如权利要求9所述的方法,其特征在于,所述第一阶和第二阶之差为2。

11.如权利要求9所述的方法,其特征在于,所述延迟状态变量信号样本流被延迟两个时钟周期,而所述输入信号样本流的延迟版本被延迟一个时钟周期。

12.一种图像处理系统,包括:

用于滤波扫描彩色图像的图形处理单元;

所述图形处理单元包括至少一个阶层式滤波器;所述至少一个阶层式滤波器包括卷式加法滤波器,

所述卷式加法滤波器包括一序列的级联单元,每个所述级联单元生成不同阶的状态变量信号样本流,其中,所述级联单元包括无乘法器单元。

13.如权利要求12所述的图像处理系统,其特征在于,至少一个所述无乘法器单元包括三个延迟单元和一个加法器,所述延迟单元和加法器被连接以产生高阶状态变量信号样本流,其中所述延迟单元将输入信号样本流和低阶状态变量信号样本流提供到所述加法器以产生所述高阶状态变量信号样本流。

14.如权利要求12所述的图像处理系统,其特征在于所述加法器包括三输入端加法器。

15.如权利要求12所述的图像处理系统,其特征在于,所述高阶和低阶状态变量信号样本流之间的阶差为2。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/820,108 US6766286B2 (en) | 2001-03-28 | 2001-03-28 | Pyramid filter |

| US09/820,108 | 2001-03-28 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1531712A CN1531712A (zh) | 2004-09-22 |

| CN100343875C true CN100343875C (zh) | 2007-10-17 |

Family

ID=25229902

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028105141A Expired - Fee Related CN100343875C (zh) | 2001-03-28 | 2002-03-07 | 阶层式滤波器 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US6766286B2 (zh) |

| EP (1) | EP1415277B1 (zh) |

| JP (1) | JP2004525463A (zh) |

| KR (1) | KR100560093B1 (zh) |

| CN (1) | CN100343875C (zh) |

| AT (1) | ATE362150T1 (zh) |

| DE (1) | DE60220064T2 (zh) |

| HK (1) | HK1061735A1 (zh) |

| TW (1) | TWI224754B (zh) |

| WO (1) | WO2002080098A2 (zh) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6563439B1 (en) * | 2000-10-31 | 2003-05-13 | Intel Corporation | Method of performing Huffman decoding |

| US6636167B1 (en) * | 2000-10-31 | 2003-10-21 | Intel Corporation | Method of generating Huffman code length information |

| US7218418B2 (en) * | 2002-07-01 | 2007-05-15 | Xerox Corporation | Digital de-screening of documents |

| US20070061390A1 (en) * | 2005-09-09 | 2007-03-15 | Leo Bredehoft | Interpolator using splines generated from an integrator stack seeded at input sample points |

| US7904841B1 (en) | 2007-10-12 | 2011-03-08 | Lockheed Martin Corporation | Method and system for optimizing digital filters |

| US9197902B2 (en) | 2010-11-30 | 2015-11-24 | M.S. Ramaiah School Of Advanced Studies | Wavelet transformation using multicore processors |

| CN104601142A (zh) * | 2013-10-31 | 2015-05-06 | 横河电机株式会社 | 滤波方法、滤波器和闪变测试系统 |

| US10853068B2 (en) * | 2018-09-28 | 2020-12-01 | Ocean Logic Pty Ltd | Method for operating a digital computer to reduce the computational complexity associated with dot products between large vectors |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4674125A (en) * | 1983-06-27 | 1987-06-16 | Rca Corporation | Real-time hierarchal pyramid signal processing apparatus |

| US4703514A (en) * | 1985-09-16 | 1987-10-27 | Rca Corporation | Programmed implementation of real-time multiresolution signal processing apparatus |

| US4829378A (en) * | 1988-06-09 | 1989-05-09 | Bell Communications Research, Inc. | Sub-band coding of images with low computational complexity |

| US5561617A (en) * | 1991-12-11 | 1996-10-01 | David Sarnoff Research Center, Inc. | Pyramid processor integrated circuit |

Family Cites Families (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5875122A (en) | 1996-12-17 | 1999-02-23 | Intel Corporation | Integrated systolic architecture for decomposition and reconstruction of signals using wavelet transforms |

| US6009201A (en) | 1997-06-30 | 1999-12-28 | Intel Corporation | Efficient table-lookup based visually-lossless image compression scheme |

| US6009206A (en) | 1997-09-30 | 1999-12-28 | Intel Corporation | Companding algorithm to transform an image to a lower bit resolution |

| US6091851A (en) | 1997-11-03 | 2000-07-18 | Intel Corporation | Efficient algorithm for color recovery from 8-bit to 24-bit color pixels |

| US6285796B1 (en) | 1997-11-03 | 2001-09-04 | Intel Corporation | Pseudo-fixed length image compression scheme |

| US6130960A (en) | 1997-11-03 | 2000-10-10 | Intel Corporation | Block-matching algorithm for color interpolation |

| US6151069A (en) | 1997-11-03 | 2000-11-21 | Intel Corporation | Dual mode digital camera for video and still operation |

| US6351555B1 (en) | 1997-11-26 | 2002-02-26 | Intel Corporation | Efficient companding algorithm suitable for color imaging |

| US6229578B1 (en) | 1997-12-08 | 2001-05-08 | Intel Corporation | Edge-detection based noise removal algorithm |

| US6094508A (en) | 1997-12-08 | 2000-07-25 | Intel Corporation | Perceptual thresholding for gradient-based local edge detection |

| US6348929B1 (en) | 1998-01-16 | 2002-02-19 | Intel Corporation | Scaling algorithm and architecture for integer scaling in video |

| US6215916B1 (en) | 1998-02-04 | 2001-04-10 | Intel Corporation | Efficient algorithm and architecture for image scaling using discrete wavelet transforms |

| US6392699B1 (en) | 1998-03-04 | 2002-05-21 | Intel Corporation | Integrated color interpolation and color space conversion algorithm from 8-bit bayer pattern RGB color space to 12-bit YCrCb color space |

| US6356276B1 (en) | 1998-03-18 | 2002-03-12 | Intel Corporation | Median computation-based integrated color interpolation and color space conversion methodology from 8-bit bayer pattern RGB color space to 12-bit YCrCb color space |

| US6366694B1 (en) | 1998-03-26 | 2002-04-02 | Intel Corporation | Integrated color interpolation and color space conversion algorithm from 8-bit Bayer pattern RGB color space to 24-bit CIE XYZ color space |

| US6366692B1 (en) | 1998-03-30 | 2002-04-02 | Intel Corporation | Median computation-based integrated color interpolation and color space conversion methodology from 8-bit bayer pattern RGB color space to 24-bit CIE XYZ color space |

| US6154493A (en) | 1998-05-21 | 2000-11-28 | Intel Corporation | Compression of color images based on a 2-dimensional discrete wavelet transform yielding a perceptually lossless image |

| US6124811A (en) | 1998-07-02 | 2000-09-26 | Intel Corporation | Real time algorithms and architectures for coding images compressed by DWT-based techniques |

| US6233358B1 (en) | 1998-07-13 | 2001-05-15 | Intel Corporation | Image compression using directional predictive coding of the wavelet coefficients |

| US6236765B1 (en) | 1998-08-05 | 2001-05-22 | Intel Corporation | DWT-based up-sampling algorithm suitable for image display in an LCD panel |

| US5995210A (en) | 1998-08-06 | 1999-11-30 | Intel Corporation | Integrated architecture for computing a forward and inverse discrete wavelet transforms |

| US6047303A (en) | 1998-08-06 | 2000-04-04 | Intel Corporation | Systolic architecture for computing an inverse discrete wavelet transforms |

| US6178269B1 (en) | 1998-08-06 | 2001-01-23 | Intel Corporation | Architecture for computing a two-dimensional discrete wavelet transform |

| US6166664A (en) | 1998-08-26 | 2000-12-26 | Intel Corporation | Efficient data structure for entropy encoding used in a DWT-based high performance image compression |

| US6301392B1 (en) | 1998-09-03 | 2001-10-09 | Intel Corporation | Efficient methodology to select the quantization threshold parameters in a DWT-based image compression scheme in order to score a predefined minimum number of images into a fixed size secondary storage |

| US6195026B1 (en) | 1998-09-14 | 2001-02-27 | Intel Corporation | MMX optimized data packing methodology for zero run length and variable length entropy encoding |

| US6108453A (en) | 1998-09-16 | 2000-08-22 | Intel Corporation | General image enhancement framework |

| US6236433B1 (en) | 1998-09-29 | 2001-05-22 | Intel Corporation | Scaling algorithm for efficient color representation/recovery in video |

| US6535648B1 (en) | 1998-12-08 | 2003-03-18 | Intel Corporation | Mathematical model for gray scale and contrast enhancement of a digital image |

| US6151415A (en) | 1998-12-14 | 2000-11-21 | Intel Corporation | Auto-focusing algorithm using discrete wavelet transform |

| US6215908B1 (en) | 1999-02-24 | 2001-04-10 | Intel Corporation | Symmetric filtering based VLSI architecture for image compression |

| US6381357B1 (en) | 1999-02-26 | 2002-04-30 | Intel Corporation | Hi-speed deterministic approach in detecting defective pixels within an image sensor |

| US6275206B1 (en) | 1999-03-17 | 2001-08-14 | Intel Corporation | Block mapping based up-sampling method and apparatus for converting color images |

| US6377280B1 (en) | 1999-04-14 | 2002-04-23 | Intel Corporation | Edge enhanced image up-sampling algorithm using discrete wavelet transform |

| US6292114B1 (en) | 1999-06-10 | 2001-09-18 | Intel Corporation | Efficient memory mapping of a huffman coded list suitable for bit-serial decoding |

| US6373481B1 (en) | 1999-08-25 | 2002-04-16 | Intel Corporation | Method and apparatus for automatic focusing in an image capture system using symmetric FIR filters |

| US6449380B1 (en) | 2000-03-06 | 2002-09-10 | Intel Corporation | Method of integrating a watermark into a compressed image |

-

2001

- 2001-03-28 US US09/820,108 patent/US6766286B2/en not_active Expired - Lifetime

-

2002

- 2002-03-07 AT AT02721304T patent/ATE362150T1/de not_active IP Right Cessation

- 2002-03-07 EP EP02721304A patent/EP1415277B1/en not_active Expired - Lifetime

- 2002-03-07 KR KR1020037012751A patent/KR100560093B1/ko not_active IP Right Cessation

- 2002-03-07 DE DE60220064T patent/DE60220064T2/de not_active Expired - Lifetime

- 2002-03-07 WO PCT/US2002/007087 patent/WO2002080098A2/en active IP Right Grant

- 2002-03-07 CN CNB028105141A patent/CN100343875C/zh not_active Expired - Fee Related

- 2002-03-07 JP JP2002578245A patent/JP2004525463A/ja active Pending

- 2002-03-26 TW TW091105914A patent/TWI224754B/zh not_active IP Right Cessation

-

2004

- 2004-06-29 HK HK04104646A patent/HK1061735A1/xx not_active IP Right Cessation

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4674125A (en) * | 1983-06-27 | 1987-06-16 | Rca Corporation | Real-time hierarchal pyramid signal processing apparatus |

| US4703514A (en) * | 1985-09-16 | 1987-10-27 | Rca Corporation | Programmed implementation of real-time multiresolution signal processing apparatus |

| US4829378A (en) * | 1988-06-09 | 1989-05-09 | Bell Communications Research, Inc. | Sub-band coding of images with low computational complexity |

| US5561617A (en) * | 1991-12-11 | 1996-10-01 | David Sarnoff Research Center, Inc. | Pyramid processor integrated circuit |

Also Published As

| Publication number | Publication date |

|---|---|

| ATE362150T1 (de) | 2007-06-15 |

| DE60220064D1 (de) | 2007-06-21 |

| WO2002080098A3 (en) | 2004-01-22 |

| KR20030085583A (ko) | 2003-11-05 |

| JP2004525463A (ja) | 2004-08-19 |

| HK1061735A1 (en) | 2004-09-30 |

| US6766286B2 (en) | 2004-07-20 |

| TWI224754B (en) | 2004-12-01 |

| DE60220064T2 (de) | 2008-01-10 |

| KR100560093B1 (ko) | 2006-03-10 |

| CN1531712A (zh) | 2004-09-22 |

| EP1415277A2 (en) | 2004-05-06 |

| WO2002080098A2 (en) | 2002-10-10 |

| EP1415277B1 (en) | 2007-05-09 |

| US20020143832A1 (en) | 2002-10-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100343875C (zh) | 阶层式滤波器 | |

| CN1925323A (zh) | 采样率转换方法及其电路 | |

| CN1655579A (zh) | 用于文档的数字去网的半色调网屏频率和大小估算 | |

| CN1324527C (zh) | 用于图像缩放的单元和方法 | |

| CN1223202C (zh) | 无倍增器的锥形滤色器 | |

| CN100342643C (zh) | 二维锥形滤波器 | |

| JP4102198B2 (ja) | 2次元ピラミッド・フィルタ・アーキテクチャ | |

| CN1511374A (zh) | 二维阶层式滤波器体系结构 | |

| CN1222171C (zh) | 图像变换装置和方法 | |

| CN1140138C (zh) | 用于将数字复合视频信号分离成分量的装置 | |

| CN1511373A (zh) | 二维锥形滤波器体系结构 | |

| CN1025405C (zh) | 数字内插电路 | |

| CN1781249A (zh) | 数字滤波器结构 | |

| CN101079612A (zh) | 高速数字滤波器的实现方法及结构 | |

| CN1905622A (zh) | 动态选择模块与动态选择滤波器系数组的方法 | |

| CN1122931C (zh) | 可实现数字滤波运算的微处理器结构及数字滤波运算方法 | |

| CN1822045A (zh) | 一种数字信号的重采样方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20071017 Termination date: 20130307 |