RU2355103C1 - Генератор псевдослучайной последовательности - Google Patents

Генератор псевдослучайной последовательности Download PDFInfo

- Publication number

- RU2355103C1 RU2355103C1 RU2007140610/09A RU2007140610A RU2355103C1 RU 2355103 C1 RU2355103 C1 RU 2355103C1 RU 2007140610/09 A RU2007140610/09 A RU 2007140610/09A RU 2007140610 A RU2007140610 A RU 2007140610A RU 2355103 C1 RU2355103 C1 RU 2355103C1

- Authority

- RU

- Russia

- Prior art keywords

- input

- output

- feedback

- adder

- trigger

- Prior art date

Links

- 238000009434 installation Methods 0.000 claims description 8

- 230000000903 blocking effect Effects 0.000 claims description 6

- 239000000126 substance Substances 0.000 abstract 1

- 238000010586 diagram Methods 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 5

- 238000000034 method Methods 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 2

- 230000003213 activating effect Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Landscapes

- Detection And Prevention Of Errors In Transmission (AREA)

Abstract

Изобретение относится к области радиотехники и может использоваться в качестве генератора опорных сигналов в передатчиках и приемниках широкополосных сигналов. Достигаемый технический результат - формирование последовательности различной длины и структуры. Генератор содержит генератор тактовых импульсов, М триггеров, М объединителей, М-коммутирующих элементов, блок установки начального состояния, N-элементов управления сумматором, N-блоков обратной связи, N-сумматоров по модулю 2, элемент запуска, элемент «ИЛИ». 8 ил.

Description

Изобретение относится к области радиотехники и может использоваться в качестве генератора опорных сигналов в передатчиках и приемниках широкополосных сигналов.

Известны генераторы псевдослучайной последовательности

Системы связи с шумоподобными сигналами, Варакина Л.Е. - М.: Радио и связь, 1985 с.50 рис.3.14 (Генератор М-последовательности), содержащие триггеры, сумматор по модулю два, недостатком которых является фиксированная, ограниченная длина и структура формируемой псевдослучайной последовательности.

Генератор псевдослучайной последовательности по патенту (RU №2003136964 от 22.12.2003 года, МПК Н 03/00, G06F 7/58). Он содержит генератор N/2-разрядной двоичной псевдослучайной последовательности, реализованной на регистре сдвига с линейными обратными связями. Его недостатком является фиксированная, ограниченная длина и структура формируемой псевдослучайной последовательности.

Наиболее близким по технической сущности к заявляемому объекту является генератор псевдослучайной последовательности (RU №2223539 от 31.05.2002 года, МПК Н03В 29/00, G06F 7/58), содержащий генератор тактовых импульсов, группу из m-триггеров, m-умножителей, сумматор по модулю два, оперативно запоминающий блок, формирователь адреса, двухвходовый сумматор по модулю два, делитель частоты. Данный генератор псевдослучайных последовательностей, содержащий генератор тактовых импульсов, выход которого соединен с первыми сигнальными входами с первого по m триггеров соответственно, выходы которых через m умножителей соединены с n входами сумматора по модулю два соответственно, выход которого соединен со вторым сигнальным входом первого триггера, отличающийся тем, что введены последовательно соединенные делитель частоты, двухвходовый сумматор по модулю два и формирователь адреса, выход которого шиной соединен со вторым входом оперативно-запоминающего блока, первый вход которого соединен с выходом сумматора по модулю два. Кроме того, выход генератора тактовых импульсов соединен с входом делителя частоты и со вторым входом двухвходового сумматора по модулю два, выход которого соединен с третьим входом оперативно-запоминающего блока.

Однако устройство-прототип имеет ограниченную область применения, обусловленную тем, что он формирует псевдослучайную последовательность фиксированной, ограниченной длины и только с фиксированным набором структур, это объясняется тем, что количество используемых для формирования псевдослучайной последовательности триггеров и умножителей не может изменяться, кроме этого, ближайший аналог имеет относительно низкую надежность, так как при выходе из строя любого из элементов, предназначенных для формирования псевдослучайной последовательности, генератор не выполняет своего функционального назначения.

Целью изобретения является разработка генератора псевдослучайной последовательности, обеспечивающего возможность расширения области его применения благодаря формированию последовательности различной длины и структуры. Заявленный генератор расширяет арсенал средств данного назначения.

Поставленная цель достигается тем, что в известном генераторе псевдослучайной последовательности, содержащем сумматор по модулю два и генератор тактовых импульсов, выход которого подключен к тактовым входам М≥3 триггеров, дополнительно введены блок установки начального состояния, элемент запуска, элемент «ИЛИ», М коммутирующих элементов, М объединителей, N=M-1 элементов управления сумматором, N блоков обратной связи и N-1 сумматоров по модулю два.

Новым также является то, что выход блока установки начального состояния подключен к входам установки в состояние ноль М-триггеров и к входу элемента запуска. Выход элемента запуска подключен к первому входу элемента «ИЛИ», второй вход которого подключен к выходу первого блока обратной связи. Выход р-го, где р=1,2,…(М-1), коммутирующего элемента подключен к первому входу р-го объединителя, второй вход которого подключен к выходу р-го триггера. Выход р-го объединителя подключен к первому входу (р+1)-го коммутирующего элемента, информационному входу (р-1)-го триггера и информационному входу р-го элемента управления сумматором. Управляющий выход р-го элемента управления сумматором подключен к блокирующему входу р-го блока обратной связи, информационный вход которого подключен к выходу р-го сумматора по модулю два. Первый и второй информационные входы каждого сумматора подключены соответственно к первому и второму информационному выходам р-го элемента управления сумматором. Вход обратной связи р-го элемента управления сумматором и передающий вход р-го блока обратной связи подключены к информационному выходу (р+1)-го блока обратной связи. Выход М-го объединителя подключен к входу обратной связи N-го элемента управления сумматором и передающему входу N-го блока обратной связи и является выходом генератора случайной последовательности. Выход элемента «ИЛИ» подключен к второму входу первого коммутирующего элемента и информационному входу первого триггера. Первый вход m-го, где m=1,2,…М, коммутирующего элемента подключен к входу установки в состояние единица и к управляющему входу m-го триггера и является m-м управляющим входом генератора случайной последовательности, причем блокирующий вход n-го, где n=l,2,…N, элемента управления сумматором подключен к входу установки в состояние единица (n+1)-го триггера. Разрешающий вход n-го элемента управления сумматором является n-м управляющим входом обратной связи генератора псевдослучайной последовательности.

Заявленное устройство поясняется чертежами, где:

Фиг 1: Структурная схема генератора псевдослучайной последовательности

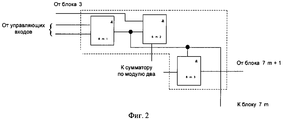

Фиг 2: Схема элемента управления сумматором

Фиг 3: Схема блока обратной связи

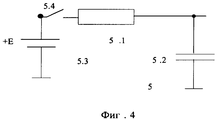

Фиг 4: Схема блока установки начального состояния

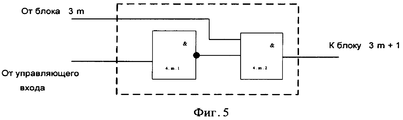

Фиг 5: Схема коммутирующего элемента

Фиг 6: Вариант схемы элемента запуска

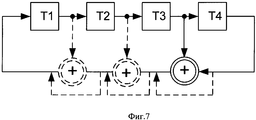

Фиг 7: Рисунок, поясняющий работу генератора

Фиг 8: Таблица структур псевдослучайных последовательностей

Генератор псевдослучайной последовательности, показанный на фиг.1, состоит из:

генератора тактовых импульсов (ГТИ) 1, М триггеров 21- 2М, М объединителей 31-3М, М-коммутирующих элементов (КЭ) 41-4М, блока установки начального состояния (БУНС) 5, N-элементов управления сумматором (ЭУС) 61-6N, N-блоков обратной связи (БОС) 71-7N, N-сумматоров по модулю 2 81-8N, элемента запуска (ЭЗ) 9, элемента «ИЛИ» 10 со связями между ними. Выход БУНС 5 подключен к входам установки в состояние ноль М триггеров 21-2М. Выход БУНС 5 подключен к входу ЭЗ 9. Выход ЭЗ 9 подключен к первому входу элемента «ИЛИ». Второй вход элемента «ИЛИ» подключен к выходу первого БОС. Выход р-го КЭ, где р=1,2,…(М-1), подключен к первому входу р-го объединителя 31-3М. Второй вход р-го объединителя 31-3М подключен к выходу р-го триггера 21-2М. Выход р-го объединителя 31-3М подключен к первому входу (р+1)-го КЭ 41-4М, информационному входу (р+1)-го триггера 21-2М и информационному входу р-го ЭУС 61-6N. Управляющий выход 61-6N подключен к блокирующему входу р-го БОС 71-7N. Информационный вход БОС 71-7N подключен к выходу р-го сумматора по модулю два 81-8N. Первый и второй информационные входы сумматора по модулю два 81-8N подключены соответственно к первому и второму информационному выходам р-го ЭУС 61-6N. Вход обратной связи р-го ЭУС 61-6N и передающий вход р-го БОС 71-7N подключены к информационному выходу (р+1)-го БОС 71-7N. Выход М-го объединителя 31-3М подключен к входу обратной связи N-го ЭУС 61-6N. Выход М-го объединителя 31-3М подключен к передающему входу N-го БОС 71-7N и является выходом генератора случайной последовательности. Выход элемента «ИЛИ» 10 подключен к второму входу первого КЭ 41-4М. Выход элемента «ИЛИ» 10 подключен к информационному входу первого триггера 21-2М. Первый вход m-го, где m=1,2,…М, КЭ 41 - 4 м, подключен к входу установки в состояние единица. Первый вход m-го, где m=1,2,…М, КЭ 41-4М, подключен к управляющему входу m-го триггера 21-2М и является m-м управляющим входом генератора случайной последовательности. Блокирующий вход n-го, где n=l,2,…N, ЭУС 61-6N подключен к входу установки в состояние единица (n+1)-го триггера 21-2М. Разрешающий вход n-го ЭУС 61-6N является n-м управляющим входом обратной связи генератора псевдослучайной последовательности.

Входящие в общую структуру генератора псевдослучайной последовательности элементы могут быть реализованы в настоящее время при использовании имеющейся элементной базы:

Генератор тактовых импульсов 1 может быть реализован путем применения интегральной схемы 2ГС191, как описано в книге: В.А.Батушев; Основы применения интегральных схем - ВАС, 1972. стр.83-84.

Элементы "И", "ИЛИ", "ИЛИ-НЕ" известны и описаны, например, в книге: П.П.Мальцев, Н.С.Долидзе, М.И.Критенко и др. Цифровые интегральные микросхемы; Справочник. - М.: Радио и связь, 1994, стр.234-237.

DV-триггеры известны и описаны, например, в книге: В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалев и др. Микросхемы и их применение: Справочное пособие. - М.: Энергия, 1978, стр.164-168.

Резистор 5.1 может быть реализован путем применения матрицы резисторов, описанных в книге: Б.В.Тарабрин, Л.Ф-Лунин, Ю.Н.Смирнов и др. Интегральные микросхемы; Справочник. - Издание второе, исправленное - М: Энергоатомиздат, 1985 г., стр.190.

Конденсатор 5.2 может быть реализован путем применения конденсаторов, описанных в книге: P.M.Терещук, К.М.Терещук, С.А.Седов. Полупроводниковые приемно-усилительные устройства; Справочник радиолюбителя. - Издание второе, стереотипное. - Киев: Наукова думка, 1982 г., стр.44-62.

Сумматор по модулю два 81-8N известен и описан например, в книге: Ю.А.Беляев, А.В.Семенов; Теоретические основы вычислительной техники Часть 1-ЛВВИУС, 1988. - с.117-118.

Схема элемента запуска 9, может быть реализована как переключатель механический, известный и описанный в книге: Ю.Л.Мазора, Е.А.Мачусского, В.И.Правды. Радиотехника: Энциклопедия. - М: Издательский дом «Додэка-XXI» 2002. стр.865

Генератор псевдослучайной последовательности работает следующим образом.

Подготовка устройства к работе заключается в установке всех элементов в исходное состояние:

- триггеры 21,…,2M (Фиг.1) устанавливаются в состояние логического ноля, посредством кратковременной подачи на установочные входы R триггеров 21,…,2M высокого уровня сигнала от БУНС 5 (Фиг.4) при замыкании ключа 5.4 (Фиг.4) данного блока;

- на управляющие входы 1,…,М и управляющие входы обратной связи 1,…,N (Фиг.1) подаются сигналы, определяющие структуру псевдослучайной последовательности;

- ГТИ 5 (Фиг.1) формирует сигналы тактовой синхронизации с частотой следования, соответствующей частоте формируемой псевдослучайной последовательности;

- элемент запуска 9 (Фиг.1,6) находится в отключенном состоянии.

Устройство-формирователь псевдослучайной последовательности работает в следующих режимах:

формирование псевдослучайной последовательности максимальной длины и фиксированной структуры; формирование псевдослучайной последовательности переменной длины; формирование псевдослучайной последовательности разных структур.

При формировании псевдослучайной последовательности максимальной длины и фиксированной структуры, задействованы все триггеры 21,…,2M устройства. Сумматоры по модулю два 81-8N, ЭУС 61-6N, БОС 71-7N подключаются в соответствии с установленными правилами.

Исходное состояние: на управляющие входы 1,…,М подается сигнал логической единицы, на управляющие входы обратной связи, за исключением одного, который определяет требуемую структуру формируемой псевдослучайной последовательности, подается сигнал логического ноля. Выбор входа обратной связи, определяющего структуру формируемой псевдослучайной последовательности, может проводиться по правилам, как показано, например, в книге: Варакин Л.Е. «Системы связи с шумоподобными сигналами - М.: Радио и связь, 1985, страница 59.

В данном случае устройство работает следующим образом: при замыкании контакта в элементе запуска 9 (Фиг.1, Фиг.6) сигнал логической единицы через элемент 10 ИЛИ (Фиг.1) подается на информационный вход триггера 21, с приходом синхронизирующего сигнала с генератора тактовых импульсов на синхронизирующие входы триггеров 21,…,2M данная единица записывается в триггер 21.

При приходе следующего тактового импульса триггер 21 переходит в состояние логического нуля, триггер 22 переводится в состояние логической единицы. Таким образом, логическая единица последовательно по триггерам передвигается до триггера 2M.

При переводе триггера 2M в состояние логической единицы, к выходу которого подключен сумматор по модулю два, формирующий структуру псевдослучайной последовательности, начинает формироваться псевдослучайная последовательность. При этом структура псевдослучайной последовательности формируется посредством подачи сигналов по цепи обратной связи с выхода включенного сумматора по модулю два 81-8N, на вход элемента «ИЛИ» 10 (Фиг.1, Фиг.4) далее на информационный вход триггера 21. То же самое происходит при переходе М-го триггера в состояние логической единицы. Таким образом, формируется структура псевдослучайной последовательности.

При формировании псевдослучайной последовательности переменной длины часть триггеров исключается из процесса формирования псевдослучайной последовательности путем подачи на соответствующие 1,…,М (Фиг1.) управляющие входы сигнала логический ноль. В этом случае триггер будет находиться в отключенном состоянии, а на его выходе будет сигнал логического ноля. Сигнал логического ноля на управляющем входе отключает одноименный триггер, переводя его в состояние логического ноля, и обеспечивает прохождение информационного сигнала через коммутирующий элемент 4 (Фиг.5) на соответствующий объеденитель 3 (Фиг.1) подключенный к выключенному триггеру. Тот же сигнал логического ноля на управляющем входе через схему элемента управления сумматором по модулю два (Фиг.2) отключает сумматор по модулю два и обеспечивает прохождение по цепи обратной связи (Фиг.3) информационного сигнала формирующего структуру псевдослучайной последовательности. Прохождение информационного сигнала относительно задействованных (включенных в работу) триггеров осуществляется аналогично процессу формирования псевдослучайной последовательности максимальной длинны.

Процесс передачи информации при отключении триггеров обеспечивается посредством работы схемы коммутирующего элемента. Если на управляющем входе будет сигнал логического ноля, элемент 4.m.1 (Фиг.5) подготовит элемент 4.m.2 к прохождению информационного сигнала, не задействуя одноименный отключенный триггер.

Формирование псевдослучайной последовательности разных структур обеспечивается за счет отключения (включения) сумматоров по модулю два 8 (Фиг.1).

Во всех случаях соответствующий сумматор по модулю два включается одновременной подачей на одноименный управляющий вход обратной связи и соответствующий управляющий вход логической единицы. В этом случае сигнал на входах сумматора по модулю два будет определяться сигналами на выходах предыдущего и М-го объеденителей. Элементы 6.m.2 и 6.m.3 (Фиг.2) устройства управления сумматором по модулю два находятся в ожидающем режиме, так как на выходе элемента 6.m.1 будет сигнал логической единицы, который соответственно подается на один из входов элементов 6.m.2 и 6.m.3. В то же время элемент 7.m.2 (Фиг.3) блока обратной связи находится в состоянии запрещающем продвижение информационного сигнала, что исключает передачу сигнала обратной связи, минуя сумматор по модулю два.

При наличии на управляющих входах схемы блока управления сумматором по модулю два (Фиг.1, Фиг.2) хотя бы одного логического ноля, что соответствует случаю отключения триггера из процесса формирования псевдослучайной последовательности (логический ноль на соответствующем управляющем входе (Фиг.1) или отключения сумматора по модулю два (логический ноль на управляющем входе обратной связи) в этом случае на выходах элементов 6.m.2 и 6.m.3 будет сигнал логического ноля, что обеспечит возможность передачи сигнала обратной связи, минуя сумматор по модулю два, так как элемент 7.m.1 и 7.m.2 (Фиг.3) в этом случае находятся в ожидающих режимах.

Таким образом, по сравнению с ближайшим аналогом заявленный генератор формирования псевдослучайной последовательности имеет большие функциональные возможности, поскольку может быть использован, например, для построения универсальных устройств тестирования каналов связи.

Claims (1)

- Генератор псевдослучайной последовательности, содержащий сумматор по модулю два, и генератор тактовых импульсов, выход которого подключен к тактовым входам М>=3 триггеров, отличающийся тем, что дополнительно введен блок установки начального состояния, элемент запуска, элемент ИЛИ, М коммутирующих элементов, М объединителей, N=M-1 элементов управления сумматором и N блоков обратной связи, и дополнительно N-1 сумматоров по модулю два, выход блока установки начального состояния подключен к входам установки в состояние ноль М триггеров и к входу элемента запуска, выход которого подключен к первому входу элемента ИЛИ, второй вход которого подключен к выходу первого блока обратной связи, выход р-го, где р=1, 2,…(М-1), коммутирующего элемента подключен к первому входу р-го объединителя, второй вход которого подключен к выходу р-го триггера, выход р-го объединителя подключен к первому входу (р+1)-го коммутирующего элемента, информационному входу (р+1)-го триггера и информационному входу р-го элемента управления сумматором, управляющий выход которого подключен к блокирующему входу р-го блока обратной связи, информационный вход которого подключен к выходу р-го сумматора по модулю два, первый и второй информационные входы которого подключены соответственно к первому и второму информационному выходам р-го элемента управления сумматором, вход обратной связи которого и передающий вход р-го блока обратной связи подключены к информационному выходу (р+1)-го блока обратной связи, выход М-го объединителя подключен к входу обратной связи N-го элемента управления сумматором и передающему входу N-го блока обратной связи, и является выходом генератора псевдослучайной последовательности, выход элемента ИЛИ подключен к второму входу первого коммутирующего элемента и информационному входу первого триггера, первый вход m-го, где m=1, 2,…М коммутирующего элемента подключен к входу установки в состояние единица и к управляющему входу m-го триггера и является m-м управляющим входом генератора псевдослучайной последовательности, причем блокирующий вход n-го, где n=1, 2,…N элемента управления сумматором подключен к входу установки в состояние единица (n+1)-го триггера, а разрешающий вход n-го элемента управления сумматором является n-м управляющим входом обратной связи генератора псевдослучайной последовательности.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2007140610/09A RU2355103C1 (ru) | 2007-11-01 | 2007-11-01 | Генератор псевдослучайной последовательности |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2007140610/09A RU2355103C1 (ru) | 2007-11-01 | 2007-11-01 | Генератор псевдослучайной последовательности |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| RU2355103C1 true RU2355103C1 (ru) | 2009-05-10 |

Family

ID=41020134

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| RU2007140610/09A RU2355103C1 (ru) | 2007-11-01 | 2007-11-01 | Генератор псевдослучайной последовательности |

Country Status (1)

| Country | Link |

|---|---|

| RU (1) | RU2355103C1 (ru) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2419224C1 (ru) * | 2009-12-08 | 2011-05-20 | Открытое акционерное общество "Концерн "Созвездие" | Формирователь м-последовательностей |

| RU2634233C1 (ru) * | 2017-01-12 | 2017-10-24 | Борис Иванович Крыжановский | Способ генерации псевдослучайной двоичной последовательности |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SU1750033A2 (ru) * | 1990-06-11 | 1992-07-23 | Военный Инженерный Краснознаменный Институт Им.А.Ф.Можайского | Генератор псевдослучайных последовательностей |

| SU1758851A2 (ru) * | 1990-08-10 | 1992-08-30 | Ростовское высшее военное командно-инженерное училище ракетных войск | Генератор псевдослучайных последовательностей |

| EP1164696A1 (en) * | 1999-12-24 | 2001-12-19 | Anritsu Corporation | Wonder generator, digital line tester comprising the same, and phase noise transfer characteristic analyzer |

| EP1330031A1 (en) * | 2002-01-21 | 2003-07-23 | Mitsubishi Electric Information Technology Centre Europe B.V. | Generation of a sequence of pulse trains |

-

2007

- 2007-11-01 RU RU2007140610/09A patent/RU2355103C1/ru not_active IP Right Cessation

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SU1750033A2 (ru) * | 1990-06-11 | 1992-07-23 | Военный Инженерный Краснознаменный Институт Им.А.Ф.Можайского | Генератор псевдослучайных последовательностей |

| SU1758851A2 (ru) * | 1990-08-10 | 1992-08-30 | Ростовское высшее военное командно-инженерное училище ракетных войск | Генератор псевдослучайных последовательностей |

| EP1164696A1 (en) * | 1999-12-24 | 2001-12-19 | Anritsu Corporation | Wonder generator, digital line tester comprising the same, and phase noise transfer characteristic analyzer |

| EP1330031A1 (en) * | 2002-01-21 | 2003-07-23 | Mitsubishi Electric Information Technology Centre Europe B.V. | Generation of a sequence of pulse trains |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2419224C1 (ru) * | 2009-12-08 | 2011-05-20 | Открытое акционерное общество "Концерн "Созвездие" | Формирователь м-последовательностей |

| RU2634233C1 (ru) * | 2017-01-12 | 2017-10-24 | Борис Иванович Крыжановский | Способ генерации псевдослучайной двоичной последовательности |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9092067B2 (en) | Phase disciplined, direct digital synthesizer based, coherent signal generator | |

| WO2018146633A1 (en) | Programmable code generation for radar sensing systems | |

| US9047152B2 (en) | Delay device, method, and random number generator using the same | |

| EP0905611A2 (en) | Pseudorandom number generating method and pseudorandom number generator | |

| Furuya et al. | Two-Pattern Test Capabilities of Autonomous TGP Circuits | |

| CN110231599A (zh) | 雷达设备、雷达系统和用于生成采样时钟信号的方法 | |

| RU2355103C1 (ru) | Генератор псевдослучайной последовательности | |

| US6177891B1 (en) | Serial-parallel conversion apparatus | |

| US3735270A (en) | Delayed pulse generator | |

| KR970029796A (ko) | 구동시간 마진이 증가된 동기식 반도체 회로 | |

| US7933310B2 (en) | System for a fast frequency hopping radio | |

| US7868679B2 (en) | Circuit, method for receiving a signal, and use of a random event generator | |

| Lukin et al. | FPGA based random waveform generators for noise radars | |

| JP2003304136A (ja) | 無限位相器 | |

| US7586348B2 (en) | Systems, apparatuses and methods for synchronizing clock signals | |

| RU92270U1 (ru) | Генератор псевдослучайных бинарных последовательностей | |

| Ying et al. | Design of BDS/GPS C/A Code Generator | |

| RU2586006C1 (ru) | Цифровой синтезатор шумовых сигналов | |

| RU2427886C2 (ru) | Генератор псевдослучайных бинарных последовательностей | |

| RU2618941C2 (ru) | Коррелятор | |

| KR100617957B1 (ko) | 역방향 데이터 샘플링 방법 및 이를 이용한 역방향 데이터샘플링 회로 | |

| JPH03251890A (ja) | 非線形フィードバック・シフトレジスタ装置 | |

| EP1215835B1 (en) | Synchronous acquisition device for cdma receiver | |

| RU2119245C1 (ru) | Реле времени | |

| WO2000039667A1 (en) | Code generator |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| MM4A | The patent is invalid due to non-payment of fees |

Effective date: 20091102 |