RU2012028C1 - Электронный таймер-задатчик ритма - Google Patents

Электронный таймер-задатчик ритма Download PDFInfo

- Publication number

- RU2012028C1 RU2012028C1 SU5027130A RU2012028C1 RU 2012028 C1 RU2012028 C1 RU 2012028C1 SU 5027130 A SU5027130 A SU 5027130A RU 2012028 C1 RU2012028 C1 RU 2012028C1

- Authority

- RU

- Russia

- Prior art keywords

- input

- output

- driver

- control signals

- pulse shaper

- Prior art date

Links

Images

Landscapes

- Control Of Linear Motors (AREA)

Abstract

Использование: изобретение относится к электронным приборам времени в системах автоматического управления с асинхронной связью с исполнительным механизмом и может быть использовано, например, в сборочном производстве для выдачи через определенный измеряемый интервал времени, т. е. задания ритма, сигналов управления на циклически работающие средства, например конвейеры, перемещающие изделия от одной технологической операции к другой. Сущность изобретения: электронный таймер содержит две памяти, два считывающих устройства, два счетчика, три формирователя управляющих сигналов, три формирователя импульсов, блок индикации, блок сигнализации, масштабный делитель, блок установок, три схемы сравнения, блок питания, задающий генератор, четыре триггера, инвертор, элемент И, три элемента И - НЕ, два элемента ИЛИ - НЕ, пять переключателей и шесть резисторов. 4 ил.

Description

Изобретение относится к электронным приборам времени в системах автоматического управления с замкнутой (асинхронной) связью с исполнительным механизмом и может быть использовано, в частности, в сборочном производстве для формирования и выдачи циклически повторяющихся по ответным сигналам с исполнительного механизма через определенный изменяемый период времени, т. е. задания ритма, сигналов управления на циклически работающие средства, например конвейеры, перемещающие изделия от одной технологической операции к другой.

Известен таймер, содержащий память для запоминания нескольких временных интервалов и схему, считывающую содержимое памяти и обеспечивающую периодическое повторение срабатывания таймера, генератор, формирующий звуки оповещения времени, счетчик числа циклов работы таймера, непрерывной в течение указанных нескольких временных интервалов, индикатор, отображающий число этих циклов [1] .

Известен таймер, содержащий память для запоминания заданного интервала времени, считывающее устройство, счетчик, начинающий подсчет импульсов с задающего генератора при воздействии на ключ, индикатор содержимого счетчика, формирователь, срабатывающий, когда содержимое счетчика станет равным интервалу времени, запомненному в памяти, схему, после возвращения счетчика в начальное состояние по сигналу формирователя обеспечивающую повторный подсчет времени и выдачу сигналов на исполнительный механизм, счетчик выходных сигналов формирователя, индикатор содержимого счетчика, ключи для управления работой таймера [2] .

Недостатком известных устройств являются ограниченные функциональные возможности, которые не обеспечивают циклического повторения срабатывания таймера с выдачей сигнала управления на исполнительный механизм, не имеют устройства управления исполнительным механизмом, не имеют индикатора, индицирующего оставшийся промежуток времени заданного интервала [1] , не обеспечивают автоматический циклически повторяющейся по ответным сигналам с исполнительного механизма выдачи сигналов управления, стабильности временных интервалов, кроме первого, при воздействии на ключи, предупредительной сигнализации перед окончанием заданного интервала времени, сброса всех счетчиков перед началом очередного интервала, индикации истекшего промежутка времени заданного интервала, не исключают ложного срабатывания таймера при подаче напряжения питания, не обеспечивают изменения числа срабатываний исполнительного механизма в одном периоде ритма [2] .

Наиболее близким техническим решением к предлагаемому, выбранному в качестве прототипа, является электронный таймер-задатчик ритма [3] , содержащий блок считывания, память, первый, второй и третий счетчики, блок индикации, блок сигнализации, первый, второй, третий, четвертый и пятый формирователи управляющих сигналов, первый, второй, третий, четвертый и пятый элементы И, первый, второй, третий и четвертый элементы ИЛИ, задающий генератор, источник питания, первый, второй и третий формирователи импульсов, первый и второй триггеры, первый, второй и третий переключатели, первый и второй элементы НЕ, панорамное табло, дешифратор, масштабный делитель.

Недостатком известного таймера является сложность и ограниченные функциональные возможности, которые не обеспечивают возможности изменения числа срабатываний исполнительного механизма и времени начала выдачи предупредительной звуковой сигнализации перед окончанием заданного интервала времени, сбоев при изменении значений периода ритма и высокой надежности работы таймера.

Сущность изобретения заключается в том, что в таймер, содержащий первую память, последовательно соединенную с первым считывающим устройством, первым счетчиком, первым формирователем управляющих сигналов и блоком индикации, масштабный делитель, сбросовый вход и первый выход которого соединены соответственно с вторым и третьим входами первого счетчика, последовательно соединенный с вторым формирователем управляющих сигналов и блоком сигнализации, блок питания, соединенный первым выходом с задающим генератором, а выходами питания и общим соответственно с первым и вторым входами первого формирователя импульсов, третий формирователь управляющих сигналов, соединенный выходом с входом "Пуск" исполнительного механизма, выход "Стоп" которого соединен с первым входом второго формирователя импульсов, второй счетчик, первый и второй триггеры, третий формирователь импульсов, элемент И, инвертор, первый, второй и третий резисторы, первые выводы которых соединены вместе, а вторые - с первыми выводами первого, второго и третьего переключателей соответственно, вторые выводы которых соединены между собой, дополнительно введены блок установок, первая, вторая и третья схемы сравнения, первый, второй и третий элемент И-НЕ, первый и второй элементы ИЛИ-НЕ, третий и четвертый триггеры, четвертый, пятый и шестой резисторы, четвертый и пятый переключатели, второе считывающее устройство и

вторая память, выход которой соединен с входом второго считывающего устройства, выход которого соединен с первым входом второго счетчика, второй вход которого соединен с выходом второго формирователя импульсов, третий вход - с выходом третьего формирователя импульсов и сбросовым входом масштабного делителя, первый выход - с вторым входом первого формирователя управляющих сигналов, а второй выход - с первым входом первого элемента ИЛИ-НЕ и первым входом элемента И, второй вход которого соединен через инвертор с первым выводом третьего переключателя, а выход - с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с вторым входом первого элемента ИЛИ-НЕ и выходом первого формирователя импульсов, третий вход - с третьим входом первого элемента ИЛИ-НЕ и выходом третьего триггера, а выход - со сбросовым входом первого триггера, выход которого соединен с первым входом первого элемента И-НЕ и первым входом второго элемента И-НЕ, стробирующий вход - с вторым входом второго элемента И-НЕ и выходом третьего элемента И-НЕ, а информационный вход - с вторым входом второго формирователя управляющих сигналов и выходом первой схемы сравнения, первый вход которой соединен с выходом первого считывающего устройства, а второй вход - с первым выходом блока уставок, второй выход которого соединен

с первым входом второй схемы сравнения, а третий выход - с первым входом третьей схемы сравнения, выход которой соединен с третьим входом второго формирователя управляющих сигналов, а второй вход - с выходом первого счетчика и вторым входом второй схемы сравнения, выход которой соединен с информационным входом второго триггера, сбросовый вход которого соединен с входом третьего формирователя импульсов и выходом первого элемента ИЛИ-НЕ, выход - с вторым входом второго формирователя импульсов и вторым входом первого элемента И-НЕ, а стробирующий вход - с вторым выходом масштабного делителя, третий выход которого соединен с третьим входом первого формирователя управляющих сигналов, а инкрементный вход - с выходом второго элемента И-НЕ, третий вход которого соединен с выходом задающего генератора и третьим входом второго формирователя импульсов, четвертый вход - с четвертым входом первого формиpователя управляющих сигналов, выходом первого элемента И-НЕ и первым входом третьего формирователя управляющих сигналов, пятый вход - с пятым входом первого формирователя управляющих сигналов, первым выводом четвертого резистора, первыми выводами четвертого и пятого переключателей и третьим входом первого элемента И-НЕ, а шестой вход - с четвертым входом первого элемента И-НЕ, шестым входом

первого формирователя управляющих сигналов, выходом готовности исполнительного механизма и первым входом третьего элемента И-НЕ, второй вход которого соединен с четвертым входом первого элемента ИЛИ-НЕ и выходом четвертого триггера, установочный вход которого соединен с первым выводом первого переключателя, а сбросовый вход - с третьим выводом первого переключателя и первым выводом пятого резистора, второй вывод которого соединен с выходом питания блока питания, первым выводом первого резистора, вторым выводом четвертого резистора и первым выводом шестого резистора, второй вывод которого соединен с третьим выводом второго переключателя и сбросовым входом третьего триггера, установочный вход которого соединен с первым выводом второго переключателя, второй вывод которого соединен с вторым выводом четвертого переключателя и общим выходом блока питания, четвертый выход которого соединен с вторым входом третьего формирователя управляющих сигналов, пятый выход - с вторым входом блока индикации, а шестой выход - с четвертым входом второго формирователя управляющих сигналов, пятый вход которого соединен с вторым выводом пятого переключателя.

вторая память, выход которой соединен с входом второго считывающего устройства, выход которого соединен с первым входом второго счетчика, второй вход которого соединен с выходом второго формирователя импульсов, третий вход - с выходом третьего формирователя импульсов и сбросовым входом масштабного делителя, первый выход - с вторым входом первого формирователя управляющих сигналов, а второй выход - с первым входом первого элемента ИЛИ-НЕ и первым входом элемента И, второй вход которого соединен через инвертор с первым выводом третьего переключателя, а выход - с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с вторым входом первого элемента ИЛИ-НЕ и выходом первого формирователя импульсов, третий вход - с третьим входом первого элемента ИЛИ-НЕ и выходом третьего триггера, а выход - со сбросовым входом первого триггера, выход которого соединен с первым входом первого элемента И-НЕ и первым входом второго элемента И-НЕ, стробирующий вход - с вторым входом второго элемента И-НЕ и выходом третьего элемента И-НЕ, а информационный вход - с вторым входом второго формирователя управляющих сигналов и выходом первой схемы сравнения, первый вход которой соединен с выходом первого считывающего устройства, а второй вход - с первым выходом блока уставок, второй выход которого соединен

с первым входом второй схемы сравнения, а третий выход - с первым входом третьей схемы сравнения, выход которой соединен с третьим входом второго формирователя управляющих сигналов, а второй вход - с выходом первого счетчика и вторым входом второй схемы сравнения, выход которой соединен с информационным входом второго триггера, сбросовый вход которого соединен с входом третьего формирователя импульсов и выходом первого элемента ИЛИ-НЕ, выход - с вторым входом второго формирователя импульсов и вторым входом первого элемента И-НЕ, а стробирующий вход - с вторым выходом масштабного делителя, третий выход которого соединен с третьим входом первого формирователя управляющих сигналов, а инкрементный вход - с выходом второго элемента И-НЕ, третий вход которого соединен с выходом задающего генератора и третьим входом второго формирователя импульсов, четвертый вход - с четвертым входом первого формиpователя управляющих сигналов, выходом первого элемента И-НЕ и первым входом третьего формирователя управляющих сигналов, пятый вход - с пятым входом первого формирователя управляющих сигналов, первым выводом четвертого резистора, первыми выводами четвертого и пятого переключателей и третьим входом первого элемента И-НЕ, а шестой вход - с четвертым входом первого элемента И-НЕ, шестым входом

первого формирователя управляющих сигналов, выходом готовности исполнительного механизма и первым входом третьего элемента И-НЕ, второй вход которого соединен с четвертым входом первого элемента ИЛИ-НЕ и выходом четвертого триггера, установочный вход которого соединен с первым выводом первого переключателя, а сбросовый вход - с третьим выводом первого переключателя и первым выводом пятого резистора, второй вывод которого соединен с выходом питания блока питания, первым выводом первого резистора, вторым выводом четвертого резистора и первым выводом шестого резистора, второй вывод которого соединен с третьим выводом второго переключателя и сбросовым входом третьего триггера, установочный вход которого соединен с первым выводом второго переключателя, второй вывод которого соединен с вторым выводом четвертого переключателя и общим выходом блока питания, четвертый выход которого соединен с вторым входом третьего формирователя управляющих сигналов, пятый выход - с вторым входом блока индикации, а шестой выход - с четвертым входом второго формирователя управляющих сигналов, пятый вход которого соединен с вторым выводом пятого переключателя.

Сопоставительный анализ известных технических решений показал, что эти решения обеспечивают только периодическое формирование и выдачу сигналов управления на исполнительный механизм либо независимо от его работы, либо по его сигналам ответа, выдачу сигналов предупреждения за определенный промежуток времени перед окончание периода ритма.

Предлагаемое техническое решение обеспечивает формирование и выдачу циклически повторяющихся через определенный при необходимости - изменяемый в процессе работы период времени ритма сигналов управления на связанный замкнутой (асинхронной) связью исполнительный механизм, включение предупредительной сигнализации за определенный устанавливаемый перед началом работы интервал времени перед окончанием периода ритма, возможность устанавливать перед началом работы определенное число срабатываний (т. е. количество шагов или количество повторений цикла работы) исполнительного механизма в одном периоде ритма, дополнительный режим работы исполнительного механизма, обеспечивающий приостановление работы предлагаемого устройства с сохранением своего состояния всеми его элементами за счет введения блока уставок, схем сравнения, второй памяти и второго считывающего устройства, четвертого и пятого переключателей и других элементов и за счет изменения связей схемы устройства, а также исключения сбоев времени периода ритма при изменении его значений за счет изменения режима работы и связей первого счетчика, повышения надежности за счет исключения части элементов и изменения связей схемы устройства.

В известных технических решениях признаки, отличные от прототипа, не обнаружены, что позволяет сделать вывод, что предлагаемое устройство обладает существенными отличиями.

Совокупность существенных признаков предлагаемого устройства при их выполнении обеспечит достижение положительного эффекта - расширения функциональных возможностей, повышения надежности и возможности изменения числа срабатываний в одном периоде ритма исполнительным механизмом, например конвейерной линией, обеспечит возможность изменения расстояния или шага, кратного определенному эталонному расстоянию между рабочими местами на различных конвейерных линиях при сохранении единой конструкции транспортера.

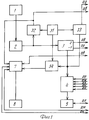

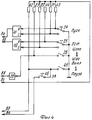

На фиг. 1-4 изображен один из возможных вариантов предложенного электронного таймера - задатчика ритма.

Электронный таймер-задатчик ритма содержит первую память 1, последовательно соединенную с первым считывающим устройством 2, первым счетчиком 3, первым формирователем 4 управляющих сигналов и блоком 5 индикации, масштабный делитель 6, сбросовый вход и первый выход которого соединены соответственно с вторым и третьим входами первого счетчика 3, последовательно соединенный с вторым формирователем 7 управляющих сигналов и блоком 8 сигнализации, блок 9 питания, соединенный первым выходом с задающим генератором 10, а выходами питания и общим - соответственно с первыми вторым входами первого формирователя 11 импульсов, третий формирователь 12 управляющих сигналов, соединенный выходом с входом "Пуск" исполнительного механизма 13, выполненного, например, в виде конвейерной линии, выход "Стоп" которого соединен с первым входом второго формирователя 14 импульсов, второй счетчик 15, первый и второй триггеры 16 и 17, третий формирователь 18 импульсов, элемент И 19, инвертор 20, первый, второй и третий резисторы 21, 22 и 23, первые выводы которых соединены вместе, а вторые - с первыми выводами первого, второго и третьего переключателей 24, 25 и 26 соответственно, вторые выводы которых соединены между собой.

При этом первый формирователь 11 импульсов состоит из инвертора 27 и соединенных с его входом первыми выводами резистора 28, диода 29 и конденсатора 30, подключенного вторым выводом к общему выходу блока 9 питания, выход питания которого подключен к вторым выводам резистора 28 и диода 29.

Электронный таймер-задатчик ритма содержит также блок 31 уставок, первую, вторую и третью схемы сравнения 32, 33 и 34, первый, второй и третий элементы И-НЕ 35-37, первый и второй элементы ИЛИ-НЕ 38 и 39, третий и четвертый триггеры 40 и 41, четвертый, пятый и шестой резисторы 42-44, четвертый и пятый переключатели 45 и 46, второе считывающее устройство 47 и вторую память 48, выход которой соединен с входом второго считывающего устройства 47, выход которого соединен с первым входом второго счетчика 15. второй вход которого соединен с выходом второго формирователя 14 импульсов, третий вход - с выходом третьего формирователя 18 импульсов и сбросовым входом масштабного делителя 6, первый вход - с вторым входом первого формирователя 4 управляющих сигналов, а второй выход - с первым входом первого элемента ИЛИ-НЕ 38 и первым входом элемента И 19, второй вход которого соединен через инвертор 20 с первым выводом третьего переключателя 26, а выход - с первым входом второго элемента ИЛИ-НЕ 39, второй вход которого соединен с вторым входом первого элемента ИЛИ-НЕ 38 и выходом первого формирователя 11 импульсов, третий вход - с третьим входом первого элемента ИЛИ-НЕ 38 и выходом третьего триггера 40, а выход - со сбросовым входом первого триггера 16, выход которого соединен с первым входом первого элемента И-НЕ 35 и первым входом второго элемента И-НЕ 36, стробирующий вход - с

вторым входом второго элемента И-НЕ 36 и выходом третьего элемента И-НЕ 37, а информационный вход - с вторым входом второго формирователя 7 управляющих сигналов и выходом первой схемы 32 сравнения, первый вход которой соединен с выходом первого считывающего устройства 2, а второй вход - с первым выходом блока 31 уставок, второй выход которого соединен с первым входом второй схемы 33 сравнения, а третий выход - с первым входом третьей схемы 34 сравнения, выход которой соединен с третьим входом второго формирователя 7 управляющих сигналов, а второй вход - с выходом первого счетчика 3 и вторым входом второй схемы 33 сравнения, выход которой соединен с информационным входом второго триггера 17, сбросовый вход которого соединен с входом третьего формирователя 18 импульсов и выходом первого элемента ИЛИ-НЕ 38, выход - с вторым входом второго формирователя 14 импульсов и вторым входом первого элемента И-НЕ 35, а стробирующий вход - с вторым выходом масштабного делителя 6, третий выход которого соединен с третьим входом первого формирователя 4 управляющих сигналов, а инкрементный вход - с выходом второго элемента И-НЕ 36, третий вход которого соединен с выходом задающего генератора 10 и третьим входом второго формирователя 14 импульсов, четвертый вход - с четвертым входом первого формирователя 4 управляющих

сигналов, выходом первого элемента И-НЕ 35 и первым входом третьего формирователя 12 управляющих сигналов, пятый вход - с пятым входом первого формирователя 4 управляющих сигналов, первым выводом четвертого резистора 42, первыми выводами четвертого и пятого переключателей 45 и 46 и третьим входом первого элемента И-НЕ 35, а шестой вход - с четвертым входом пеpвого элемента И-НЕ 35, шестым входом первого формирователя 4 управляющих сигналов, выходом готовности исполнительного механизма 13 и первым входом третьего элемента И-НЕ 37, второй вход которого соединен с четвертым входом первого элемента ИЛИ-НЕ 38 и выходом четвертого триггера 41, установочный вход которого соединен с первым выводом первого переключателя 24, а сбросовый вход - с третьим выводом первого переключателя 24 и первым выводом пятого резистора 43, второй вывод которого соединен с выходом питания блока 9 питания, первым выводом первого резистора 21, вторым выводом четвертого резистора 42 и первым выводом шестого резистора 44, второй вывод которого соединен с третьим выводом второго переключателя 25 и сбросовым входом четвертого триггера 41, установочный вход которого соединен с первым выводом второго переключателя 25, второй вывод которого соединен с вторым выводом четвертого переключателя 45 и общим выходом блока 9 питания,

четвертый выход которого соединен с вторым входом третьего формирователя 12 управляющих сигналов, пятый выход - с вторым входом блока 5 индикации, а шестой выход - с четвертым входом второго формирователя 7 управляющих сигналов, пятый вход которого соединен с вторым выводом пятого переключателя 46.

вторым входом второго элемента И-НЕ 36 и выходом третьего элемента И-НЕ 37, а информационный вход - с вторым входом второго формирователя 7 управляющих сигналов и выходом первой схемы 32 сравнения, первый вход которой соединен с выходом первого считывающего устройства 2, а второй вход - с первым выходом блока 31 уставок, второй выход которого соединен с первым входом второй схемы 33 сравнения, а третий выход - с первым входом третьей схемы 34 сравнения, выход которой соединен с третьим входом второго формирователя 7 управляющих сигналов, а второй вход - с выходом первого счетчика 3 и вторым входом второй схемы 33 сравнения, выход которой соединен с информационным входом второго триггера 17, сбросовый вход которого соединен с входом третьего формирователя 18 импульсов и выходом первого элемента ИЛИ-НЕ 38, выход - с вторым входом второго формирователя 14 импульсов и вторым входом первого элемента И-НЕ 35, а стробирующий вход - с вторым выходом масштабного делителя 6, третий выход которого соединен с третьим входом первого формирователя 4 управляющих сигналов, а инкрементный вход - с выходом второго элемента И-НЕ 36, третий вход которого соединен с выходом задающего генератора 10 и третьим входом второго формирователя 14 импульсов, четвертый вход - с четвертым входом первого формирователя 4 управляющих

сигналов, выходом первого элемента И-НЕ 35 и первым входом третьего формирователя 12 управляющих сигналов, пятый вход - с пятым входом первого формирователя 4 управляющих сигналов, первым выводом четвертого резистора 42, первыми выводами четвертого и пятого переключателей 45 и 46 и третьим входом первого элемента И-НЕ 35, а шестой вход - с четвертым входом пеpвого элемента И-НЕ 35, шестым входом первого формирователя 4 управляющих сигналов, выходом готовности исполнительного механизма 13 и первым входом третьего элемента И-НЕ 37, второй вход которого соединен с четвертым входом первого элемента ИЛИ-НЕ 38 и выходом четвертого триггера 41, установочный вход которого соединен с первым выводом первого переключателя 24, а сбросовый вход - с третьим выводом первого переключателя 24 и первым выводом пятого резистора 43, второй вывод которого соединен с выходом питания блока 9 питания, первым выводом первого резистора 21, вторым выводом четвертого резистора 42 и первым выводом шестого резистора 44, второй вывод которого соединен с третьим выводом второго переключателя 25 и сбросовым входом четвертого триггера 41, установочный вход которого соединен с первым выводом второго переключателя 25, второй вывод которого соединен с вторым выводом четвертого переключателя 45 и общим выходом блока 9 питания,

четвертый выход которого соединен с вторым входом третьего формирователя 12 управляющих сигналов, пятый выход - с вторым входом блока 5 индикации, а шестой выход - с четвертым входом второго формирователя 7 управляющих сигналов, пятый вход которого соединен с вторым выводом пятого переключателя 46.

Первый, второй и третий формирователи 4, 7 и 12 управляющих сигналов выполнены в виде соответственно блока управления индикацией, блока управления предупредительной сигнализации и блока управления исполнительным механизмом.

Второй и третий формирователи 14 и 18 импульсов выполнены в виде соответственно формирователя выделения одиночного импульса из непрерывной последовательности импульсов и формирователя одиночного короткого импульса.

Блок 31 уставок выполнен в виде блока формиpования констант для первой, второй и третьей схем сравнения 32, 33 и 34.

Работа предложенного электронного таймера-задатчика ритма происходит следующим образом.

Рассмотрим вариант, при котором устройство используется в качестве пульта управления исполнительным механизмом, например транспортером конвейерной линии, обладающей следующими параметрами:

период ритма, с - от 1 до 999;

изменение числа повторных срабатываний (шагов) исполнительного механизма за один период ритма, раз - от 0 до 3;

запрет запуска устройства при периоде ритма, с - 3

выдача сигналов предупредительной сигнализации перед окончанием периода ритма, с 3

выдача сигнала разрешения для прохождения команды "Пуск" на исполнительный механизм перед окончанием периода ритма, с - 1, для чего в первую и вторую памяти 1 и 48 занесены двоично-десятичные коды констант соответственно от 000 до 999 и от 0 до 3, а в блок 31 уставок занесены двоичные коды констант 3, 1 и 4 соответственно для первой, второй и третьей схем 31-34 сравнения.

период ритма, с - от 1 до 999;

изменение числа повторных срабатываний (шагов) исполнительного механизма за один период ритма, раз - от 0 до 3;

запрет запуска устройства при периоде ритма, с - 3

выдача сигналов предупредительной сигнализации перед окончанием периода ритма, с 3

выдача сигнала разрешения для прохождения команды "Пуск" на исполнительный механизм перед окончанием периода ритма, с - 1, для чего в первую и вторую памяти 1 и 48 занесены двоично-десятичные коды констант соответственно от 000 до 999 и от 0 до 3, а в блок 31 уставок занесены двоичные коды констант 3, 1 и 4 соответственно для первой, второй и третьей схем 31-34 сравнения.

Период опорной частоты с выхода задающего генератора 10 равен периоду удвоенной частоты синхронизации блока 9 питания, подключенного к сети переменного тока частоты 50 Гц, точностные характеристики которой высокие и достаточны для таймеров такого класса, и равен 0,01 с. Режим работы, выбираемый третьим переключателем 26, - циклический. Период тактовой частоты с первого выхода масштабного делителя 6 выбран равным дискрету установки периода ритма, т. е. 1 с. Коэффициенты счета первого и второго счетчиков 3 и 15 равны соответственно 999 и 4. Первое и второе считывающие устройства 2 и 47 позволяют оператору выбрать любое значение соответственно периоду ритма, т. е. считать из первой памяти 1 любой из кодов с дискретом 1 и числа срабатываний исполнительным механизмом 13, т. е. считать из второй памяти 48 любой из кодов с дискретом 1. Период частоты модуляции с второго выхода масштабного делителя 6 выбираем из условия, что предупредительная сигнализация должна включаться за 3 с (уставка для третьей схемы 34 сравнения) до окончании периода ритма, а в течение этого интервала времени, например, должно выдаваться два сигнала в течение 3 и 1 с, с интервалом между ними в 1 с, до окончания периода ритма. Таким образом частоту модуляции целесообразно выбрать равной также 1 Гц и синхронной с тактовой частотой. Минимальное значение периода ритма выбираем равным 4 с (уставка для первой схемы 32 сравнения равна 3).

При включении питания таймера блок 9 питания выдает все необходимые напряжения на все элементы схемы, а задающий генератор 10, построенный по принципу синхронизированного формирователя коротких импульсов, запускается и начинает генерировать короткие импульсы с периодом, равным 0,01 с. При появлении напряжения на выходе питания блока 9 питания и соответственно на первом входе первого формирователя 11 импульсов на выходе инвертора 27 этого формирователя удерживается, пока уровень напряжения на заряжающемся через резистор 26 конденсаторе 30 не превысит порог срабатывания инвертора 27, сигнал сброса по питанию, который через первый и второй элементы ИЛИ-НЕ 38 и 39 устанавливает таймер в исходное состояние, при котором первый и второй триггеры 16 и 17 сброшены, на выходе третьего формирователя 18 импульсов появляется импульс, который сбрасывает масштабный делитель 6, а в первый и второй счетчики 3 и 15 запитывает исходное число, равное кодам, считанным соответственно через первые считывающее устройство 2 из первой памяти 1 и через второе считывающее устройство 47 - из второй памяти 48, инкрементный вход масштабного делителя 6, четвертый вход первого формирователя 4 управляющих сигналов и первый вход третьего формирователя 12 управляющих сигналов закрыты первым и вторым элементами И-НЕ 35 и 36, на один из выходов которых приходит

запрещающий уровень сигнала с выхода первого триггера 16, индикаторы блока 5 индикации отображают состояние блока 9 питания, а через первый формирователь 4 управляющих сигналов - состояние первого и второго счетчиков 3 и 15, масштабного делителя 6 и исполнительного механизма 13, блок 8 сигнализации выключен. Индикация состояния первого счетчика 3 дополнительно отображает время, оставшееся до окончания периода ритма, а индикация состояния второго счетчика 15 - оставшееся число повторных срабатываний исполнительного механизма 13. Диод 29 первого формирователя 11 импульсов служит для ускоренного разряда конденсатора 30 при выключении питания таймера.

запрещающий уровень сигнала с выхода первого триггера 16, индикаторы блока 5 индикации отображают состояние блока 9 питания, а через первый формирователь 4 управляющих сигналов - состояние первого и второго счетчиков 3 и 15, масштабного делителя 6 и исполнительного механизма 13, блок 8 сигнализации выключен. Индикация состояния первого счетчика 3 дополнительно отображает время, оставшееся до окончания периода ритма, а индикация состояния второго счетчика 15 - оставшееся число повторных срабатываний исполнительного механизма 13. Диод 29 первого формирователя 11 импульсов служит для ускоренного разряда конденсатора 30 при выключении питания таймера.

С помощью первого считывающего устройства 2 оператор выбирает из первой памяти 1 код, соответствующий требуемому значению периода ритма, например, равного 10 с, который постоянной контролируется первой схемой 32 сравнения и в случае, если этот код меньше минимального значения периода ритма (т. е. меньше или равен константе в блоке 31 уставок), ее выходной сигнал блокирует информационный вход (вход установки в единичное состояние) первого триггера 16 и второй формирователь 7 управляющих сигналов, а с помощью второго считывающего устройства 47 - из второй памяти 48 код, соответствующий требуемому значению числа повторных срабатываний исполнительного механизма 13, например 1. При этом коды этих значений подаются соответственно на первые входы первого и второго счетчиков 3 и 15. Оператор устанавливает также третий и четвертый переключатели 26 и 45 в положение соответственно "Цикл" и "Выкл. ", нажимает и отпускает первый переключатель 24, выполняющий функцию кнопки пуска. При этом сигнал пуска с выхода четвертого триггера 41, выполняющего функцию антидребезгового, через первый элемент ИЛИ-НЕ 38 повторно сбрасывает второй триггер 17 и запускает третий формиpователь 18 импульсов, сигнал с выхода которого сбрасывает масштабный делитель 6, а в первый и второй счетчики 3 и 15 записывает коды, находящиеся на первых их входах. Коды, записанные в первый и

второй счетчики 3 и 15 с помощью первого формирователя 4 управляющих сигналов, отображаются индикаторами блока 5 индикации. Кроме того, сигнал пуска с выхода четвертого триггера 41 через третий элемент И-НЕ 37 при наличии на его первом входе сигнала готовности с исполнительного механизма 13 устанавливает в единичное состояние первый триггер 16, так как установленное значение периода ритма больше его минимального значения и на выходе первой схемы 32 сравнения и, следовательно, информационном входе первого триггера 16 единичный уровень и блокирует инкрементный вход масштабного делителя 6 через второй элемент И-НЕ 36 до окончания этого сигнала. После отпускания первого переключателя 24 разрешающий уровень сигнала пуска с выхода четвертого триггера 41 снимается и появляется запрещающий уровень, который закрывает первый элемент ИЛИ-НЕ 38 и третий элемент И-НЕ 37, разрешающий уровень сигнала, с выхода которого снимает блокировку с первого входа второго элемента И-НЕ 36. Запрещающий уровень сигнала с выхода второго триггера 17 блокирует второй формирователь 14 импульсов и первый элемент И-НЕ 35, выходной сигнал которого имеет запрещающий уровень для третьего формирователя 12 управляющих сигналов и разрешающий уровень для второго элемента И-НЕ 36. Импульсы с выхода задающего генератора 10 через открытый второй элемент И-НЕ 36 начинают

поступать на инкрементный вход масштабного делителя 6, который преобразует импульсы опорной частоты с периодом 0,01 с в тактовую частоту таймера с периодом 1 с и в частоту модуляции с периодом, также равным 1 с. Контроль работы масштабного делителя 6 по сигналу (меандр) с его третьего выхода через первый формирователь 4 управляющих сигналов осуществляется по индикатору в блоке 5 индикации. С второго выхода масштабного делителя 6 импульсы модуляции поступают на второй формирователь 7 управляющих сигналов, блокированный запрещающий уровнем сигнала с выхода третьей схемы 34 сравнения, и на стробирующий вход второго триггера 17, блокированного по информационному входу запрещающим уровнем сигнала с выхода второй схемы 33 сравнения. Тактовый импульсы с первого выхода масштабного делителя 6 поступают на декрементный вход первого счетчика 3, который начинает уменьшать свое состояние на единицу с приходом каждого импульса. Изменение состояния первого счетчика 3 отображается на блоке 4 индикации и постоянно контролируется второй и третьей схемами 33 и 34 сравнения. При достижении первым счетчиком 3 состояния 004 на выходе третьей схемы 34 сравнения появляется сигнал, разрешающий уровень которого открывает второй формирователь 7 управляющих сигналов и удерживает его в этом состоянии до окончания периода ритма, т. е. до достижения первым счетчиком 3 состояния 000. С

приходом очередного тактового импульса первый счетчик 3 переходит в состояние 003, а по очередному импульсу модуляции, синхронного с тактовым, на выходе второго формирователя 7 управляющих сигналов появляется сигнал, разрешающий уровень которого включает предупредительную сигнализацию блока 8 сигнализации и удерживает ее до следующего импульса модуляции. По следующему тактовому импульсу первый счетчик 3 переходит в состояние 002, а по импульсу модуляции с выхода второго формирователя 7 управляющих сигналов снимается сигнал и блок 8 сигнализации выключается. Следующий тактовый импульс переводит первый счетчик 3 в состояние 001, а импульс модуляции вновь обеспечивает появление сигнала на выходе второго формирователя 7 управляющих сигналов и включение блока 8 сигнализации и удерживает его в этом состоянии до окончания периода ритма. При достижении первым счетчиком 3 состояния 001 на выходе второй схемы 33 сравнения появляется сигнал, который поступает на информационный вход второго триггера 17 и подготавливает его для установки в единичное состояние.

второй счетчики 3 и 15 с помощью первого формирователя 4 управляющих сигналов, отображаются индикаторами блока 5 индикации. Кроме того, сигнал пуска с выхода четвертого триггера 41 через третий элемент И-НЕ 37 при наличии на его первом входе сигнала готовности с исполнительного механизма 13 устанавливает в единичное состояние первый триггер 16, так как установленное значение периода ритма больше его минимального значения и на выходе первой схемы 32 сравнения и, следовательно, информационном входе первого триггера 16 единичный уровень и блокирует инкрементный вход масштабного делителя 6 через второй элемент И-НЕ 36 до окончания этого сигнала. После отпускания первого переключателя 24 разрешающий уровень сигнала пуска с выхода четвертого триггера 41 снимается и появляется запрещающий уровень, который закрывает первый элемент ИЛИ-НЕ 38 и третий элемент И-НЕ 37, разрешающий уровень сигнала, с выхода которого снимает блокировку с первого входа второго элемента И-НЕ 36. Запрещающий уровень сигнала с выхода второго триггера 17 блокирует второй формирователь 14 импульсов и первый элемент И-НЕ 35, выходной сигнал которого имеет запрещающий уровень для третьего формирователя 12 управляющих сигналов и разрешающий уровень для второго элемента И-НЕ 36. Импульсы с выхода задающего генератора 10 через открытый второй элемент И-НЕ 36 начинают

поступать на инкрементный вход масштабного делителя 6, который преобразует импульсы опорной частоты с периодом 0,01 с в тактовую частоту таймера с периодом 1 с и в частоту модуляции с периодом, также равным 1 с. Контроль работы масштабного делителя 6 по сигналу (меандр) с его третьего выхода через первый формирователь 4 управляющих сигналов осуществляется по индикатору в блоке 5 индикации. С второго выхода масштабного делителя 6 импульсы модуляции поступают на второй формирователь 7 управляющих сигналов, блокированный запрещающий уровнем сигнала с выхода третьей схемы 34 сравнения, и на стробирующий вход второго триггера 17, блокированного по информационному входу запрещающим уровнем сигнала с выхода второй схемы 33 сравнения. Тактовый импульсы с первого выхода масштабного делителя 6 поступают на декрементный вход первого счетчика 3, который начинает уменьшать свое состояние на единицу с приходом каждого импульса. Изменение состояния первого счетчика 3 отображается на блоке 4 индикации и постоянно контролируется второй и третьей схемами 33 и 34 сравнения. При достижении первым счетчиком 3 состояния 004 на выходе третьей схемы 34 сравнения появляется сигнал, разрешающий уровень которого открывает второй формирователь 7 управляющих сигналов и удерживает его в этом состоянии до окончания периода ритма, т. е. до достижения первым счетчиком 3 состояния 000. С

приходом очередного тактового импульса первый счетчик 3 переходит в состояние 003, а по очередному импульсу модуляции, синхронного с тактовым, на выходе второго формирователя 7 управляющих сигналов появляется сигнал, разрешающий уровень которого включает предупредительную сигнализацию блока 8 сигнализации и удерживает ее до следующего импульса модуляции. По следующему тактовому импульсу первый счетчик 3 переходит в состояние 002, а по импульсу модуляции с выхода второго формирователя 7 управляющих сигналов снимается сигнал и блок 8 сигнализации выключается. Следующий тактовый импульс переводит первый счетчик 3 в состояние 001, а импульс модуляции вновь обеспечивает появление сигнала на выходе второго формирователя 7 управляющих сигналов и включение блока 8 сигнализации и удерживает его в этом состоянии до окончания периода ритма. При достижении первым счетчиком 3 состояния 001 на выходе второй схемы 33 сравнения появляется сигнал, который поступает на информационный вход второго триггера 17 и подготавливает его для установки в единичное состояние.

С приходом очередного тактового импульса первый счетчик 3 переходит в состояние 000, а по импульсу модуляции снимается сигнал с выхода второго формирователя 7 управляющих сигналов, т. е. выключается блок 8 сигнализации, и второй триггер 17 устанавливается в единичное состояние. Таким образом предупредительная сигнализация подается за три и одну секунду до окончания периода ритма, т. е. до начала движения транспортера конвейерной линии. Разрешающий уровень сигнала с выхода второго триггера 17 снимает блокировку с второго входа второго формирователя 14 импульсов и с второго входа первого элемента И-НЕ 35, сигнал с выхода которого блокирует по четвертому входу второй элемент И-НЕ 36, т. е. запрещает прохождение на инкрементный вход масштабного делителя 6 импульсов с выхода задающего генератора 10 и останавливает работу масштабного делителя 6 и первого счетчика 3, включают третий формирователь 12 управляющих сигналов и через первый формирователь 4 управляющих сигналов индикацию блока 5 индикации, свидетельствующую о подаче на исполнительный механизм 13 команды пуска.

Сигнал с выхода третьего формирователя 12 управляющих сигналов, выполняющий функцию команды пуска для исполнительного механизма 13, поступает на вход "Пуск" исполнительного механизма 13, включает его двигатель и транспортер конвейерной линии начинает движение и перемещает изделие от одного рабочего места к другому.

Транспортер конвейерной линии, пройдя заданное эталонное расстояние (т. е. выполнит одно срабатывание или сделает один шаг), определяемое конструкцией конвейерной линии, формирует на выходе "Стоп" исполнительного механизма 13 сигнал, который поступает на первый вход второго формирователя 14 импульсов и запускает его. Второй формиpователь 14 импульсов обеспечивает выделение одиночного импульса из опорной частоты, поступающей на его третий вход с выхода задающего генератора 10. Импульс с выхода второго формирователя 14 импульсов поступает на декрементный вход второго счетчика 15. Второй счетчик 15 в зависимости от предварительно записанного в него кода повторного числа срабатываний либо пропускает импульс на свой второй выход (при коде 0), либо уменьшает на 1 свое состояние (при коде 0) и ожидает прихода следующего импульса. В выбранном варианте код равен 1.

Состояние второго счетчика 15 с его первого выхода отображается с помощью первого формиpователя 4 управляющих сигналов блоком 5 индикации.

Транспортер конвейерной линии начинает выполнять первый повтор команды пуска, т. е. переходит на выполнение второго шага, и, пройдя вторично заданное эталонное расстояние, т. е. переместив изделие уже на два шага, вновь сформирует на выходе "Стоп" исполнительного механизма 13 сигнал, который запускает второй формирователь 14 импульсов и обеспечивает появление на его выходе одиночного импульса, который без задержки транслируется с декрементного входа на второй выход второго счетчика 15. Сигнал с второго выхода второго счетчика 15 через первый элемент ИЛИ-НЕ сбрасывает второй триггер 17 и через третий формирователь 18 импульсов обнуляет масштабный делитель 6 и вновь записывает коды установки периода ритма и числа срабатываний в первый и второй счетчики 3 и 15. Этот же сигнал с второго выхода второго счетчика 15 опрашивает элемент И 19, на второй вход которого поступает через инвертор 20 сигнал с третьего переключателя 26, выполняющего функцию переключателя выбора режима. При выбранном режиме "Цикл" сигнал на втором входе элемента И 19 блокирует прохождение импульса с второго выхода второго счетчика 15. Сигнал с выхода второго триггера 17 вновь блокирует второй формирователь 14 импульсов и первый элемент И-НЕ 35, выходной сигнал которого снимает команду пуска через третий формирователь 12 управляющих сигналов с входа "Пуск" исполнительного механизма 13, выключает соответствующий индикатор через первый формирователь 4

управляющих сигналов блока 5 индикации и снимает запрет с четвертого входа второго элемента И-НЕ 36 на прохождение импульсов опорной частоты с выхода задающего генератора 10 на инкрементный вход масштабного делителя 6, т. е. вновь повторяется алгоритм работы таймера без повторного нажатия первого переключателя 24. При шаговом режиме работы, т. е. третий переключатель 26 установлен в положение "Шаг" и на втором входе элемента И 19 разрешающий уровень сигнала, импульс с второго выхода второго счетчика 15 через элемент И 19 и второй элемент ИЛИ-НЕ 39 сбрасывает первый триггер 16, т. е. приводит таймер в исходное состояние.

управляющих сигналов блока 5 индикации и снимает запрет с четвертого входа второго элемента И-НЕ 36 на прохождение импульсов опорной частоты с выхода задающего генератора 10 на инкрементный вход масштабного делителя 6, т. е. вновь повторяется алгоритм работы таймера без повторного нажатия первого переключателя 24. При шаговом режиме работы, т. е. третий переключатель 26 установлен в положение "Шаг" и на втором входе элемента И 19 разрешающий уровень сигнала, импульс с второго выхода второго счетчика 15 через элемент И 19 и второй элемент ИЛИ-НЕ 39 сбрасывает первый триггер 16, т. е. приводит таймер в исходное состояние.

Для остановки работы таймера необходимо нажать и отпустить второй переключатель 25, выполняющий функцию кнопки останова, при этом третий триггер 40, являющийся антидребезговым, переходит в единичное состояние, сигнал с его выхода через первый и второй элементы ИЛИ-НЕ 38 и 39 сбрасывает второй и первый триггеры 17 и 16 и приводит таймер в исходное состояние.

Для кратковременного прерывания выполнения алгоритма работы таймера необходимо установить четвертый переключатель 45 в положение "Пауза", при котором запрещающий уровнем сигнала с этого переключателя блокируются первый и второй элементы И-НЕ 35 и 36, при этом снимается команда пуска с исполнительного механизма 13 и запрещается прохождение импульсов с задающего генератора 10 на инкрементный вход масштабного делителя 6, который вместе с первым счетчиком 3 останавливается, сохраняя свое состояние, а блок 5 индикации с помощью первого формирователя 4 управляющих сигналов индицирует состояние паузы.

При таком состоянии таймера возможно ручное, с помощью пятого переключателя 46, выполняющего функцию кнопки подачи предупредительной сигнализации, включение блока 8 сигнализации через второй формирователь 7 управляющих сигналов, при этом длительность включения соответствует времени нажатия пятого переключателя 46.

Для продолжения выполнения алгоритма работы таймера необходимо четвертый переключатель 45 установить в положение "Выкл. ".

Все элементы схемы таймера реализуются на базе стандартных схемных решений и стандартных микросхем.

Первый формирователь 4 управляющих сигналов преобразует входные сигналы в сигналы управления индикаторами блока 5 индикации и должен содержать дешифраторы кодов состояний первого и второго счетчиков 3 и 15, а также ключи для управления индикаторами блока 5 индикации.

Второй формирователь 7 управляющих сигналов преобразует входные сигналы в сигналы управления блоком 8 сигнализации и должен содержать ключ с гальванической развязкой, обеспечивающей включение исполнительного органа блока 8 сигнализации. Блок 8 сигнализации преобразует сигналы управления в сигналы той или иной физической природы, необходимой или удобной в конкретном случае применения таймера. Это могут быть сигналы акустические, оптические и т. д.

Третий формирователь 12 управляющих сигналов преобразует входные сигналы в сигналы управления включением исполнительного механизма 13 и должен содержать ключ, обеспечивающий гальваническую развязку и замыкание цепи питания исполнительного механизма 13.

В процессе подготовки таймера к работе имеется возможность запрограммировать блок 31 уставок и установить второе считывающее устройство 47 таким образом, чтобы обеспечивался необходимый режим работы с выбранным исполнительным механизмом, а именно установить требуемое время подачи предупредительной сигнализации перед окончанием периода ритма, минимальное время периода ритма и требуемое число срабатываний исполнительного механизма 13, что обеспечивает расширение функциональных возможностей и расширение класса исполнительных механизмов, с которыми может использоваться предлагаемый таймер.

Наличие возможности изменения установки периода ритма с помощью первого считывающего устройства 2 в процессе работы и подача предупредительной сигнализации с помощью блока 8 сигнализации перед окончанием периода ритма, т. е. перед включением исполнительного механизма 13, позволяют влиять на производительность и безопасность труда, а также улучшить процесс обслуживания таймера, используя блок 5 индикации, тем самым воздействовать на функциональные возможности и эксплуатационные характеристики таймера.

Упрощение схемы, изменение связей и изменение алгоритма работы таймера позволило также повысить надежность при его эксплуатации.

Положительный эффект заявляемого таймера, обусловленный описанными преимуществами, выражается в расширении функциональных возможностей и повышении эксплуатационных характеристик. Использование предлагаемого таймера, например, в качестве устройства управления конвейерной лини позволит значительно снизить вспомогательные затраты.

Claims (1)

- ЭЛЕКТРОННЫЙ ТАЙМЕР-ЗАДАТЧИК РИТМА, содержащий первую память, последовательно соединенную с первым считывающим устройством, первым счетчиком, первым формирователем управляющих сигналов и блоком индикации, масштабный делитель, сбросовый вход и первый выход которого соединены соответственно с вторым и третьим входами первого счетчика, последовательно соединенный с вторым формирователем управляющих сигналов и блоком сигнализации, блок питания, соединенный первым выходом с задающим генератором, а выходами питания и общим - соответственно с первым и вторым входами первого формирователя импульсов, третий формирователь управляющих сигналов, соединенный выходом с входом "Пуск" исполнительного механизма, выход "Стоп" которого соединен с первым входом второго формирователя импульсов, второй счетчик, первый и второй триггеры, третий формирователь импульсов, элемент И, инвертор, первый, второй и третий резисторы, первые выводы которых соединены вместе, а вторые - с первыми выводами первого, второго и третьего переключателей соответственно, вторые выводы которых соединены между собой, отличающийся тем, что в него дополнительно введены блок уставок, первая, вторая и третья схемы сравнения, первый, второй и третий элементы И - НЕ, первый и второй элементы ИЛИ - НЕ, третий и четвертый триггеры, четвертый, пятый и шестой резисторы, четвертый и пятый переключатели, второе считывающее устройство и вторая память, выход которой соединен с входом второго считывающего устройства, выход которого соединен с первым входом второго счетчика, второй вход которого соединен с выходом второго формирователя импульсов, третий вход - с выходом третьего формирователя импульсов и сбросовым входом масштабного делителя, первый выход - с вторым входом первого формирователя управляющих сигналов, а второй выход - с первым входом первого элемента ИЛИ - НЕ и первым входом элемента И, второй вход которого соединен через инвертор с первым выводом третьего переключателя, а выход - с первым входом второго элемента ИЛИ - НЕ, второй вход которого соединен с вторым входом первого элемента ИЛИ - НЕ и выходом первого формирователя импульсов, третий вход - с третьим входом первого элемента ИЛИ - НЕ и выходом третьего триггера, а выход - со сбросовым входом первого триггера, выход которого соединен с первым входом первого элемента И - НЕ и первым входом второго элемента И - НЕ, стробирующий вход - с вторым входом второго элемента И - НЕ и выходом третьего элемента И - НЕ, а информационный вход - с вторым входом второго формирователя управляющих сигналов и выходом первой схемы сравнения, первый вход которой соединен с выходом первого считывающего устройства, а второй вход - с первым выходом блока уставок, второй выход которого соединен с первым входом второй схемы сравнения, а третий выход - с первым входом третьей схемы сравнения, выход которой соединен с третьим входом второго формирователя управляющих сигналов, а второй вход - с выходом первого счетчика и вторым входом второй схемы сравнения, выход которой соединен с информационным входом второго триггера, сбросовый вход которого соединен с входом третьего формирователя импульсов и выходом первого элемента ИЛИ - НЕ, выход - с вторым входом второго формирователя импульсов и вторым входом первого элемента И - НЕ, а стробирующий вход - с вторым выходом масштабного делителя, третий выход которого соединен с третьим входом первого формирователя управляющих сигналов, а инкрементный вход - с выходом второго элемента И - НЕ, третий вход которого соединен с выходом задающего генератора и третьим входом второго формирователя импульсов, четвертый вход - с четвертым входом первого формирователя управляющих сигналов, выходом первого элемента И - НЕ и первым входом третьего формирователя управляющих сигналов, пятый вход - с пятым входом первого формирователя управляющих сигналов, первым выводом четвертого резистора, первыми выводами четвертого и пятого переключателей и третьим входом первого элемента И - НЕ, а шестой вход - с четвертым входом первого элемента И - НЕ, шестым входом первого формирователя управляющих сигналов, выходом готовности исполнительного механизма и первым входом третьего элемента И - НЕ, второй вход которого соединен с четвертым входом первого элемента ИЛИ - НЕ и выходом четвертого триггера, установочный вход которого соединен с первым выводом первого переключателя, а сбросовый вход - с третьим выводом первого переключателя и первым выводом пятого резистора, второй вывод которого соединен с выходом питания блока питания, первым выводом первого резистора, вторым выводом четвертого резистора и первым выводом шестого резистора, второй вывод которого соединен с третьим выводом второго переключателя и сбросовым входом третьего триггера, установочный вход которого соединен с первым выводом второго переключателя, второй вывод которого соединен с вторым выводом четвертого переключателя и общим выходом блока питания, четвертый выход которого соединен с вторым входом третьего формирователя управляющих сигналов, пятый выход - с вторым входом блока индикации, а шестой выход - с четвертым входом второго формирователя управляющих сигналов, пятый вход которого соединен с вторым выводом пятого переключателя.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| SU5027130 RU2012028C1 (ru) | 1992-02-10 | 1992-02-10 | Электронный таймер-задатчик ритма |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| SU5027130 RU2012028C1 (ru) | 1992-02-10 | 1992-02-10 | Электронный таймер-задатчик ритма |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| RU2012028C1 true RU2012028C1 (ru) | 1994-04-30 |

Family

ID=21596798

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| SU5027130 RU2012028C1 (ru) | 1992-02-10 | 1992-02-10 | Электронный таймер-задатчик ритма |

Country Status (1)

| Country | Link |

|---|---|

| RU (1) | RU2012028C1 (ru) |

-

1992

- 1992-02-10 RU SU5027130 patent/RU2012028C1/ru active

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| RU2012028C1 (ru) | Электронный таймер-задатчик ритма | |

| RU2019907C1 (ru) | Программируемый генератор импульсов | |

| US4847832A (en) | Time multiplexed data transmission system | |

| US4517473A (en) | Solid-state automatic injection control device | |

| SU875340A1 (ru) | Устройство дл програмного управлени | |

| SU1594005A1 (ru) | Устройство дл контрол срабатывани электроаппаратов цепей управлени локомотивом | |

| SU1737479A1 (ru) | Устройство дл реакции на аварию в схеме управлени потребител ми электроэнергии | |

| SU624230A1 (ru) | Устройство дл управлени последовательностью операций | |

| SU1545122A1 (ru) | Блок управлени пневматическим коммутатором | |

| SU1610596A1 (ru) | Программируемый таймер | |

| SU1062696A1 (ru) | Генератор потоков случайных событий | |

| SU1091351A1 (ru) | Делитель частоты следовани импульсов с регулируемой длительностью импульсов | |

| SU1480120A1 (ru) | Делитель частоты следовани импульсов с регулируемой длительностью импульсов | |

| SU1541764A1 (ru) | Многоканальный коммутатор | |

| SU1358063A1 (ru) | Цифровой фазочастотный компаратор | |

| SU450136A1 (ru) | Программный регул тор | |

| SU1027703A1 (ru) | Устройство дл дозировани | |

| SU1206730A1 (ru) | Устройство дл контрол коммутационных изделий | |

| SU824220A1 (ru) | Формирователь сигналов о предельныхОТКлОНЕНи Х пАРАМЕТРОВ Об'ЕКТА | |

| SU1213428A1 (ru) | Устройство дл контрол частоты | |

| SU1539974A1 (ru) | Датчик одиночных импульсов | |

| SU1508193A1 (ru) | Устройство дл циклового программного управлени | |

| SU1645981A1 (ru) | Устройство дл сигнализации состо ний объекта | |

| SU995066A1 (ru) | Программное временное устройство | |

| SU1167574A1 (ru) | Электронное временное устройство с обнаружением отказов |