KR950002712B1 - 네트워크 인터페이스 장치 - Google Patents

네트워크 인터페이스 장치 Download PDFInfo

- Publication number

- KR950002712B1 KR950002712B1 KR1019860010395A KR860010395A KR950002712B1 KR 950002712 B1 KR950002712 B1 KR 950002712B1 KR 1019860010395 A KR1019860010395 A KR 1019860010395A KR 860010395 A KR860010395 A KR 860010395A KR 950002712 B1 KR950002712 B1 KR 950002712B1

- Authority

- KR

- South Korea

- Prior art keywords

- data

- random

- access memory

- message

- bus

- Prior art date

Links

- 230000015654 memory Effects 0.000 claims description 77

- 238000012360 testing method Methods 0.000 claims description 9

- 238000004891 communication Methods 0.000 claims description 7

- 238000012545 processing Methods 0.000 claims description 5

- 230000008878 coupling Effects 0.000 claims 1

- 238000010168 coupling process Methods 0.000 claims 1

- 238000005859 coupling reaction Methods 0.000 claims 1

- 230000004044 response Effects 0.000 claims 1

- 230000005540 biological transmission Effects 0.000 description 20

- 238000012546 transfer Methods 0.000 description 12

- 238000000034 method Methods 0.000 description 7

- 238000010586 diagram Methods 0.000 description 5

- 238000001514 detection method Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 238000004364 calculation method Methods 0.000 description 2

- 125000004122 cyclic group Chemical group 0.000 description 2

- 230000001934 delay Effects 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 239000003365 glass fiber Substances 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 206010009944 Colon cancer Diseases 0.000 description 1

- 244000208060 Lawsonia inermis Species 0.000 description 1

- 101100172132 Mus musculus Eif3a gene Proteins 0.000 description 1

- CYTYCFOTNPOANT-UHFFFAOYSA-N Perchloroethylene Chemical compound ClC(Cl)=C(Cl)Cl CYTYCFOTNPOANT-UHFFFAOYSA-N 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 229910052602 gypsum Inorganic materials 0.000 description 1

- 239000010440 gypsum Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000003325 tomography Methods 0.000 description 1

- 238000012795 verification Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/40006—Architecture of a communication node

- H04L12/40032—Details regarding a bus interface enhancer

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/10—Program control for peripheral devices

- G06F13/12—Program control for peripheral devices using hardware independent of the central processor, e.g. channel or peripheral processor

- G06F13/124—Program control for peripheral devices using hardware independent of the central processor, e.g. channel or peripheral processor where hardware is a sequential transfer control unit, e.g. microprocessor, peripheral processor or state-machine

- G06F13/128—Program control for peripheral devices using hardware independent of the central processor, e.g. channel or peripheral processor where hardware is a sequential transfer control unit, e.g. microprocessor, peripheral processor or state-machine for dedicated transfers to a network

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/40143—Bus networks involving priority mechanisms

- H04L12/4015—Bus networks involving priority mechanisms by scheduling the transmission of messages at the communication node

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/407—Bus networks with decentralised control

- H04L12/413—Bus networks with decentralised control with random access, e.g. carrier-sense multiple-access with collision detection (CSMA-CD)

Abstract

내용 없음.

Description

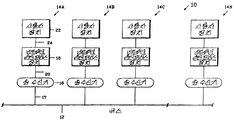

제1도는 본 발명의 네트워크 인터페이스 장치가 사용될 수 있는 버스 시스템의 간단한 블록 다이어그램.

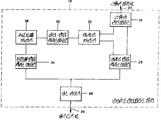

제2도는 본 발명의 실시예에 따른 네트워크 인터페이스 장치의 간단한 블록 다이어그램.

제3도는 제2도의 메세지 랜덤-액세스 메모리의 간단한 블록 다이어그램.

* 도면의 주요부분에 대한 부호의 설명

16 : 송수신기 18 : 네트워크 인터페이스 장치

22 : 사용자 장치 26 : 버스 제어기

28 : 메세지 랜덤-액세스 메모리 30 : 사용자 인터페이스

32 : 메세지 처리기 34 : 프로토콜 랜덤-액세스 메모리

36 : 프로토콜 처리기 38 : 상태 랜덤-액세스 메모리

62 : 어드레스 및 데이타 스위치

본 발명은 디지탈 데이타 전송에 관한 것으로서, 특히 디지탈 데이타 버스와 사용자 장치 사이의 인더페이스 장치에 관한 것이다.

분산 디지탈 데이타 시스템은 통신 시스템에 걸쳐서 서로 통신 능력이 있는 다수의 위치로 구성되어 있다. 노드라 불리는 각 위치는 수신, 전송 또는 수신 및 전송할 수 있다. 노드는 예를들어, 자치 계산 능력을 갖고 있는 개인용 컴퓨터, 차치 계산 능력이 없는 덤(dumb) 터미널, 프린터, 통신 링크, 또는 여러 네트워크로의 통로일 수 있다, 일반적인 3종류의 네트워크 즉, 스타, 링 및 버스는 공통 사용된다.

스타 네트워크에서, 각 노드는 네트워크 서버로부터 외부로 뻗어있는 전용 케이블에 의해 직접 연결된다.그러나 네트워크는 요구되는 상호 연결을 하기 위해 많은 양의 케이블을 필요로 한다. 더구나, 네트워크 서버는 통상적으로 전체 실행이 네트워그의 필요에 사용되는 스마트 터미널이다. 스타 네트워크가 각 노드를 위해 전용 링크를 제공하기 때문에, 분배된 통신 어세트로의 동시 액세스를 시도하는 노드 사이의 간섭 문제는 발생하지 않는다.

링 네트워크는 그것의 이름이 함축하고 있듯이 인접한 노드를 폐쇄 링에 연결시킨다. 한 노드에서 발생하는 메세지는 상호 연결 케이블에 편승해 그것의 인접 노드로 통과한다. 만약 상기 메세지가 인접 노드에 어드레스되면 인접 노드는 이러한 사실을 검출한 다음 그것을 수신하는 작용을 한다. 만약 상기 메세지가 인접 노드에 어드레스되지 않으면 그것은 상기 어드레스 노드가 발견될 때까지 링내의 차기 노드로 통과한다.수신하자마자, 수신 노드는 수신을 확인하기 위하여 상기 메세지를 발생한 노드에 어드레스된 케이블에 인지 메세지를 보낼 수 있다. 인지 메세지는 그것이 본래의 목적지에서 수신될 때까지 노드에서 노드로 진행한다. 링 네트워크에서 흐르는 단일 방향 데이타는 데이타 전송률을 제한하는 경향이 있다. 더구나, 각 노드가 수신되지 않은 메세지를 그것의 이웃으로 통과시킬 책임이 있기 때문에 한 노드의 고장은 전체 네트워크를 방해할 수 있다

버스는 노드가 편리한 위치에 부착되는 이연식 또는 동축 링크로 구성된 선형 네트워크이다. 모든 노드는 메세지를 버스에 인가시키고, 그들에게 어드레스된 메세지를 위해 버스를 모니터한다. 한 노드의 고장은 정상적으로 네트워크 동작을 중지시킬 수 없다. 버스의 선형 특성은 스타 네트워크의 케이블링 고스트를 필요로 하지 않는다. 가장 일반적인 버스는 초당 몃 킬로비트에서 초당 수백 메가비트까지 변화하는 데이타 전송률로 직렬 데이타를 나른다.

본 발명에 관련된 버스 네트워크는 임의 두개의 특정 노드 사이에 데이타를 보내고 뜩같은 시간에 버스로의 엑세스를 요구하는 둘 또는 그 이상의 노드의 문제점을 취급하는 수단을 제공한다. 본 발명의 목적을 위하여,IEEE 네트워크 표준 802.3에 기술된 버스 프로토콜과의 사용을 위한 본 발명의 실시예가 설명될 것이다.802.3 표준을 구체화하는 하나의 상업적인 네트워크 시스템은 이서네트(Ethernet)라 공지되어 있고 3Com으로부터 구입 가능하다. IEEE 네트워크 표준(802.3)은 초당 10메가비트의 비트 전송률을 갖고 있는 베이스밴드 시스템을 구체적으로 설명한다. 후에 설명되겠지만 지능을 통신하는 그러한 버스 네트워크의 실제 능력은 그것의 비트 전송률보다 상당히 낮다. 본 분야에 숙련된 사람이면 본 발명이 특정 비트 전송률에 또는 와이어 또는 동축 케이블로 통신하는 베이스밴드 시스템에 제한되지 않음을 인지할 것이다. 와이어 또는 동축 케이블과 다른 미디어상의 노드 사이에 통신될 수 있는 광대역 시스렘에서 여기에 설명된 기술을 사용하는 것은 본 발명의 범위내에 속한다. 광대역 시스템은 하나의 데이타 채널에 편승되는 것이 각각에 따라 다수의 부반송파를 사용할 수 있다. 각각의 그러한 데이타 채널은 802.3 베이스밴드 채널과 같은 것으로 간주된다. 전송 미디어는 예를들어, 적어도 노드 사이의 거리의 일부를 커버하는 마이크로웨이브 전송을 포함할 수 있다. 광 전송도 역시 그러하다. 광 전송은 공기중에서 실행될 수 있고 또는 예를들어, 유리 파이버와 같은 광 통신 미디어에 제한될 수 있다. 유리 파이버는 초당 기가비트일 수 있는 보다 큰 대역폭을 제공한다.

버스 전송은 고정 또는 가변 길이일 수 있는 데이타 패킷을 사용한다. 데이타 패킷은 헤더, 데이타 및 트레일러를 포함한다. 데이타 패킷내의 데이타는 단지 전송으로부터 목적지 노드까지의 전체 메세지의 부분일수 있다. 헤더는 동기 신호를 제공하고 소스 및 의도된 데이타 목적지를 확인하며, 데이타 패킷내의 데이타가 관련된 데이타 패킷내의 데이타에 관하여 차지하는 시권스를 확인하는 정보를 포함한다. 트레일러는 통상적으로 데이타가 에라없이 수신되는 것을 입증하기 위해 수신 노드가 사용하는 메세지인 순환 중복 검사또는 검사 합계를 포함한다.

이서네트 표준에 따르면, 데이타 패킷은 전송되는 전체 메세지의 길이에 관계없이 고정된 최대 길이를 갖고 있다. 헤더와 트레일러는 지능을 포함하지 않으므로 데이타 전송에 대한 오버헤드로 간주된다. 오버헤드와 데이타의 비는 헤너 빛 트레일러의 사이즈와 거기에 포함된 데이타 부분의 길이에 의존한다. 어떤 시스템은 짧은 메세지를 취급할 능력을 필요로 한다, 그러한 시스템은 예를들어, 44바이트의 헤더와 4바이트의 트레일러와 데이타용 80바이트를 갖는 128바이트(8-비트워드)의 전체 길이를 갖고 있는 데이타 페킷을 사용할 수 있다. 전형적인 메세지가 80바이트보다 작게 구성되면 효율이 떨어진다. 비록 비효울 데이타 전송기술일지라도 짧은 데이타 전송에는 적합한다.

긴 메세지를 위해, 긴 데이타 패킷은 전송 효율을 향상시킨다. 상기 이서네트 시스템은 예를들어, 44바이트 오버헤드를 갖고 있는 약 1500바이트의 데이타 패킷을 사용한다. 이와같이 오버헤드는 데이타 패킷의 비교적 작은 퍼센티지가 된다.

본 발명을 위해 우리가 예견한 버스 전송에 대한 한 출원은 그래픽 데이타의 전송을 포함한다. 그러한 그래픽 데이타는 통상적으로 메세지당 몇십만 내지 몇백만 바이트를 포함한다. 큰 데이타 패킷은 높은 전송효울을 엄기 위해 필요한 것이다. 그래픽 데이타 전송 시스템에서, 약 4000바이트의 데이타 페킷 길이가 사용될 수 있다. 데이타 패킷의 데이타 부분이 채워질때, 오버헤드와 전체 길이의 비는 무의미한 것이 된다. 메세지에서 마지막 데이타 패킷의 채워지지 많은 부분은 오버헤드이다. 예를들어, 초당 9.6메가비트의 버스속도를 갖고 있는 시스템 선송 그대픽 데이타는 초당약 9메가비트 정도의 데이타-전송률을 얻을 수 있다.

버스 데이타를 사용하는 장치는 전송/수신, 수신전용, 또는 송신전용일 수 있다. 송신/수신 장치는 컴퓨터 터미널일 수 있다. 수신전용장치는 그래픽 디스플례이일 수 있고 또는 프린터일 수 있다. 전송전용 장치는 비디오 카메라 체인, CAT(컴퓨터 축방향 단층 촬영) 주사기, 또는 마그네틱 공진 주사기일 수 있다.

각 노도는 사용자 장치와 버스 데이타를 접속하기 위한 인터페이스 장치를 필요로 한다. 전송 노드는 긴 메세지를 데이타 패킷으로 분리하기 위해 계산을 실행하고, 헤더와 트레일러를 첨부하며, 버스를 액세스 한다. 수신 노드는 그것의 유일한 확인기가 검출될 때까지 모니터하고, 데이타 패킷을 받아들이고, 데이타 패킷에 대한 다른 여러 테스트는 물론 데이타 패킷에 대한 순환 중복 검사(CRC) 또는 검사 합계를 계산하며, 전송하도록 요청될 때 전송 노드로 어드레스된 버스상으로 인지를 전송한다. 계산되어 수신된 CRCs또는 검사 합계와 다른 테스트가 일치하지 않을때, 수신 노드는 데이타 패킷내에 데이타를 스크랩하며, 인지 요청에 응납하여 일치하지 않음을 알리는 전송 노드에 어드레스된 버스상으로 메세지를 보낸다. 그에 따라 전송 노드는 수신 노드에서 일치함이 발견될 때까지 데이타 패킷을 전송하기 위한 시도를 한다.

상기에서 주목했듯이 모든 노드는 임의 시간에 버스를 액세스하는 독립 능력을 갖고 있다. 두개의 노드가동시에 전송한다면, 양 데이타 패킷내의 데이타는 오전된다. 많은 노드를 갖고 있는 시스템에서, 두개의 노드가 동시에 버스를 액세스하려고 시도하는 가능성이 약간 존재한다. 802.3 표준은 오전을 하지 많으며, 충돌 검출에 의한 캐리어-감지, 다중-액세스 시스템(CSMA/CD)을 사용하여 데이타 손실도 없애준다. 전송하기 전에, 노드는 버스를 따른다. 만약 버스에 전송되는 데이타가 검출되면, 노드는 버스가 프리(free)가 될 때까지 기다린 다음 송신을 시작한다. 만약 2노드가 동시에 전송하기 시작하면 충돌의 결과가 나타난다. 양 전송 노드는 한 신호 이상이 존재함을 가리키는 상태를 검출하기 위하여 그들의 전송동안 버스를 모니터한다. 만약 한 신호 이상이 검출되면, 양쪽은 전송을 중지하고 길이가 랜덤하게 결정되는 타임 아웃 주기동안은 활동하지 않는다. 인터페이스 장치는 충돌 검출의 시간까지 임의 부분적인 데이타 전승의 처리를 결정한다.

몇몇의 경우에, 부분적인 데이타 전송은 스크랩 된다. 타임 아웃 주기의 랜덤은 노드중 하나가 다른 노드전에 그것의 타임 아웃 주기의 단부에 도착하는 것을 공고히 한다. 앞선 노드는 버스를 따르고, 데이타 전송이 없음을 검출하고 그것의 선택 데이타 패킷을 재선송하기 시작한다. 다음 노드는 버스를 따르고, 앞선 노드의 데이타 전송을 검출하며, 그것은 전송이 시작되기 전에 클리어 버스를 검출할 때까지 대기한다. 다수의 노드가 버스상에 존재할 때, 그러한 감소는 이론적인 버스 전송률의 상당한 부분이 될 것이다. 수신된 데이타 패킷을 검사하고 충돌 희피를 취급하는 데이타 패킷의 어셈블리같은 그러한 오버헤드 타스크는 상당한 짐을 인터페이스 장치에 부여한다. 인터페이스 장치는 일반적으로 오버헤드 및 직렬 전송 또는 수신을 실행한다. 즉, 데이타 패킷의 전송 또는 수신이 발생하는 동안 그외에는 어느것도 인터페이스 장치에 의해 실행되지 않는다. 오버헤드 타스크는 전송 및 수신으로 보간될 수 있지만 그들은 메모리와 처리기 시간을 분리한다. 결과적으로, 오버헤드 활동을 수용하기 위해 데이타의 송신 및 수신에서 갭이 나타난다. 우리는 초당 10에 가비트의 버스트 전송률을 갖고 있는 버스 시스템의 효과적인 전송률이 오버헤드 타스크가 고려된 경우에는 초당 2베가비트 이하로 된다는 것을 관찰했다.

따라서, 본 발명의 목적은 종래 기술의 결점을 극복하는 네트워크를 위한 인터페이스 장치를 제공하는 것이다.

본 발명의 또하나의 목적은 분리 처리기를 사용하여 버스 프로토콜 및 메세지 데이타를 병렬로 처리하는 버스 네트워크를 위한 인터페이스 장치를 제공하는 것이다. 버스 프로토콜 및 메세지내의 데이타 부분은 표준 데이타 패킷을 발생시키기에 적당한 순서로 전송 노드로부터 판독된다. 버스 프로토콜 및 수신된 데이타패킷의 데이타 부분은 데이타가 받아들여지고 인지되는 속도를 향상시키기 위해 분리 처리기에서 처리된다.

본 발명의 또하나의 목적은 프로토콜 처리기의 제어하에 유출 메세지의 버스-프로트콜 데이타를 기억하기 위하여 똑같은 시간에 수신된 데이타를 받아들이는 능력이 있는 3중부 메세지 랜덤-액세스 메모리를 사용하는 네트워크 인터페이스 장치를 제공하는 것이다. 더구나, 2중부 프로토콜랜덤-액세스 메모리는 프로토콜 처리기의 제어하에 유출 메세지의 버스 프로토콜 데이타를 기억하기 위해 똑같은 시간에 수신된 버스-프로토콜데이타를 받아들인다.

본 발명의 또하나의 목적은 두개의 처리기를 조정하기 위하여 메세지 처리기 및 프로토콜 처리기에 의해 액세스 가능한 상태 랜덤-액세스 메모리를 제공하는 것이다.

본 발명의 또다른 목적은 버스 시스템의 버스트 통신 능력에 근접한 속도로 버스 통신을 인네이블하는 인터페이스 장치를 제공하는 것이다.

간략히 말하면, 본 발명은 버스-프로토콜 및 데이타 패킷내의 데이타 부분을 처리하기 위해 분리처리기및 랜덤-액세스 메모리를 사용하는 버스 네트워크를 위한 네트워크 인터페이스 장치를 제공하는 것이다.각 처리기는 데이타를 이동시키는 곳인 분리 랜덤-액세스 메모리에 액세스한다. 랜덤 액세스 메모리는 논리 조정기를 갖고 있는 하나이상의 요청에 의한 액세스가 충돌을 피할 수 있게 하는 다중-포트이다.

본 발명의 한 실시예에 따르면, 버스 디지탈 데이타와 사용자 장치를 접속하는 네트워크 인터페이스 장치는 메세지 처리기, 메모리 랜덤-액세스 메모리, 상기 버스, 상기 메세지 및 상기 사용자 장치로부터 데이타 요청을 서비스하는 상기 메세지 랜덤-액세스 메모리내의 수단, 프로토콜처리기, 프로토콜 랜덤-액세스 메모리 및, 상기 버스 및 상기 프로토콜처리기로부터 프로토콜 요청을 서비스하는 상기 프로토콜 랜덤-액세스 메모리내의 수단을 포함하며, 상기 메세지 랜덤-액세스 메모리는 전송 또는 수신되는 데이타패킷의 데이타 부분을 저장하는데 효과적인 수단을 갖고 있으며, 상기 프로토콜 처리기는 전송되는 데이타패킷을 위한 상기 프로트콜 랜덤-액세스 메모리에 저장을 위한 상기 데이타 패킷중 적어도 헤더 부분을 발생시키고 수신된 메세지의 올바름을 테스트하기에 효과적이며, 상기 메세지 및 프로토콜랜덤-액세스 메모리중 하나는 다른 요청에 관계없이 그들의 각 데이타 요청의 임의를 서비스하기에 효과적이므로, 프로토콜및 데이타 처리의 실제 병렬성이 성취되는 것을 특징으로 한다.

본 발명의 상기 목적 및 다른 목적, 특징 및 장점은 도면을 참조로 상세히 설명될 것이다. 도면에서 같은번호는 같은 엘리먼트를 가리킨다.

제1도를 보면, 본 발명이 적용될 수 있는 버스 시스템(1O)이 도시되어 있다. 버스 시스템(10)은 다수의노드(14A 내지 14N)가 부착되어 있는 버스(12)를 포함한다.

본 발명에 관계되어 있는 모든 노드(14)가 동일하므로, 단지 노드(14A)만 상세히 설명된다.

노드(14A)내의 종래의 송수신기(16)는 데이타 라인(17)에 의해 버스(12)에 연결되어 있다. 네트워그 인터페이스 장치(18)는 데이타 라인(20)을 통해 송수신기(l6)에 보내고 송수신기(16)로부터 데이타를 수신한다.사용자 장치는 그것의 형태에 따라서 데이타 라인(24)을 통해 데이타를 네트워크 인터페이스 장치로 보내고 네트워크 인터페이스 장치로부터 데이타를 수신한다.

데이타 라인(17)은 일반적으로 동축 케이블로 구성된다. 데이타 라인(20)은 다음의 3세트 라인 즉, 1) 송수신기(16)로 전송되는 데이타를 운반하는 제1연 이선식, 2) 버스(12)로부터 수신된 데이타를 운반하는 제2연 이선식, 3) 충돌이 버스(12)상에서 진행중에 있음을 가리키는 제3연 이선식으로 구성된다. 송수신기(16)는 전송되고 수신된 신호 사이의 스위칭을 처리한다. 충돌 검출이 노드(14)로부러의 데이타 전송과 일치하면, 상기 열거된 단계는 오전되는 것을 피할 수 있다.

종래의 버스 시스템(10)에서, 버스(12)상의 데이타는 맨체스터 코드이다. 공지된 바와 같이, 맨체스터 코드화된 신호는 50퍼센트 평균 충격 계수를 갖고 있다. 만약 만일 맨체스터-코드화된 신호가 버스(12)상에 나타나면, 평균 신호 전압은 선정된 값을 취한다. 그러나, 두개의 맨체스터 코드화된 신호가 버스(12)상에 존재하면 신호 전압은 단지 하나의 신호가 존재할 때의 신호 전압과 다르다. 송수신기(16)는 충돌이 존재함을 가리켜주는 신호 전압을 위해 버스(12)상의 평균 신호 전압을 모니터하며, 그러한 상태가 존재할 때는 네트워크 인터페이스 장치(18)에 통보한다.

송수신기(16)는 예를들어 3Com으로부터 구입 가능한 종래의 이서네트 송수신기와 같이 임의 적당한 송수신기일 수 있다.

제2도를 보면, 네트워크 인터페이스 장치(18)는 데이타 라인(20)으로부터의 데이타 수신, 데이타 라인(20)으로의 데이타 전송 및 데이타 라인(20)으로부터의 충돌 신호의 수신을 제어하는 버스 제어기(26)를 포함한다. 메세지 랜덤-액세스 메모리(28)는 버스 제어기(26)로부터 데이타 페킷의 메세지 부분을 수신하고, 버스 제어기(26)로 데이타 패킷의 메세지 부분을 송신하며, 사용자 인터페이스(30)로부터 데이타를 수신하고 상기 인터페이스(30)로 데이타를 송신할 수 있는 3중 포트이다. 상기 사용자 인터페이스(30)는 데이타라인(24)상의 데이타를 사용자 장치(22)에 접속시킨다. 메세지 랜덤-액세스 메모리(28)는 메세지 처리기(32)와 데이타를 교환한다.

2중 포트 프로토콜 랜덤-액세스 메모리(34)는 제어기(26)로부터 데이타 패킷의 버스 프로토콜 파트를 수신하며, 프로토콜 처리기(36)의 제어하에 전송되는 데이타 패킷의 프로토콜 부분을 기억한다. 상대 랜덤-액세스 메모리(38)는 후에 설명되겠지만 프로토콜 처리기(36)와 메세지 처리기(32) 사이에 인터페이스를 제공한다.

동작시, 데이타 전송을 위하여 사용자 장치(제1도)는 전송되는 데이타의 목적지와 파일의 사이즈를 가리키는 명령을 데이타 라인(24)으로 보낸다. 전송 준비가 된 데이타 패킷내의 데이타는 메세지 처리기(32)에 의해 구성되는 메세지 랜덤-액세스 메모리(28)로 파이프 라인된다. 메세지 처리기(32)는 데이타 패킷이 전송되고 그들의 목적지 및 그들이 메세지 랜덤-액세스 메모리(28)에서 차지하는 어드레스를 위한 준비가 되었음을 프로토콜 처리기(36)에 통보하는 메세지를 상태 랜덤-액세스 메모리(38)에 기억시킨다. 프로토콜처리기(36)는 프로토콜 랜덤-액세스 메모리(34)내에 저장을 위해 데이타 패킷에 대한 헤더를 구성한다.

데이타 라인(20)상의 충돌-검출 신호가 버스(12)상의 다른 노드의 전송이 없음을 가리킬때, 프로토콜 처리기(36)는 프로토콜 랜덤-액세스 메모리(34)로부터 패킷 헤더와 메세지 랜덤-액세스 메모리(28)로부터 데이타 패킷의 데이타 부분을 데이타 라인(20)으로 전송하도록 버스 제어기(26)에 통보한다. 패킷의 데이타부분의 단부에서, CRC 또는 검사 합계 트레일러는 버스 제어기(26)에 의해 가산되어 데이타 패킷이 완성된다.

충돌-검출 신호는 데이타가 전송되는 동안 데이타의 존재를 가리키면, 상기 상세한 회복 절차가 개시된다.

메세지 처리기(32)와 프로토콜 처리기(36)가 데이타 패킷을 전송하기 위한 준비 단계에 있는 시간동안,프로토콜랜덤-액세스 메모리(34)와 메세지 랜덤-액세스 메모리(28)가 버스 제어기(26)로부터 데이타를 수신할 수 있는 시간이 있다. 유사하게, 데이타 메세지를 포함하는 데이타 패킷의 각 부분이 프로토콜랜덤-액세스 메모리(34)와 메세지 랜덤-액세스 메모리(28)로부터 전송되는 동안 이들 엘리먼트가 사용자 인터페이스(30)로부터의 차기 파이프라인 데이타를 수신하고 저장하며, 데이타 페킷의 연속 스트림의 완성에 따르는 지연없이 결과 데이타 패킷을 전송하기 위해 적당한 헤더를 발생시키는 시간이 허용될 수 있다. 네트워크 인터페이스 장치(18)내의 결과 병렬성은 데이타 전송에서의 갭의 부과를 피할 수 있으며, 그렇지 않으면 오버헤드 활동을 위한 것이 필요해진다,

데이타를 수신하기 위하여, 인입 데이타 패킷상의 헤더 및, 선택적으로 트레일러는 프로토콜 랜덤-액세스 메모리(34)로 향하며, 데이타 패킷의 데이타 부분은 메시지 랜덤-액세스 메모리(28)로 향한다. 버스 제어기(26)는 데이타 패킷이 그것의 노드에 어드레스되는 것을 공고히 하기 위해 어드레스 검증을 실행하고,CRC 또는 검사 합계 비교 및 데이타 패킷의 데이타 부분상에 대한 다른 계산을 실행할 준비를 한다, 트레일러는 메세지 처리기(32)에 의한 처리를 위해 메시지 랜덤-액세스 메모리(28)로 선택적으로 향할 수 있다. 테스트를 통과한 데이타 패킷내의 데이타는 데이타 라인(24)으로의 전송을 위해 준비된다. 프로토콜 랜덤-액세스 메모리(34)는 테스트 결과의 영상을 보유한다. 데이타 패킷의 헤더가 인지 요청을 포함하면, 프로토콜처리기(36)는 테스트를 통과한 데이타 패킷의 인지를 포함하는 메세지를 전송하고 테스트에 실패한 데이타 패킷들을 지시한다. 전송 노드는 테스트에 성공한 후 메세지 랜덤-액세스 메모리(28)내의 적당한 어드레스에 기억된 앞서 실패한 데이타 패킷을 다시 전송한다. 메세지 랜덤-액세스 메모리(28)내의 데이타 메세지를 수신하고 프로토콜 랜덤-액세스 메모리(34)내의 수신된 버스 프로토콜을 처리하는 상기 단계는 새로운 인출 메세지가 메세지 랜덤-액세스 메모리(28)와 프로토콜 랜덤-액세스 메모리(34)에 기억을 위한 프로토콜 처리기(36)에서 발생된 그것의 헤더에 기억되고 또는 앞서 수신된 메세지가 메세지 랜덤-액세스 메모리(28)로부터 데이타 라인(24)에 전송되는 똑같은 시간에 선정된 우선 순위에 따라 실행될 수 있다. 이와같이, 연속 수신 동작 또는 연속 합성 수신 및 전송 동작은 버스상의 데이타 패킷의 스트림내의 갭을 피할 수 있기에 충분한 병렬성을 가지고 실행된다.

제3도를 보면, 메세지 랜덤-액세스 메모리(28)는 랜덤-액세스 메모리(40)를 포함하며, 상기 랜덤-액세스 메모리(40) 서비스는 라인(42,44 및 46)상의 각 사용자, 처리기 및 버스 선택 신호 경쟁에 의해 요청되어 RAM 조정기(48)의 입력에 인가된다. RAM 조정기(48)는 예를들어, 랜덤-액세스 메모리(40)로 또는 메모리로부터의 데이타에 대한 동시 요구 사이의 우선 순위를 결정하는 능력이 있는 종래의 게이트로 구성되는 조합 논리를 포함한다. 높은 우선 순위 활동에 의해 만족될 수 없는 요구는 대기 라인(50,52 또는54)상의 각 사용자, 처리기 또는 버스 대기 신호의 발생에 의해 지연된다. 사용자, 처리기, 및 버스 데이타와 어드레스 정보는 라인(56,58 및 60)을 통해 데이타 및 어드레스 스위치(62)에 인가된다. RAM 조정기(48)로부터의 제어 라인(64)은 입력과 데이타 및 어드레스 스위치(62)의 출력 사이에 어느 데이타 및 어드레스가 연결되는지를 결정한다. 선택된 어드레스 정보는 데이타 및 어드레스 라인을 통해 랜덤-액세스 메모리(40)에 연결되며, 상기 데이타는 데이타 및 어드레스 라인(66)을 통해 랜덤-액세스 메모리(40)에 또는 메모리로부터 연결된다. 인네이블 신호는 RAM 조정기(48)로부터 랜덤-액세스 메모리(40)에 인네이블 라인(68)을 통해 연결된다.

동작시, 단지 만일 선택 신호가 라인(42,44 및 46)중 한 라인에서 나타나면, RAM 조정기(48)는 데이타 및 어드레스 스위치(62)를 통하여 요청 엘리먼트의 어드레스 및 데이타 라인상의 정보 연결을 인네이블하기 위해 적당한 제어 신호를 데이타 및 어드레스 스위치(62)에 인가시키며, 지시된 어드레스내의 데이타를 판독 또는 기록하기 위하여 인네이블 신호를 랜덤-액세스 메모리(40)에 공급한다. 두개의 선택 신호가 동시에 나타나면, RAM 조정기(48)내의 논리 회로는 랜덤-액세스 메모리(40)로의 액세스를 요구하는 두 엘리먼트중 어느 엘리먼트가 우선 순위를 갖는지 결정하여 낮은 우선 순위 경쟁자를 지체시키기 위해 대기 신호를 발생시킨다. 제어 라인(64)상의 제어 신호는 높은 우선 순위 경쟁자에 의해 액세스를 인네이를 한다.

랜덤-액세스 메모리(40)가 또 하나의 엘리먼트에 의해 액세스되는 동안 도착하는 선택 신호는 두 방법중 한 방법에 의해 처리될 수 있다. 만약 새로운 선택 신호에 절대적인 우선 순위가 할당되면, RAM 액세스는 즉각적으로 새로운 요청기에 할당된다·그러한 기술은 랜덤-액세스 메모리(40)내의 데이타 오염을 방지하기 위하여 지체시키는 많은 양의 데이타를 필요로 한다. 양호한 실시예에서, 한 엘러먼트가 랜덤-액세스메모리(40)를 포착하자마자, 높은 우선 순위 선택 신호가 판독 또는 기록 동작시에 수신될지라도 상기 엘리먼트의 판독 및 기록 동작이 완성되도록 허용된다. 다음 선택 신호는 현행 동작이 완성될 때까지 다음 요청기를 지체시키는 대기 신호에 의해 응답받는다.

메세지 랜덤-액세스 메모리(28)는 임의 종래의 하드웨어를 사용하여 실현될 수 있다. 양호한 실시예에서, 랜덤-액세스 메모리(40)는 다수의 텍사스 인스트루먼트 타입 4256EC4 다이내믹 랜덤-액세스 메모리칩으로 만들어진 배열이다. 한 실시예에서, 16개의 64-킬로비트 칩의 2뱅크는 128000개의 16-비트 워드의 저장 용량을 제공하기 위해 병렬로 사용되어 있다. 또다른 실시예에서, 16개의 256-킬로비트 칩의 4뱅크는 1백만개의 16-비트 워드의 저장 용량을 위해 병렬로 사용되어 있다. RAM 조정기(48)와 데이타 및 어드레스 스위치(62)는 예를들어, 디스크리트 콤포넌트 또는 집적 회로와 같은 임의 종래의 하드웨어로 실현될수 있는 종래의 게이트 회로를 사용한다. 양호한 실시예에서는 집적 회로가 사용되고, 가장 양호한 실시예에서는 알맞게 상호 연결된 프로그램 가능한 배열 논리(PAL)가 사용된다.

또한 제2도를 다시 보면, 프로토콜 랜덤-액세스 메모리(34)와 상태 랜덤-액세스 메모리(38)는 메세지랜덤-액세스 메모리(28)가 3개의 요청기에 의한 액세스를 필요로 하는 반면 그들이 단지 2요청기에 의한 액세스를 필요로 하는 것을 제외하고는 메세지 랜덤-액세스 메모리(28)와 비슷하다. 더구나, 그들은 작은데이타 저장 공간을 필요로 하며, 그들의 랜덤-액세스 메모리는 예를들어, 히다찌 6264 다이내믹 랜덤 액세스 칩에 의해 제공된 것과 같은 16-킬로바이트 용량을 갖고 있다. 프로토콜 랜덤-액세스 메모리(34)의 블럭 다이어그램은 USER이 붙은 라인(42,50 및 56)을 제거하면 제3도에 있는 메세지 랜덤-액세스 메모리(28)의 블럭 다이어그램과 동일하다. 프로토콜 랜덤-액세스 메모리(34)의 기능과 상태 랜덤-액세스 메모리(38)는 메세지 랜덤-액세스 메모리(28)의 기능과 동일하므로 설명을 생략한다.

네트워크 인터페이스 장치(18)내의 나머지 앨리먼트는 현존하거나 또는 후에 개발될 임의 적당한 하드웨어로 실현될 수 있다. 구체성의 목적을 위해, 양호한 실시예는 마이크로 처리기를 사용하여 프로토콜 처리기(36) 및 메세지 처리기(32)를 실행하며, 가장 양호한 실시예에서는 본 발명의 출원의 시기에 구입할 수있는 인텔 80186 마이크로프로세서를 사용하는 것이다. 사용자 인터페이스(30)는 사용자와 네트워크 인터페이스 장치(18)의 나머지 사이에 데이타를 수신하고 전송하는 종래의 다이렉트-메모리-액세스 회로를 포함할 수 있다. 사용자 인터페이스(30)는 ACR/NEMA 표준 인터페이스 문서에 공보된 16-비트 병렬 인터페이스에 대한 제안된 표준에 부착되어 있고, 임의 적당한 하드웨어는 그것을 실행하는데 사용될 수 있지만 여기서 설명할 필요는 없다.

버스 제어기(26)는 예를들어, 인텔 82586과 같은 종래의 버스 제어기이다.

도면을 참조로 설명한 양호한 실시예를 보면, 본 발명이 상술된 실시예에 제한되지 않으며, 본 기술분야에 숙련된 사람이면 본 발명의 영역이나 사상을 벗어나지 않고도 여러 변형이나 수정을 할 수 있음을 이해할 것이다.

Claims (4)

- 버스 디지탈 데이타와 사용자 장치를 접속하는 네트워크 인터페이스 장치가 메세지 처리기, 메모리 랜덤-액세스 메모리, 상기 버스, 상기 메세지 및 상기 사용자 장치로부터 데이타 요청을 서비스하는 상기 메세지 랜덤-액세스 메모리내의 수단, 프로토콜처리기, 프로토콜 랜덤-액세스 메모리 및, 상기 버스 및 상기 프로토콜 처리기로부터 프로토콜 요청을 서비스하는 상기 프로토콜 랜덤-액세스 메모리내의 수단을 포함하며, 상기 메세지 랜덤-액세스 메모리는 전송 또는 수신되는 데이타 패킷의 데이타 부분을 저장하는데 효과적인 수단을 갖고 있으며, 상기 프로토콜 처리기는 전송되는 데이타 패킷을 위한 상기 프로토콜 랜덤-액세스 메모리에 저장을 위한 상기 데이타 패킷중 적어도 헤더 부분을 발생시키고 수신된 메세지의 올바름을 테스트하기에 효과적이며, 상기 메세지 및 랜덤-액세스 메모리중 하나는 다른 요청에 관계없이 그들의 각 데이타 요청의 임의를 서비스하기에 효과적이므로, 프로토콜 및 데이타 처리의 실제 병렬성이 성취되는 것을 특징으로 하는 네트워크 인터페이스 장치.

- 제1항에 있어서, 상기 메세지 처리기와 상기 프로토콜 처리기 사이의 통신을 제공하는 상태 랜덤-액세스 메모리를 더 포함하는 것을 특징으로 하는 네트워크 인터페이스 장치.

- 제1항에 있어서, 상기 프로토콜랜덤-액세스 메모리내의 수단은 랜덤-액세스 메모리와 선행 데이타 요청을 상기 랜덤-액세스 메모리에 연결하고 다음 데이타 요청에 응답하여 대기 신호를 연결시키는 논리수단을 포함하는 것을 특징으로 하는 네트워크 인터페이스 장치.

- 제3항에 있어서, 상기 논리 수단은 우선 순위 규칙에 따라 2개의 동시 요청중 하나를 선택하는 수단을 포함하는 것을 특징으로 하는 네트워크 인터페이스 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US06/809,893 US4858112A (en) | 1985-12-17 | 1985-12-17 | Interface comprising message and protocol processors for interfacing digital data with a bus network |

| US809,893 | 1991-12-18 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR870006478A KR870006478A (ko) | 1987-07-11 |

| KR950002712B1 true KR950002712B1 (ko) | 1995-03-24 |

Family

ID=25202441

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019860010395A KR950002712B1 (ko) | 1985-12-17 | 1986-12-05 | 네트워크 인터페이스 장치 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US4858112A (ko) |

| EP (1) | EP0226975A3 (ko) |

| JP (1) | JPS62164335A (ko) |

| KR (1) | KR950002712B1 (ko) |

| IL (1) | IL79843A0 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100331873B1 (ko) * | 1999-07-02 | 2002-04-09 | 서평원 | 무선 망 연동장치에서의 이더넷 인터페이스 장치 및 이더넷 인터페이스 방법 |

Families Citing this family (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4999771A (en) * | 1987-08-31 | 1991-03-12 | Control Data Corporation | Communications network |

| FR2642246B1 (fr) * | 1988-12-30 | 1991-04-05 | Cit Alcatel | Procede de deblocage d'un systeme multiprocesseurs multibus |

| US5130981A (en) * | 1989-03-22 | 1992-07-14 | Hewlett-Packard Company | Three port random access memory in a network bridge |

| US5249292A (en) * | 1989-03-31 | 1993-09-28 | Chiappa J Noel | Data packet switch using a primary processing unit to designate one of a plurality of data stream control circuits to selectively handle the header processing of incoming packets in one data packet stream |

| US5687314A (en) * | 1989-06-02 | 1997-11-11 | Tele Digital Development, Inc. | Method and apparatus for assisting data bus transfer protocol |

| JPH0795766B2 (ja) * | 1989-06-30 | 1995-10-11 | 株式会社日立製作所 | デジタル・データ通信装置及びそれに使用するデータ通信アダプタ |

| JPH0366241A (ja) * | 1989-08-04 | 1991-03-20 | Matsushita Electric Ind Co Ltd | プロパティ管理方法とその装置 |

| US5214644A (en) * | 1989-10-17 | 1993-05-25 | Matsushita Electric Industrial Co., Ltd. | Electronic device with data transmission function |

| US5151978A (en) * | 1990-03-22 | 1992-09-29 | Square D Company | Lan interface which permits a host computer to obtain data without interrupting a ladder program executing in the interface |

| IL96808A (en) * | 1990-04-18 | 1996-03-31 | Rambus Inc | Introductory / Origin Circuit Agreed Using High-Performance Brokerage |

| FR2662523B1 (fr) * | 1990-05-28 | 1994-08-12 | Copernique | Dispositif controleur d'unites de memoire de masse multiprocesseur a bus central unique. |

| US5134613A (en) * | 1990-06-20 | 1992-07-28 | Standard Microsystems Corporation | Two parety memory access arbitrator |

| FR2668275B1 (fr) * | 1990-10-17 | 1994-12-23 | Bull Sa | Controleur de communication entre un ordinateur et une pluralite de terminaux, appartenant a un reseau de type csma/cd. |

| US5544317A (en) * | 1990-11-20 | 1996-08-06 | Berg; David A. | Method for continuing transmission of commands for interactive graphics presentation in a computer network |

| GB9027249D0 (en) * | 1990-12-17 | 1991-02-06 | Reuters Ltd | Offer matching system |

| JP2566081B2 (ja) * | 1990-12-19 | 1996-12-25 | エイ・ティ・アンド・ティ・コーポレーション | 光パケットのエンコーディング方法及びスイッチングノード |

| JP2501965B2 (ja) * | 1991-02-12 | 1996-05-29 | パイオニア株式会社 | デ―タ転送制御装置 |

| US5276684A (en) * | 1991-07-22 | 1994-01-04 | International Business Machines Corporation | High performance I/O processor |

| WO1993016430A1 (en) * | 1992-02-11 | 1993-08-19 | Koz Mark C | An isdn audiovisual teleservices interface subsystem |

| US5566301A (en) * | 1992-02-11 | 1996-10-15 | Futuretel, Inc. | ISDN audiovisual teleservices interface subsystem |

| IT1254885B (it) * | 1992-04-17 | 1995-10-11 | Metodo per fornire servizi corrispondenti ad un protocollo di comunicazione di livello applicativo utilizzando servizi forniti da una rete on-osi, e rete utilizzante lo stesso. | |

| WO1993023809A1 (en) * | 1992-05-15 | 1993-11-25 | Connective Strategies, Inc. | Isdn-based high speed communication system |

| US6000026A (en) * | 1992-06-22 | 1999-12-07 | Texas Instrument Incorporated | Multiple processor apparatus having a protocol processor intended for the execution of a collection of instructions in a reduced number of operations |

| US5440687A (en) * | 1993-01-29 | 1995-08-08 | International Business Machines Corporation | Communication protocol for handling arbitrarily varying data strides in a distributed processing environment |

| US5692128A (en) * | 1993-06-23 | 1997-11-25 | Microtest, Inc. | Computer network with reliable and efficient removable media services |

| US5533200A (en) * | 1994-03-18 | 1996-07-02 | Intel Corporation | Method and apparatus for transmission of signals over a shared line |

| US5634099A (en) * | 1994-12-09 | 1997-05-27 | International Business Machines Corporation | Direct memory access unit for transferring data between processor memories in multiprocessing systems |

| US5867669A (en) * | 1995-07-03 | 1999-02-02 | General Electric Company | Apparatus and method for upgrading communication functions |

| US5752251A (en) * | 1995-08-07 | 1998-05-12 | Ncr Corporation | Method and apparatus for recovering aborted file (or data) transmission |

| US5761428A (en) * | 1996-07-05 | 1998-06-02 | Ncr Corporation | Method and aparatus for providing agent capability independent from a network node |

| US6145045A (en) * | 1998-01-07 | 2000-11-07 | National Semiconductor Corporation | System for sending and receiving data on a Universal Serial Bus (USB) using a memory shared among a number of end points |

| KR100290729B1 (ko) | 1998-01-07 | 2001-05-15 | 클라크 3세 존 엠. | 유에스비 등시 데이타를 전송 및 수신하는 장치 및 방법 |

| US7412654B1 (en) * | 1998-09-24 | 2008-08-12 | Apple, Inc. | Apparatus and method for handling special windows in a display |

| US6785758B1 (en) * | 2001-06-01 | 2004-08-31 | Advanced Micro Devices, Inc. | System and method for machine specific register addressing in a split transactional unidirectional bus architecture |

| DE10211939A1 (de) * | 2002-03-18 | 2003-10-02 | Sick Ag | Kopplungsvorrichtung zum Ankoppeln von Geräten an ein Bussystem |

| DE10243782A1 (de) * | 2002-09-20 | 2004-03-25 | Sick Ag | Parametrier-/Diagnosesystem für Feldgeräte |

| DE10243783A1 (de) | 2002-09-20 | 2004-03-25 | Sick Ag | Elektronische Vorrichtung für ein Bussystem |

| DE10243781A1 (de) | 2002-09-20 | 2004-03-25 | Sick Ag | Elektronische Vorrichtung für ein Bussystem |

| US7853774B1 (en) | 2005-03-25 | 2010-12-14 | Tilera Corporation | Managing buffer storage in a parallel processing environment |

| US20070011554A1 (en) * | 2005-06-27 | 2007-01-11 | Intel Corporation | Block acknowledgement request apparatus, systems, and methods |

| WO2007014359A2 (en) * | 2005-07-27 | 2007-02-01 | Qualcomm Incorporated | System and method for forward link only messages |

| US8730826B2 (en) * | 2010-11-17 | 2014-05-20 | Ixia | Testing fragment reassembly |

| US11108675B2 (en) | 2018-10-31 | 2021-08-31 | Keysight Technologies, Inc. | Methods, systems, and computer readable media for testing effects of simulated frame preemption and deterministic fragmentation of preemptable frames in a frame-preemption-capable network |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4016541A (en) * | 1972-10-10 | 1977-04-05 | Digital Equipment Corporation | Memory unit for connection to central processor unit and interconnecting bus |

| US4425664A (en) * | 1975-11-26 | 1984-01-10 | Bell Telephone Laboratories, Incorporated | Multiport programmable digital data set |

| US4161786A (en) * | 1978-02-27 | 1979-07-17 | The Mitre Corporation | Digital bus communications system |

| US4241398A (en) * | 1978-09-29 | 1980-12-23 | United Technologies Corporation | Computer network, line protocol system |

| US4387425A (en) * | 1980-05-19 | 1983-06-07 | Data General Corporation | Masterless and contentionless computer network |

| US4393461A (en) * | 1980-10-06 | 1983-07-12 | Honeywell Information Systems Inc. | Communications subsystem having a self-latching data monitor and storage device |

| US4493021A (en) * | 1981-04-03 | 1985-01-08 | The United States Of America As Represented By The Administrator Of The National Aeronautics And Space Administration | Multicomputer communication system |

| US4516239A (en) * | 1982-03-15 | 1985-05-07 | At&T Bell Laboratories | System, apparatus and method for controlling a multiple access data communications system including variable length data packets and fixed length collision-free voice packets |

| US4510594A (en) * | 1983-03-31 | 1985-04-09 | At&T Bell Laboratories | Loop-around testing facilities for a multiline protocol controller |

| US4593282A (en) * | 1983-04-14 | 1986-06-03 | At&T Information Systems Inc. | Network protocol for integrating synchronous and asynchronous traffic on a common serial data bus |

| US4604683A (en) * | 1984-12-10 | 1986-08-05 | Advanced Computer Communications | Communication controller using multiported random access memory |

| US4692918A (en) * | 1984-12-17 | 1987-09-08 | At&T Bell Laboratories | Reliable local data network arrangement |

| US4675865A (en) * | 1985-10-04 | 1987-06-23 | Northern Telecom Limited | Bus interface |

-

1985

- 1985-12-17 US US06/809,893 patent/US4858112A/en not_active Expired - Fee Related

-

1986

- 1986-08-26 IL IL79843A patent/IL79843A0/xx not_active IP Right Cessation

- 1986-12-05 KR KR1019860010395A patent/KR950002712B1/ko active IP Right Grant

- 1986-12-12 EP EP86117321A patent/EP0226975A3/en not_active Withdrawn

- 1986-12-16 JP JP61297863A patent/JPS62164335A/ja active Granted

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100331873B1 (ko) * | 1999-07-02 | 2002-04-09 | 서평원 | 무선 망 연동장치에서의 이더넷 인터페이스 장치 및 이더넷 인터페이스 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| IL79843A0 (en) | 1986-11-30 |

| EP0226975A3 (en) | 1989-09-27 |

| KR870006478A (ko) | 1987-07-11 |

| EP0226975A2 (en) | 1987-07-01 |

| JPH0440904B2 (ko) | 1992-07-06 |

| JPS62164335A (ja) | 1987-07-21 |

| US4858112A (en) | 1989-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR950002712B1 (ko) | 네트워크 인터페이스 장치 | |

| US5764895A (en) | Method and apparatus for directing data packets in a local area network device having a plurality of ports interconnected by a high-speed communication bus | |

| US6308218B1 (en) | Address look-up mechanism in a multi-port bridge for a local area network | |

| US4715030A (en) | Local area network bridge | |

| US5857075A (en) | Method and integrated circuit for high-bandwidth network server interfacing to a local area network | |

| US4750109A (en) | Method and system for expediting multi-packet messages in a computer network | |

| AU635263B2 (en) | Dual-path computer interconnect system with four-ported packet memory control | |

| US5187780A (en) | Dual-path computer interconnect system with zone manager for packet memory | |

| EP0256463B1 (en) | Improved token passing network | |

| US5121382A (en) | Station-to-station full duplex communication in a communications network | |

| EP0355861B1 (en) | Industrialized token passing network | |

| US5361372A (en) | Memory management for data transmission networks | |

| US5020020A (en) | Computer interconnect system with transmit-abort function | |

| US5878028A (en) | Data structure to support multiple transmit packets for high performance | |

| US6157951A (en) | Dual priority chains for data-communication ports in a multi-port bridge for a local area network | |

| US5469438A (en) | Method of transmitting signals in an extendible local area network | |

| US6195334B1 (en) | Apparatus and method for terminating a data transfer in a network switch in response to a detected collision | |

| US6061748A (en) | Method and apparatus for moving data packets between networks while minimizing CPU intervention using a multi-bus architecture having DMA bus | |

| GB2301996A (en) | Intermodular communications using system bus controllers | |

| US6111890A (en) | Gigabuffer lite repeater scheme | |

| US5734675A (en) | Receiver sharing for demand priority access method repeaters | |

| US6256313B1 (en) | Triplet architecture in a multi-port bridge for a local area network | |

| Scott | The SCX channel: A new, supercomputer-class system interconnect | |

| KR100275069B1 (ko) | 에취에스비인터페이스프로그램을이용한노드간메시지전송방법 | |

| KR100249158B1 (ko) | 네트워크(망) 효율증대장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| NORF | Unpaid initial registration fee |