KR910006355B1 - 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치 - Google Patents

채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치 Download PDFInfo

- Publication number

- KR910006355B1 KR910006355B1 KR1019880010505A KR880010505A KR910006355B1 KR 910006355 B1 KR910006355 B1 KR 910006355B1 KR 1019880010505 A KR1019880010505 A KR 1019880010505A KR 880010505 A KR880010505 A KR 880010505A KR 910006355 B1 KR910006355 B1 KR 910006355B1

- Authority

- KR

- South Korea

- Prior art keywords

- enable

- disable

- multiplexer

- control signal

- output

- Prior art date

Links

- 239000000872 buffer Substances 0.000 claims abstract description 81

- 238000010586 diagram Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 3

- 230000007547 defect Effects 0.000 description 1

- 230000003245 working effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/04—Distributors combined with modulators or demodulators

- H04J3/047—Distributors with transistors or integrated circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Theoretical Computer Science (AREA)

- Human Computer Interaction (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Electronic Switches (AREA)

- Time-Division Multiplex Systems (AREA)

Abstract

내용 없음.

Description

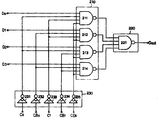

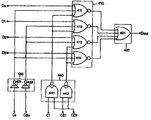

제1도 및 제2도는 4×1 멀티플렉서를 예로들어 설명한 종래의 인에이블/디스에이블 제어장치의 구성도.

제3도는 본 발명의 일실시예로 4×1 멀티플렉서를 예로들어 설명한 인에블/디스에이블 제어장치의 구성도(디스에이블시 인에이블 및 디스에이블 제어단출력이 논리 "0"인 경우).

제4도는 제3도의 타실시예들로 디스에이블시 출력이 논리 "0"이 되는 인에이블 및 디스에이블 제어단의 구성도.

제5도는 본 발명의 이실시예로 4×1 멀티플렉서를 예로들어 설명한 인에이블/디스에이블 제어장치의 구성도(디스에이블시 인에이블 및 디시에이블 제어단 출력이 논리 "1"인 경우).

제6도는 제5도의 타실시예들로 디스에이블 출력이 논리 "1"이 되는 인에이블 및 디스에이블 제어단의 구성도.

* 도면의 주요부분에 대한 부호의 설명

110, 210, 310, 410 : 데이터 입력단 130, 220, 320, 420 : 출력단

140, 230, 330, 430 : 제어신호 입력버퍼단

340∼390, 440∼490 : 인에이블 및 디스에이블 제어단

111∼114, 211∼214, 221, 311∼314, 321, 381, 382, 461, 462 : 낸드게이트

120, 361, 362, 481, 482 : 앤드게이트

131, 371, 372, 411∼414, 491, 492 : 노아게이트

391, 392, 421, 471, 472 : 오아게이트,

141∼144, 231∼235, 331, 332, 383, 384, 393, 394, 431, 432, 483, 484, 493, 494 : 반전 버퍼게이트

341, 342 : 노아버퍼게이트 451, 452 : 오아버퍼게이트

441, 442 : 낸드버퍼게이트 351, 352 : 앤드 버퍼게이트

363, 364, 373, 374, 463, 464, 473, 474 : 비반전 버퍼게이트

본 발명은 다채널 입력 데이터중에서 한채널 입력 데이터만을 출력시키는 m×n 멀티플렉서 출력의 인에블(Enable)/디스에이블(Disable) 제어장치에 관한 것으로, 특히 임의의 채널 선택 제어신호의 반전 및 비반전신호를 인에이블 및 디스에이블 제어신호와 논리게이트로 논리시켜 멀티플렉서 출력의 인에이블 및 디스에이블을 실현할 수 있도록 한채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치에 관한 것이다.

일반적으로 멀티플렉서 출력의 디스에이블이란 입력 데이터레 관계없이 데이터 입력단의 모든 게이트의 출력을 동시에 같은 논리상태로 제어하여 출력이 한 논리상태로 고정되는 것으로 멀티플렉서의 채널 선택 제어신호는 반전 및 비반전신호로 이분되어 데이터 입력단 게이트에 인가되는데 이때 상기 반전 및 비반전 신호는 데이터 입력단 게이트를 이분하여 각기 다른 데이터 입력단 게이트를 구동시키므로 상기 채널 선택 제어신호로는 모든 데이터 입력 게이트를 동시에 같은 논리상태로 제어할 수 없으며 따라서 상기 채널 선택 제어신호 이외에 따로 인에이블 및 디스에이블 제어신호를 멀티플렉서에 인가함으로써 출력의 인에이블 및 디스에이블을 실현할 수 있었는데 종래 멀티플렉서의 출력 인에이블/디스에이블 제어장치로는 멀티플렉서의 출력단 게이트에 상기 인에이블 및 디스에이블 제어신호를 인가하는 방식의 인에이블/디스에이블 제어장치와 데이터 입력단에 상기 인에이블 및 디스에이블 제어신호를 입력 데이터 및 채널 선택 제어신호와 함께 인가하는 방식의 인에이블/디스에이블 제어장치 등이 있었다.

제1도는 4×1 멀티플렉서를 예로들어 상기 4×1 멀티플렉서의 출력단 게이트에 인에이블 및 디스에이블 제어신호를 인가하는 종래의 인에이블/디스에이블 제어장치를 도시한 것으로 상기 회로는 4개의 낸드게이트(111∼114)로 이루어진 데이터 입력단(110)과 앤드게이트(120), 그리고 노아게이트(131)로 이루어진 출력단(130)과 4개의 반전버퍼(141∼144)로 이루어진 제어신호 입력버퍼단(140)으로 구성되어 데이터 입력단자(D0∼D3)를 통해 인가되는 4개의 입력 데이터중에서 하나의 입력 데이터를 선택하여 데이터 출력단자(Dout)를 통해 출력하는데 이때 반전 및 비반전신호로 이분되어 입력되는 채널 선택 제어신호의 비반전신호는 채널 선택 제어 제어신호 입력단자(C0)(C1)를 통해 입력되고 상기 채널 선택 제어신호의 반전신호는 또다른 채널 선택 제어신호 입력단자(CB0)(CB1)를 통해 입력되며 인에이블 및 디스에이블 제어신호는 인에이블 및 디스에이블 제어신호 입력단자(CEN)를 통해 입력되어 출력단(130)으로 인가된다.

여기서 상기 인에이블 및 디스에이블 제어신호가 논리 "0"일 경우 출력단(130)은 또다른 입력, 즉 앤드게이트(120)의 출력상태에 따라 상기 출력단(130)의 출력 상태가 달라지므로 제1도에서 도시한 것과 같은 4×1 멀티플렉서는 4개의 입력 데이터와 채널 선택 제어신호에 의해 선택된 하나의 데이터가 출력되는 정상 동작을 하는 인에이블 상태가 되며 상기 인에이블 및 디스에이블 제어신호가 논리 "1"일 경우는 상기 앤드 게이트(120)의 출력상태에 관계 없이 상기 출력단(130)의 출력이 항상 논리 "0"으로 고정되므로 상기 제1도의 멀티플렉서는 디스에이블 상태가 된다.

한편 제2도는 4×1 멀티플렉서를 예로들어 상기 4×1 멀티플렉서의 데이터 입력단에 인에이블 및 디스에이블 제어신호를 인가하는 또다른 종래의 인에이블/디스에이블 제어장치를 도시한 것으로 상기 회로는 4개의 낸드게이트(211∼214)로 이루어진 데이터 입력단(210)과 낸드게이트(221)로 이루어진 출력단(220), 그리고 5개의 반전버퍼(231∼235)로 이루어진 제어신호 입력버퍼단(230)으로 구성되어 있으며 이때 인에이블 및 디스에이블 제어신호는 채널 선택 제어신호와 함께 상기 제어신호 입력버퍼단(230)으로 인가되어 상기 제어신호 입력버퍼단(230)을 통해 데이터 입력단(210)으로 인가되므로 상기 인에이블 및 디스에이블 제어신호로 멀티플렉서 출력의 인에이블 및 디스에이블을 실현할 수 있다.

즉, 상기 인에이블 및 디스에이블 제어신호가 논리 "0"일 경우 상기 인에이블 및 디스에이블 제어신호는 반전버퍼(235)에 의해 논리 "1"로 반전 되어 데이터 입력단(210)의 각 낸드게이트(211∼214)로 인가되므로 상기 4×1 멀티플렉서는 입력 데이터 및 채널 선택 제어신호에 의해 출력 상태가 결정되는 인에이블 상태가 되고 상기 인에이블 및 디스에이블 제어신호가 논리 "1"일 경우는 상기 인에이블 및 디스에이블 제어신호가 반전버퍼(235)에 의해 논리 "0"으로 반전되어 데이터 입력단(210)의 각 낸드게이트(211∼214)로 인가되므로 상기 데이터 입력단(210)의 모든 게이트들의 출력은 논리 "1"로 고정되며 이로 인해 상기 4×1 멀티플렉서의 출력이 논리 "0"으로 고정되어 디스에이블 상태가 된다.

그런데 상기 제1도 및 제2도에서 도시한 것과 같이 멀티플렉서의 출력을 인에이블 및 디시에이블할 경우 여러가지 결점이 생기게 되는데 상기 제1도의 방식으로 멀티플렉서의 출력을 인에이블 및 디스에이블할 경우는 채널 선택 제어신호와 인에이블 및 디스에이블 제어신호 사이에 경로차로 인한 스큐(Skew)가 발생하게 되므로 출력을 인에이블 및 디스에이블할 때 출력 데이터 파형이 손상되는 결점이 있었고 이로 인해 고속 스위칭에 적합하지 않은 결점이 있었으며 상기 제2도의 방식으로 멀티플렉서의 출력을 인에이블 및 디스에이블할 경우는 데이터 입력단 각 게이트 인에이블 및 디스에이블 제어신호 입력용으로 별도의 입력단자가 필요하게 되므로 회로 및 배선이 복잡해짐과 아울러 게이트의 노이즈 마진(Noise Margin)이 작아지는 결점이 있었고 또한 인에이블 및 디스에이블 제어신호가 입력 데이터의 채널수 만큼의 다수의 입력단 게이트를 동시에 구동하여야 하므로 버퍼게이트가 별도로 필요하게 되어 전력소모가 많아지는 결점이 있었다.

본 발명은 이러한 결점을 감안하여, m×n 멀티플렉서의 출력을 인에이블 및 디스에이블할때 임의의 채널 선택 제어신호의 반전 및 비반전신호를 논리 게이트로 인에이블 및 디스에이블 제어신호와 논리시킴으로써 인에이블 및 디스에이블 제어신호로 반전 및 비반전신호를 동시에 같은 논리상태로 제어할 수 있도록 하여 데이터 입력단 각 게이트에 인에이블 및 디스에이블 제어신호 입력용으로 별도의 입력단자와 인에이블 및 디스에이블 제어신호가 입력 데이터의 채널수 만큼의 다수의 데이터 입력단 게이트를 구동하기 위한 별도의 버퍼게이트가 필요없으면서도 채널 선택 제어신호와 인에이블 및 디스에이블 제어신호 사이에 스큐가 없도록 창안한 것으로, 본 발명의 구성 및 작용효과를 실시예를 통해서 상세히 설명하면 다음과 같다.

제3도는 본 발명의 일실시예로서 4×1 멀티플렉서를 예로들어 상기 멀티플렉서의 출력 디스에이블시 출력이 논리 "0"인 인에이블 및 디스에이블 제어단을 이용해 멀티플렉서의 출력 인에이블 및 디스에이블을 실현한 예를 도시했는데 상기 회로는 4개의 3입력 낸드게이트(311∼314)로 이루어진 데이터 입력단(310)과 4입력 낸드게이트(321)로 이루어진 출력단(320), 그리고 2개의 반전버퍼(331)(332)로 이루어진 제어신호 입력버퍼단(330)과 2개의 2입력 노아버퍼게이트(341)(342)로 이루어진 인에이블 및 디스에이블 제어단(340)으로 구성되어 있으며 상기 제3도의 실시예를 제2도에서 도시한 것과 같은 종래의 인에이블/디스에이블 제어장치와 비교할 때 상기 제2도의 입력버퍼단(230)에서와 채널 선택 제어신호 반전버퍼(233)(234)의 인에이블 및 디스에이블 제어신호 반전버퍼(235)를 인에이블 및 디스에이블 제어단(340)으로 대체함으로써 인에이블 및 디스에이블용 버퍼가 없어졌고 상기 제2도의 데이터 입력단(210)에서의 4입력 낸드 게이트(211∼214)가 3입력 낸드게이트(311∼314)로 대체됨으로써 제3도의 데이터 입력단 게이트의 입력수가 줄었으며 또한 상기 제3도의 2개의 노아버퍼게이트(341)(342)는 제2도의 제어신호 입력버퍼단(230)내의 반전버퍼(233)(234)와 같은 방법으로 연결되었고 남는 2개의 입력은 묶어서 인에이블 및 디스에이블 제어신호를 받아들이도록 구성되었다.

이때 인에이블 및 디스에이블 제신호 입력단자(CEN)를 통해 인가되는 상기 인에이블 및 디스에이블 제어신호가 논리 "0"이 되면 2개의 노아버퍼게이트(341)(342)는 채널 선택 제어신호 입력단자(C1)(CB1)를 통해 인가되는 반전 및 비반전신호에 따라 출력이 결정되는 단순한 반전버퍼로 동작하여 제2도의 인에이블 및 디스에이블 제어신호가 논리 "0"으로서 인에이블된 상태와 같으며 따라서 상기 제3도의 4×1 멀티플렉서는 4개의 입력 데이터와 채널 선택 제어신호에 의해 출력 상태가 결정되는 인에이블 상태가 된다.

또한 상기 인에이블 및 디스에이블 제어신호가 논리 "1"이 되면 채널 선택 제어신호 입력단자(C1)(CB1)를 통해 인가되는 채널 선택 제어신호의 논리 상태에 관계 없이 2개의 2입력 노아버퍼게이트(341)(342)의 출력은 모두 논리 "0"이 되고 상기 논리 "0"인 노아버퍼게이트(341)(342)의 출력은 데이터 입력단(310)의 모든 게이트들의 출력을 논리 "1"로 고정시키며 결과적으로 상기 4×1 멀티플렉서의 출력은 논리 "0"으로 고정되어 디스에이블 상태가 된다.

상기아 같이 제3도의 실시예로 멀티플렉서의 출력을 인에이블 및 디스에이블할 경우 인에이블 및 디스에이블 제어단은 여러가지 형태로 구성될 수 있는데 상기 제3도의 인에이블 및 디스에이블 제어단(340)은 인에이블 및 디스에이블 제어신호가 논리 "1"로서 멀티플렉서의 출력이 디스에이블될 때 상기 인에이블 및 디스에이블 제어단(340)의 출력이 논리 "0"이 되며 상기와 같이 멀티플렉서의 출력 디스에이블시 출력이 논리 "0"이 되는 인에이블 및 디스에이블 제어단으로 인에이블 및 디스에이블을 실현할 경우 논리 "0" 입력에 의해 데이터 입력단의 모든 게이트들의 출력이 고정되어야 하므로 데이터 입력단 게이트는 낸드게이트나 앤드 게이트로 구성해야 한다.

제4도는 제3도의 타실시예로서 상기 제3도에서 도시한 것과 같은 4×1 멀티플렉서의 출력 디스에이블시 출력이 논리 "0"이 되는 인에이블 및 디스에이블 제어단들을 도시했는데 인에이블 및 디스에이블 제어단(340)은 2개의 2입력 노아버퍼게이트(341)(342)로 구성되어 인에이블 및 디스에이블 제어신호가 논리 "0"일 경우는 채널 선택 제어신호를 반전하여 출력시키는 반전버퍼로 동작하고 인에이블 및 디스에이블 제어신호가 논리 "1"일 경우는 채널 선택 제어신호에 관계없이 디스에이블 신호를 출력시켜 멀티플렉서의 출력이 디스에이블되도록 하며 인에이블 및 디스에이블 제어단(350)은 2개의 2입력 앤드버퍼게이트(351)(352)로 구성되어 인에이블 및 디스에이블 제어신호가 논리 "1"일 경우는 채널 선택 제어신호의 입력버퍼로 동작하고 인에이블 및 디스에이블 제어신호가 논리 "0" 일 경우는 디스에이블 신호를 출력한다. 이때 상기 인에이블 및 디스에이블 제어단(340)(350)은 제어신호의 구동능력이 커서 버퍼게이트를 구동함에 무리가 없을때 적합하고 회로가 간단하며 고속 스위칭에 적합하다.

한편 인에이블 및 디스에이블 제어단(360)(370)은 상기 인에이블 및 디스에이블 제어단(350)(340)의 버퍼게이트를 일반 게이트로 대체하고 출력에 비반전 버펴를 달아서 구성되었으며 상기 인에이블 및 디스에이블 제어단(350)(340)과 각각 동일한 동작을 하는데 상기 인에이블 및 디스에이블 제어단(360)은 2개의 앤드게이트(361)(362)와 2개의 비반전버퍼(363)(364)로 구성되어 인에이블 및 디스에이블 제어신호가 논리 "1"일 때 디스에이블 신호를 출력하고 상기 인에이블 및 디스에이블 제어란(370)은 각각 2개의 노아게이트(371)(372)와 비반전 버퍼(373)(374)로 구성되어 인에이블 및 디스에이블 논리 "1"일때 디스에이블 신호를 출력하며 제어신호 구동능력이 작아서 제어신호 입력단의 버퍼게이트를 직접 구동하기에 지연시간이 큰 경우 상기 인에이블 및 디스에이블 제어단(360)(370)에서와 같이 제어신호와 버퍼게이트 사이에 일반 게이트로 제어신호를 비반전시킴으로써 부하의 불균등을 해소하여 동작지연시간을 줄일 수 있다.

또한 또다른 인에이블 및 디스에이블 제어단(380)(390)은 각각 2개의 2입력 낸드게이트 및 오아게이트로서 제어신호를 비반전시키며 출력에 반전버퍼게이트를 달아 구성했는데 상기 인에이블 및 디스에이블 제어단(380)은 각각 2개의 낸드게이트(381)(382)와 반전버퍼게이트(383)(384)로 구성되어 상기 인에이블 및 디스에이블 제어판(350)과 동일한 동작을 하고 상기 인에이블 및 디스에이블 제어단(390)은 각각 2개의 오아게이트(391)(392)와 반전버퍼게이트(393)(394)로 구성되어 상기 인에이블 및 디스에이블 제어단(340)과 동일한 동작을 하며 전술된 인에이블 및 디스에이블 제어단(360)(370)과 마찬가지로 제어신호의 구동능력이 작아서 직접 제어신호 입력버퍼단의 버퍼게이트를 구동하기 어려울 때 적용하여 속도특성을 향상시킬 수 있다.

제5도는 본 발명의 이실시예로서 4×1 멀티플렉서를 예로 들어 상기 멀티플렉서의 출력 디스에이블시 출력이 논리 "1"인 인에이블 및 디스에이블 제어단을 이용해 멀티플렉서의 출력 인에이블 및 디스에이블을 실현한 예를 도시했는데 상기 회로는 4개의 3입력 노아게이트(411∼414)로 이루어진 데이터 입력단(410)과 4입력 오아게이트(421)로 이루어진 출력단(420), 그리고 2개의 반전 버퍼(431)(432)로 이루어진 제어신호 입력버퍼단(430)과 2개의 2입력 낸드게이트(441)(442)로 이루어진 인에이블 및 디스에이블 제어단(440)으로 구성되어 있으며 인에이블 및 디스에이블 제어신호가 논리 "1"일 경우는 상기 2개의 낸드버퍼게이트(441)(442)가 단순한 반전버퍼로 동작하므로 상기 제5도의 4×1 멀티플렉서는 정상동작을 하는 인에이블 상태가 되고 인에이블 및 디스에이블 제어신호가 논리 "0"일 경우는 채널 선택 제어신호의 논리상태에 관계없이 상기 낸드버퍼게이트(441)(442)의 출력이 모두 논리 "1"이 되므로 데이터 입력단(410)의 모든 게이트들의 출력이 논리 "0"으로 고정되어 상기 4×1 멀티플렉서는 디스에이블 상태가 되며 이 경우 논리 "1"입력에 의해 데이터 입력단의 모든 게이트의 출력이 고정되어야 하므로 데이터 입력게이트는 노아게이트나 오아게이트로 구성되어야 한다.

제6도는 제5도의 타실시예로서 상기 제5도에서 도시한 것과 같은 4×1 멀티플렉서의 출력 디스에이블시 출력이 논리 "1"이 되는 인에이블 및 디스에이블 제어단들을 도시했는데 인에이블 및 디스에이블 제어단(440)은 2개의 2입력 낸드버퍼게이트(441)(442)로 구성되어 인에이블 및 디스에이블 제어신호가 논리 "0"일 때 디스에이블 신호를 출력하고 인에이블 및 디스에이블 제어단(450)은 2개의 2입력 오아버퍼게이트(451)(452)로 구성되어 인에이블 및 디스에이블 제어신호가 논리 "1"일 때 디스에이블 신호를 출력하며 이때 상기 인에이블 및 디스에이블 제어단(440)(450)들은 전술된 인에이블 및 디스에이블 제어단(340)(350)에서와 마찬가지로 제어신호의 구동능력이 커서 제어신호 입력단의 버퍼게이트를 직접 구동하기에 무리가 없을 경우에 적합하고 회로가 간단하며 고속 스위칭에 적합하다.

한편 인에이블 및 디스에이블 제어단(460)(470)은 상기 인에이블 및 디스에이블 제어단(440)(450)의 버퍼게이트를 일반게이트로 대체하고 출력에 비반전 버퍼를 달아서 구성되었으며 전체회로 동작은 상기 인에이블 및 디스에이블 제어단(440)(450)과 동일한데 상기 인에이블 및 디스에이블 제어단(460)은 2개의 낸드게이트(461)(462)와 2개의 비반전 버퍼(463)(464)로 구성되고 상기 인에이블 및 디스에이블 제어단(470)은 각각 2개의 오아게이트(471)(472)와 비반전버퍼(473)(474)로 구성된 것으로 제어신호의 구동능력이 작아서 직접 제어신호 입력단의 버퍼게이트를 구동하기 어려울때 적용하여 지연시간을 줄일 수 있다.

또한 인에이블 및 디스에이블 제어단(480)은 각각 2개의 2입력 앤드게이트(481)(482)와 반전버퍼게이트(483)(484)로 구성되고 또다른 인에이블 및 디스에이블 제어단(490)은 각각 2개의 노아게이트(491)(492)와 반전버퍼게이트(493)(494)로 구성된 것으로 전체적으로 상기 인에이블 및 디스에이블 제어단(440)(450)과 각각 동일한 동작을 하며 상기 인에이블 및 디스에이블 제어단(460)(470)과 마찬가지로 제어신호의 구동능력이 작아서 직접 제어신호 입력단의 버퍼게이트를 구동하기 어려울 때 적용하여 속도특성을 향상시킬 수 있다.

이상에서와 같이 본 실시예들은 모두 4×1 멀티플렉서로 설명했으나 본 발명은 모든 m×n 멀티플렉서에 적용할 수 있으며 특히 입력수가 많은 멀티플렉서 일수록 효과적으로 이용할 수 있고 본 발명을 종래의 인에이블/디스에이블 제어장치와 비교할 때 인에이블 및 디스에이블용 버퍼게이트를 없앰으로써 전력소모가 적어지는 효과가 있으며 멀티플렉서의 채널 선택 제어신호와 인에이블 및 디스에이블 제어신호의 경로차에 의한 유효출력 데이터 비트(bit)의 손상을 막아줌으로써 고속 스위칭에 적합한 장점이 있고 데이터 입력단 게이트의 입력수 감소로 게이트의 노이즈 마진이 커지는 효과가 있으며 데이터 입력단 게이트의 입력을 구성하는 다이오드 및 트랜지스터수 감소와 인에이블 및 디스에이블용 버퍼게이트 및 배선이 없어짐에 따라 집적회로 제작시 다이(die) 면적이 줄어드는 효과가 있고 데이터 입력단 게이트의 간략화와 인에이블 및 디스에이블용 버퍼게이트의 불필요, 노이즈 마진의 증대로 집적회로 제작시 수율이 개선되는 효과가 있는 것이다.

Claims (11)

- 다채널 입력 데이터중에서 한채널 입력 데이터만을 출력시키는 m×n 멀티플렉서에 있어서, 채널 선택 제어신호를 반전시켜 한채널이 선택되도록 하는 제어신호 입력버퍼단과, 다채널의 입력 데이터와 채널선택 제어신호, 인에이블 및 디스에이블 제어신호등을 받아 논리시키는 데이터 입력단과, 상기 데이터 입력단의 출력에 따라 한채널의 입력 데이터를 출력시키는 출력단과, 반전 및 비반전신호로 이루어진 채널 선택 제어신호를 논리게이트로 인에이블 및 디스에이블 제어신호와 논리시켜 인에이블 및 디스에이블 제어신호로써 상기 반전 및 비반전신호가 서로 비반전되도록 제어함으로써 데이터 입력단의 모든 게이트들의 출력을 입력에 관계없이 한 논리상태로 고정시키도록 한 인에이블 및 디스에이블 제어단과를 구비하고 상기 인에이블 및 디스에이블 제어단의 출력들이 모두 논리 "0"일 경우에만 디스에이블되고 그 외에는 모두 인에이블되는 제1멀티플렉서와, 상기 출력들이 논리 "1"일 경우에만 디스에이블되고 그 외에는 모두 인에이블되는 제2멀티플렉서를 구성함으로써 전력낭비나 출력데이터의 손상없이 멀티플렉서의 출력을 인에이블 및 디스에이블시킬 수 있도록 한 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제1항에 있어서, 상기 제1멀티플렉서는 4개의 3입력 낸드게이트(311∼314)로 이루어진 데이터 입력단(310)과 4입력 낸드게이트(321)로 이루어진 출력단(320), 그리고 2개의 반전버퍼(331)(332)로 이루어진 제어신호 입력버퍼단(330)과 2개의 2입력 노아버퍼게이트(341)(342)로 이루어진 인에이블 및 디스에이블 제어단(340)으로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제1항에 있어서, 상기 제2멀티플렉서는 4개의 3입력 노아게이트(411∼414)로 이루어진 데이터 입력단(410)과 4입력 오아게이트(421)로 이루어진 출력단(420), 그리고 2개의 반전버퍼(431)(432)로 이루어진 제어신호 입력버퍼단(430)과 2개의 2입력 낸드버퍼게이트(441)(442)로 이루어진 인에이블 및 디스에이블 제어단(440)으로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제2항에 있어서, 상기 인에이블 및 디스에이블 제어단은 2개의 앤드버퍼게이트(351)(352)나 각각 2개씩의 앤드게이트(361)(362) 및 비반전버퍼(363)(364)로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제2항에 있어서, 상기 인에이블 및 디스에이블 제어단은 각각 2개의 노아게이트(371)(372)와 비반전버퍼(373)(374)로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제2항에 있어서, 상기 인에이블 및 디스에이블 제어단은 각각 2개의 낸드게이트(381)(382)와 반전버퍼게이트(383)(384)로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제2항에 있어서, 상기 인에이블 및 디스에이블 제어단은 각각 2개의 오아게이트(391)(392)와 반전버퍼게이트(393)(394)로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제3항에 있어서, 상기 인에이블 및 디스에이블 제어단은 2개의 2입력 오아버퍼게이트(451)(452)나 각각 2개의 오아게이트(471)(472) 및 비반전버퍼(473)(474)로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제3항에 있어서, 상기 인에이블 및 디스에이블 제어단은 2개의 낸드게이트(461)(462)와 2개의 비반전버퍼(463)(464)로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제3항에 있어서, 상기 인에이블 및 디스에이블 제어단은 2개의 2입력 앤드게이트(481)(482)와 반전버퍼게이트(483)(484)로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

- 제3항에 있어서, 상기 인에이블 및 디스에이블 제어단은 각각 2개의 노아게이트(491)(492)와 반전버퍼(493)(494)로 구성된 것을 특징으로 하는 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019880010505A KR910006355B1 (ko) | 1988-08-18 | 1988-08-18 | 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치 |

| JP63314000A JPH0276411A (ja) | 1988-08-18 | 1988-12-14 | チヤネル選択制御信号を利用したマルチプレツクサー出力のイネーブル/デイスエーブル制御装置 |

| US07/393,652 US5045714A (en) | 1988-08-18 | 1989-08-14 | Multiplexer with improved channel select circuitry |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019880010505A KR910006355B1 (ko) | 1988-08-18 | 1988-08-18 | 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR900003724A KR900003724A (ko) | 1990-03-26 |

| KR910006355B1 true KR910006355B1 (ko) | 1991-08-21 |

Family

ID=19276953

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019880010505A KR910006355B1 (ko) | 1988-08-18 | 1988-08-18 | 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US5045714A (ko) |

| JP (1) | JPH0276411A (ko) |

| KR (1) | KR910006355B1 (ko) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5261068A (en) * | 1990-05-25 | 1993-11-09 | Dell Usa L.P. | Dual path memory retrieval system for an interleaved dynamic RAM memory unit |

| US5122685A (en) * | 1991-03-06 | 1992-06-16 | Quicklogic Corporation | Programmable application specific integrated circuit and logic cell therefor |

| US5220213A (en) * | 1991-03-06 | 1993-06-15 | Quicklogic Corporation | Programmable application specific integrated circuit and logic cell therefor |

| US5416367A (en) * | 1991-03-06 | 1995-05-16 | Quicklogic Corporation | Programmable application specific integrated circuit and logic cell therefor |

| US5227678A (en) * | 1991-05-22 | 1993-07-13 | Illinois Institute Of Technology | Fast digital comparison circuit for fuzzy logic operations |

| US5237573A (en) * | 1992-03-31 | 1993-08-17 | Apple Computer, Inc. | Method and apparatus for selectively switching between input signals |

| EP0637182A3 (en) * | 1993-07-30 | 1995-11-29 | At & T Corp | Self-routing optical communication node using sagnac doors. |

| US5615126A (en) * | 1994-08-24 | 1997-03-25 | Lsi Logic Corporation | High-speed internal interconnection technique for integrated circuits that reduces the number of signal lines through multiplexing |

| US5724361A (en) * | 1996-03-12 | 1998-03-03 | Lsi Logic Corporation | High performance n:1 multiplexer with overlap control of multi-phase clocks |

| US5903616A (en) * | 1996-10-08 | 1999-05-11 | Advanced Micro Devices, Inc. | Synchronous clock multiplexer |

| JP3277856B2 (ja) | 1997-08-29 | 2002-04-22 | 日本電気株式会社 | ビタビデコーダ |

| US6111898A (en) * | 1997-12-08 | 2000-08-29 | Intel Corporation | Method of establishing when to propagate the output of a multiplexer |

| US5974058A (en) * | 1998-03-16 | 1999-10-26 | Storage Technology Corporation | System and method for multiplexing serial links |

| US6774693B2 (en) * | 2000-01-18 | 2004-08-10 | Pmc-Sierra, Inc. | Digital delay line with synchronous control |

| JP3727838B2 (ja) * | 2000-09-27 | 2005-12-21 | 株式会社東芝 | 半導体集積回路 |

| US6691689B2 (en) * | 2000-10-13 | 2004-02-17 | Prüfrex-Elektro-Apparatebau, Inh. Helga Müller. Geb Dutschke | Rotation direction detector in ignition equipment of an internal combustion engine |

| US6982589B2 (en) * | 2001-02-28 | 2006-01-03 | Intel Corporation | Multi-stage multiplexer |

| JP2009507425A (ja) * | 2005-09-02 | 2009-02-19 | サイプレス セミコンダクター コーポレイション | ジッタを低減させて信号を多重化する回路、システム、方法 |

| CN115047789A (zh) * | 2021-03-08 | 2022-09-13 | 联华电子股份有限公司 | 机台感测电路板及其运作方法 |

| EP4096098A1 (en) | 2021-05-27 | 2022-11-30 | Samsung Electronics Co., Ltd. | Transmitter circuit including selection circuit |

| CN113609058A (zh) * | 2021-07-30 | 2021-11-05 | 许昌智能继电器股份有限公司 | 一种串口电路 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3262101A (en) * | 1962-01-31 | 1966-07-19 | Melpar Inc | Generalized self-synthesizer |

| US3458240A (en) * | 1965-12-28 | 1969-07-29 | Sperry Rand Corp | Function generator for producing the possible boolean functions of eta independent variables |

| US3538443A (en) * | 1968-06-11 | 1970-11-03 | Us Navy | General purpose logic package |

| US3911399A (en) * | 1970-01-31 | 1975-10-07 | Kurt Maecker | Digital incremental emitter, especially for numerical control of machine tools |

| US3666930A (en) * | 1970-08-05 | 1972-05-30 | Bendix Corp | Time shared positioning system for numerical control |

| US3932816A (en) * | 1974-12-13 | 1976-01-13 | Honeywell Information Systems, Inc. | Multifrequency drive clock |

| US4272829A (en) * | 1977-12-29 | 1981-06-09 | Ncr Corporation | Reconfigurable register and logic circuitry device for selective connection to external buses |

| JPS5636740A (en) * | 1979-09-04 | 1981-04-10 | Nippon Telegr & Teleph Corp <Ntt> | Signal selecting circuit |

| SU991587A1 (ru) * | 1980-09-25 | 1983-01-23 | Восточно-Сибирский технологический институт | Формирователь временных интервалов |

| US4481623A (en) * | 1982-11-23 | 1984-11-06 | Burroughs Corporation | Speed independent arbiter switch employing M-out-of-N codes |

| US4486880A (en) * | 1982-12-09 | 1984-12-04 | Motorola, Inc. | Output multiplexer having one gate delay |

| US4692633A (en) * | 1984-07-02 | 1987-09-08 | International Business Machines Corporation | Edge sensitive single clock latch apparatus with a skew compensated scan function |

| US4593390A (en) * | 1984-08-09 | 1986-06-03 | Honeywell, Inc. | Pipeline multiplexer |

| US4837743A (en) * | 1987-08-17 | 1989-06-06 | Texas Instruments Incorporated | Architecture for memory multiplexing |

| JP2604385B2 (ja) * | 1987-08-28 | 1997-04-30 | 株式会社日立製作所 | ディジタル信号の多重化方法及び装置 |

| EP0310377B1 (en) * | 1987-10-02 | 1992-06-10 | Kawasaki Steel Corporation | Programmable input/output circuit |

| JPH0194608A (ja) * | 1987-10-06 | 1989-04-13 | Toshiba Corp | 巻線方法 |

| JPH0198115A (ja) * | 1987-10-12 | 1989-04-17 | Seiko Epson Corp | 複合型浮上磁気ヘッドの製造方法 |

-

1988

- 1988-08-18 KR KR1019880010505A patent/KR910006355B1/ko not_active IP Right Cessation

- 1988-12-14 JP JP63314000A patent/JPH0276411A/ja active Granted

-

1989

- 1989-08-14 US US07/393,652 patent/US5045714A/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH0572133B2 (ko) | 1993-10-08 |

| JPH0276411A (ja) | 1990-03-15 |

| KR900003724A (ko) | 1990-03-26 |

| US5045714A (en) | 1991-09-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR910006355B1 (ko) | 채널 선택 제어신호를 이용한 멀티플렉서 출력의 인에이블/디스에이블 제어장치 | |

| US4567385A (en) | Power switched logic gates | |

| US4344005A (en) | Power gated decoding | |

| US5598114A (en) | High speed reduced area multiplexer | |

| US5625303A (en) | Multiplexer having a plurality of internal data paths that operate at different speeds | |

| US5396108A (en) | Latch controlled output driver | |

| US5677638A (en) | High speed tristate bus with multiplexers for selecting bus driver | |

| US4761570A (en) | Programmable logic device with programmable signal inhibition and inversion means | |

| US5012126A (en) | High speed CMOS multiplexer having reduced propagation delay | |

| US5317211A (en) | Programmable pin for use in programmable logic devices | |

| US5059830A (en) | Integrated circuit using bus driver having reduced area | |

| US6505226B1 (en) | High speed parallel adder | |

| US5173627A (en) | Circuit for outputting a data signal following an output enable command signal | |

| US6452423B1 (en) | Circuit for avoiding contention in one-hot or one-cold multiplexer designs | |

| US4894558A (en) | Power saving input buffer for use with a gate array | |

| JPH05101674A (ja) | 半導体メモリ | |

| US5377158A (en) | Memory circuit having a plurality of input signals | |

| US6982589B2 (en) | Multi-stage multiplexer | |

| US6326808B1 (en) | Inversion of product term line before or logic in a programmable logic device (PLD) | |

| EP1030450B1 (en) | Tristate differential output stage | |

| US7263054B2 (en) | Sample-and-hold interface circuit of a pickup head | |

| SU1499487A1 (ru) | Мажоритарный элемент | |

| US5513141A (en) | Single port register | |

| US5379442A (en) | Fast primary and feedback path in a programmable logic circuit | |

| JPH11339491A (ja) | シフトレジスタ装置及びそのシフトレジスタ装置を利用した負荷駆動装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| N231 | Notification of change of applicant | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 19980725 Year of fee payment: 8 |

|

| LAPS | Lapse due to unpaid annual fee |