KR20220104663A - 반도체 메모리 장치 및 이의 제조 방법 - Google Patents

반도체 메모리 장치 및 이의 제조 방법 Download PDFInfo

- Publication number

- KR20220104663A KR20220104663A KR1020220084479A KR20220084479A KR20220104663A KR 20220104663 A KR20220104663 A KR 20220104663A KR 1020220084479 A KR1020220084479 A KR 1020220084479A KR 20220084479 A KR20220084479 A KR 20220084479A KR 20220104663 A KR20220104663 A KR 20220104663A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- source

- mold

- cell substrate

- structures

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/20—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B41/23—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B41/27—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

-

- H01L27/11556—

-

- H01L27/11521—

-

- H01L27/11526—

-

- H01L27/11568—

-

- H01L27/11573—

-

- H01L27/11582—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/20—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B43/23—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B43/27—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/40—EEPROM devices comprising charge-trapping gate insulators characterised by the peripheral circuit region

Landscapes

- Non-Volatile Memory (AREA)

Abstract

소자 성능 및 신뢰성을 개선할 수 있는 반도체 메모리 장치를 제공하는 것이다. 반도체 메모리 장치는 기판, 기판 상의 주변 로직 구조체, 주변 로직 구조체 상의 셀 기판, 셀 기판 상에 배치되고, 제1 방향으로 이격되는 복수의 소오스 구조체로, 각각의 소오스 구조체는 제1 소오스 층과, 제1 소오스 층 상의 제2 소오스 층을 포함하는 복수의 소오스 구조체, 소오스 구조체 상에, 각각의 소오스 구조체에 대응되게 배치되는 복수의 몰드 구조체로, 절연층과 반도체 층이 교대로 적층되는 복수의 몰드 구조체, 셀 기판 상에, 제1 방향으로 인접하는 몰드 구조체를 분리하는 분리 구조체, 셀 기판 상에, 몰드 구조체를 관통하고 제2 방향으로 연장된 복수의 채널 구조체, 및 소오스 구조체 하부에 배치되고, 분리 구조체와 상기 제2 방향으로 중첩되는 도전성 블로킹 막을 포함한다.

Description

본 발명은 반도체 메모리 장치 및 이의 제조 방법에 관한 것이다.

데이터 저장을 필요로 하는 전자 시스템에서 고용량의 데이터를 저장할 수 있는 반도체 장치가 요구되고 있다. 이에 따라, 반도체 장치의 데이터 저장 용량을 증가시킬 수 있는 방안이 연구되고 있다. 예를 들어, 반도체 장치의 데이터 저장 용량을 증가시키기 위한 방법 중 하나로써, 2차원적으로 배열되는 메모리 셀들 대신에 3차원적으로 배열되는 메모리 셀들을 포함하는 반도체 장치가 제안되고 있다.

본 발명이 해결하고자 하는 기술적 과제는 제품 신뢰성이 향상된 반도체 메모리 장치를 제공하는 것이다.

본 발명이 해결하고자 하는 다른 기술적 과제는 제품 신뢰성이 향상된 반도체 메모리 장치의 제조 방법을 제공하는 것이다.

본 발명의 기술적 과제들은 이상에서 언급한 기술적 과제로 제한되지 않으며, 언급되지 않은 또 다른 기술적 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

상기 과제를 해결하기 위한 본 발명의 반도체 메모리 장치의 일 태양(aspect)은, 기판, 기판 상의 주변 로직 구조체, 주변 로직 구조체 상의 셀 기판, 셀 기판 상에 배치되고, 제1 방향으로 이격되는 복수의 소오스 구조체로, 각각의 소오스 구조체는 제1 소오스 층과, 제1 소오스 층 상의 제2 소오스 층을 포함하는 복수의 소오스 구조체, 소오스 구조체 상에, 각각의 소오스 구조체에 대응되게 배치되는 복수의 몰드 구조체로, 절연층과 반도체 층이 교대로 적층되는 복수의 몰드 구조체, 셀 기판 상에, 상기 제1 방향으로 인접하는 몰드 구조체를 분리하는 분리 구조체, 셀 기판 상에, 몰드 구조체를 관통하고 제2 방향으로 연장된 복수의 채널 구조체, 및 소오스 구조체 하부에 배치되고, 분리 구조체와 상기 제2 방향으로 중첩되는 도전성 블로킹 막을 포함한다.

상기 다른 과제를 해결하기 위한 본 발명의 반도체 메모리 장치의 제조 방법의 일 태양은 주변 로직 구조체 상에 셀 기판이 적층되고, 셀 기판 내에 리세스를 형성하고, 리세스 상에 라이너 막과 필링 막을 순차적으로 적층하여 도전성 블로킹 막을 형성하고, 셀 기판 및 상기 도전성 블로킹 막 상에 희생 반도체 층과 제1 소오스 층을 적층하고, 제1 소오스 층 상에 몰드 절연층과 반도체 층을 교대로 적층하여 몰드 구조체를 형성하고, 몰드 구조체와, 제1 소오스 층과, 희생 반도체 층을 관통하는 채널 구조체로, 정보 저장막과 반도체 패턴을 포함하는 채널 구조체를 형성하고, 몰드 구조체와, 제1 소오스 층과, 희생 반도체 층을 관통하는 워드 라인 컷을 형성하여 희생 반도체 층을 노출시키고, 희생 반도체 층을 제거하여 정보 저장막의 일부를 노출시키고, 정보 저장막의 일부를 제거하고, 희생 반도체 층이 제거된 영역에 반도체 패턴과 접촉하는 제2 소오스 층을 형성하고, 셀 기판 상에, 제1 방향으로 인접하는 몰드 구조체를 분리하는 분리 구조체를 형성하는 것을 포함하되, 분리 구조체는 제2 방향으로 상기 도전성 블로킹 막과 중첩된다.

본 발명의 기타 구체적인 사항들은 상세한 설명 및 도면들에 포함되어 있다.

도 1은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 예시적인 블록도이다.

도 2는 몇몇 실시예에 따른 반도체 메모리 장치를 설명하기 위한 예시적인 회로도이다.

도 3은 몇몇 실시예에 따른 반도체 메모리 장치를 설명하기 위한 예시적인 레이아웃도이다.

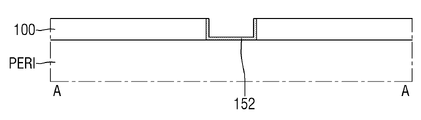

도 4는 도 3의 A - A를 따라 절단한 단면도이다.

도 5는 도 4의 S1 영역을 설명하기 위한 확대도이다.

도 6은 도 3의 B - B를 따라 절단한 단면도이다.

도 7은 도 6의 S2 영역을 설명하기 위한 확대도이다.

도 8은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다.

도 9는 도 8의 S3 영역을 설명하기 위한 확대도이다.

도 10은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다.

도 11은 도 10의 S5 영역을 설명하기 위한 확대도이다.

도 12는 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다.

도 13은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다.

도 14 내지 도 27은 몇몇 실시예에 따른 반도체 메모리 장치의 제조 방법을 설명하기 위한 중간 단계 도면들이다.

도 2는 몇몇 실시예에 따른 반도체 메모리 장치를 설명하기 위한 예시적인 회로도이다.

도 3은 몇몇 실시예에 따른 반도체 메모리 장치를 설명하기 위한 예시적인 레이아웃도이다.

도 4는 도 3의 A - A를 따라 절단한 단면도이다.

도 5는 도 4의 S1 영역을 설명하기 위한 확대도이다.

도 6은 도 3의 B - B를 따라 절단한 단면도이다.

도 7은 도 6의 S2 영역을 설명하기 위한 확대도이다.

도 8은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다.

도 9는 도 8의 S3 영역을 설명하기 위한 확대도이다.

도 10은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다.

도 11은 도 10의 S5 영역을 설명하기 위한 확대도이다.

도 12는 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다.

도 13은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다.

도 14 내지 도 27은 몇몇 실시예에 따른 반도체 메모리 장치의 제조 방법을 설명하기 위한 중간 단계 도면들이다.

도 1은 몇몇 실시예에 따른 반도체 메모리 장치를 설명하기 위한 예시적인 블록도이다.

도 1을 참조하면, 몇몇 실시예에 따른 반도체 메모리 장치(10)는 메모리 셀 어레이(20) 및 주변 회로(30)를 포함한다.

메모리 셀 어레이(20)는 복수의 메모리 셀 블록들(BLK1~BLKn)을 포함할 수 있다. 각각의 메모리 셀 블록들(BLK1~BLKn)은 복수의 메모리 셀들을 포함할 수 있다. 메모리 셀 어레이(20)는 비트 라인(BL), 워드 라인(WL), 적어도 하나의 스트링 선택 라인(SSL) 및 적어도 하나의 그라운드 선택 라인(GSL)을 통해 주변 회로(30)에 연결될 수 있다. 구체적으로, 메모리 셀 블록들(BLK1~BLKn)은 워드 라인(WL), 스트링 선택 라인(SSL) 및 그라운드 선택 라인(GSL)을 통해 로우 디코더(33)에 연결될 수 있다. 또한, 메모리 셀 블록들(BLK1~BLKn)은 비트 라인(BL)을 통해 페이지 버퍼(35)에 연결될 수 있다.

주변 회로(30)는 반도체 메모리 장치(10)의 외부로부터 어드레스(ADDR), 커맨드(CMD) 및 제어 신호(CTRL)를 수신할 수 있고, 반도체 메모리 장치(10)의 외부의 장치와 데이터(DATA)를 송수신할 수 있다. 주변 회로(30)는 제어 로직(37), 로우 디코더(33) 및 페이지 버퍼(35)를 포함할 수 있다. 도시되지 않았으나, 주변 회로(30)는 입출력 회로, 반도체 메모리 장치(10)의 동작에 필요한 다양한 전압들을 생성하는 전압 생성 회로, 및 메모리 셀 어레이(20)로부터 독출된 데이터(DATA)의 오류를 정정하기 위한 오류 정정 회로 등 다양한 서브 회로들을 더 포함할 수도 있다.

제어 로직(37)은 로우 디코더(33), 상기 입출력 회로 및 상기 전압 생성 회로에 연결될 수 있다. 제어 로직(37)은 반도체 메모리 장치(10)의 전반적인 동작을 제어할 수 있다. 제어 로직(37)은 제어 신호(CTRL)에 응답하여 반도체 메모리 장치(10) 내에서 사용되는 각종 내부 제어 신호들을 생성할 수 있다. 예를 들어, 제어 로직(37)은 프로그램(program) 동작 또는 소거(erase) 동작 등의 메모리 동작 수행 시 워드 라인(WL) 및 비트 라인(BL)으로 제공되는 전압 레벨을 조절할 수 있다.

로우 디코더(33)는 어드레스(ADDR)에 응답하여 복수의 메모리 셀 블록들(BLK1~BLKn) 중 적어도 하나를 선택할 수 있으며, 선택된 메모리 셀 블록들(BLK1~BLKn)의 적어도 하나의 워드 라인(WL), 적어도 하나의 스트링 선택 라인(SSL) 및 적어도 하나의 그라운드 선택 라인(GSL)을 선택할 수 있다. 또한, 로우 디코더(33)는 선택된 메모리 셀 블록들(BLK1~BLKn)의 워드 라인(WL)에 메모리 동작 수행을 위한 전압을 전달할 수 있다.

페이지 버퍼(35)는 비트 라인(BL)을 통해 메모리 셀 어레이(20)에 연결될 수 있다. 페이지 버퍼(35)는 기입 드라이버(writer driver) 또는 감지 증폭기(sense amplifier)로 동작할 수 있다. 구체적으로, 프로그램 동작 수행 시, 페이지 버퍼(35)는 기입 드라이버로 동작하여 메모리 셀 어레이(20)에 저장하고자 하는 데이터(DATA)에 따른 전압을 비트 라인(BL)에 인가할 수 있다. 한편, 독출 동작 수행 시, 페이지 버퍼(35)는 감지 증폭기로 동작하여 메모리 셀 어레이(20)에 저장된 데이터(DATA)를 감지할 수 있다.

도 2는 몇몇 실시예에 따른 반도체 메모리 장치를 설명하기 위한 예시적인 회로도이다.

도 2를 참조하면, 몇몇 실시예에 따른 반도체 메모리 장치의 메모리 셀 어레이(예컨대, 도 1의 20)는 공통 소오스 라인(CSL), 복수의 비트 라인(BL)들 및 복수의 셀 스트링(CSTR)들을 포함한다.

공통 소오스 라인(CSL)은 제1 방향(X)으로 연장될 수 있다. 몇몇 실시예에서, 복수의 공통 소오스 라인(CSL)들은 2차원적으로 배열될 수 있다. 예를 들어, 복수의 공통 소오스 라인(CSL)들은 서로 이격되어 각각 제1 방향(X)으로 연장될 수 있다. 공통 소오스 라인(CSL)들에는 전기적으로 동일한 전압이 인가될 수도 있고, 또는 서로 다른 전압이 인가되어 별개로 제어될 수도 있다.

복수의 비트 라인(BL)들은 2차원적으로 배열될 수 있다. 예를 들어, 비트 라인(BL)들은 서로 이격되어 제1 방향(X)과 교차하는 제2 방향(Y)으로 각각 연장될 수 있다. 각각의 비트 라인(BL)들에는 복수의 셀 스트링(CSTR)들이 병렬로 연결될 수 있다. 셀 스트링(CSTR)들은 공통 소오스 라인(CSL)에 공통으로 연결될 수 있다. 즉, 비트 라인(BL)들과 공통 소오스 라인(CSL) 사이에 복수의 셀 스트링(CSTR)들이 배치될 수 있다.

각각의 셀 스트링(CSTR)들은 공통 소오스 라인(CSL)에 접속되는 그라운드 선택 트랜지스터(GST), 비트 라인(BL)에 접속되는 스트링 선택 트랜지스터(SST) 및 그라운드 선택 트랜지스터(GST)와 스트링 선택 트랜지스터(SST) 사이에 배치되는 복수의 메모리 셀 트랜지스터들(MCT)을 포함할 수 있다. 각각의 메모리 셀 트랜지스터들(MCT)은 데이터 저장 소자(data storage element)를 포함할 수 있다. 그라운드 선택 트랜지스터(GST), 스트링 선택 트랜지스터(SST) 및 메모리 셀 트랜지스터들(MCT)은 직렬로 연결될 수 있다.

공통 소오스 라인(CSL)은 그라운드 선택 트랜지스터(GST)들의 소오스들에 공통으로 연결될 수 있다. 또한, 공통 소오스 라인(CSL)과 비트 라인(BL) 사이에는 그라운드 선택 라인(GSL), 복수의 워드 라인들(WL11~WL1n, WL21~WL2n) 및 스트링 선택 라인(SSL)이 배치될 수 있다. 그라운드 선택 라인(GSL)은 그라운드 선택 트랜지스터(GST)의 반도체 층으로 사용될 수 있고, 워드 라인들(WL11~WL1n, WL21~WL2n)은 메모리 셀 트랜지스터들(MCT)의 반도체 층으로 사용될 수 있고, 스트링 선택 라인(SSL)은 스트링 선택 트랜지스터(SST)의 반도체 층으로 사용될 수 있다.

몇몇 실시예에서, 공통 소오스 라인(CSL)과 그라운드 선택 트랜지스터(GST) 사이에 소거 제어 트랜지스터(ECT)가 배치될 수 있다. 공통 소오스 라인(CSL)은 소거 제어 트랜지스터(ECT)들의 소오스들에 공통으로 연결될 수 있다. 또한, 공통 소오스 라인(CSL)과 그라운드 선택 라인(GSL) 사이에는 소거 제어 라인(ECL)이 배치될 수 있다. 소거 제어 라인(ECL)은 소거 제어 트랜지스터(ECT)의 반도체 층으로 사용될 수 있다. 소거 제어 트랜지스터(ECT)들은 게이트 유도 드레인 누설(GIDL; Gate Induced Drain Leakage)을 발생시켜 상기 메모리 셀 어레이의 소거 동작을 수행할 수 있다.

도 3은 몇몇 실시예에 따른 반도체 메모리 장치를 설명하기 위한 예시적인 레이아웃도이다. 도 4는 도 3의 A - A를 따라 절단한 단면도이다. 도 5는 도 4의 S1 영역을 설명하기 위한 확대도이다. 도 6은 도 3의 B - B를 따라 절단한 단면도이다. 도 7은 도 6의 S2 영역을 설명하기 위한 확대도이다.

도 3 내지 도 7을 참고하면, 몇몇 실시예에 따른 반도체 메모리 장치는 메모리 셀 영역(CELL) 및 주변 회로 영역(PERI)을 포함한다.

메모리 셀 영역(CELL)은 셀 기판(100), 제1 몰드 구조체(MS1), 제1 층간 절연막(140a), 채널 구조체(CS), 워드 라인 컷(WLC), 셀 컨택 구조체(170), 비트 라인(BL), 비트 라인 컨택(182) 및 배선간 절연막(142)을 포함할 수 있다.

셀 기판(100)은 예를 들어, 실리콘 기판, 게르마늄 기판 혹은 실리콘-게르마늄 기판 등과 같은 반도체 기판을 포함할 수 있다. 또는, 셀 기판(100)은 실리콘-온-인슐레이터(Silicon-On-Insulator: SOI) 기판 혹은 게르마늄-온-인슐레이터(Germanium-On-Insulator: GOI) 기판 등을 포함할 수도 있다. 몇몇 실시예에서, 셀 기판(100)은 불순물을 포함할 수 있다. 예를 들어, 셀 기판(100)은 n형 불순물(예컨대, 인(P), 비소(As) 등)을 포함할 수 있다.

셀 기판(100)은 셀 어레이 영역(R1) 및 확장 영역(R2)을 포함할 수 있다.

셀 어레이 영역(R1)에는 복수의 메모리 셀들을 포함하는 메모리 셀 어레이(예컨대, 도 1의 20)가 형성될 수 있다. 예를 들어, 셀 어레이 영역(R1)에는 후술되는 채널 구조체(CS), 비트 라인(BL) 및 반도체 층들(120) 등이 배치될 수 있다. 이하의 설명에서, 상기 메모리 셀 어레이가 배치되는 셀 기판(100)의 표면은 셀 기판(100)의 전면(front side)으로 지칭될 수 있다. 반대로, 셀 기판(100)의 전면과 반대되는 셀 기판(100)의 표면은 셀 기판(100)의 후면(back side)으로 지칭될 수 있다.

확장 영역(R2)은 셀 어레이 영역(R1)의 주변에 배치될 수 있다. 확장 영역(R2)에는 후술되는 반도체 층들(120)이 계단형으로 적층될 수 있다.

제1 몰드 구조체(MS1)는 셀 기판(100)의 전면(예컨대, 상면) 상에 형성될 수 있다. 제1 몰드 구조체(MS1)는 셀 기판(100) 상에 교대로 적층되는 복수의 반도체 층들(120) 및 복수의 몰드 절연층들(110)을 포함할 수 있다. 각각의 반도체 층들(120) 및 각각의 몰드 절연층들(110)은 셀 기판(100)의 상면과 평행하게 연장되는 층상 구조일 수 있다. 반도체 층들(120)은 몰드 절연층(110)들에 의해 상호 이격되어 셀 기판(100) 상에 차례로 적층될 수 있다.

반도체 층들(120)은 확장 영역(R2)에서 계단형으로 적층될 수 있다. 예를 들어, 반도체 층들(120)은 제1 방향(X)에서 서로 다른 길이로 연장되어 단차를 가질 수 있다. 몇몇 실시에에서, 반도체 층들(120)은 제2 방향(Y)에서 단차를 가질 수도 있다. 이에 따라, 각각의 반도체 층들(120)은 다른 반도체 층들로부터 노출되는 패드 영역을 포함할 수 있다.

반도체 층(120)은 폴리 실리콘을 포함한다. 몇몇 실시예에서, 반도체 층(120)은 N형 불순물이 도핑된 폴리 실리콘일 수 있고, P형 불순물이 도핑된 폴리 실리콘 일 수 있다.

몇몇 실시예에서, 셀 기판(100) 상에 소오스 구조체(SS1)가 형성될 수 있다. 소오스 구조체(SS1)는 셀 기판(100)과 제1 몰드 구조체(MS1) 사이에 개재될 수 있다. 예를 들어, 소오스 구조체(SS1)는 셀 기판(100)의 상면을 따라 연장될 수 있다. 소오스 구조체(SS1)는 채널 구조체(CS)의 반도체 패턴(130)과 접속되도록 형성될 수 있다. 예를 들어, 도 7에 도시된 것처럼, 소오스 구조체(SS1)는 정보 저장막(132)을 관통하여 반도체 패턴(130)과 접촉할 수 있다. 소오스 구조체(SS1)는 예를 들어, 불순물이 도핑된 폴리 실리콘 또는 금속을 포함할 수 있으나, 이에 제한되는 것은 아니다.

소오스 구조체(SS1)는 복수개 일 수 있다. 소오스 구조체(SS1)는 제1 방향(X)으로 이격될 수 있다. 인접하는 소오스 구조체(SS1) 사이에 후술할 분리 구조체(140b)가 배치될 수 있다.

제1 몰드 구조체(MS1)는 복수개 일 수 있다. 제1 몰드 구조체(MS1)는 제1 방향(X)으로 이격되어 배치될 수 있다. 복수의 제1 몰드 구조체(MS1)는 소오스 구조체(SS1) 상에 각각의 소오스 구조체에 대응되게 배치될 수 있다. 인접하는 제1 몰드 구조체(MS1) 사이에 후술할 분리 구조체(140b)가 배치될 수 있다.

몇몇 실시예에서, 셀 기판(100) 내에 도전성 블로킹 막(150)이 형성될 수 있다. 도전성 블로킹 막(150)은 주변 회로 영역(PERI) 상에 배치될 수 있다. 도전성 블로킹 막(150)은 제2 방향(Y)으로 연장될 수 있다. 도전성 블로킹 막(150)은 셀 기판(100) 사이에 배치될 수 있다. 도전성 블로킹 막(150)은 셀 기판(100)을 분리할 수 있다. 셀 기판(100)상에, 셀 기판(100) 각각에 대응되게 소오스 구조체(SS1) 및 제1 몰드 구조체(MS1)가 배치될 수 있다.

몇몇 실시예에서, 도전성 블로킹 막(150)의 상면(150_US)은 셀 기판(100)의 상면(100_US)과 동일 평면에 배치될 수 있다. 도전성 블로킹 막(150)의 상면(150_US)의 일부는 소오스 구조체(SS1)와 접촉할 수 있다. 도전성 블로킹 막(150)의 상면(150_US)의 일부는 분리 구조체(140b)와 접촉할 수 있다. 다르게 표현하면, 도전성 블로킹 막(150)의 일부는 소오스 구조체(SS1)와 제3 방향(Z)으로 중첩될 수 있다. 도전성 블로킹 막(150)의 일부는 분리 구조체(140b)와 제3 방향(Z)으로 중첩될 수 있다. 여기서 제3 방향(Z)은 반도체 메모리 장치의 두께 방향일 수 있다.

도전성 블로킹 막(150)은 제1 방향(X)으로 제2 거리(d2)를 가질 수 있다. 도전성 블로킹 막(150)의 제2 거리(d2)는 인접하는 셀 기판(100) 사이의 거리일 수 있다.

도전성 블로킹 막(150)의 측벽은 셀 기판(100)과 접촉할 수 있다. 도전성 블로킹 막(150)은 셀 기판(100)과 전기적으로 연결될 수 있다. 도전성 블로킹 막(150) 및 셀 기판(100)은 반도체 메모리 장치의 공통 소오스 라인(예컨대, 도 2의 CSL)으로 제공될 수 있다. 도전성 블로킹 막(150)은 식각 공정에서 주변 회로 영역(PERI)을 보호할 수 있다.

몇몇 실시예에서, 도전성 블로킹 막(150)은 라이너 막(152)과 필링 막(151)을 포함할 수 있다.

라이너 막(152)은 셀 기판(100)의 측벽 및 주변 회로 영역(PERI) 상에 컨포멀 하게 형성될 수 있다. 라이너 막(152)은 제2 방향(Y)으로 연장될 수 있다. 라이너 막(152)은 셀 기판(100)의 측벽과 접촉할 수 있다. 라이너 막(152)은 셀 기판(100)과 오믹 컨택(ohmic contact)을 형성할 수 있다.

라이너 막(152)은 티타늄 질화물(TiN), 티타늄 실리콘 질화물(TiSiN) 등 도전성 금속 질화물을 포함할 수 있다. 다만, 본 발명의 기술적 사상이 이에 제한되는 것은 아니다.

필링 막(151)은 라이너 막(152) 상에 배치될 수 있다. 필링 막(151)은 제2 방향(Y)으로 연장될 수 있다. 필링 막(151)은 텅스텐(W), 알루미늄(Al), 구리(Cu), 코발트(Co), 티타늄(Ti) 등 도전성 금속을 포함할 수 있다. 다만 본 발명의 기술적 사상이 이에 제한되는 것은 아니다.

도시되지 않았지만, 금속 실리사이드막이 도전성 블로킹 막(150)과 셀 기판(100) 사이의 경계를 따라 배치될 수 있다.

몇몇 실시예에서, 도전성 블로킹 막(150) 상에 분리 구조체(140b)가 배치될 수 있다. 분리 구조체(140b)는 소오스 구조체(SS1) 사이 및 제1 몰드 구조체(MS1)사이에 배치될 수 있다. 분리 구조체(140b)는 제3 방향(Z)로 연장될 수 있다. 도시된 것과 달리, 몇몇 실시예에서, 분리 구조체(140b)의 제1 방향(X)의 폭은 셀 기판(100)에서 멀어질수록 증가할 수 있다.

분리 구조체(140b)는 제1 방향(X)으로 인접하는 소오스 구조체(SS1)를 분리할 수 있다. 분리 구조체(140b)는 제1 방향(X)으로 인접하는 제1 몰드 구조체(MS1)를 분리할 수 있다. 인접하는 제1 몰드 구조체(MS1)는 분리 구조체(140b)에 의해 전기적으로 연결되지 않을 수 있다.

분리 구조체(140b)는 제1 방향(X)으로 제1 거리(d1)를 갖는다. 제1 거리는 인접하는 소오스 구조체(SS1) 사이의 거리일 수 있다. 몇몇 실시예에서, 분리 구조체(140b)의 제1 거리(d1)는 도전성 블로킹 막(150)의 제2 거리(d2)보다 작을 수 있다. 다른 실시예에서, 제1 거리(d1)는 제2 거리(d2)와 동일할 수 있다.

분리 구조체(140b)는 후술할 제1 층간 절연막(140a)과 동일한 물질로 형성될 수 있다. 분리 구조체(140b)는 예를 들어, 실리콘 산화물, 실리콘 산질화물 및 실리콘 산화물보다 유전율이 작은 저유전율(low-k) 물질 중 적어도 하나를 포함할 수 있으나, 이에 제한되는 것은 아니다.

셀 컨택 구조체(170)는 확장 영역(R2)에서 반도체 층(120)과 연결될 수 있다. 셀 컨택 구조체(170)는 제3 방향(Z)으로 연장되어 제1 몰드 구조체(MS1)를 관통할 수 있다. 셀 컨택 구조체(170)는 각각의 반도체 층(120)의 패드 영역과 접속될 수 있다.

각각의 반도체 층들(120)은 도 2의 소거 제어 라인(ECL), 그라운드 선택 라인(GSL), 복수의 워드 라인들(WL11~WL1n, WL21~WL2n) 및 스트링 선택 라인(SSL)에 대응될 수 있다. 몇몇 실시예에서, 소거 제어 라인(ECL)은 생략될 수도 있다. 또한 몇몇 실시예에서, 그라운드 선택 라인(GSL)에 인접한 반도체 층 또는 스트링 선택 라인(SSL)에 인접한 반도체 층은 더미 반도체 층일 수 있다.

몰드 절연층(110)은 절연 물질, 예를 들어, 실리콘 산화물, 실리콘 질화물 및 실리콘 산질화물 중 적어도 하나를 포함할 수 있으나, 이에 제한되는 것은 아니다. 일례로, 몰드 절연층(110)은 실리콘 산화물을 포함할 수 있다.

제1 층간 절연막(140a)은 셀 기판(100) 상에 형성될 수 있다. 제1 층간 절연막(140a)은 제1 몰드 구조체(MS1)를 덮을 수 있다. 제1 층간 절연막(140a)은 예를 들어, 실리콘 산화물, 실리콘 산질화물 및 실리콘 산화물보다 유전율이 작은 저유전율(low-k) 물질 중 적어도 하나를 포함할 수 있으나, 이에 제한되는 것은 아니다.

채널 구조체(CS)는 셀 어레이 영역(R1)의 제1 몰드 구조체(MS1) 내에 형성될 수 있다. 채널 구조체(CS)는 셀 기판(100)의 상면과 교차하는 수직 방향(이하, 제3 방향(Z))으로 연장되어 제1 몰드 구조체(MS1)를 관통할 수 있다. 예를 들어, 채널 구조체(CS)는 제3 방향(Z)으로 연장되는 필러(pillar) 모양(예컨대, 원기둥 모양)일 수 있다. 몇몇 실시예에서, 채널 구조체(CS)의 폭은 셀 기판(100)으로부터 멀어질수록 증가할 수 있다.

채널 구조체(CS)는 반도체 패턴(130) 및 정보 저장막(132)을 포함할 수 있다.

반도체 패턴(130)은 제3 방향(Z)으로 연장되어 제1 몰드 구조체(MS1)를 관통할 수 있다. 반도체 패턴(130)은 컵(cup) 형상인 것만이 도시되었으나, 이는 예시적인 것일 뿐이다. 예를 들어, 반도체 패턴(130)은 원통 형상, 사각통 형상, 속이 찬 필러 형상 등 다양한 형상을 가질 수도 있다. 반도체 패턴(130)은 예를 들어, 단결정 실리콘, 다결정 실리콘, 유기 반도체물 및 탄소 나노 구조체 등의 반도체 물질을 포함할 수 있으나, 이에 제한되는 것은 아니다.

정보 저장막(132)은 반도체 패턴(130)과 각각의 반도체 층들(120) 사이에 개재될 수 있다. 예를 들어, 정보 저장막(132)은 반도체 패턴(130)의 외측면을 따라 연장될 수 있다. 정보 저장막(132)은 예를 들어, 실리콘 산화물, 실리콘 질화물, 실리콘 산질화물 및 실리콘 산화물보다 유전율이 큰 고유전율 물질 중 적어도 하나를 포함할 수 있다. 상기 고유전율 물질은 예를 들어, 알루미늄 산화물(aluminum oxide), 하프늄 산화물(hafnium oxide), 란타늄 산화물(lanthanum oxide), 탄탈륨 산화물(tantalum oxide), 티타늄 산화물(titanium oxide), 란타늄 하프늄 산화물(lanthanum hafnium oxide), 란타늄 알루미늄 산화물(lanthanum aluminum oxide), 디스프로슘 스칸듐 산화물(dysprosium scandium oxide) 및 이들의 조합 중 적어도 하나를 포함할 수 있다.

몇몇 실시예에서, 복수의 채널 구조체(CS)들은 지그재그(zigzag) 형태로 배열될 수 있다. 예를 들어, 도 3에 도시된 것처럼, 복수의 채널 구조체(CS)들은 제1 방향(X) 및 제2 방향(Y)에서 서로 엇갈리게 배열될 수 있다. 지그재그 형태로 배열된 복수의 채널 구조체(CS)들은 반도체 메모리 장치의 집적도를 보다 향상시킬 수 있다. 몇몇 실시예에서, 복수의 채널 구조체(CS)들은 벌집(honeycomb) 형태로 배열될 수 있다.

몇몇 실시예에서, 확장 영역(R2)의 제1 몰드 구조체(MS1) 내에 더미 채널 구조체(DCH)가 형성될 수 있다. 더미 채널 구조체(DCH)는 채널 구조체(CS)와 유사한 형상으로 형성되어 확장 영역(R2)에서 제1 몰드 구조체(MS1)에 인가되는 스트레스를 경감할 수 있다.

몇몇 실시예에서, 정보 저장막(132)은 다중막으로 형성될 수 있다. 예를 들어, 도 7을 참조하면, 정보 저장막(132)은 반도체 패턴(130)의 외측면 상에 차례로 적층되는 터널 절연막(132a), 전하 저장막(132b) 및 블로킹 절연막(132c)을 포함할 수 있다.

터널 절연막(132a)은 예를 들어, 실리콘 산화물 또는 실리콘 산화물보다 높은 유전율을 갖는 고유전율 물질(예컨대, 알루미늄 산화물(Al2O3), 하프늄 산화물(HfO2))을 포함할 수 있다. 전하 저장막(132b)은 예를 들어, 실리콘 질화물을 포함할 수 있다. 블로킹 절연막(132c)은 예를 들어, 실리콘 산화물 또는 실리콘 산화물보다 높은 유전율을 갖는 고유전율 물질(예컨대, 알루미늄 산화물(Al2O3), 하프늄 산화물(HfO2))을 포함할 수 있다.

몇몇 실시예에서, 채널 구조체(CS)는 충진 패턴(134)을 더 포함할 수 있다. 충진 패턴(134)은 컵 형상인 반도체 패턴(130)의 내부를 채우도록 형성될 수 있다. 충진 패턴(134)은 절연 물질, 예를 들어, 실리콘 산화물을 포함할 수 있으나, 이에 제한되는 것은 아니다.

몇몇 실시예에서, 채널 구조체(CS)는 채널 패드(136)를 더 포함할 수 있다. 채널 패드(136)는 반도체 패턴(130)과 접속되도록 형성될 수 있다. 예를 들어, 채널 패드(136)는 제1 층간 절연막(140a) 내에 형성되어 반도체 패턴(130)의 상부와 접속될 수 있다. 채널 패드(136)는 예를 들어, 불순물이 도핑된 폴리 실리콘을 포함할 수 있으나, 이에 제한되는 것은 아니다.

몇몇 실시예에서, 채널 구조체(CS)는 소오스 구조체(SS1)를 관통할 수 있다. 예를 들어, 채널 구조체(CS)의 하부는 소오스 구조체(SS1)를 관통하여 셀 기판(100) 내에 매립될 수 있다.

몇몇 실시예에서, 소오스 구조체(SS1)는 다중막으로 형성될 수 있다. 예를 들어, 소오스 구조체(SS1)는 셀 기판(100) 상에 차례로 적층되는 제1 소오스 층(102) 및 제2 소오스 층(104)을 포함할 수 있다. 제1 소오스 층(102) 및 제2 소오스 층(104)은 각각 불순물이 도핑된 폴리 실리콘 또는 불순물이 도핑되지 않은 폴리 실리콘을 포함할 수 있으나, 이에 제한되는 것은 아니다. 제1 소오스 층(102)은 반도체 패턴(130)과 접촉하여 반도체 메모리 장치의 공통 소오스 라인(예컨대, 도 2의 CSL)으로 제공될 수 있다. 제2 소오스 층(104)은 제1 소오스 층(102)을 형성하기 위한 대체(replacement) 공정에서 몰드 스택의 무너짐 또는 쓰러짐을 방지하기 위한 지지층으로 이용될 수 있다.

다시 도 6을 참조하면, 워드 라인 컷(WLC)은 제1 방향(X)으로 연장되어 제1 몰드 구조체(MS1)를 절단할 수 있다. 제1 몰드 구조체(MS1)는 복수의 워드 라인 컷(WLC)들에 의해 절단되어 복수의 메모리 셀 블록들(예컨대, 도 1의 BLK1~BLKn)을 형성할 수 있다. 예를 들어, 인접하는 2개의 워드 라인 컷(WLC)은 그들 사이에 하나의 메모리 셀 블록을 정의할 수 있다. 워드 라인 컷(WLC)들에 의해 정의되는 각각의 메모리 셀 블록들 내에는 복수의 채널 구조체(CS)들이 배치될 수 있다.

하나의 메모리 셀 블록 내에 제2 방향(Y)을 따라 지그재그로 배열되는 채널 구조체(CS)들의 개수는 도 3에 도시된 것에 한정되지 않고 다양할 수 있음은 물론이다.

몇몇 실시예에서, 워드 라인 컷(WLC)은 제1 방향(X)으로 연장되어 소오스 구조체(SS1)를 절단할 수 있다. 워드 라인 컷(WLC)의 하면은 예를 들어, 소오스 구조체(SS1)의 하면보다 낮을 수 있다. 또 다른 예를 들어, 워드 라인 컷(WLC)의 하면은 소오스 구조체(SS1)의 하면과 공면 상에 배치될 수 있다.

몇몇 실시예에서, 워드 라인 컷(WLC)은 절연 물질을 포함할 수 있다. 예를 들어, 상기 절연 물질은 워드 라인 컷(WLC)을 채울 수 있다. 상기 절연 물질은 예를 들어, 실리콘 산화물, 실리콘 질화물 및 실리콘 산질화물 중 적어도 하나를 포함할 수 있으나, 이에 제한되는 것은 아니다.

몇몇 실시예에서, 제1 몰드 구조체(MS1) 내에 스트링 분리 구조체(SC)가 형성될 수 있다. 스트링 분리 구조체(SC)는 제1 방향(X)으로 연장되어 반도체 층(120)을 절단할 수 있다. 스트링 분리 구조체(SC)는 최상부에 배치된 반도체 층(120)의 일부를 절단할 수 있다. 워드 라인 컷(WLC)에 의해 정의되는 각각의 메모리 셀 블록들은 스트링 분리 구조체(SC)에 의해 분할되어 복수의 스트링 영역들을 형성할 수 있다. 예를 들어, 스트링 분리 구조체(SC)는 하나의 메모리 셀 블록 내에 2개의 스트링 영역들을 정의할 수 있다.

비트 라인(BL)은 제1 몰드 구조체(MS1) 및 제1 층간 절연막(140a) 상에 형성될 수 있다. 비트 라인(BL)은 제2 방향(Y)으로 연장되어 워드 라인 컷(WLC)과 교차할 수 있다. 또한, 비트 라인(BL)은 제2 방향(Y)으로 연장되어 제2 방향(Y)을 따라 배열되는 복수의 채널 구조체(CS)들과 접속될 수 있다. 예를 들어, 제1 층간 절연막(140a) 내에 각각의 채널 구조체(CS)들의 상부와 접속되는 비트 라인 컨택(182)이 형성될 수 있다. 비트 라인(BL)은 비트 라인 컨택(182)을 통해 채널 구조체(CS)들과 전기적으로 연결될 수 있다.

주변 회로 영역(PERI)은 주변 회로 기판(200), 주변 로직 구조체(PT) 및 제2 배선 구조체(260)를 포함할 수 있다.

주변 회로 기판(200)은 셀 기판(100) 아래에 배치될 수 있다. 예를 들어, 주변 회로 기판(200)의 상면은 셀 기판(100)의 하면과 대향할 수 있다. 주변 회로 기판(200)은 예를 들어, 실리콘 기판, 게르마늄 기판 혹은 실리콘-게르마늄 기판 등과 같은 반도체 기판을 포함할 수 있다. 또는, 주변 회로 기판(200)은 실리콘-온-인슐레이터(SOI; Silicon-On-Insulator) 기판 혹은 게르마늄-온-인슐레이터(GOI; Germanium-On-Insulator) 기판 등을 포함할 수도 있다.

주변 로직 구조체(PT)는 주변 회로 기판(200) 상에 형성될 수 있다. 주변 로직 구조체(PT)는 반도체 메모리 장치의 동작을 제어하는 주변 회로(예컨대, 도 1의 30)를 구성할 수 있다. 예를 들어, 주변 로직 구조체(PT)는 제어 로직(예컨대, 도 1의 37), 로우 디코더(예컨대, 도 1의 33) 및 페이지 버퍼(예컨대, 도 1의 35) 등을 포함할 수 있다. 이하의 설명에서, 주변 로직 구조체(PT)가 배치되는 주변 회로 기판(200)의 표면은 주변 회로 기판(200)의 전면(front side)으로 지칭될 수 있다. 반대로, 주변 회로 기판(200)의 전면과 반대되는 주변 회로 기판(200)의 표면은 주변 회로 기판(200)의 후면(back side)으로 지칭될 수 있다.

주변 로직 구조체(PT)는 예를 들어, 트랜지스터를 포함할 수 있으나, 이에 제한되는 것은 아니다. 예를 들어, 주변 로직 구조체(PT)는 트랜지스터 등의 다양한 능동 소자(active element)뿐만 아니라, 커패시터(capacitor), 레지스터(resistor), 인덕터(inductor) 등의 다양한 수동 소자(passive element)를 포함할 수도 있다.

도 8은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다. 도 9는 도 8의 S3 영역을 설명하기 위한 확대도이다. 설명의 편의를 위해, 도 1 내지 도 7을 이용하여 상술한 것과 중복되는 부분은 간략히 설명하거나 생략한다.

도 8 및 도 9를 참조하면, 도전성 블로킹 막(150)은 셀 기판(100) 내에 형성될 수 있다. 도전성 블로킹 막(150)의 일부는 주변 회로 영역(PERI)에 형성될 수 있다. 도전성 블로킹 막(150)의 하면(150_BS)은 셀 기판(100)의 하면(100_BS)보다 낮게 형성될 수 있다. 다르게 표현하면, 셀 기판(100)은 제3 방향(Z)으로 제1 높이(w1)를 가질 수 있고, 도전성 블로킹 막(150)은 제3 방향(Z)으로 제1 높이(w1)보다 큰 제2 높이(w2)를 가질 수 있다. 여기서, 제1 높이(w1)는 셀 기판(100)의 하면(100_BS)에서 셀 기판(100)의 상면(100_US)까지 높이이고, 제2 높이(w2)는 도전성 블로킹 막(150)의 하면(150_BS)에서 도전성 블로킹 막(150)의 상면(150_US)까지의 높이일 수 있다.

도 10은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다. 도 11은 도 10의 S5 영역을 설명하기 위한 확대도이다. 설명의 편의를 위해, 도 1 내지 도 7을 이용하여 상술한 것과 중복되는 부분은 간략히 설명하거나 생략한다.

도 10 및 도 11을 참조하면, 몇몇 실시예에 따른 반도체 메모리 장치는 컨택 라인(160)을 더 포함할 수 있다. 컨택 라인(160)은 도전성 블로킹 막(150) 상에 배치될 수 있다. 컨택 라인(160)은 도전성 블로킹 막(150)과 접촉할 수 있다. 몇몇 실시예에서, 컨택 라인(160)의 일부는 필링 막(151) 내에 배치될 수 있다. 컨택 라인(160)은 제3 방향(Z)으로 연장될 수 있다. 컨택 라인(160)은 도전성 블로킹 막(150)과 전기적으로 연결될 수 있다. 컨택 라인(160)은 분리 구조체(140b) 및 제1 층간 절연막(140a) 내에 형성될 수 있다. 컨택 라인(160)은 제1 몰드 구조체(MS1) 및 소오스 구조체(SS1)와 이격되어 배치될 수 있다. 컨택 라인(160)은 제1 몰드 구조체(MS1) 및 소오스 구조체(SS1)와 전기적으로 연결되지 않을 수 있다.

컨택 라인(160)은 컨택 라이너 막(162)과 컨택 필링 막(161)을 포함할 수 있다. 컨택 라이너 막(162)은 분리 구조체(140b) 상에 형성될 수 있다. 컨택 필링 막(161)은 컨택 라이너 막(162) 상에 형성될 수 있다.

컨택 라이너 막(162)은 라이너 막(152)과 동일한 물질로 형성될 수 있다. 컨택 라이너 막(162)은 예를 들어, 티타늄 질화물(TiN), 티타늄 실리콘 질화물(TiSiN) 등 도전성 금속 질화물을 포함할 수 있다. 다만, 본 발명의 기술적 사상이 이에 제한되는 것은 아니다.

컨택 필링 막(161)은 필링 막(151)과 동일한 물질로 형성될 수 있다. 컨택 필링 막(161)은 예를 들어, 텅스텐(W), 알루미늄(Al), 구리(Cu), 코발트(Co), 티타늄(Ti) 등 도전성 금속을 포함할 수 있다. 다만 본 발명의 기술적 사상이 이에 제한되는 것은 아니다.

도 12는 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다. 설명의 편의를 위해, 도 1 내지 도 7을 이용하여 상술한 것과 중복되는 부분은 간략히 설명하거나 생략한다.

도 12를 참조하면, 몇몇 실시예에 따른 반도체 메모리 장치는, 더미 몰드 구조체(DMS1), 제2 몰드 구조체(MS2)를 더 포함할 수 있다.

셀 기판(100)내에 복수의 도전성 블로킹 막(150)이 형성될 수 있다. 도전성 블로킹 막(150)은 제1 방향(X)으로 이격될 수 있다. 각각의 도전성 블로킹 막(150) 상에 분리 구조체(140b)가 배치될 수 있다.

제2 몰드 구조체(MS2)는 셀 기판(100)의 전면(예컨대, 상면) 상에 형성될 수 있다. 제2 몰드 구조체(MS2)는 제1 몰드 구조체(MS1)와 제1 방향(X)으로 이격될 수 있다. 제2 몰드 구조체(MS2)는 셀 기판(100) 상에 교대로 적층되는 복수의 반도체 층들(120) 및 복수의 몰드 절연층들(110)을 포함할 수 있다. 제1 몰드 구조체(MS1)와 동일한 적층 구조를 가질 수 있다. 제2 몰드 구조체(MS2)는 제1 몰드 구조체(MS1)와 동일한 공정으로 형성될 수 있다.

더미 몰드 구조체(DMS1)는 제1 몰드 구조체(MS1)와 제2 몰드 구조체(MS2) 사이에 배치될 수 있다. 더미 몰드 구조체(DMS1)는 제1 몰드 구조체(MS1)와 동일한 적층 구조를 가질 수 있다. 더미 몰드 구조체(DMS1)는 몰드 구조체가 쓰러지는 것을 방지할 수 있다.

분리 구조체(140b)는 제1 몰드 구조체(MS1) 및 더미 몰드 구조체(DMS1) 사이와, 더미 몰드 구조체(DMS1) 및 제2 몰드 구조체(MS2) 사이에 배치될 수 있다. 분리 구조체(140b)는 제1 및 제2 몰드 구조체(MS1, MS2)와 더미 몰드 구조체(DMS1)를 전기적으로 절연시킬 수 있다.

도 13은 몇몇 실시예들에 따른 반도체 메모리 장치를 설명하기 위한 단면도이다. 설명의 편의를 위해, 도 1 내지 도 7, 도 10 및 도 12를 이용하여 상술한 것과 중복되는 부분은 간략히 설명하거나 생략한다.

도 13을 참조하면, 몇몇 실시예에 따른 반도체 메모리 장치는 컨택 라인(160)을 더 포함할 수 있다. 컨택 라인(160)은 컨택 라이너 막(162)과 컨택 필링 막(161)을 포함할 수 있다. 컨택 라인(160)은 도전성 블로킹 막(150) 상에 배치될 수 있다. 컨택 라인(160)은 도전성 블로킹 막(150)과 접촉할 수 있다. 몇몇 실시예에서, 컨택 라인(160)의 일부는 필링 막(151) 내에 배치될 수 있다. 이는 도 11의 S4 영역과 동일할 수 있다.

컨택 라인(160)은 제3 방향(Z)으로 연장될 수 있다. 컨택 라인(160)은 도전성 블로킹 막(150)과 전기적으로 연결될 수 있다. 컨택 라인(160)은 분리 구조체(140b) 및 제1 층간 절연막(140a) 내에 형성될 수 있다. 몇몇 실시예에서, 컨택 라인(160)은 제1 몰드 구조체(MS1)와 더미 몰드 구조체(DMS1) 사이에 배치될 수 있다. 도시되지는 않았지만, 다른 실시예에서 컨택 라인(160)은 제2 몰드 구조체(MS2)와 더미 몰드 구조체(DMS1) 사이에 배치될 수 있다. 또 다른 실시예에서, 컨택 라인(160)은 제1 몰드 구조체(MS1) 및 더미 몰드 구조체(DMS1) 사이와 제2 몰드 구조체(MS2) 및 더미 몰드 구조체(DMS1) 사이에 배치될 수 있다.

도 14 내지 도 27은 몇몇 실시예에 따른 반도체 메모리 장치의 제조 방법을 설명하기 위한 중간 단계 도면들이다. 도 14 내지 도 21, 도 26 및 도 27은 도 3의 A - A 따라 절단한 실시예의 중간 단계 도면들이다. 도 22 내지 도 25는 도 3의 B - B를 따라 절단한 실시예의 중간 단계 도면들이다.

도 14를 참조하면, 주변 회로 영역(PERI) 상에 프리 셀 기판(100P)이 형성될 수 있다. 간략하게 도시되었지만, 도 14의 주변 회로 영역(PERI)은 도 4의 주변 회로 영역(PERI)과 동일한 구조일 수 있다.

도 15를 참조하면, 프리 셀 기판(100P)을 식각하여 리세스(150R)가 형성되고, 셀 기판(100)이 형성될 수 있다. 리세스(150R)는 셀 기판(100)의 측벽 및 주변 회로 영역(PERI) 상면에 의해 정의될 수 있다.

도 16을 참조하면, 리세스(150R) 상에 라이너 막(152)이 형성될 수 있다. 라이너 막(152)은 셀 기판(100)의 측벽 및 주변 회로 영역(PERI)의 상면을 따라 컨포멀 하게 형성될 수 있다.

도 17을 참조하면, 라이너 막(152)상에 필링 막(151)이 형성되어 도전성 블로킹 막(150)을 형성할 수 있다. 도전성 블로킹 막(150)의 상면은 셀 기판(100)의 상면과 동일 평면에 배치될 수 있다.

도 18을 참조하면, 셀 기판(100) 및 도전성 블로킹 막(150) 상에 희생 반도체 층(302) 및 제2 소오스 층(104)이 적층될 수 있다.

도 19를 참조하면, 제2 소오스 층(104) 상에 몰드 절연층(110)과 반도체 층(120)이 교대로 적층되어 제1 몰드 구조체(MS1)를 형성할 수 있다.

도 20을 참조하면, 제1 몰드 구조체(MS1) 상에 제1 프리 캡핑층(140P1)이 형성될 수 있다. 이어서, 제1 프리 절연층(140P1), 제1 몰드 구조체(MS1), 제2 소오스 층(104), 희생 반도체 층(302) 및 셀 기판(100)의 일부를 관통하는 채널 홀(CH)이 형성될 수 있다. 채널 홀(CH)의 제1 방향(X)으로의 폭은 셀 기판(100)에서 멀어짐에 따라 증가할 수 있다.

도 21을 참조하면, 채널 홀(CH)의 측벽을 따라 정보 저장막(132)이 형성될 수 있다. 이어서, 정보 저장막(132) 상에 반도체 패턴(130) 및 충진 패턴(134)이 순차적으로 형성되어 채널 구조체(CS)를 형성할 수 있다. 채널 구조체(CS) 상에 채널 패드(136)가 형성될 수 있다. 제1 몰드 구조체(MS1) 및 채널 패드(136) 상에 제2 프리 절연층(140P2)이 형성될 수 있다.

도 22를 참조하면, 제2 프리 절연층(140P2), 제1 몰드 구조체(MS1), 제2 소오스 층(104) 및 희생 반도체 층(302)을 관통하는 워드 라인 컷(WLC)이 형성될 수 있다. 워드 라인 컷(WLC)의 하부에 희생 반도체 층(302)이 노출될 수 있다.

도 23을 참조하면, 도 22의 희생 반도체 층(302) 제거한다. 이때, 워드 라인 컷(WLC)을 통해 노출된 공간을 이용하여, 풀백 공정을 이용해 도 22의 희생 반도체 층(302)을 제거할 수 있다.

도 24을 참조하면, 도 22의 희생 반도체 층(302)이 제거되어 노출된 영역을 통해, 정보 저장막(132)의 일부를 식각할 수 있다. 도 22의 희생 반도체 층(302)이 제거되어 노출된 영역을 통해, 정보 저장막(132) 및 반도체 패턴(130)의 일부가 노출될 수 있다.

도 25 및 도 26을 참조하면, 도 22의 희생 반도체 층(302)이 제거된 영역에 제1 소오스 층(102) 적층될 수 있다. 제1 소오스 층(102)은 반도체 패턴(130)의 일부와 접촉할 수 있다.

도 27을 참조하면, 식각 공정에 의해 도전성 블로킹 막(150) 상에 분리 구조체 리세스(140R)가 형성될 수 있다. 구체적으로, 분리 구조체 리세스(140R)는 제2 프리 절연층(140P2), 제1 몰드 구조체(MS1), 제1 소오스 층(102) 및 제2 소오스 층(104)을 관통할 수 있다. 도전성 블로킹 막(150)의 일부는 노출될 수 있다. 도전성 블로킹 막(150)은 상술한 식각 공정에서 식각 정지막 기능을 할 수 있다. 도전성 블로킹 막(150)은 주변 회로 영역(PERI)을 보호할 수 있다. 이어서, 분리 구조체 리세스(140R) 내에 절연물질을 채워 넣어 분리 구조체(140b)가 형성될 수 있다.

이상 첨부된 도면을 참조하여 본 발명의 실시예를 설명하였지만, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자는 본 발명이 그 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다.

100: 셀 기판

102: 제1 소오스 층

104: 제2 소오스 층 110: 몰드 절연층

120: 반도체 층 130: 반도체 패턴

132: 정보 저장막 140a: 제1 층간 절연막

140b: 분리 구조체 150: 도전성 블로킹 막

151: 필링 막 152: 라이너 막

CS: 채널 구조체 SS1: 소오스 구조체

MS1: 제1 몰드 구조체

104: 제2 소오스 층 110: 몰드 절연층

120: 반도체 층 130: 반도체 패턴

132: 정보 저장막 140a: 제1 층간 절연막

140b: 분리 구조체 150: 도전성 블로킹 막

151: 필링 막 152: 라이너 막

CS: 채널 구조체 SS1: 소오스 구조체

MS1: 제1 몰드 구조체

Claims (10)

- 기판;

상기 기판 상의 주변 로직 구조체;

상기 주변 로직 구조체 상의 셀 기판;

상기 셀 기판 상에 배치되고, 제1 방향으로 이격되는 복수의 소오스 구조체로, 각각의 소오스 구조체는 제1 소오스 층과, 상기 제1 소오스 층 상의 제2 소오스 층을 포함하는 복수의 소오스 구조체;

상기 소오스 구조체 상에, 각각의 소오스 구조체에 대응되게 배치되는 복수의 몰드 구조체로, 절연층과 반도체 층이 교대로 적층되는 복수의 몰드 구조체;

상기 셀 기판 상에, 상기 제1 방향으로 인접하는 몰드 구조체를 분리하는 분리 구조체;

상기 셀 기판 상에, 상기 몰드 구조체를 관통하고 제2 방향으로 연장된 복수의 채널 구조체; 및

상기 소오스 구조체 하부에 배치되고, 상기 분리 구조체와 상기 제2 방향으로 중첩되는 도전성 블로킹 막을 포함하는, 반도체 메모리 장치. - 제1 항에 있어서,

상기 도전성 블로킹 막의 상면은 상기 셀 기판의 상면과 동일 평면에 배치되는, 반도체 메모리 장치. - 제1 항에 있어서,

상기 도전성 블로킹 막은 라이너 막과, 상기 라이너 막 상에 배치되는 필링 막을 포함하는, 반도체 메모리 장치. - 제1 항에 있어서,

상기 셀 기판의 상기 제2 방향으로 높이는, 상기 도전성 블로킹 막의 상기 제2 방향으로 높이보다 작은, 반도체 메모리 장치. - 제1 항에 있어서,

상기 복수의 몰드 구조체는 제1 몰드 구조체와, 상기 제1 몰드 구조체와 인접하는 제2 몰드 구조체를 포함하고,

상기 제1 몰드 구조체와 상기 제2 몰드 구조체 사이에 배치되는 더미 몰드 구조체를 더 포함하는, 반도체 메모리 장치. - 제1 항에 있어서,

상기 채널 구조체는 정보 저장막 및 반도체 패턴을 포함하고,

상기 소오스 구조체는 상기 반도체 패턴의 일부와 접촉하는, 반도체 메모리 장치. - 제1 항에 있어서,

상기 블로킹 막과 연결되고, 상기 복수의 몰드 구조체와 이격되고, 제2 방향으로 연장되는 컨택 라인을 더 포함하는, 반도체 메모리 장치. - 제1 항에 있어서,

상기 인접하는 몰드 구조체 사이의 상기 제1 방향으로 폭은,

상기 블로킹 막의 제1 방향으로 폭보다 작은, 반도체 메모리 장치. - 주변 로직 구조체 상에 셀 기판이 적층되고,

상기 셀 기판 내에 리세스를 형성하고,

상기 리세스 상에 라이너 막과 필링 막을 순차적으로 적층하여 도전성 블로킹 막을 형성하고,

상기 셀 기판 및 상기 도전성 블로킹 막 상에 희생 반도체 층과 제1 소오스 층을 적층하고,

상기 제1 소오스 층 상에 몰드 절연층과 반도체 층을 교대로 적층하여 몰드 구조체를 형성하고,

상기 몰드 구조체와, 상기 제1 소오스 층과, 상기 희생 반도체 층을 관통하는 채널 구조체로, 정보 저장막과 반도체 패턴을 포함하는 채널 구조체를 형성하고,

상기 몰드 구조체와, 상기 제1 소오스 층과, 상기 희생 반도체 층을 관통하는 워드 라인 컷을 형성하여 상기 희생 반도체 층을 노출시키고,

상기 희생 반도체 층을 제거하여 상기 정보 저장막의 일부를 노출시키고,

상기 정보 저장막의 일부를 제거하고,

상기 희생 반도체 층이 제거된 영역에 상기 반도체 패턴과 접촉하는 제2 소오스 층을 형성하고,

상기 셀 기판 상에, 제1 방향으로 인접하는 몰드 구조체를 분리하는 분리 구조체를 형성하는 것을 포함하되,

상기 분리 구조체는 제2 방향으로 상기 도전성 블로킹 막과 중첩되는, 반도체 메모리 장치 제조 방법. - 제9 항에 있어서,

상기 도전성 블로킹 막의 상면은 상기 셀 기판의 상면과 동일 평면에 배치되는, 반도체 메모리 장치 제조 방법.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020220084479A KR20220104663A (ko) | 2022-07-08 | 2022-07-08 | 반도체 메모리 장치 및 이의 제조 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020220084479A KR20220104663A (ko) | 2022-07-08 | 2022-07-08 | 반도체 메모리 장치 및 이의 제조 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20220104663A true KR20220104663A (ko) | 2022-07-26 |

Family

ID=82609665

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020220084479A Pending KR20220104663A (ko) | 2022-07-08 | 2022-07-08 | 반도체 메모리 장치 및 이의 제조 방법 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR20220104663A (ko) |

-

2022

- 2022-07-08 KR KR1020220084479A patent/KR20220104663A/ko active Pending

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US12108599B2 (en) | Semiconductor memory device and a method of manufacturing the same | |

| US12058863B2 (en) | Semiconductor memory devices and methods for fabricating the same | |

| KR102850151B1 (ko) | 반도체 메모리 장치 | |

| US20210296358A1 (en) | Nonvolatile memory device and method for fabricating the same | |

| US20240088045A1 (en) | Semiconductor device and method of fabricating the same | |

| KR20210088836A (ko) | 비휘발성 메모리 장치 및 그 제조 방법 | |

| KR20210015422A (ko) | 반도체 메모리 장치 | |

| US12543321B2 (en) | Three-dimensional semiconductor memory device | |

| KR20250129591A (ko) | 반도체 장치 | |

| KR20210112051A (ko) | 비휘발성 메모리 장치 및 그 제조 방법 | |

| US20230147901A1 (en) | Semiconductor memory devices, electronic systems including the same and fabricating methods of the same | |

| US20230403854A1 (en) | Semiconductor memory devices and electronic systems | |

| US20230240072A1 (en) | Non-volatile memory device and electronic system including the same | |

| KR20220104663A (ko) | 반도체 메모리 장치 및 이의 제조 방법 | |

| US11723200B2 (en) | Semiconductor device | |

| KR20230110869A (ko) | 반도체 메모리 장치 | |

| KR20230067175A (ko) | 반도체 메모리 장치, 그의 제조 방법 및 그를 포함하는 전자 시스템 | |

| KR102909712B1 (ko) | 반도체 메모리 장치, 그의 제조 방법 및 그를 포함하는 전자 시스템 | |

| US20250324590A1 (en) | Semiconductor device | |

| KR20250120233A (ko) | 반도체 메모리 장치 및 그를 포함하는 전자 시스템 | |

| KR20220038615A (ko) | 비휘발성 메모리 장치, 비휘발성 메모리 장치 제조 방법, 및 비휘발성 메모리 장치를 포함하는 전자 시스템 | |

| KR20250015339A (ko) | 반도체 메모리 장치 | |

| KR20250136625A (ko) | 반도체 장치 제조방법 | |

| KR20210148009A (ko) | 반도체 장치 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-2-2-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-2-2-P10-P22-nap-X000 |

|

| A201 | Request for examination | ||

| D21 | Rejection of application intended |

Free format text: ST27 STATUS EVENT CODE: A-1-2-D10-D21-EXM-PE0902 (AS PROVIDED BY THE NATIONAL OFFICE) |

|

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |