KR20220020831A - 반도체 장치 및 반도체 장치의 제작 방법 - Google Patents

반도체 장치 및 반도체 장치의 제작 방법 Download PDFInfo

- Publication number

- KR20220020831A KR20220020831A KR1020217041369A KR20217041369A KR20220020831A KR 20220020831 A KR20220020831 A KR 20220020831A KR 1020217041369 A KR1020217041369 A KR 1020217041369A KR 20217041369 A KR20217041369 A KR 20217041369A KR 20220020831 A KR20220020831 A KR 20220020831A

- Authority

- KR

- South Korea

- Prior art keywords

- oxide

- insulator

- film

- conductor

- oxygen

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 421

- 238000004519 manufacturing process Methods 0.000 title claims description 66

- 229910052760 oxygen Inorganic materials 0.000 claims description 289

- 239000001301 oxygen Substances 0.000 claims description 287

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 279

- 238000000034 method Methods 0.000 claims description 251

- 238000010438 heat treatment Methods 0.000 claims description 129

- 238000004544 sputter deposition Methods 0.000 claims description 103

- 229910044991 metal oxide Inorganic materials 0.000 claims description 94

- 150000004706 metal oxides Chemical class 0.000 claims description 94

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 85

- 229910052710 silicon Inorganic materials 0.000 claims description 74

- 239000010703 silicon Substances 0.000 claims description 74

- 238000000231 atomic layer deposition Methods 0.000 claims description 64

- 238000012545 processing Methods 0.000 claims description 54

- 239000012298 atmosphere Substances 0.000 claims description 52

- 238000005229 chemical vapour deposition Methods 0.000 claims description 52

- 229910052782 aluminium Inorganic materials 0.000 claims description 51

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 51

- 230000008569 process Effects 0.000 claims description 49

- 229910052757 nitrogen Inorganic materials 0.000 claims description 34

- 229910000449 hafnium oxide Inorganic materials 0.000 claims description 25

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims description 25

- 229910052715 tantalum Inorganic materials 0.000 claims description 25

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 25

- 229910052738 indium Inorganic materials 0.000 claims description 22

- 229910052733 gallium Inorganic materials 0.000 claims description 20

- 229910052725 zinc Inorganic materials 0.000 claims description 10

- 239000012299 nitrogen atmosphere Substances 0.000 claims description 8

- 230000001681 protective effect Effects 0.000 claims description 4

- 125000002524 organometallic group Chemical group 0.000 claims description 3

- 230000001678 irradiating effect Effects 0.000 claims description 2

- 239000012212 insulator Substances 0.000 description 1105

- 239000004020 conductor Substances 0.000 description 527

- 239000010408 film Substances 0.000 description 457

- 239000010410 layer Substances 0.000 description 211

- 239000001257 hydrogen Substances 0.000 description 175

- 229910052739 hydrogen Inorganic materials 0.000 description 175

- 239000000758 substrate Substances 0.000 description 170

- 230000006870 function Effects 0.000 description 168

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 152

- 230000002829 reductive effect Effects 0.000 description 108

- 239000000463 material Substances 0.000 description 105

- 230000015654 memory Effects 0.000 description 105

- 239000012535 impurity Substances 0.000 description 104

- 239000007789 gas Substances 0.000 description 99

- 230000015572 biosynthetic process Effects 0.000 description 78

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 74

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 73

- 239000003990 capacitor Substances 0.000 description 73

- 229910052581 Si3N4 Inorganic materials 0.000 description 71

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 71

- 229910052751 metal Inorganic materials 0.000 description 62

- 229910052814 silicon oxide Inorganic materials 0.000 description 62

- 238000009792 diffusion process Methods 0.000 description 61

- 239000002184 metal Substances 0.000 description 56

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 55

- 229910001868 water Inorganic materials 0.000 description 55

- 239000013078 crystal Substances 0.000 description 48

- 239000011701 zinc Substances 0.000 description 47

- 229910052735 hafnium Inorganic materials 0.000 description 44

- 238000003860 storage Methods 0.000 description 40

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 38

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 37

- 238000012546 transfer Methods 0.000 description 35

- 150000004767 nitrides Chemical class 0.000 description 32

- -1 element M Chemical compound 0.000 description 29

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 28

- 125000004429 atom Chemical group 0.000 description 28

- 230000004888 barrier function Effects 0.000 description 28

- 238000010586 diagram Methods 0.000 description 28

- 239000000203 mixture Substances 0.000 description 28

- 238000001451 molecular beam epitaxy Methods 0.000 description 27

- 238000004549 pulsed laser deposition Methods 0.000 description 27

- 239000000523 sample Substances 0.000 description 26

- 230000007547 defect Effects 0.000 description 25

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 24

- 229910052721 tungsten Inorganic materials 0.000 description 23

- 239000010937 tungsten Substances 0.000 description 23

- 229910052799 carbon Inorganic materials 0.000 description 22

- 238000005530 etching Methods 0.000 description 22

- 150000002431 hydrogen Chemical class 0.000 description 22

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 22

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 21

- 229910052719 titanium Inorganic materials 0.000 description 21

- 239000010936 titanium Substances 0.000 description 21

- 238000001312 dry etching Methods 0.000 description 19

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 18

- 238000007789 sealing Methods 0.000 description 18

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 16

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 16

- 239000011261 inert gas Substances 0.000 description 16

- 239000002356 single layer Substances 0.000 description 16

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 15

- 229910052802 copper Inorganic materials 0.000 description 15

- 239000010949 copper Substances 0.000 description 15

- 230000007423 decrease Effects 0.000 description 15

- 229910001873 dinitrogen Inorganic materials 0.000 description 15

- 229910001882 dioxygen Inorganic materials 0.000 description 15

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 14

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 14

- 238000013473 artificial intelligence Methods 0.000 description 14

- 229910052759 nickel Inorganic materials 0.000 description 14

- 238000005406 washing Methods 0.000 description 14

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 13

- 239000011229 interlayer Substances 0.000 description 13

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 12

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 12

- 230000010354 integration Effects 0.000 description 12

- 229910052750 molybdenum Inorganic materials 0.000 description 12

- 239000011733 molybdenum Substances 0.000 description 12

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 12

- 239000010453 quartz Substances 0.000 description 12

- 229910001928 zirconium oxide Inorganic materials 0.000 description 12

- 238000002441 X-ray diffraction Methods 0.000 description 11

- 238000004140 cleaning Methods 0.000 description 11

- 238000002156 mixing Methods 0.000 description 11

- 230000003647 oxidation Effects 0.000 description 11

- 238000007254 oxidation reaction Methods 0.000 description 11

- 239000011347 resin Substances 0.000 description 11

- 229920005989 resin Polymers 0.000 description 11

- 229910052707 ruthenium Inorganic materials 0.000 description 11

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 10

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 10

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 10

- 230000000694 effects Effects 0.000 description 10

- 229910001195 gallium oxide Inorganic materials 0.000 description 10

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 10

- 229910052726 zirconium Inorganic materials 0.000 description 10

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 9

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 9

- 230000005684 electric field Effects 0.000 description 9

- 229910052731 fluorine Inorganic materials 0.000 description 9

- 239000011737 fluorine Substances 0.000 description 9

- 229910052746 lanthanum Inorganic materials 0.000 description 9

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 9

- 229910052749 magnesium Inorganic materials 0.000 description 9

- 239000011777 magnesium Substances 0.000 description 9

- 230000001590 oxidative effect Effects 0.000 description 9

- 239000000126 substance Substances 0.000 description 9

- 229910052727 yttrium Inorganic materials 0.000 description 9

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 9

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 8

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 8

- 230000009471 action Effects 0.000 description 8

- 229910052786 argon Inorganic materials 0.000 description 8

- 239000000969 carrier Substances 0.000 description 8

- 238000006243 chemical reaction Methods 0.000 description 8

- 229910052732 germanium Inorganic materials 0.000 description 8

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 8

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 8

- 230000007246 mechanism Effects 0.000 description 8

- 230000004048 modification Effects 0.000 description 8

- 238000012986 modification Methods 0.000 description 8

- 125000004430 oxygen atom Chemical group O* 0.000 description 8

- 230000002093 peripheral effect Effects 0.000 description 8

- 238000001228 spectrum Methods 0.000 description 8

- 239000006227 byproduct Substances 0.000 description 7

- 230000000875 corresponding effect Effects 0.000 description 7

- 238000002003 electron diffraction Methods 0.000 description 7

- 229910003437 indium oxide Inorganic materials 0.000 description 7

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 7

- 239000011810 insulating material Substances 0.000 description 7

- 239000000395 magnesium oxide Substances 0.000 description 7

- 239000011159 matrix material Substances 0.000 description 7

- 238000001039 wet etching Methods 0.000 description 7

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 229910052796 boron Inorganic materials 0.000 description 6

- 238000013461 design Methods 0.000 description 6

- 238000010894 electron beam technology Methods 0.000 description 6

- 230000005669 field effect Effects 0.000 description 6

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 6

- 229910052742 iron Inorganic materials 0.000 description 6

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 6

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 6

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 6

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 6

- 230000003071 parasitic effect Effects 0.000 description 6

- 238000009832 plasma treatment Methods 0.000 description 6

- 239000000376 reactant Substances 0.000 description 6

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 6

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 6

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 6

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 5

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 5

- 229910052779 Neodymium Inorganic materials 0.000 description 5

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 5

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 5

- QGZKDVFQNNGYKY-UHFFFAOYSA-N ammonia Natural products N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 5

- 235000011114 ammonium hydroxide Nutrition 0.000 description 5

- 229910052804 chromium Inorganic materials 0.000 description 5

- 239000011651 chromium Substances 0.000 description 5

- 229910000423 chromium oxide Inorganic materials 0.000 description 5

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 5

- 239000007788 liquid Substances 0.000 description 5

- 230000014759 maintenance of location Effects 0.000 description 5

- 238000005259 measurement Methods 0.000 description 5

- 239000002159 nanocrystal Substances 0.000 description 5

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 5

- 230000036961 partial effect Effects 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 5

- 239000000047 product Substances 0.000 description 5

- 238000006722 reduction reaction Methods 0.000 description 5

- 238000009751 slip forming Methods 0.000 description 5

- 239000013589 supplement Substances 0.000 description 5

- 229910052718 tin Inorganic materials 0.000 description 5

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 4

- 229910052783 alkali metal Inorganic materials 0.000 description 4

- 150000001340 alkali metals Chemical class 0.000 description 4

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 4

- 150000001342 alkaline earth metals Chemical class 0.000 description 4

- 238000004458 analytical method Methods 0.000 description 4

- 238000000137 annealing Methods 0.000 description 4

- 239000007864 aqueous solution Substances 0.000 description 4

- 238000004364 calculation method Methods 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 4

- 150000004770 chalcogenides Chemical class 0.000 description 4

- 239000011248 coating agent Substances 0.000 description 4

- 238000000576 coating method Methods 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 239000000470 constituent Substances 0.000 description 4

- 238000009826 distribution Methods 0.000 description 4

- 238000002524 electron diffraction data Methods 0.000 description 4

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 4

- 238000001341 grazing-angle X-ray diffraction Methods 0.000 description 4

- 230000020169 heat generation Effects 0.000 description 4

- 238000003384 imaging method Methods 0.000 description 4

- SHXXPRJOPFJRHA-UHFFFAOYSA-K iron(iii) fluoride Chemical compound F[Fe](F)F SHXXPRJOPFJRHA-UHFFFAOYSA-K 0.000 description 4

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 4

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 4

- 239000002243 precursor Substances 0.000 description 4

- 239000011241 protective layer Substances 0.000 description 4

- 238000004151 rapid thermal annealing Methods 0.000 description 4

- 230000009467 reduction Effects 0.000 description 4

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 4

- 229910052712 strontium Inorganic materials 0.000 description 4

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 4

- 239000010409 thin film Substances 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910052723 transition metal Inorganic materials 0.000 description 4

- 229910052720 vanadium Inorganic materials 0.000 description 4

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 4

- 239000011787 zinc oxide Substances 0.000 description 4

- 229910052684 Cerium Inorganic materials 0.000 description 3

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 3

- 238000010521 absorption reaction Methods 0.000 description 3

- 239000003463 adsorbent Substances 0.000 description 3

- 238000003491 array Methods 0.000 description 3

- 229910052790 beryllium Inorganic materials 0.000 description 3

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 238000005520 cutting process Methods 0.000 description 3

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- 150000002500 ions Chemical class 0.000 description 3

- 238000001459 lithography Methods 0.000 description 3

- 239000013081 microcrystal Substances 0.000 description 3

- 125000004433 nitrogen atom Chemical group N* 0.000 description 3

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 3

- 239000007800 oxidant agent Substances 0.000 description 3

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 239000012466 permeate Substances 0.000 description 3

- 229910001936 tantalum oxide Inorganic materials 0.000 description 3

- 229910052714 tellurium Inorganic materials 0.000 description 3

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 3

- 229910001930 tungsten oxide Inorganic materials 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 2

- 241000209094 Oryza Species 0.000 description 2

- 235000007164 Oryza sativa Nutrition 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910001080 W alloy Inorganic materials 0.000 description 2

- 238000004833 X-ray photoelectron spectroscopy Methods 0.000 description 2

- 238000013528 artificial neural network Methods 0.000 description 2

- 229910052800 carbon group element Inorganic materials 0.000 description 2

- 229910052798 chalcogen Inorganic materials 0.000 description 2

- 150000001787 chalcogens Chemical class 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 230000001276 controlling effect Effects 0.000 description 2

- 238000013527 convolutional neural network Methods 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000007865 diluting Methods 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- 230000014509 gene expression Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 238000009499 grossing Methods 0.000 description 2

- 238000010348 incorporation Methods 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 2

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 2

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 2

- 229910021334 nickel silicide Inorganic materials 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 229910052756 noble gas Inorganic materials 0.000 description 2

- 230000001151 other effect Effects 0.000 description 2

- 230000000704 physical effect Effects 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920001296 polysiloxane Polymers 0.000 description 2

- 239000011148 porous material Substances 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 238000001552 radio frequency sputter deposition Methods 0.000 description 2

- 230000006798 recombination Effects 0.000 description 2

- 235000009566 rice Nutrition 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 229910052708 sodium Inorganic materials 0.000 description 2

- 239000011734 sodium Substances 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 238000005477 sputtering target Methods 0.000 description 2

- 238000004506 ultrasonic cleaning Methods 0.000 description 2

- 230000000007 visual effect Effects 0.000 description 2

- 229910019311 (Ba,Sr)TiO Inorganic materials 0.000 description 1

- SDDGNMXIOGQCCH-UHFFFAOYSA-N 3-fluoro-n,n-dimethylaniline Chemical compound CN(C)C1=CC=CC(F)=C1 SDDGNMXIOGQCCH-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- 235000015842 Hesperis Nutrition 0.000 description 1

- 235000012633 Iberis amara Nutrition 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- 108010083687 Ion Pumps Proteins 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 229910016001 MoSe Inorganic materials 0.000 description 1

- 241000699670 Mus sp. Species 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 1

- 238000003917 TEM image Methods 0.000 description 1

- 238000005411 Van der Waals force Methods 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- AZDRQVAHHNSJOQ-UHFFFAOYSA-N alumane Chemical group [AlH3] AZDRQVAHHNSJOQ-UHFFFAOYSA-N 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- WVMYSOZCZHQCSG-UHFFFAOYSA-N bis(sulfanylidene)zirconium Chemical compound S=[Zr]=S WVMYSOZCZHQCSG-UHFFFAOYSA-N 0.000 description 1

- 229910000416 bismuth oxide Inorganic materials 0.000 description 1

- 229910052795 boron group element Inorganic materials 0.000 description 1

- 235000012206 bottled water Nutrition 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- TYIXMATWDRGMPF-UHFFFAOYSA-N dibismuth;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Bi+3].[Bi+3] TYIXMATWDRGMPF-UHFFFAOYSA-N 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 235000013305 food Nutrition 0.000 description 1

- 235000012041 food component Nutrition 0.000 description 1

- 239000005417 food ingredient Substances 0.000 description 1

- 230000008014 freezing Effects 0.000 description 1

- 238000007710 freezing Methods 0.000 description 1

- 239000000446 fuel Substances 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- 229910021389 graphene Inorganic materials 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- NRJVMVHUISHHQB-UHFFFAOYSA-N hafnium(4+);disulfide Chemical compound [S-2].[S-2].[Hf+4] NRJVMVHUISHHQB-UHFFFAOYSA-N 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 238000002173 high-resolution transmission electron microscopy Methods 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 229910000040 hydrogen fluoride Inorganic materials 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000004615 ingredient Substances 0.000 description 1

- 230000002401 inhibitory effect Effects 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 235000012054 meals Nutrition 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- MHWZQNGIEIYAQJ-UHFFFAOYSA-N molybdenum diselenide Chemical compound [Se]=[Mo]=[Se] MHWZQNGIEIYAQJ-UHFFFAOYSA-N 0.000 description 1

- CWQXQMHSOZUFJS-UHFFFAOYSA-N molybdenum disulfide Chemical compound S=[Mo]=S CWQXQMHSOZUFJS-UHFFFAOYSA-N 0.000 description 1

- MGRWKWACZDFZJT-UHFFFAOYSA-N molybdenum tungsten Chemical compound [Mo].[W] MGRWKWACZDFZJT-UHFFFAOYSA-N 0.000 description 1

- 229910000484 niobium oxide Inorganic materials 0.000 description 1

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 235000006408 oxalic acid Nutrition 0.000 description 1

- 238000006213 oxygenation reaction Methods 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 235000011007 phosphoric acid Nutrition 0.000 description 1

- 239000011295 pitch Substances 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229910052696 pnictogen Inorganic materials 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910052699 polonium Inorganic materials 0.000 description 1

- HZEBHPIOVYHPMT-UHFFFAOYSA-N polonium atom Chemical compound [Po] HZEBHPIOVYHPMT-UHFFFAOYSA-N 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000098 polyolefin Polymers 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 238000011002 quantification Methods 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000000306 recurrent effect Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000003362 replicative effect Effects 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000004645 scanning capacitance microscopy Methods 0.000 description 1

- 238000000851 scanning transmission electron micrograph Methods 0.000 description 1

- 229910052711 selenium Inorganic materials 0.000 description 1

- 239000011669 selenium Substances 0.000 description 1

- HVEIXSLGUCQTMP-UHFFFAOYSA-N selenium(2-);zirconium(4+) Chemical compound [Se-2].[Se-2].[Zr+4] HVEIXSLGUCQTMP-UHFFFAOYSA-N 0.000 description 1

- 229910021428 silicene Inorganic materials 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 229910002076 stabilized zirconia Inorganic materials 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 1

- 238000012916 structural analysis Methods 0.000 description 1

- 238000000859 sublimation Methods 0.000 description 1

- 230000008022 sublimation Effects 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 239000011593 sulfur Substances 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 230000008719 thickening Effects 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 230000032258 transport Effects 0.000 description 1

- ITRNXVSDJBHYNJ-UHFFFAOYSA-N tungsten disulfide Chemical compound S=[W]=S ITRNXVSDJBHYNJ-UHFFFAOYSA-N 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

- 239000013585 weight reducing agent Substances 0.000 description 1

- 230000003936 working memory Effects 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 1

- RUDFQVOCFDJEEF-UHFFFAOYSA-N yttrium(III) oxide Inorganic materials [O-2].[O-2].[O-2].[Y+3].[Y+3] RUDFQVOCFDJEEF-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02565—Oxide semiconducting materials not being Group 12/16 materials, e.g. ternary compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/268—Bombardment with radiation with high-energy radiation using electromagnetic radiation, e.g. laser radiation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/34—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies not provided for in groups H01L21/0405, H01L21/0445, H01L21/06, H01L21/16 and H01L21/18 with or without impurities, e.g. doping materials

- H01L21/42—Bombardment with radiation

- H01L21/423—Bombardment with radiation with high-energy radiation

- H01L21/428—Bombardment with radiation with high-energy radiation using electromagnetic radiation, e.g. laser radiation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/34—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies not provided for in groups H01L21/0405, H01L21/0445, H01L21/06, H01L21/16 and H01L21/18 with or without impurities, e.g. doping materials

- H01L21/46—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428

- H01L21/477—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/105—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration including field-effect components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/788—Field effect transistors with field effect produced by an insulated gate with floating gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/792—Field effect transistors with field effect produced by an insulated gate with charge trapping gate insulator, e.g. MNOS-memory transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/70—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates the floating gate being an electrode shared by two or more components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

Abstract

트랜지스터 특성의 편차가 적은 반도체 장치를 제공한다. 반도체막과, 반도체막 위의 한 쌍의 차폐막과, 반도체막 위에 위치하며 한 쌍의 차폐막 사이에 제공되는 절연막을 가지고, 반도체막은 한 쌍의 n형 영역과, 한 쌍의 n형 영역 사이에 제공되는 i형 영역을 가지고, n형 영역은 차폐막과 중첩되고, i형 영역은 절연막과 중첩된다.

Description

본 발명의 일 형태는 트랜지스터, 반도체 장치, 및 전자 기기에 관한 것이다. 또는 본 발명의 일 형태는 반도체 장치의 제작 방법에 관한 것이다. 또는 본 발명의 일 형태는 반도체 웨이퍼 및 모듈에 관한 것이다.

또한 본 명세서 등에서 반도체 장치란, 반도체 특성을 이용함으로써 기능할 수 있는 장치 전반을 가리킨다. 트랜지스터 등의 반도체 소자를 비롯하여, 반도체 회로, 연산 장치, 기억 장치는 반도체 장치의 일 형태이다. 표시 장치(액정 표시 장치, 발광 표시 장치 등), 투영 장치, 조명 장치, 전기 광학 장치, 축전 장치, 기억 장치, 반도체 회로, 촬상 장치, 전자 기기 등은 반도체 장치를 가진다고 할 수 있는 경우가 있다.

또한 본 발명의 일 형태는 상기 기술분야에 한정되지 않는다. 본 명세서 등에서 개시(開示)하는 발명의 일 형태는 물건, 방법, 또는 제조 방법에 관한 것이다. 또는 본 발명의 일 형태는 프로세스(process), 기계(machine), 제품(manufacture), 또는 조성물(composition of matter)에 관한 것이다.

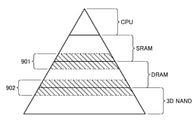

근년, 반도체 장치의 개발이 진행되고, 특히 LSI(Large Scale Integrated Circuit)나 CPU(Central Processing Unit)나 메모리의 개발이 현저하게 진행되고 있다. CPU는 반도체 웨이퍼로부터 분리된 반도체 집적 회로(적어도 트랜지스터 및 메모리)를 가지고, 접속 단자인 전극이 형성된 반도체 소자의 집합체이다.

LSI나 CPU나 메모리 등의 반도체 회로(IC(Integrated Circuit)칩)는 회로 기판, 예를 들어 인쇄 배선판에 실장되고, 다양한 전자 기기의 부품의 하나로서 사용된다.

또한 절연 표면을 가지는 기판 위에 형성된 반도체 박막을 사용하여 트랜지스터를 구성하는 기술이 주목받고 있다. 상기 트랜지스터는 집적 회로(IC)나 화상 표시 장치(단순히 표시 장치라고도 표기함)와 같은 전자 디바이스에 널리 응용되고 있다. 트랜지스터에 적용할 수 있는 반도체 박막으로서 실리콘계 반도체 재료가 널리 알려져 있지만, 그 외의 재료로서 산화물 반도체가 주목받고 있다.

또한 산화물 반도체가 사용된 트랜지스터는, 비도통 상태에서 누설 전류가 매우 작은 것이 알려져 있다. 예를 들어 산화물 반도체가 사용된 트랜지스터의 누설 전류가 낮다는 특성을 응용한 저소비 전력의 CPU 등이 개시되어 있다(특허문헌 1 참조). 또한 예를 들어 산화물 반도체가 사용된 트랜지스터의 누설 전류가 낮다는 특성을 응용하여, 장기간에 걸쳐 기억 내용을 유지할 수 있는 기억 장치 등이 개시되어 있다(특허문헌 2 참조).

또한 근년에는 전자 기기의 소형화, 경량화에 따라, 고밀도화가 더 진행된 집적 회로에 대한 요구가 높아지고 있다. 또한 집적 회로를 포함하는 반도체 장치의 생산성의 향상이 요구되고 있다.

본 발명의 일 형태는 트랜지스터 특성의 편차가 적은 반도체 장치를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 신뢰성이 양호한 반도체 장치를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 전기 특성이 양호한 반도체 장치를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 온 전류가 큰 반도체 장치를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 미세화 또는 고집적화가 가능한 반도체 장치를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 저소비 전력의 반도체 장치를 제공하는 것을 과제 중 하나로 한다.

또한 이들 과제의 기재는 다른 과제의 존재를 방해하는 것이 아니다. 또한 본 발명의 일 형태는 이들 과제 모두를 해결할 필요는 없는 것으로 한다. 또한 이들 외의 과제는 명세서, 도면, 청구항 등의 기재에서 저절로 명백해지는 것이며 명세서, 도면, 청구항 등의 기재에서 이들 외의 과제를 추출할 수 있다.

본 발명의 일 형태는 반도체막과, 반도체막 위의 한 쌍의 차폐막과, 반도체막 위에 위치하며 한 쌍의 차폐막 사이에 제공되는 절연막을 가지고, 반도체막은 한 쌍의 n형 영역과, 한 쌍의 n형 영역 사이에 제공되는 i형 영역을 가지고, n형 영역은 차폐막과 중첩되고, i형 영역은 절연막과 중첩되는 반도체 장치이다.

본 발명의 다른 일 형태는 반도체막과, 반도체막 위의 한 쌍의 차폐막과, 한 쌍의 차폐막 위의 보호막과, 반도체막 위에 위치하며 한 쌍의 차폐막 사이에 제공되는 절연막을 가지고, 반도체막은 한 쌍의 n형 영역과, 한 쌍의 n형 영역 사이에 제공되는 i형 영역을 가지고, n형 영역은 차폐막과 중첩되고, i형 영역은 절연막과 중첩되는 반도체 장치이다.

상기에 있어서, 보호막은 알루미늄과 산소를 가지는 것이 바람직하다. 또한 상기에 있어서, 차폐막은 300MHz 이상 300GHz 이하의 전자기파를 차폐하는 기능을 가지는 것이 바람직하다. 또한 상기에 있어서, 차폐막은 탄탈럼과 질소를 가지는 것이 바람직하다.

상기에 있어서, i형 영역은 캐리어 농도가 1×10-9cm-3 이상 1×1017cm-3 미만이고, n형 영역은 캐리어 농도가 1×1017cm-3 이상 1×1021cm-3 이하인 것이 바람직하다. 또한 상기에 있어서, 반도체막은 금속 산화물인 것이 바람직하다. 또한 상기에 있어서, 반도체막은 In, Ga, 및 Zn에서 선택되는 어느 하나 또는 복수인 것이 바람직하다. 또한 상기에 있어서, 절연막은 실리콘과 산소를 가지는 것이 바람직하다.

본 발명의 다른 일 형태는 반도체막을 형성하는 제 1 공정과, 반도체막 위에 차폐막을 형성하는 제 2 공정과, 반도체막 및 차폐막을 섬 형상으로 가공하는 제 3 공정과, 반도체막 및 차폐막 위에 산화물 절연막을 형성하는 제 4 공정과, 산화물 절연막 및 차폐막을 가공하여 반도체막에 도달하는 개구부를 형성하는 제 5 공정과, 반도체막, 차폐막, 및 산화물 절연막에 대하여 가열 처리를 수행하는 제 6 공정과, 개구부를 덮도록 절연막을 형성하는 제 7 공정과, 절연막을 통하여 반도체막에 마이크로파를 조사하는 제 8 공정을 가지고, 마이크로파의 조사는 적어도 산소를 포함하는 분위기에서 수행되고, 또한 100℃ 이상 750℃ 이하의 온도 범위에서 수행되는, 반도체 장치의 제작 방법이다.

상기에 있어서, 마이크로파의 조사는 300℃ 이상 500℃ 이하의 온도 범위에서 수행되는 것이 바람직하다. 또한 상기에 있어서, 마이크로파의 조사는 300Pa 이상 700Pa 이하의 압력 범위에서 수행되는 것이 바람직하다.

상기에 있어서, 가열 처리는 제 1 가열 처리와 제 2 가열 처리를 가지고, 제 1 가열 처리는 산소 분위기에서, 300℃ 이상 500℃ 이하의 범위에서 수행되고, 제 2 가열 처리는 질소 분위기에서, 300℃ 이상 500℃ 이하의 범위에서 수행되는 것이 바람직하다. 또한 상기에 있어서, 제 1 가열 처리는 제 2 가열 처리보다 장시간 수행되는 것이 바람직하다.

상기에 있어서, 절연막은 플라스마 화학 기상 성장법 또는 원자층 퇴적법을 사용하여 형성되는 것이 바람직하다. 또한 상기에 있어서, 반도체막은 금속 산화물을 가지고, 금속 산화물은 In, Ga, 및 Zn에서 선택되는 어느 하나 또는 복수를 가지고, 금속 산화물은 스퍼터링법, 원자층 퇴적법, 또는 유기 금속 화학 기상 성장법을 사용하여 형성되는 것이 바람직하다.

상기에 있어서, 제 8 공정 후에 제 9 공정을 더 가지고, 제 9 공정에서는 원자층 퇴적법에 의하여 산화 하프늄을 형성하는 것이 바람직하다.

본 발명의 다른 일 형태는 기판 위에 산화막을 성막하고, 산화막 위에 제 1 도전막을 성막하고, 산화막 및 제 1 도전막을 섬 형상으로 가공하여 산화물 및 제 1 도전체를 형성하고, 산화물 및 제 1 도전체를 덮어 제 1 절연체를 형성하고, 제 1 절연체의 일부를 제거하여 개구를 형성하고, 상기 개구에 중첩된 제 1 도전체의 일부를 제거함으로써 제 2 도전체와 제 3 도전체를 형성하여, 상기 제 2 도전체와 상기 제 3 도전체 사이의 영역에 산화물을 노출시키고, 산화물의 상면에 접하여 절연막을 성막하고, 산소를 포함하는 분위기에서 마이크로파 처리를 수행하고, 절연막 위에 제 2 도전막을 성막하고, 절연막 및 제 2 도전막에 대하여 제 1 절연체의 상면이 노출될 때까지 CMP 처리를 수행하여 제 2 절연체 및 제 4 도전체를 형성하는 반도체 장치의 제작 방법이다.

본 발명의 다른 일 형태는 기판 위에 산화막을 성막하고, 산화막 위에 제 1 도전막을 성막하고, 산화막 및 제 1 도전막을 섬 형상으로 가공하여 산화물 및 제 1 도전체를 형성하고, 산화물 및 제 1 도전체를 덮어 제 1 절연체를 형성하고, 제 1 절연체의 일부를 제거하여 개구를 형성하고, 상기 개구에 중첩된 제 1 도전체의 일부를 제거함으로써 제 2 도전체와 제 3 도전체를 형성하여, 상기 제 2 도전체와 상기 제 3 도전체 사이의 영역에 산화물을 노출시키고, 산소를 포함하는 분위기에서 마이크로파 처리를 수행하고, 산화물의 상면에 접하여 절연막을 성막하고, 절연막 위에 제 2 도전막을 성막하고, 절연막 및 제 2 도전막에 대하여 제 1 절연체의 상면이 노출될 때까지 CMP 처리를 수행하여 제 2 절연체 및 제 4 도전체를 형성하는 반도체 장치의 제작 방법이다.

본 발명의 다른 일 형태는 기판 위에 산화막을 성막하고, 산화막 위에 제 1 도전막을 성막하고, 산화막 및 제 1 도전막을 섬 형상으로 가공하여 산화물 및 제 1 도전체를 형성하고, 산화물 및 제 1 도전체를 덮어 제 1 절연체를 형성하고, 제 1 절연체의 일부를 제거하여 개구를 형성하고, 상기 개구에 중첩된 제 1 도전체의 일부를 제거함으로써 제 2 도전체와 제 3 도전체를 형성하여, 상기 제 2 도전체와 상기 제 3 도전체 사이의 영역에 산화물을 노출시키고, 산소를 포함하는 분위기에서 마이크로파 처리를 수행하고, 산화물의 상면에 접하여 제 1 절연막을 PEALD법에 의하여 성막하고, 제 1 절연막의 상면에 접하여 제 2 절연막을 열 ALD법에 의하여 성막하고, 제 2 절연막 위에 제 2 도전막을 성막하고, 제 1 절연막, 제 2 절연막, 및 제 2 도전막에 대하여 제 1 절연체의 상면이 노출될 때까지 CMP 처리를 수행하여 제 2 절연체, 제 3 절연체, 및 제 4 도전체를 형성하고, 제 3 절연체는 제 2 절연체보다 산소를 확산시키기 어려운, 반도체 장치의 제작 방법이다.

상기에 있어서, 마이크로파 처리, 제 1 절연막의 성막, 제 2 절연막의 성막을, 대기 환경에 노출시키지 않고 연속적으로 수행하는 것이 바람직하다. 또한 상기에 있어서, 제 1 절연막은 실리콘을 포함하는 산화막이고, 제 2 절연막은 하프늄을 포함하는 산화막인 것이 바람직하다.

상기에 있어서, 마이크로파 처리는 산소를 포함하는 분위기에서 수행하고, 산소 유량비는 0%보다 크고, 100% 이하로 하여도 좋다. 또한 상기에 있어서, 마이크로파 처리는 산소 및 아르곤을 포함하는 분위기에서 수행하고, 산소 유량비는 10% 이상, 40% 이하인 것이 바람직하다.

본 발명의 일 형태에 의하여 트랜지스터 특성의 편차가 적은 반도체 장치를 제공할 수 있다. 또는 본 발명의 일 형태에 의하여 신뢰성이 양호한 반도체 장치를 제공할 수 있다. 또는 본 발명의 일 형태에 의하여 전기 특성이 양호한 반도체 장치를 제공할 수 있다. 또는 본 발명의 일 형태에 의하여 온 전류가 큰 반도체 장치를 제공할 수 있다. 또는 본 발명의 일 형태에 의하여 미세화 또는 고집적화가 가능한 반도체 장치를 제공할 수 있다. 또는 본 발명의 일 형태에 의하여 저소비 전력의 반도체 장치를 제공할 수 있다.

또한 이들 효과의 기재는 다른 효과의 존재를 방해하는 것이 아니다. 또한 본 발명의 일 형태는 이들 효과 모두를 가질 필요는 없다. 또한 이들 외의 효과는 명세서, 도면, 청구항 등의 기재에서 저절로 명백해지는 것이며 명세서, 도면, 청구항 등의 기재에서 이들 외의 효과를 추출할 수 있다.

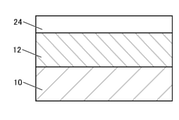

도 1의 (A)는 본 발명의 일 형태인 반도체 장치의 상면도이다. 도 1의 (B) 내지 (D)는 본 발명의 일 형태인 반도체 장치의 단면도이다.

도 2는 본 발명의 일 형태인 반도체 장치의 단면도이다.

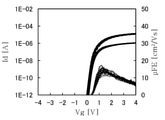

도 3의 (A)는 IGZO의 결정 구조의 분류를 설명하는 도면이다. 도 3의 (B)는 CAAC-IGZO막의 XRD 스펙트럼을 설명하는 도면이다. 도 3의 (C)는 CAAC-IGZO막의 나노빔 전자 회절 패턴을 설명하는 도면이다.

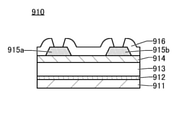

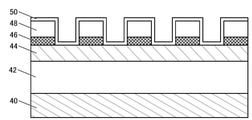

도 4의 (A)는 본 발명의 일 형태인 반도체 장치의 제작 방법을 나타낸 상면도이다. 도 4의 (B) 내지 (D)는 본 발명의 일 형태인 반도체 장치의 제작 방법을 나타낸 단면도이다.

도 5의 (A)는 본 발명의 일 형태인 반도체 장치의 제작 방법을 나타낸 상면도이다. 도 5의 (B) 내지 (D)는 본 발명의 일 형태인 반도체 장치의 제작 방법을 나타낸 단면도이다.

도 6의 (A)는 본 발명의 일 형태인 반도체 장치의 제작 방법을 나타낸 상면도이다. 도 6의 (B) 내지 (D)는 본 발명의 일 형태인 반도체 장치의 제작 방법을 나타낸 단면도이다.