KR20190000768A - 통신 또는 방송 시스템에서 채널 부호화/복호화 방법 및 장치 - Google Patents

통신 또는 방송 시스템에서 채널 부호화/복호화 방법 및 장치 Download PDFInfo

- Publication number

- KR20190000768A KR20190000768A KR1020170151743A KR20170151743A KR20190000768A KR 20190000768 A KR20190000768 A KR 20190000768A KR 1020170151743 A KR1020170151743 A KR 1020170151743A KR 20170151743 A KR20170151743 A KR 20170151743A KR 20190000768 A KR20190000768 A KR 20190000768A

- Authority

- KR

- South Korea

- Prior art keywords

- matrix

- ldpc

- exponent

- value

- bits

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0057—Block codes

- H04L1/0058—Block-coded modulation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1105—Decoding

- H03M13/1111—Soft-decision decoding, e.g. by means of message passing or belief propagation algorithms

- H03M13/1117—Soft-decision decoding, e.g. by means of message passing or belief propagation algorithms using approximations for check node processing, e.g. an outgoing message is depending on the signs and the minimum over the magnitudes of all incoming messages according to the min-sum rule

- H03M13/112—Soft-decision decoding, e.g. by means of message passing or belief propagation algorithms using approximations for check node processing, e.g. an outgoing message is depending on the signs and the minimum over the magnitudes of all incoming messages according to the min-sum rule with correction functions for the min-sum rule, e.g. using an offset or a scaling factor

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/116—Quasi-cyclic LDPC [QC-LDPC] codes, i.e. the parity-check matrix being composed of permutation or circulant sub-matrices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/118—Parity check matrix structured for simplifying encoding, e.g. by having a triangular or an approximate triangular structure

- H03M13/1185—Parity check matrix structured for simplifying encoding, e.g. by having a triangular or an approximate triangular structure wherein the parity-check matrix comprises a part with a double-diagonal

- H03M13/1188—Parity check matrix structured for simplifying encoding, e.g. by having a triangular or an approximate triangular structure wherein the parity-check matrix comprises a part with a double-diagonal wherein in the part with the double-diagonal at least one column has an odd column weight equal or greater than three

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/63—Joint error correction and other techniques

- H03M13/6306—Error control coding in combination with Automatic Repeat reQuest [ARQ] and diversity transmission, e.g. coding schemes for the multiple transmission of the same information or the transmission of incremental redundancy

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/63—Joint error correction and other techniques

- H03M13/635—Error control coding in combination with rate matching

- H03M13/6362—Error control coding in combination with rate matching by puncturing

- H03M13/6368—Error control coding in combination with rate matching by puncturing using rate compatible puncturing or complementary puncturing

- H03M13/6393—Rate compatible low-density parity check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6508—Flexibility, adaptability, parametrability and configurability of the implementation

- H03M13/6516—Support of multiple code parameters, e.g. generalized Reed-Solomon decoder for a variety of generator polynomials or Galois fields

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6522—Intended application, e.g. transmission or communication standard

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0041—Arrangements at the transmitter end

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0045—Arrangements at the receiver end

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0057—Block codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0067—Rate matching

- H04L1/0068—Rate matching by puncturing

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L2001/0092—Error control systems characterised by the topology of the transmission link

- H04L2001/0093—Point-to-multipoint

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Probability & Statistics with Applications (AREA)

- Theoretical Computer Science (AREA)

- Mathematical Physics (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Error Detection And Correction (AREA)

Abstract

본 개시는 LTE와 같은 4G 통신 시스템 이후 보다 높은 데이터 전송률을 지원하기 위한 5G 또는 pre-5G 통신 시스템에 관련된 것이다. 본 발명은 통신 또는 방송 시스템에서 채널 부호화 방법에 있어서, 입력 비트 크기를 확인하는 과정; 블록의 크기(Z)를 결정하는 과정; LDPC 부호화를 수행할 LDPC 수열을 결정하는 과정; 상기 LDPC 수열과 블록 크기에 기반하여 LDPC 부호화 하는 과정; 을 포함함을 특징으로 한다.

Description

본 발명은 통신 또는 방송 시스템에서 채널 부호화/복호화 방법 및 장치에 관한 것이다.

4G 통신 시스템 상용화 이후 증가 추세에 있는 무선 데이터 트래픽 수요를 충족시키기 위해, 개선된 5G 통신 시스템 또는 pre-5G 통신 시스템을 개발하기 위한 노력이 이루어지고 있다. 이러한 이유로, 5G 통신 시스템 또는 pre-5G 통신 시스템은 4G 네트워크 이후 (Beyond 4G Network) 통신 시스템 또는 LTE 시스템 이후 (Post LTE) 이후의 시스템이라 불리어지고 있다.

높은 데이터 전송률을 달성하기 위해, 5G 통신 시스템은 초고주파(mmWave) 대역 (예를 들어, 60기가(60GHz) 대역과 같은)에서의 구현이 고려되고 있다. 초고주파 대역에서의 전파의 경로손실 완화 및 전파의 전달 거리를 증가시키기 위해, 5G 통신 시스템에서는 빔포밍(beamforming), 거대 배열 다중 입출력(massive MIMO), 전차원 다중입출력(Full Dimensional MIMO: FD-MIMO), 어레이 안테나(array antenna), 아날로그 빔형성(analog beam-forming), 및 대규모 안테나 (large scale antenna) 기술들이 논의되고 있다.

또한 시스템의 네트워크 개선을 위해, 5G 통신 시스템에서는 진화된 소형 셀, 개선된 소형 셀 (advanced small cell), 클라우드 무선 액세스 네트워크 (cloud radio access network: cloud RAN), 초고밀도 네트워크 (ultra-dense network), 기기 간 통신 (Device to Device communication: D2D), 무선 백홀 (wireless backhaul), 이동 네트워크 (moving network), 협력 통신 (cooperative communication), CoMP (Coordinated Multi-Points), 및 수신 간섭제거 (interference cancellation) 등의 기술 개발이 이루어지고 있다.

이 밖에도, 5G 시스템에서는 진보된 코딩 변조(Advanced Coding Modulation: ACM) 방식인 FQAM (Hybrid FSK and QAM Modulation) 및 SWSC (Sliding Window Superposition Coding)과, 진보된 접속 기술인 FBMC(Filter Bank Multi Carrier), NOMA(non-orthogonal multiple access), 및 SCMA(sparse code multiple access) 등이 개발되고 있다.

통신 또는 방송 시스템에서, 링크(link) 성능은 채널의 여러 가지 잡음(noise), 페이딩(fading) 현상 및 심벌 간 간섭(ISI: inter-symbol interference)에 의해 현저히 저하될 수 있다. 따라서 차세대 이동 통신, 디지털 방송 및 휴대 인터넷과 같이 높은 데이터 처리량과 신뢰도를 요구하는 고속 디지털 통신 또는 방송 시스템들을 구현하기 위해서, 잡음, 페이딩 및 심벌 간 간섭을 극복하기 위한 기술을 개발하는 것이 요구된다. 잡음 등을 극복하기 위한 연구의 일환으로서, 최근에는 정보의 왜곡을 효율적으로 복원하여 통신의 신뢰도를 높이기 위한 방법으로서 오류정정부호(error-correcting code)에 대한 연구가 활발히 이루어지고 있다.

본 발명은 다양한 입력 길이와 부호율을 지원 할 수 있는 LDPC 부호화/복호화 방법 및 장치를 제공한다.

본 발명은 100 비트 내외의 짧은 정보어 길이를 가지며, 부호율이 정해져 있는 경우에 적합한 LDPC 부호의 설계 방법 및 부호화/복호화 방법 및 장치를 제공한다.

본 발명은 다양한 길이와 부호율이 지원 가능한 LDPC 부호의 설계에 있어서 리프팅 방법과 트랩핑 집합 특성을 동시에 고려하여 설계하는 방법을 제안한다.

본 발명은 정보 비트 수가 적고, 부호율이 고정되어 있는 경우에 적합한 전용(dedicated) LDPC 부호의 설계 방법을 제안한다.

본 발명은 가변 길이와 가변 레이트에 대하여 LDPC 부호를 지원할 수 있다.

도 1은 시스테메틱(systematic) LDPC 부호어 구조도이다.

도 2는 LDPC 부호의 그래프 표현 방법에 대해 도시한 도면이다.

도 3a 및 3b는 QC-LDPC 부호의 사이클 특성을 설명하기 위한 예시도이다.

도 4는 본 발명의 일 실시 예에 따른 송신 장치 블록 구성도이다.

도 5는 본 발명의 일 실시 예에 따른 수신 장치 블록 구성도이다.

도 6a, b는 LDPC 복호화를 위해 임의의 검사 노드와 변수 노드에서 메시지 패싱 동작을 나타낸 메시지 구조도이다.

도 7은 본 발명의 일 실시 예에 따른 LDPC 부호화부의 세부 구성을 설명하기 위한 블록도이다.

도 8은 본 발명의 일 실시 예에 따른 복호화 장치의 구성을 나타내는 블록도이다.

도 9는 본 발명의 다른 실시 예에 따른 LDPC 복호화부 구조도이다.

도 10은 본 발명의 다른 실시 예에 따른 전송 블록 구조도이다.

도 11은 본 발명의 실시 예에 따른 LDPC 부호화 과정의 예시도이다.

도 12는 본 발명의 실시 예에 따른 LDPC 복호화 과정의 예시도이다.

도 13은 본 발명의 실시 예에 따른 LDPC 부호화 과정의 다른 예시도이다.

도 14는 본 발명의 실시 예에 따른 LDPC 복호화 과정의 다른 예시도이다.

도 15는 본 발명의 실시 예에 따른 LDPC 부호화 과정의 다른 예시도이다.

도 16은 본 발명의 실시 예에 따른 LDPC 복호화 과정의 다른 예시도이다.

도 17은 본 발명의 실시 예에 따른 LDPC 부호화 과정의 다른 예시도이다.

도 18은 본 발명의 실시 예에 따른 LDPC 복호화 과정의 다른 예시도이다.

도 19, 19a, 19b, 19c, 19d, 19e, 19f, 19g, 19h 및 19i는 본 발명의 실시 예에 따른 LDPC 부호 기본 행렬의 예시도이다.

도 20, 20a, 20b, 20c, 20d, 20e, 20f, 20g, 20h 및 20i는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 예시도이다.

도 21, 21a, 21d, 21g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 22, 22a, 22d, 22g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 23, 23a, 23d, 23g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 24, 24a, 24d, 24g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 25, 25a, 25d, 25g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 26, 26a, 26d, 26g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 27, 27a, 27d, 27g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 28, 28a, 28d, 28g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 29, 29a, 29d, 29g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 30, 30a, 30d, 30g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 31, 31a, 31d, 31g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 32, 32a, 32d, 32g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 33, 33a, 33d, 33g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 34, 34a, 34d, 34g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 35, 35a, 35d, 35g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 36, 36a, 36d, 36g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 2는 LDPC 부호의 그래프 표현 방법에 대해 도시한 도면이다.

도 3a 및 3b는 QC-LDPC 부호의 사이클 특성을 설명하기 위한 예시도이다.

도 4는 본 발명의 일 실시 예에 따른 송신 장치 블록 구성도이다.

도 5는 본 발명의 일 실시 예에 따른 수신 장치 블록 구성도이다.

도 6a, b는 LDPC 복호화를 위해 임의의 검사 노드와 변수 노드에서 메시지 패싱 동작을 나타낸 메시지 구조도이다.

도 7은 본 발명의 일 실시 예에 따른 LDPC 부호화부의 세부 구성을 설명하기 위한 블록도이다.

도 8은 본 발명의 일 실시 예에 따른 복호화 장치의 구성을 나타내는 블록도이다.

도 9는 본 발명의 다른 실시 예에 따른 LDPC 복호화부 구조도이다.

도 10은 본 발명의 다른 실시 예에 따른 전송 블록 구조도이다.

도 11은 본 발명의 실시 예에 따른 LDPC 부호화 과정의 예시도이다.

도 12는 본 발명의 실시 예에 따른 LDPC 복호화 과정의 예시도이다.

도 13은 본 발명의 실시 예에 따른 LDPC 부호화 과정의 다른 예시도이다.

도 14는 본 발명의 실시 예에 따른 LDPC 복호화 과정의 다른 예시도이다.

도 15는 본 발명의 실시 예에 따른 LDPC 부호화 과정의 다른 예시도이다.

도 16은 본 발명의 실시 예에 따른 LDPC 복호화 과정의 다른 예시도이다.

도 17은 본 발명의 실시 예에 따른 LDPC 부호화 과정의 다른 예시도이다.

도 18은 본 발명의 실시 예에 따른 LDPC 복호화 과정의 다른 예시도이다.

도 19, 19a, 19b, 19c, 19d, 19e, 19f, 19g, 19h 및 19i는 본 발명의 실시 예에 따른 LDPC 부호 기본 행렬의 예시도이다.

도 20, 20a, 20b, 20c, 20d, 20e, 20f, 20g, 20h 및 20i는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 예시도이다.

도 21, 21a, 21d, 21g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 22, 22a, 22d, 22g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 23, 23a, 23d, 23g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 24, 24a, 24d, 24g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 25, 25a, 25d, 25g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 26, 26a, 26d, 26g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 27, 27a, 27d, 27g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 28, 28a, 28d, 28g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 29, 29a, 29d, 29g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 30, 30a, 30d, 30g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 31, 31a, 31d, 31g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 32, 32a, 32d, 32g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 33, 33a, 33d, 33g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 34, 34a, 34d, 34g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 35, 35a, 35d, 35g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

도 36, 36a, 36d, 36g는 본 발명의 실시 예에 따른 LDPC 부호 지수 행렬의 다른 예시도이다.

이하 본 발명의 바람직한 실시 예를 첨부된 도면의 참조와 함께 상세히 설명한다. 그리고, 본 발명을 설명함에 있어서, 관련된 공지 기능 혹은 구성에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단된 경우, 그 상세한 설명은 생략한다. 그리고 후술되는 용어들은 본 발명에서의 기능을 고려하여 정의된 용어들로서 이는 사용자, 운용자의 의도 또는 관례 등에 따라 달라질 수 있다. 그러므로 그 정의는 본 명세서 전반에 걸친 내용을 토대로 내려져야 할 것이다.

본 발명의 주요한 요지는 유사한 기술적 배경을 가지는 여타의 시스템에도 본 발명의 범위를 크게 벗어나지 아니하는 범위에서 약간의 변형으로 적용 가능하며, 이는 본 발명의 기술분야에서 숙련된 기술적 지식을 가진 자의 판단으로 가능할 것이다.

본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시 예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 수 있으며, 단지 본 실시 예들은 본 발명의 개시가 완전하도록 하고, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

1960년대에 Gallager에 의해서 처음 소개된 저밀도 패리티 체크(Low Density Parity Check, 이하 LDPC) 부호는 당시 기술 수준에서 구현하기 어려운 복잡도로 인해 오랫동안 잊혀져 왔다. 하지만, 1993년 Berrou와 Glavieux, Thitimajshima에 의해 제안된 터보(turbo) 부호가 셰논(Shannon)의 채널 용량에 근접하는 성능을 보임에 따라 터보 부호의 성능과 특성에 대한 많은 해석이 이루어지면서 반복 복호(iterative decoding)와 그래프를 기반으로 하는 채널 부호화에 대한 많은 연구가 진행되었다. 이를 계기로 1990년대 후반에 LDPC 부호가 재연구되면서 LDPC 부호에 대응되는 태너(Tanner) 그래프 상에서 합-곱(sum-product) 알고리즘에 기반한 반복 복호(iterative decoding)를 적용하여 복호화를 수행하면 LDPC 부호 또한 셰논의 채널 용량에 근접하는 성능을 가지게 됨이 밝혀졌다.

LDPC 부호는 일반적으로 패리티 검사 행렬(parity-check matrix)로 정의되며 태너 그래프로 통칭되는 이분(bipartite) 그래프를 이용하여 표현될 수 있다.

도 1은 시스테메틱(systematic) LDPC 부호어 구조도를 도시한 도면이다.

도 1에 따르면, LDPC 부호는 Kldpc 개 비트 혹은 심볼로 구성되어 있는 정보어(102)를 입력받아 LDPC 부호화를 하여 Nldpc 개 비트 혹은 심볼로 구성되어 있는 부호어(100)(codeword)를 생성한다. 이하 설명의 편의를 위해, Kldpc 개 비트를 포함하는 정보어(102)를 입력받아 Nldpc 개 비트로 구성되는 부호어(100)가 생성되는 것으로 가정한다. 즉, Kldpc 개의 입력 비트인 정보어 (102)를 LDPC 부호화하면, 부호어 (100)가 생성된다. 즉, 정보어 및 부호어는 다수의 비트로 구성되어 있는 비트열이며, 정보어 비트 및 부호어 비트는 정보어 및 부호어를 구성하는 각각의 비트를 의미한다. 통상적으로 부호어가 와 같이 정보어를 포함하고 있을 경우 시스테메틱(systemetic) 부호라 한다. 여기에서, 는 패리티 비트(104)이고, 패리티 비트의 개수 Nparity는 Nparity=Nldpc - Kldpc 로 나타낼 수 있다.

LDPC 부호는 선형 블록 부호(linear block code)의 일종으로 아래의 수학식 1과 같은 조건을 만족하는 부호어를 결정하는 과정을 포함한다.

[수학식 1]

수학식 1에서, H는 패리티 검사 행렬, C는 부호어, ci는 부호어의 i 번째 비트, Nldpc는 LDPC 부호어 길이를 의미한다. 여기서 hi는 패리티 검사 행렬(H)의 i번째 열(column)을 의미한다.

패리티 검사 행렬 H는 LDPC 부호어의 비트 개수와 동일한 Nldpc 개의 열(column)로 구성되어 있다. 수학식 1은 패리티 검사 행렬의 i 번째 열(hi)과 i 번째 부호어 비트 ci의 곱의 합이 '0'이 됨을 의미하므로, i 번째 열(hi)은 i 번째 부호어 비트 ci와 관계가 있음을 의미한다.

도 2를 참조하여 LDPC 부호의 그래프 표현 방법에 대해 설명하기로 한다.

도 2는 4 개의 행(row)와 8 개의 열(column)로 이루어진 LDPC 부호의 패리티 검사 행렬 H1의 일 예와 이를 태너 그래프(Tanner graph)로 도시한 도면이다. 도 2를 참조하면, 패리티 검사 행렬 H1은 열이 8개 있기 때문에 길이가 8인 부호어(codeword)를 생성하며, H1을 통해 생성된 부호는 LDPC 부호를 의미하며, 각 열은 부호화된 8 비트에 대응된다.

도 2를 참조하면, 패리티 검사 행렬 H1을 기반으로 부호화 및 복호화하는 LDPC 부호의 태너 그래프는 8 개의 변수 노드(variable node)들 즉, x1(202), x2(204), x3(206), x4(208), x5(210), x6(212), x7(214), x8(216)와 4 개의 검사 노드(check node)(218, 220, 222, 224)들로 구성되어 있다. 여기서, LDPC 부호의 패리티 검사 행렬 H1의 i 번째 열과 j 번째 행은 각각 변수 노드 xi와 j 번째 검사 노드에 대응된다. 또한, LDPC 부호의 패리티 검사 행렬 H1의 j 번째 열과 j 번째 행이 교차하는 지점의 1의 값, 즉 0이 아닌 값의 의미는, 도 2와 같이 태너 그래프 상에서 변수 노드 xi와 j 번째 검사 노드를 연결하는 선분(edge)이 존재함을 의미한다.

LDPC 부호의 태너 그래프에서 변수 노드와 검사 노드의 차수(degree)는 각 노드들에 연결되어 있는 선분의 개수를 의미하며, 이는 LDPC 부호의 패리티 검사 행렬에서 해당 노드에 대응되는 열 또는 행에서 0이 아닌 원소(entry)들의 개수와 동일하다. 예를 들어, 도 2에서 변수 노드들 x1(202), x2(204), x3(206), x4(208), x5(210), x6(212), x7(214), x8(216)의 차수는 각각 순서대로 4, 3, 3, 3, 2, 2, 2, 2가 되며, 검사 노드들(218, 220, 222, 224)의 차수는 각각 순서대로 6, 5, 5, 5가 된다. 또한, 도 2의 변수 노드에 대응되는 도 2의 패리티 검사 행렬 H1의 각각의 열에서 0이 아닌 원소들의 개수는 상술한 차수들 4, 3, 3, 3, 2, 2, 2, 2와 순서대로 일치하며, 도 2의 검사 노드들에 대응되는 도 2의 패리티 검사 행렬 H1의 각각의 행에서 0이 아닌 원소들의 개수는 상술한 차수들 6, 5, 5, 5와 순서대로 일치한다.

LDPC 부호는 도 2에서 나열한 bipartite 그래프 상에서 합곱(sum-product) 알고리즘(algorithm)에 기반한 반복 복호(iterative decoding) 알고리즘을 사용하여 복호할 수 있다. 여기서, 합곱 알고리즘은 메시지 패싱 알고리즘(message passing algorithm)의 일종이며, 메시지 패싱 알고리즘이라 함은 이분 그래프 상에서 에지를 통해 메시지들을 교환하고, 변수 노드 혹은 검사 노드로 입력되는 메시지들로부터 출력 메시지를 계산하여 업데이트하는 알고리즘을 나타낸다.

여기에서, i 번째 변수 노드의 메시지를 기반으로 i 번째 부호화 비트의 값을 결정할 수 있다. i 번째 부호화 비트의 값은 경판정(hard decision)과 연판정(soft decision) 모두 가능하다. 그러므로, LDPC 부호어의 i 번째 비트인 ci의 성능은 태너 그래프의 i 번째 변수 노드의 성능에 대응되며, 이는 패리티 검사 행렬의 i 번째 열의 1의 위치 및 개수에 따라 결정될 수 있다. 다시 말해, 부호어의 Nldpc 개의 부호어 비트들의 성능은 패리티 검사 행렬의 1의 위치 및 개수에 의해 성능이 좌우 될 수 있으며, 이는 LDPC 부호의 성능은 패리티 검사 행렬에 따라 많은 영향을 받음을 의미한다. 따라서 우수한 성능을 갖는 LDPC 부호를 설계 하기 위해서는 좋은 패리티 검사 행렬을 설계하는 방법이 필요하다.

통신 및 방송 시스템에서 사용되는 패리티 검사 행렬은 구현의 용이성을 위해 통상적으로 준순환(quasi-cyclic) 형태의 패리티 검사 행렬을 사용하는 준순환 LDPC 부호(또는 QC-LDPC 부호, 이하 QC-LDPC 부호)가 많이 사용된다.

QC-LDPC 부호는 작은 정사각 행렬의 형태를 가지는 0-행렬(zero matrix)이나 순환 순열 행렬(circulant permutation matrices)로 구성된 패리티 검사 행렬을 가짐을 특징으로 한다. 이 때, 순열 행렬이란 정사각 행렬의 모든 원소가 0 또는 1이고, 각 행이나 열이 오직 하나의 1만을 포함하는 행렬을 의미한다. 또한, 순환 순열 행렬이란, 항등 행렬의 각 원소들을 오른쪽으로 순환 이동 시킨 행렬을 의미한다.

이하에서는, QC-LDPC 부호에 대해서 구체적으로 설명한다.

먼저, 수학식 2와 같이 크기의 순환 순열 행렬 을 정의한다. 여기서 는 행렬 상기 행렬 P에서의 i번째 행(row), j번째 열(column)의 원소(entry)를 의미한다.(0 ≤i, j < L)

[수학식 2]

상기와 같이 정의된 순열 행렬 P에 대해서 (0 ≤ i < L)는 크기의 항등 행렬(identity matrix)의 각 원소들을 i 번 만큼 오른쪽 방향으로 순환 이동(circular shift) 시킨 형태의 순환 순열 행렬임을 알 수 있다.

가장 간단한 QC-LDPC 부호의 패리티 검사 행렬 H는 다음 수학식 3와 같은 형태로 나타낼 수 있다.

[수학식 3]

만일 을 크기의 0-행렬이라 정의할 경우, 상기 수학식 3에서 순환 순열 행렬 또는 0-행렬의 각 지수 는 {-1, 0, 1, 2, ..., L-1} 값 중에 하나를 가지게 된다. 또한 상기 수학식 3의 패리티 검사 행렬 H는 열 블록(column block)이 n개, 행 블록이 m개이므로, 크기를 가지게 됨을 알 수 있다.

상기 수학식 3의 패리티 검사 행렬이 완전 계수(full rank)를 가진다면, 상기 패리티 검사 행렬에 대응되는 QC-LDPC 부호의 정보어 비트의 크기는 (n-m)L 이 됨은 자명하다. 편의상 정보어 비트에 대응되는 (n-m)개의 열 블록을 정보어 열 블록이라 부르고, 나머지 패리티 비트에 대응되는 m개의 열 블록을 패리티 열 블록이라 부른다.

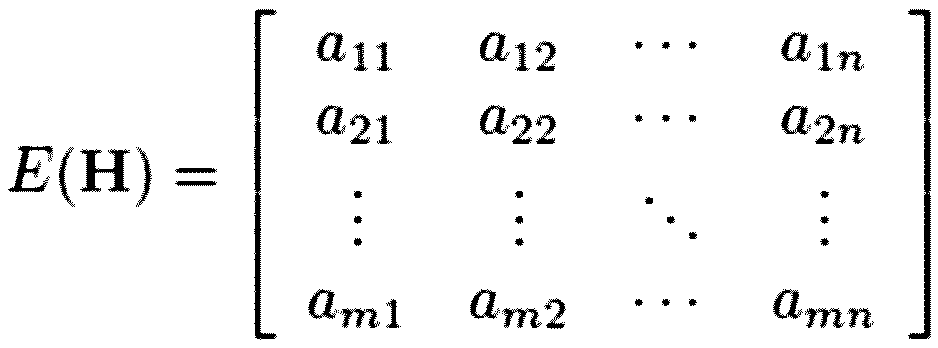

통상적으로 상기 수학식 3의 패리티 검사 행렬에서 각 순환 순열 행렬 및 0-행렬을 각각 1과 0으로 치환(replace)하여 얻은 크기의 이진(binary) 행렬을 패리티 검사 행렬 H의 모행렬(mother matrix) 또는 기본 행렬(base matrix) M(H)라 하고, 각 순환 순열 행렬 또는 0-행렬의 지수를 선택하여 수학식 4와 같이 얻은 크기의 정수 행렬을 패리티 검사 행렬 H의 지수 행렬 E(H)라 한다.

[수학식 4]

결과적으로 지수 행렬에 포함되어 있는 정수 1개는 패리티 검사 행렬에서의 순환 순열 행렬에 대응되므로 상기 지수 행렬은 편의상 정수로 이루어진 수열들로 표현할 수도 있다. (상기 수열은 다른 수열과 구분하기 위하여 LDPC 수열 또는 LDPC 부호 수열이라고 부르기도 한다). 일반적으로 패리티 검사 행렬은 지수 행렬 뿐만 아니라 대수적으로 동일한 특성을 가지는 수열로도 표현 가능하다. 본 발명에서는 편의상 패리티 검사 행렬을 지수 행렬 또는 패리티 검사 행렬 내에 있는 1의 위치를 나타내는(indicate) 수열 등으로 표현하였으나, 패리티 검사 행렬에 포함되어 있는 1 또는 0의 위치를 구분할 수 있는 수열 표기 법은 다양하므로, 본 명세서에 표현한 방법에 국한되지 않고 대수적으로 동일한 효과를 나타내는 다양한 수열의 형태로 나타낼 수 있다.

또한 디바이스 상의 송수신 장치에서도 패리티 검사행렬을 직접 생성하여 LDPC 부호화 및 복호화를 수행할 수도 있지만, 구현 상의 특징에 따라 상기 패리티 검사행렬과 대수적으로 동일한 효과를 내는 지수 행렬이나 수열을 이용하여 LDPC 부호화 및 복호화를 수행할 수도 있다. 따라서 본 발명에서 편의상 패리티 검사 행렬을 이용한 부호화 및 복호화에 대해서 설명하고 있지만, 실제 디바이스 상에서는 상기 패리티 검사 행렬과 동일한 효과를 얻을 수 있는 다양한 방법을 통해 구현 가능함을 고려하고 있음을 밝혀둔다.

참고로 대수적으로 동일한 효과란, 서로 다른 두 개 이상의 표현에 대해서 논리적 또는 수학적으로 서로 간에 완벽하게 동일함을 설명 가능하거나 변환 가능함을 의미한다.

본 발명에서는 편의상 하나의 블록에 대응되는 순환 순열 행렬이 1 개인 경우만 설명하였으나, 이하 하나의 블록에 여러 개의 순환 순열 행렬이 포함된 경우에도 동일한 발명을 적용할 수 있다. 예를 들어 다음 수학식 5와 같이 하나의 i 번째 행 블록 및 j 번째 열 블록의 위치에 2 개의 순환 순열 행렬 의 합으로 포함되어 있을 때, 그 지수 행렬은 수학식 6과 같이 나타낼 수 있다. 상기 수학식 6을 살펴보면, 상기 복수 개의 순환 순열 행렬 합이 포함된 행 블록 및 열 블록에 대응되는 i 번째 행 및 j 번째 열에 2 개의 정수가 대응되는 행렬임을 알 수 있다.

[수학식 5]

[수학식 6]

상기 실시 예와 같이 일반적으로 QC-LDPC 부호는 패리티 검사행렬에서 하나의 행 블록 및 열 블록에 복수 개의 순환 순열 행렬이 대응될 수 있으나 본 발명에서는 편의상 하나의 블록에 하나의 순환 순열 행렬이 대응되는 경우에 대해서만 설명하지만, 발명의 요지는 그에 한정되지 않는다. 참고로 이와 같이 하나의 행 블록 및 열 블록에 복수 개의 순환 순열 행렬이 중복되어 있는 크기의 행렬을 순환 행렬(circulant matrix 또는 circulant)이라 한다.

한편, 상기 수학식 5 및 수학식 6의 패리티 검사 행렬 및 지수 행렬에 대한 모행렬 또는 기본행렬은 상기 수학식 3에서 사용된 정의와 유사하게 각 순환 순열 행렬 및 0-행렬을 각각 1과 0으로 치환(replace)하여 얻은 이진(binary) 행렬을 의미하는데, 하나의 블록에 포함된 복수 개의 순환 순열 행렬의 합 (즉, 순환 행렬) 또한 단순히 1로 치환한다.

LDPC 부호의 성능은 패리티 검사 행렬에 따라 결정되기 때문에 우수한 성능을 갖는 LDPC 부호를 위해 패리티 검사 행렬을 설계하는 것이 필요하다. 또한 다양한 입력 길이와 부호율을 지원할 수 있는 LDPC 부호화 또는 복호화 방법이 필요하다.

리프팅(Lifting)은 QC-LDPC 부호의 효율적인 설계를 위해서 사용될 뿐만 아니라, 주어진 지수 행렬로부터 다양한 길이의 패리티 검사 행렬을 생성하거나 LDPC 부호어를 생성하기 위해서 사용되는 방법을 의미한다. 즉, 상기 리프팅은 주어진 작은 모행렬로부터 순환 순열 행렬 또는 0-행렬의 크기를 결정하는 L 값을 특정한 규칙에 따라 설정함으로써 효율적으로 매우 큰 패리티 검사 행렬을 설계하는데 적용하거나, 주어진 지수 행렬 또는 그에 대응되는 수열에 적절한 L 값을 적용함으로써 다양한 길이의 패리티 검사 행렬을 생성하거나 LDPC 부호어를 생성하는 방법을 의미한다.

기존 리프팅 방법과 이렇게 리프팅을 통해 설계된 QC-LDPC 부호의 특징을 다음과 같은 참조문헌 [Myung2006]을 참고하여 간단히 설명한다.

Reference [Myung2006]

S. Myung, K. Yang, and Y. Kim, "Lifting Methods for Quasi-Cyclic LDPC Codes," IEEE Communications Letters. vol. 10, pp. 489-491, June 2006.

먼저 LDPC 부호 C0가 주어져 있을 때 리프팅 방법을 통해 설계될 S개의 QC-LDPC 부호를 C1, ..., CS라 하고, 상기 각 QC-LDPC 부호의 패리티 검사 행렬의 행블록 및 열블록의 크기에 해당하는 값은 Lk라 한다. 여기서 C0는 C1, ..., CS 부호의 모행렬을 패리티 검사 행렬로 가지는 가장 작은 LDPC 부호에 해당하며 행블록 및 열블록의 크기에 해당하는 L0 값은 1이다. 또, 편의상 각 부호 Ck의 패리티 검사 행렬 는 크기의 지수 행렬 을 가지며 각 지수 들은 {-1, 0, 1, 2, ..., Lk - 1} 값 중에 하나로 선택된다.

기존 리프팅 방법은 C0 → C1 →...→ CS와 같은 단계로 이루어지며 Lk +1 = qk + 1Lk (qk +1은 양의 정수, k=0,1,..., S-1)와 같은 조건을 만족하는 특징을 가진다. 또한 리프팅 과정의 특성에 의해 CS의 패리티 검사 행렬 만 저장하고 있으면 리프팅 방식에 따라 다음 수학식 7을 이용하여 상기 QC-LDPC 부호 C0, C1, ..., CS를 모두 나타낼 수 있다.

[수학식 7]

또는

[수학식 8]

이와 같이 C0로부터 보다 큰 QC-LDPC 부호 C1, ..., CS 등을 설계하는 방법 뿐만 아니라 큰 부호 Ck로부터 수학식 7 또는 수학식 8과 같이 적절한 방법을 이용하여 작은 부호 Ci(i=k-1, k-2, … 1, 0)를 생성하는 방법을 리프팅이라 부른다.

상기 수학식 7 또는 8의 리프팅 방식은 각 QC-LDPC 부호 Ck의 패리티 검사 행렬에서 행블록 또는 열블록의 크기에 해당하는 Lk들이 서로 배수 관계(multiple)를 가지게 되어, 지수 행렬 또한 특정 방식에 의해 선택된다. 이와 같은 기존 리프팅 방식은 리프팅을 통해 설계된 각 패리티 검사 행렬의 대수적 또는 그래프 특성을 좋게 하여 오류 마루(error floor) 특성을 개선한 QC-LDPC 부호를 쉽게 설계할 수 있게 돕는다.

하지만, 각 Lk 값들이 서로 배수 관계에 있기 때문에 각 부호의 길이가 크게 제한되는 단점이 있다. 예를 들어 각 Lk 값들에 대해 Lk +1 = 2×Lk와 같은 최소한의 리프팅 방식을 적용하였다고 가정시, 이 경우 각 QC-LDPC 부호의 패리티 검사 행렬의 크기는 만을 가질 수 있다. 즉, 리프팅을 10 단계 적용할 경우(S=10) 패리티 검사 행렬의 크기는 총 10 가지를 생성할 수 있으며, 이는 곧 10 가지 종류의 길이를 가지는 QC-LDPC 부호를 지원할 수 있음을 의미한다.

이와 같은 이유로 다양한 길이를 지원하는 QC-LDPC 부호를 설계하는데 있어서 기존 리프팅 방식은 다소 불리한 특성을 가지고 있다. 하지만, 통상적으로 사용되는 통신 시스템에서는 다양한 형태의 데이터 전송을 고려하여 매우 높은 수준의 길이 호환성(length compatibility)을 요구하게 된다. 이러한 이유로 기존 리프팅 방식에 기반한 LDPC 부호화 기법은 통신 시스템에서 적용하기 어려운 문제점이 있다.

이와 같은 문제를 해결하기 위하여 본 발명에서는 다음과 같은 리프팅 방법을 이용한다.

일반적으로 리프팅은 도 4의 지수 행렬을 다양한 L 값에 대해 그 원소들의 값들을 변경하여 LDPC 부호화 및 복호화에 사용하는 것으로 생각할 수도 있다. 예를 들어, 상기 도 4의 지수 행렬을 라 하고, L 값에 따라 변환된 지수 행렬을 이라 할 때 일반적으로 다음과 수학식 9와 같은 변환식을 적용할 수 있다.

[수학식 9]

[수학식 10]

상기 수학식 10에서 mod(a,b)는 a에 대한 모듈로-b 연산을 의미하며, D는 사전에 정의된 양의 정수인 상수를 의미한다.

참고로 상기 수학식 9의 변환식에서 변환식 f를 적용하는 기준을 편의상 0으로 나타내었으나 그 기준 값은 지원하고자 하는 블록 크기 L 값에 따라 다르게 설정할 수 있다.

도 4는 본 발명의 일 실시 예에 따른 송신 장치 블록 구성도이다.

구체적으로, 도 4과 같이, 송신 장치(400)는 가변 길이 입력 비트들을 처리하기 위해, 세그멘터이션부(410), 제로 패딩부(420), LDPC 부호화부(430), 레이트 매칭부(440), 변조부(450) 등을 포함할 수 있다. 레이트 매칭부(440)은 인터리버(441) 및 천공/리피티션(repetition)/제로 제거부(442) 등을 포함할 수 있다.

여기에서, 도 4에 도시된 구성 요소는, 가변 길이 입력 비트들에 대한 부호화 및 변조를 수행하는 구성 요소로서, 이는 일 예일 뿐이며, 경우에 따라 도 4에 도시된 구성요소 중 일부는 생략 또는 변경될 수 있고, 다른 구성요소가 더 추가될 수도 있다.

한편, 송신 장치(400)는 필요한 파라미터(가령, 입력 비트 길이, ModCod(modulation and code rate), 제로 패딩 (또는 단축)을 위한 파라미터, LDPC 부호의 부호율/부호어 길이, 인터리빙(interleaving)을 위한 파라미터, 리피티션(repetition) 및 펑처링(puncturing) 등을 위한 파라미터 및 변조 방식 등)를 결정하고, 결정된 파라미터를 기초로 부호화하여 수신 장치(500)로 전송할 수 있다.

입력 비트들의 수가 가변적이라는 점에서, 입력 비트들의 수가 기설정된 값보다 큰 경우, 기설정된 값 이하의 길이를 갖도록 세그먼테이션 될 수 있다. 또한 세그먼트된 블록 각각은 하나의 LDPC 코딩된 블록에 대응될 수 있다. 다만, 입력 비트들의 수가 기 설정된 값보다 작거나 같은 경우, 세그먼테이션 되지 않는다. 입력 비트들은 하나의 LDPC 코딩된 블록에 대응될 수 있다.

한편, 송신 장치(400)는 부호화, 인터리빙 및 변조에 이용되는 각종 파라미터를 기저장하고 있을 수 있다. 여기에서, 부호화에 이용되는 파라미터는 LDPC 부호의 부호율, 부호어 길이, 패리티 검사 행렬에 대한 정보가 될 수 있다. 그리고, 인터리빙에 이용되는 파리미터는 인터리빙 룰에 대한 정보가 될 수 있으며, 변조에 이용되는 파리미터는 변조 방식에 대한 정보가 될 수 있다. 또한 펑처링에 관한 정보는 펑처링 길이가 될 수 있다. 또한 리피티션에 관한 정보는 리피티션 길이가 될 수 있다. 상기 패리티 검사 행렬에 대한 정보는 본 발명에서 제시하는 패리티 행렬을 사용할 경우 순환 행렬의 지수 값을 저장 할 수 있다.

이 경우, 송신 장치(400)를 구성하는 각 구성 요소를 이러한 파라미터를 이용하여 동작을 수행할 수 있다.

한편, 도시하지 않았지만 경우에 따라 송신 장치(400)는 송신 장치(400)의 동작을 제어하기 위한 제어부(미도시)를 더 포함할 수도 있다.

도 5는 본 발명의 일 실시 예에 따른 수신 장치 블록 구성도이다.

구체적으로, 도 5와 같이, 수신 장치(500)는 가변 길이 정보들을 처리하기 위해, 복조부(510), 레이트 디매칭부(520), LDPC 복호화부(530), 제로 제거부(540) 및 디세그멘테이이션부(550) 등을 포함할 수 있다. 레이트 디매칭부(520)는 LLR(log likelihood ratio) 삽입부(522), LLR 컴바이너(523), 디인터리버(524) 등을 포함할 수 있다.

여기에서, 도 5에 도시된 구성요소는, 도 5에 도시된 구성요소에 대응되는 기능을 수행하는 구성요소로서, 이는 일 예일 뿐이고 경우에 따라 일부는 생략 또는 변경될 수 있고, 다른 구성요소가 더 추가될 수도 있다.

본 발명에서의 패리티 검사 행렬은 메모리를 이용하여 독출할 수도 있고, 송신 장치 또는 수신 장치에서 사전에 주어질 수도 있고, 송신 장치 또는 수신 장치에서 직접 생성될 수도 있다. 또한 송신 장치는 상기 패리티 검사 행렬에 대응되는 수열 또는 지수 행렬 등을 저장 또는 생성하여 부호화에 적용할 수 있다. 마찬가지로 수신 장치에서도 상기 패리티 검사 행렬에 대응되는 수열 또는 지수 행렬 등을 저장 또는 생성하여 복호화에 적용될 수 있음은 물론이다.

이하에서는 도 5를 기반으로 수신기 동작에 대한 구체적인 설명을 하도록 한다.

복조부(510)는 송신 장치(400)로부터 수신된 신호를 복조한다.

구체적으로, 복조부(510)는 송신 장치(400)의 변조부(450)에 대응되는 구성요소로, 송신 장치(400)로부터 수신된 신호를 복조하여, 송신 장치(400)에서 전송한 비트들에 대응되는 값들을 생성할 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)에서 모드에 따라 변조한 변조 방식에 대한 정보를 기저장할 수 있다. 이에 따라, 복조부(510)는 모드에 따라 송신 장치(400)로부터 수신된 신호를 복조하여, LDPC 코드워드 비트들에 대응되는 값들을 생성할 수 있다.

한편, 송신 장치(400)에서 전송한 비트들에 대응되는 값은 LLR(Log Likelihood Ratio) 값일 수 있다.

구체적으로, LLR 값은 송신 장치(400)에서 전송한 비트가 0일 확률과 1일 확률의 비율에 Log를 취한 값으로 나타낼 수 있다. 또는, LLR 값은 비트 값 자체가 될 수 있으며, 또한, LLR 값은 송신 장치(400)에서 전송한 비트가 0 또는 1일 확률이 속하는 구간에 따라 결정된 대표 값이 될 수도 있다.

상기 복조부(510)는 LLR 값에 대한 멀티플렉싱(미도시)을 수행하는 과정을 포함한다. 구체적으로, 송신 장치(400)의 비트 디먹스(미도시)에 대응되는 구성요소로, 비트 디먹스(미도시)에 대응되는 동작을 수행할 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)가 디멀티플렉싱 및 블록 인터리빙을 위해 이용하였던 파라미터에 대한 정보를 기저장하고 있을 수 있다. 이에 따라, 먹스(미도시)는 셀 워드에 대응되는 LLR 값에 대해 비트 디먹스(미도시)에서 수행된 디멀티플렉싱 및 블록 인터리빙 동작을 역으로 수행하여, 셀 워드에 대응되는 LLR 값을 비트 단위로 멀티플렉싱할 수 있다.

레이트 디매칭부(520)은 복조부(510)로부터 출력되는 LLR 값에 LLR 값을 삽입할 수 있다. 이 경우, 레이트 디매칭부(520)는 복조부(510)로부터 출력되는 LLR 값들의 사이에 미리 약속된 LLR 값들을 삽입할 수 있다.

구체적으로, 레이트 디매칭부(520)는 송신 장치(400)의 레이트 매칭부(440)에 대응되는 구성요소로, 인터리버(441), 제로 제거 및 펑처링/리피티션/제로 제거부(442)에 대응되는 동작을 수행할 수 있다.

먼저, 레이트 디매칭부(520)는 상기 송신기의 인터리버(441)에 상응하도록 디인터리빙 하도록 한다. 디인터리버(524)의 출력 값들은 LLR 삽입부(522)에서 LDPC 코드워드에서 제로 비트들이 패딩되었던 위치에 제로 비트들에 대응되는 LLR 값을 삽입할 수 있다. 이 경우, 패딩되었던 제로 비트들 즉, 쇼트닝된 제로 비트들에 대응되는 LLR 값은 ∞ 또는 -∞가 될 수 있다. 하지만, ∞ 또는 -∞는 이론적인 값이며, 실질적으로는 수신 장치(500)에서 이용되는 LLR 값의 최대값 또는 최소값이 될 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)가 제로 비트들을 패딩하기 위해 이용하였던 파라미터에 대한 정보를 기저장하고 있을 수 있다. 이에 따라, 레이트 디매칭부(520)는 LDPC 코드워드에서 제로 비트들이 패딩되었던 위치를 판단하고, 해당 위치에 쇼트닝된 제로 비트들에 대응되는 LLR 값을 삽입할 수 있다.

또한, 레이트 디매칭부(520)의 LLR 삽입부(522)에서는 LDPC 코드워드에서 펑처링된 비트들의 위치에 펑처링된 비트들에 대응되는 LLR 값을 삽입할 수 있다. 이 경우, 펑처링된 비트들에 대응되는 LLR 값은 0이 될 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)에서 펑처링을 위해 이용한 파라미터에 대한 정보를 기저장할 수 있다. 이에 따라, LLR 삽입부(522)는 LDPC 패리티 비트들이 펑처링된 위치에 그에 대응되는 LLR 값을 삽입할 수 있다.

LLR 컴바이너(523)는 LLR 삽입부(522) 및 복조부(510)에서 출력되는 LLR 값을 컴바인 즉, 합산할 수 있다. 구체적으로, LLR 컴바이너(523)는 송신 장치(400)의 펑처링/리피티션/제로 제거부(442)에 대응되는 구성요소로, 리피티션부(442)에 대응되는 동작을 수행할 수 있다. 먼저, LLR 컴바이너(523)는 리피티션된 비트들에 대응되는 LLR 값을 다른 LLR 값과 컴바인할 수 있다. 여기에서, 다른 LLR 값은 송신 장치(400)에서 리피티션된 비트들 생성에 기초가 된 비트들 즉, 리피티션 대상으로 선택되었던 LDPC 패리티 비트들에 대한 LLR 값일 수 있다.

즉, 상술한 바와 같이, 송신 장치(400)는 LDPC 패리티 비트들에서 비트들을 선택하고, 이들을 LDPC 정보어 비트들 및 LDPC 패리티 비트들 사이에서 리피티션시켜 수신 장치(500)로 전송하게 된다.

이에 따라, LDPC 패리티 비트들에 대한 LLR 값은 리피티션된 LDPC 패리티 비트들에 대한 LLR 값 및 리피티션되지 않은 LDPC 패리티 비트들 즉, 부호화에 의해 생성된 LDPC 패리티 비트들에 대한 LLR 값으로 구성될 수 있다. 따라서, LLR 컴바이너(523)는 동일한 LDPC 패리티 비트들에 LLR 값들을 컴바인할 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)에서 리피티션을 위해 이용한 파라미터에 대한 정보를 기저장할 수 있다. 이에 따라, LLR 컴바이너(523)는 리피티션된 LDPC 패리티 비트들에 대한 LLR 값을 판단하고, 이를 리피티션의 기초가 된 LDPC 패리티 비트들에 대한 LLR 값과 컴바인할 수 있다.

또한, LLR 컴바이너(523)는 재전송 혹은 IR(Increment Redundancy)된 비트들에 대응되는 LLR 값을 다른 LLR 값과 컴바인할 수 있다. 여기에서, 다른 LLR 값은 송신 장치(400)에서 재전송 혹은 IR된 비트들 생성에 기초가 된 LDPC 부호어 비트들 생성을 위해 선택되었던 비트들에 대한 LLR 값일 수 있다.

즉, 상술한 바와 같이, 송신 장치(400)는 HARQ를 위하여 NACK이 발생할 경우 부호어 비트들중 일부 비트들 혹은 모든 비트들을 수신 장치(500)로 전송할 수 있다.

이에 따라, LLR 컴바이너(523)는 재전송 혹은 IR을 통해 수신된 비트들에 대한 LLR 값을 이전 프레임을 통해 수신되는 LDPC 코드워드 비트들에 대한 LLR 값과 컴바인할 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)에서 재전송 혹은 IR비트들 생성을 위해 이용한 파라미터에 대한 정보를 기저장할 수 있다. 이에 따라, LLR 컴바이너(523)는 재전송 혹은 IR비트들의 수에 대한 LLR 값을 판단하고, 이를 재전송 비트들의 생성에 기초가 된 LDPC 패리티 비트들에 대한 LLR 값과 컴바인할 수 있다.

디인터리버(524)는 LLR 컴바이너(523)에서 출력되는 LLR 값을 디인터리빙 할 수 있다.

구체적으로, 디인터리버부(524)는 송신 장치(400)의 인터리버(441)에 대응되는 구성요소로, 인터리버(441)에 대응되는 동작을 수행할 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)가 인터리빙을 위해 이용하였던 파라미터에 대한 정보를 기저장하고 있을 수 있다. 이에 따라, 디인터리버(524)는 LDPC 코드워드 비트들에 대응되는 LLR 값에 대해 인터리버(441)에서 수행된 인터리빙 동작을 역으로 수행하여, LDPC 코드워드 비트들에 대응되는 LLR 값을 디인터리빙 할 수 있다.

LDPC 복호화부(530)는 레이트 디매칭부(520)에서 출력되는 LLR 값에 기초하여 LDPC 복호화를 수행할 수 있다.

구체적으로, LDPC 복호화부(530)는 송신 장치(400)의 LDPC 부호화부(430)에 대응되는 구성요소로, LDPC 부호화부(430)에 대응되는 동작을 수행할 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)에서 모드에 따라 LDPC 부호화를 수행하기 위해 이용하였던 파라미터에 대한 정보를 기저장하고 있을 수 있다. 이에 따라, LDPC 복호화부(530)는 모드에 따라 레이트 디매칭부(520)에서 출력되는 LLR 값에 기초하여 LDPC 복호화를 수행할 수 있다.

예를 들어, LDPC 복호화부(530)는 합곱 알고리즘에 기반한 반복 복호 방식에 기초하여 레이트 디매칭부(520)에서 출력되는 LLR 값에 기초하여 LDPC 복호화를 수행하고, LDPC 복호화에 따라 에러가 정정된 비트들을 출력할 수 있다.

제로 제거부(540)는 LDPC 복호화부(530)에서 출력되는 비트들에서 제로 비트들을 제거할 수 있다.

구체적으로, 제로 제거부(540)는 송신 장치(400)의 제로 패딩부(420)에 대응되는 구성요소로, 제로 패딩부(420)에 대응되는 동작을 수행할 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)에서 제로 비트들을 패딩하기 위해 이용하였던 파라미터에 대한 정보를 기저장하고 있을 수 있다. 이에 따라, 제로 제거부(540)는 LDPC 복호화부(530)에서 출력되는 비트들에서 제로 패딩부(420)에서 패딩되었던 제로 비트들을 제거할 수 있다.

디세그먼테이션부(550)는 송신 장치(400)의 세그먼테이션부(410)에 대응되는 구성요소로, 세그먼테이션부(410)에 대응되는 동작을 수행할 수 있다.

이를 위해, 수신 장치(500)는 송신 장치(400)가 세그먼테이션을 위해 이용하였던 파라미터에 대한 정보를 기저장하고 있을 수 있다. 이에 따라, 디세그먼테이션부(550)는 제로 제거부(540)에서 출력되는 비트들 즉, 가변 길이 입력 비트들에 대한 세그먼트들을 결합하여, 세그먼테이션 전의 비트들을 복원할 수 있다.

한편, LDPC 부호는 도 2에서 나열한 이분 그래프 상에서 합곱 알고리즘에 기반한 반복 복호 알고리즘을 사용하여 복호할 수 있으며, 합곱 알고리즘은 메시지 패싱 알고리즘의 일종이다.

이하에서는, 도 6a, b를 참조하여 LDPC 복호화 시 일반적으로 사용되는 메시지 패싱 동작에 대해서 설명하기로 한다.

도 6a, 6b는 LDPC 복호화를 위해 임의의 검사 노드와 변수 노드에서 메시지 패싱 동작을 나타낸다.

도 6a에는 검사 노드 m(600)과 검사 노드 m(600)에 연결되는 다수의 변수 노드들(610, 620, 630, 640)이 도시되어 있다. 또한, 도시되어 있는 Tn',m은 변수 노드 n'(610)에서 검사 노드 m(600)으로 패싱되는 메시지를 나타내며, En,m은 검사 노드 m(600)에서 변수 노드 n(630)으로 패싱되는 메시지를 나타낸다. 여기서, 검사 노드 m(600)에 연결되어 있는 모든 변수 노드들의 집합을 N(m)이라고 정의하고, N(m)에서 변수 노드 n(630)을 제외한 집합을 N(m)\n이라고 정의하기로 한다.

이 경우, 합곱 알고리즘에 기반한 메시지 업데이트(update) 규칙은 하기 수학식 11와 같이 나타낼 수 있다.

[수학식 11]

여기에서, Sign(En,m)은 메시지 En,m의 부호(sign)를 나타내고, |En,m|은 메시지 En,m의 크기(magnitude)를 나타낸다. 한편, 함수 는 하기의 수학식 12와 같이 나타낼 수 있다.

[수학식 12]

한편, 도 6b에는 변수 노드 x(650)과 변수 노드 x(650)에 연결되는 다수의 검사 노드들(660, 670, 680, 690)이 도시되어 있다. 또한, 도시되어 있는 Ey ',x은 검사 노드 y'(660)에서 변수 노드 x(650)로 패싱되는 메시지를 나타내며, Ty,x은 변수 노드 x(650)에서 변수 노드 y(680)로 패싱되는 메시지를 나타낸다. 여기서, 변수 노드 x(650)에 연결되어 있는 모든 변수 노드들의 집합을 M(x)이라고 정의하고, M(x)에서 검사 노드 y(680)을 제외한 집합을 M(x)\y라고 정의하기로 한다. 이 경우, 합곱 알고리즘에 기반한 메시지 업데이트(update) 규칙은 하기 수학식 13과 같이 나타낼 수 있다.

[수학식 13]

여기에서, Ex는 변수 노드 x의 초기 메시지 값을 의미한다.

또한, 노드 x의 비트 값을 판정할 경우에는 하기 수학식 14와 같이 나타낼 수 있다.

[수학식 14]

이 경우, Px값에 따라 노드 x에 대응하는 부호화 비트를 판정할 수 있다.

도 6a 및 6b에서 상술한 방식은 일반적인 복호화 방법이라는 점에서 더 이상 구체적인 설명은 생략하도록 한다. 다만, 도 6a, b에서 설명한 방법 외에도 변수 노드와 검사 노드에서의 패싱되는 메시지 값을 결정하는 데 있어 다른 방법이 적용될 수도 있고, 이와 관련된 상세한 설명은 『Frank R. Kschischang, Brendan J. Frey, and Hans-Andrea Loeliger, "Factor Graphs and the Sum-Product Algorithm," IEEE TRANSACTIONS ON INFORMATION THEORY, VOL. 47, NO. 2, FEBRUARY 2001, pp498-519)』를 참고하기로 한다.

도 7은 본 발명의 일 실시 예에 따른 LDPC 부호화부의 세부 구성을 설명하기 위한 블록도이다.

Kldpc 개의 비트들은 LDPC 부호화부(700)를 위한 Kldpc 개의 LDPC 정보어 비트들 I=(i0,i1,..., )을 구성할 수 있다. LDPC 부호화부(700)는 Kldpc 개의 LDPC 정보어 비트들을 시스테매틱하게 LDPC 부호화하여, Nldpc 개의 비트들로 구성된 LDPC 코드워드 =(c0,c1,..., cNldpc-1)=(i0,i1,..., iKldpc-1,p0,p1,...,pNldpc-Kldpc-1)를 생성할 수 있다.

상기 수학식 1에서 서술한 바와 같이 상기 LDPC 코드워드와 패리티 검사 행렬의 곱이 제로 벡터가 되도록 부호어를 결정하는 과정을 포함한다.

도 7에 따르면, 부호화 장치(700)는 LDPC 부호화부(710)를 포함한다. LDPC 부호화부(710)는 패리티 검사 행렬 또는 그에 대응되는 지수행렬 또는 수열에 기초하여 입력 비트들에 대해 LDPC 부호화를 수행하여 LDPC 부호어를 생성할 수 있다. 이 경우, LDPC 부호화부(710)는 부호율(즉, LDPC 부호의 부호율)에 따라 서로 다르게 정의된 패리티 검사 행렬을 이용하여 LDPC 부호화를 수행할 수 있다.

한편, 부호화 장치(700)는 LDPC 부호의 부호율, 부호어 길이, 패리티 검사 행렬에 대한 정보를 기저장하기 위한 메모리(미도시)를 더 포함할 수 있으며, LDPC 부호화부(710)는 이러한 정보를 이용하여 LDPC 부호화를 수행할 수 있다. 상기 패리티 검사 행렬에 대한 정보는 본 발명에서 제시하는 패리티 행렬을 사용할 경우 순환 행렬의 지수 값에 대한 정보를 저장 할 수 있다.

도 8은 본 발명의 일 실시 예에 따른 복호화 장치의 구성을 나타내는 블록도이다.

도 8에 따르면, 복호화 장치(800)는 LDPC 복호화부(810)를 포함할 수 있다.

LDPC 복호화부(810)는 패리티 검사 행렬 또는 그에 대응되는 지수 행렬 또는 수열 에 기초하여 LDPC 부호어에 대해LDPC 복호화를 수행한다.

예를 들어, LDPC 복호화부(810)는 반복 복호 알고리즘을 통해 LDPC 부호어 비트들에 대응되는 LLR(Log Likelihood Ratio) 값을 패싱하여 LDPC 복호화를 수행하여 정보어 비트들을 생성할 수 있다.

여기에서, LLR 값은 LDPC 부호어 비트들에 대응되는 채널 값으로, 다양한 방법으로 표현될 수 있다.

예를 들어, LLR 값은 송신 측에서 채널을 통해 전송한 비트가 0일 확률과 1일 확률의 비율에 Log를 취한 값으로 나타낼 수 있다. 또한, LLR 값은 경판정에 따라 결정된 비트 값 자체가 될 수 있으며, 송신 측에서 에서 전송한 비트가 0 또는 1일 확률이 속하는 구간에 따라 결정된 대표 값이 될 수도 있다.

이 경우, 송신 측은 도 7과 같은 LDPC 부호화부(710)를 이용하여 LDPC 부호어를 생성할 수 있다.

이 경우, LDPC 복호화부(810)는 부호율(즉, LDPC 부호의 부호율)에 따라 서로 다르게 정의된 패리티 검사 행렬을 이용하여 LDPC 복호화를 수행할 수 있다.

도 9은 본 발명의 다른 실시 예에 따른 LDPC 복호화부 구조도를 나타낸다.

한편, 상술한 바와 같이 LDPC 복호화부(810)는 반복 복호 알고리즘을 사용하여 LDPC 복호화를 수행할 수 있으며, 이 경우, LDPC 복호화부(810)는 도 9와 같은 구조로 구성될 수 있다. 다만, 반복 복호 알고리즘의 경우 이미 공지된 사항이라는 점에서, 도 9에 도시된 세부 구성 역시 일 예일 뿐이다.

도 9에 따르면, 복호화 장치(900)는 입력 처리기(901), 메모리(902), 변수노드 연산기(904), 제어기(906), 검사노드 연산기(908) 및 출력 처리기(910) 등을 포함한다.

입력 처리기(901)는 입력되는 값을 저장한다. 구체적으로, 입력 처리기(901)는 무선 채널을 통해 수신되는 수신 신호의 LLR 값을 저장할 수 있다.

제어기(904)는 무선 채널을 통해 수신되는 수신 신호의 블록의 크기(즉, 부호어의 길이), 부호율에 대응되는 패리티 검사 행렬을 기반으로 하여 변수 노드 연산기(904)에 입력되는 값의 개수 및 메모리(902)에서의 주소 값, 검사 노드 연산기(908)에 입력되는 값의 개수 및 메모리(902)에서의 주소 값 등을 결정한다.

메모리(902)는 변수 노드 연산기(904)와 검사 노드 연산기(908)의 입력 데이터 및 출력 데이터를 저장한다.

변수 노드 연산기(904)는 제어기(906)에서 입력받은 입력 데이터의 주소 정보 및 입력 데이터의 개수 정보에 따라 메모리(902)에서 데이터들을 입력 받아 변수 노드 연산을 한다. 이후, 변수 노드 연산기(904)는 제어기(906)에서 입력 받은 출력 데이터의 주소 정보 및 출력 데이터의 개수 정보에 기초하여 변수 노드 연산 결과들을 메모리(902)에 저장한다. 또한, 변수 노드 연산기(904)에서는 입력 처리기(901)와 메모리(902)에서 입력 받은 데이터를 기반으로 하여 변수 노드 연산 결과를 출력 처리기(910)에 입력한다. 여기에서, 변수 노드 연산은 도 6를 기반으로 상술한 바 있다.

검사 노드 연산기(908)는 제어기(906)에서 입력받은 입력 데이터의 주소 정보 및 입력 데이터의 개수 정보에 기초하여 메모리(902)에서 데이터들을 입력받아 검사 노드 연산을 한다. 이후, 검사 노드 연산기(908)는 제어기(906)에서 입력받은 출력 데이터의 주소 정보 및 출력 데이터의 개수 정보에 기초하여 변수 노드 연산 결과들을 메모리(902)에 저장한다. 여기에서, 검사 노드 연산은 도 6을 기반으로 상술한 바 있다.

출력 처리기(910)는 변수 노드 연산기(904)로부터 입력받은 데이터를 기반으로 하여 송신 측의 부호어의 정보어 비트들이 0이었는지 1이었는지 경판정한 후, 그 경판정 결과를 출력하게 되고, 출력 처리기(910)의 출력 값이 최종적으로 복호화된 값이 되는 것이다. 이 경우, 도 6에서 하나의 변수 노드로 입력되는 모든 메시지 값(초기 메시지 값과 검사 노드로부터 입력되는 모든 메시지 값들)을 더한 값을 기반으로 경판정 할 수 있다.

한편, 복호화 장치(900)는 LDPC 부호의 부호율, 부호어 길이, 패리티 검사 행렬에 대한 정보를 기저장하기 위한 메모리(미도시)를 더 포함할 수 있으며, LDPC 복호화부(810)는 이러한 정보를 이용하여 LDPC 부호화를 수행할 수 있다. 하지만, 이는 일 예일 뿐, 해당 정보들은 송신 측으로부터 제공될 수도 있다.

도 10는 본 발명의 다른 실시 예에 따른 전송 블록 구조도이다.

도 10를 참조하면, <Null> bit들을 세그먼트된 길이가 동일하도록 하기 위해 추가할 수 도 있다.

또한 <Null> bit들을 LDPC 부호의 정보 길이를 맞추기 위해 추가할 수도 있다.

이상에서는 다양한 길이의 LDPC 부호를 지원하는 통신 및 방송 시스템에 있어서, QC-LDPC 부호에 기반하여 다양한 블록 크기를 적용하는 방법에 대해서 살펴보았다. 다음으로는 상기 제안된 방법에서 부호화 성능을 더 개선하는 방법에 대해서 제안한다.

일반적으로 만일 수학식 9 및 수학식 10에서 설명한 리프팅 방법처럼 하나의 LDPC 지수 행렬 또는 수열 등으로부터 매우 다양한 블록 크기 L에 대해 적절히 수열을 변환하여 사용할 경우에는 시스템 구현 시에 1개 또는 적은 개수의 수열에 대해서만 구현하면 되기 때문에 많은 이점이 있다. 하지만, 지원하고자 하는 블록 크기의 종류가 많아질수록 모든 블록 크기에 대해 성능이 좋은 LDPC 부호를 설계하는 것은 매우 어려운 문제이다.

이와 같은 문제를 해결하기 위하여 다음과 같은 QC LDPC 부호의 효율적인 설계 방법에 대해서 설명한다. 본 발명에서는 수학식 9 및 수학식 10의 리프팅 방법과 LDPC 부호의 패리티 검사행렬 또는 Tanner 그래프 상의 트래핑 집합 특성을 고려하며 우수한 성능을 가지는 패리티 검사 행렬의 설계 방법에 대해서 제안한다. 본 발명에서는 편의상 수학식 10의 에 기반한 리프팅을 가정하여 설명을 진행하지만 반드시 이에 국한할 필요는 없다.

*

가변 길이 LDPC 부호의 설계 방법 1

Step 1) 채널 부호의 복호 성공에 대한 잡음 임계치(noise threshold)를 결정함에 있어 반복 복호 횟수 (iteration number) 및 밀도 진화 (density evolution)의 수렴(convergence) 기준을 변경하며 밀도 진화 분석을 수행하여 기본 행렬의 무게 분포(weight distribution)을 구한다.

Step 2) 힐 크라이밍(Hill Climbing) 방식을 통해 Step 1)에서 얻어진 무게 분포를 개선할 수 있을 경우 그 개선된 무게 분포를 최종 기본 행렬의 무게 분포로 설정한다.

Step 3) Step 2)에서 구해진 무게 분포를 토대로 기본 행렬 1개를 구한다. 이때 기본 행렬을 구하는 방법은 기존에 알려진 다양한 방법을 통해 설계해도 무관하다.

Step 5) 의 범위를 만족하는 L 값에 따라 지수 행렬을 결정함에 있어 먼저 거스(girth, Tanner 그래프 상의 사이클 길이 중 가장 작은 값)를 최대화한 다음, 사전에 결정된 트랩핑 집합 제거 순서에 따라 트랩핑 집합이 순서대로 최대한 제거되는 지수 행렬을 결정한다. 여기서 상기 결정된 트랩핑 집합 제거 순서는 다음과 같다.

1순위: (4,0) 트랩핑 집합

2순위: (3,1) 트랩핑 집합

3순위: (2,2) 트랩핑 집합

4순위: (3,2) 트랩핑 집합

5순위: (4,1) 트랩핑 집합

6순위: (4,2) 트랩핑 집합

Step 6) 상기 Step 1)부터 Step 5) 과정을 사전에 정해진 수만큼 반복한 다음, 각각 얻어진 부호에 대한 전산 실험을 통해 L 값에 따라 평균적인 성능이 가장 좋은 부호를 최종 선택한다. 여기서 평균적인 성능은 다양한 방법으로 정의 가능한데, 예를 들어서 L 값의 변화에 따라 시스템에서 요구되는 BLER (block error rate)을 달성하기 위해 필요한 최소 SNR (signal to noise ratio)을 찾고, L의 변화에 따른 평균 SNR이 가장 작은 부호를 최종 선택할 수 있다.

상기 가변 길이 QC LDPC 부호의 설계 방법은 일 실시 예일 뿐이며 채널 부호에 대한 요구 조건에 따라 변경 가능함은 자명하다. 예를 들어 Step 3)는 시스템에서 적용하고자 하는 리프팅 방법이 다를 경우에 해당 리프팅 방법을 고려하여 변경 가능하다. 또한 Step 4)에서는 시스템에서 요구되는 채널 부호의 특성에 따라 트랩핑 집합의 제거 순서를 변경할 수도 있다. 또한 상기 가변 길이 QC LDPC 부호의 설계 방법은 길이가 가변인 경우에 대해서 설명하고 있지만, 길이가 1개로 고정되어 있는 경우에도 Step 3) 및 Step 4)에서 리프팅 과정만 제거하고 적용 가능하다.

예를 들어 정보 비트 수가 작은 수로 정해져 있고, 부호율이 낮은 경우에 복잡도와 성능을 모두 고려하여 채널 부호화 이후 얻어진 부호어 비트 일부를 반복(repetition)하여 전송함을 가정하여 부호를 설계할 수 있다. 이 경우 상기 가변 길이 QC LDPC 부호의 설계 방법의 Step 1)에서 밀도 진화 분석을 위한 초기값 일부를 반복 전송 횟수만큼 증가시켜 잡음 임계치를 결정한다. 또한 부호율이 또는 길이도 고정되어 있다면 Step 3) 및 Step 4)에서 리프팅 과정을 제외할 수 있다.

참고로 기존에 잘 알려져 있는 밀도 진화 분석 방법 및 트랩핑 집합의 특징에 대한 자세한 내용은 본 발명의 요지에 벗어나므로 생략하고 각각 다음 참조문헌 Reference [RSU2001] 및 Reference [KaBa2012]으로 대신한다:

Reference [RSU2001]:

T. J. Richardson, M. A. Shokrollahi, , and R. L. Urbanke, “Design of capacity-approaching irregular low-density parity-check codes,” IEEE Trans. Inf. Theory, vol. 47, no. 2, pp. 619-637, Feb. 2001.

Reference [KaBa2012]:

M. Karimi and A. H. Banihashemi, “Efficient algorithm for finding dominant trapping sets of LDPC codes,” IEEE Trans. Inf. Theory, vol. 58, no. 11, pp. 6942-6958, Nov. 2012.

본 발명의 다른 실시 예로서 정해진 하나의 기본 행렬 상에서 복수 개의 지수 행렬 또는 LDPC 수열을 적용하는 경우에 대해 LDPC 부호의 지수 행렬 또는 수열을 설계하는 방법을 제안한다. 즉, 기본 행렬은 하나로 고정되어 있으며, 상기 기본 행렬 상에서 정의된 LDPC 부호의 지수 행렬 또는 수열 등을 결정하고, 상기 지수 행렬 또는 수열로부터 각 블록 크기 그룹에 포함된 블록 크기에 맞게 리프팅을 적용함으로써 가변 길이의 LDPC 부호화 및 복호화를 수행한다. 이러한 방식은 LDPC 부호의 지수 행렬 또는 LDPC 수열을 구성하는 원소 또는 숫자들은 서로 다른 값을 가질 수 있지만, 해당 원소 또는 숫자들의 위치는 정확히 일치하는 특징을 가진다. 이와 같이 지수 행렬 또는 LDPC 수열들은 각각 순환 순열 행렬의 지수, 즉, 비트들에 대한 일종의 순환 시프트(circular shift) 값을 의미하는데, 원소 또는 숫자들의 위치를 모두 동일하게 설정함으로써 해당 순환 순열 행렬에 대응되는 비트들의 위치를 파악하기가 용이하다. 참고로 본 발명에서 제안하는 지수 행렬 또는 LDPC 수열은 블록 크기(Z)에 대응되는 비트들의 순환 시프트 값에 대응되기 때문에 시프트 행렬 (shift matrix) 또는 시프트 값 행렬(shift value matrix) 또는 시프트 수열 (shift sequence) 또는 시프트 값 수열 (shift value sequence) 등과 같이 다양하게 명명할 수 있다.

지원하고자 하는 블록 크기(Z)를 다음 수학식 15와 같이 복수 개의 블록 크기 그룹 (또는 집합)으로 구분하자. 상기 블록 크기(Z)는 LDPC 부호의 패리티 검사 행렬에서 순환 순열 행렬 또는 순환 행렬의 크기 ZxZ에 대응되는 값임에 유의한다.

[수학식 15]

Z1 = {2, 4, 8, 16, 32, 64, 128, 256}

Z2 = {3, 6, 12, 24, 48, 96, 192, 384}

Z3 = {5, 10, 20, 40, 80, 160, 320}

Z4 = {7, 14, 28, 56, 112, 224}

Z5 = {9, 18, 36, 72, 144, 288}

Z6 = {11, 22, 44, 88, 176, 352}

Z7 = {13, 26, 52, 104, 208}

Z8 = {15, 30, 60, 120, 240}

상기 수학식 15는 일례일 뿐이며, 상기 수학식 15의 블록 크기 그룹에 포함된 모든 블록 크기(Z) 값을 사용할 수도 있으며, 다음 수학식 16과 같이 적절한 부분 집합에 포함되는 블록 크기 값을 사용할 수도 있으며, 상기 수학식 15 또는 수학식 16의 블록 크기 그룹(또는 집합)에 적절한 값들을 추가 또는 제외하여 사용할 수도 있다.

[수학식 16]

Z1'= {8, 16, 32, 64, 128, 256}

Z2'= {12, 24, 48, 96, 192, 384}

Z3'= {10, 20, 40, 80, 160, 320}

Z4'= {14, 28, 56, 112, 224}

Z5'= {9, 18, 36, 72, 144, 288}

Z6'= {11, 22, 44, 88, 176, 352}

Z7'= {13, 26, 52, 104, 208}

Z8'= {15, 30, 60, 120, 240}

상기 수학식 15 및 수학식 16의 블록 크기 그룹들의 특징은 서로 다른 입도를 가질 뿐만 아니라 이웃한 블록 크기의 비율이 모두 동일한 정수인 특징을 가지고 있다. 즉 다시 말해 하나의 그룹에 포함되어 있는 블록 크기들은 서로 약수 또는 배수 관계에 있다. p (p = 1, 2, …, 8)번째 그룹에 대응되는 지수 행렬을 각각 라 하고, 상기 p번째 그룹에 포함된 Z 값에 대응되는 지수 행렬을 라 할 때, 를 이용하여 수학식 9와 같은 수열의 변환 방법을 적용한다고 하자. 즉, 예를 들어 블록 크기 Z가 Z = 28와 같이 결정된 경우에는 Z = 28이 포함되어 있는 4번째 블록 크기 그룹에 대응되는 지수 행렬(또는 LDPC 수열) 에 대해서 Z = 28에 대한 지수 행렬(또는 LDPC 수열) 각 원소 를 다음 수학식 17과 같이 얻을 수 있다.

[수학식 17]

상기 수학식 17과 같은 변환은 간단히 다음 수학식 18과 같이 나타내기도 한다.

[수학식 18]

참고로, 이상에서는 수학식 9 또는 수학식 15 내지 수학식 18에서의 리프팅 또는 지수 행렬의 변환 방식에 대해 패리티 검사 행렬에 대응되는 지수 행렬 전체에 적용하는 것을 가정하여 설명하였지만, 상기 지수 행렬의 부분적으로도 적용 가능하다. 예를 들어 통상적으로 패리티 검사 행렬의 패리티 비트에 대응되는 부분 행렬은 효율적인 부호화를 위해서 특수한 구조를 가지는 경우가 많다. 이 경우에 리프팅에 의해 부호화 방법 또는 복잡도에 변화가 생길 수도 있다. 따라서 동일한 부호화 방법 또는 복잡도 유지를 위해서 패리티 검사 행렬에서 패리티에 대응되는 부분 행렬에 대한 지수 행렬의 일부에는 리프팅을 적용하지 않거나 정보어 비트에 대응되는 부분 행렬에 대한 지수 행렬에 적용하는 리프팅 방식과 서로 다른 리프팅을 적용할 수 있다. 다시 말하면, 지수 행렬 내에서 정보어 비트에 대응되는 수열에 적용하는 리프팅 방식과 패리티 비트에 대응되는 수열에 적용하는 리프팅 방식을 서로 다르게 설정할 수 있으며, 경우에 따라 패리티 비트에 대응되는 수열의 일부 또는 전체에는 리프팅을 적용하지 않아 수열 변환 없이 고정된 값을 사용할 수도 있다.

본 발명의 다른 실시 예로서 상기 수학식 15 내지 18에 나타낸 방법을 고려하여 기본 행렬이 주어져 있을 경우에 LDPC 지수 행렬 또는 수열을 설계하는 방법을 다음과 같이 제안한다. 다음 실시 예는 편의상 하나의 블록 크기 그룹에 대응되는 지수 행렬 또는 수열을 설계하는 방법에 대해서 설명하지만, 이는 다양한 블록 크기 그룹에 동일한 방식으로 적용하여 또 다른 지수 행렬 또는 수열을 설계할 수 있다.

*

가변 길이 LDPC 부호의 설계 방법 2

Step 1) 기본 행렬이 주어져 있다.

Step 3) 인 를 리프팅의 시작점으로 설정하여 설계를 시작한다. 값에 따라 지수 행렬 또는 수열을 결정함에 있어 먼저 거스(girth, Tanner 그래프 상의 사이클 길이 중 가장 작은 값)를 최대화한 다음, 사전에 결정된 트랩핑 집합 제거 순서에 따라 트랩핑 집합이 순서대로 최대한 제거되는 지수 행렬 또는 수열을 결정한다. 여기서 상기 결정된 트랩핑 집합 제거 순서는 다음과 같다.

1순위: (4,0) 트랩핑 집합

2순위: (3,1) 트랩핑 집합

3순위: (2,2) 트랩핑 집합

4순위: (3,2) 트랩핑 집합

5순위: (4,1) 트랩핑 집합

6순위: (4,2) 트랩핑 집합

이때, 상기 트랩핑 집합 제거 순서에 따라 지수 행렬의 지수 값을 결정할 때 가능하다면 후보 지수 값들 중에서 작은 값을 선택한다. 또한 복수 개의 지수 행렬 또는 수열 등을 얻을 수도 있다.

Step 5) 상기 Step 1)부터 Step 4) 과정을 사전에 정해진 수만큼 반복한 다음, , , …, 에 대한 LDPC 지수 행렬 또는 수열을 결정한다. 이때, Step 3)의 트랩핑 집합 제거 순서와 (조건) 등을 통과하는 많은 수의 LDPC 지수 행렬 또는 수열이 있을 수 있는데, 이 경우에는 전산 실험을 통해 평균적인 성능이 좋은 복수 개의 LDPC 지수 행렬 또는 수열을 결정한다. 여기서 평균적인 성능은 다양한 방법으로 정의 가능한데, 예를 들어서 Z 값의 변화에 따라 시스템에서 요구되는 BLER (block error rate)을 달성하기 위해 필요한 최소 SNR (signal to noise ratio)을 찾고, Z의 변화에 따른 평균 SNR이 가장 작은 부호를 최종 선택할 수 있다.

Step 6) 상기 결정된 복수 개의 LDPC 지수 행렬 또는 수열 에 대해 수학식 18과 같이 , , … , 를 적용하여 복수 개의 , , …, 들을 생성한다. 상기 생성된 복수 개의 지수 행렬 집합 , , …, 에 대해서 Step 3)의 트랩핑 집합 제거 순서를 고려하여 나쁜 트랩핑 집합이 적게 생성되는 복수 개의 지수 행렬 또는 수열의 집합을 결정한다.

Step 7) Step 6)에서 결정된 지수 행렬 또는 수열의 집합 중에서 안정적인 성능을 제공하는 지수 행렬 또는 수열을 집합을 결정하고, 해당 집합을 생성할 수 있는 를 최종 LDPC 지수 행렬 또는 수열로 결정한다.

여기서 안정적인 성능의 의미는 특정 목표 BLER를 달성하기 위한 SNR 값이 사전에 정의된 어떤 값 보다 크게 벗어나지 않음을 의미한다.

기존의 설계 방식들과 가변 길이 QC LDPC 부호의 설계 방법 2 와 같은 설계 방식의 차이점은 LDPC 부호의 패리티 검사 행렬 또는 지수 행렬 등을 설계할 때 지원하고자 하는 블록 크기들 중에서 중요한 정도의 우선 순위를 차별화 하여 설계한 예이다. 예를 들어서 에 대해서는 시스템에서의 중요성이 높아 지수 행렬의 대수적 특성이 어느 수준 이상 정도 보장되어야 하고, 에 대해서는 시스템에서의 중요성이 다소 낮은 경우에 위와 같은 방법으로 설계함으로써 시스템에 보다 적합한 LDPC 부호를 설계하기 용이하다.

상기 수학식 15 내지 수학식 18을 고려하여 상기 설계 방법을 통해 설계된 LDPC 부호의 기본 행렬 및 지수 행렬 (또는 LDPC 수열)에 기반한 LDPC 부호화 및 복호화 과정의 실시 예에 대한 흐름도를 도 11 내지 도 18에 나타내었다. 먼저 도 11의 (1110) 단계와 같이 정보어의 길이를 먼저 결정한다. 본 발명에서 정보어의 길이는 경우에 따라 CBS(code block size)라 표현하기도 한다. 그 다음으로는 (1120) 단계와 같이 상기 결정된 CBS에 맞는 LDPC 지수 행렬 또는 수열을 결정한 다음, 상기 지수 행렬 또는 수열을 기반으로 (1130)단계에서 LDPC 부호화를 수행한다.

LDPC 복호화 과정도 이와 유사하게 도 12와 같이 나타낼 수 있다. 만일 (1210) 단계에서 CBS가 결정되면, (1220) 단계에서 적합한 지수 행렬 또는 수열을 결정하여 (1230) 단계에서 상기 지수 행렬 또는 수열을 이용하여 LDPC 복호화를 수행할 수 있다.

설계된 기본 행렬 또는 지수 행렬에 기반한 LDPC 부호화 및 복호화 과정의 또 다른 실시 예에 대한 흐름도를 도 13 및 도 14에 나타내었다.

먼저 도 13의 (1310) 단계와 같이 전송하고자 하는 트랜스포트 블록 크기 TBS (Transport Block Size)의 크기를 결정한다. 만일, 시스템에서 주어진 채널 부호에서 한 번에 부호화를 적용할 수 있는 최대 정보어의 길이를 max CBS라 할 때, 상기 TBS의 크기가 max CBS 보다 클 경우에는 상기 트랜스포트 블록을 복수 개의 정보어 블록 (또는 코드 블록)으로 세그멘테이션(segmentation)하여 부호화를 수행하여야 한다. 상기 도 13에서는 (1320) 단계에서 상기 TBS가 max CBS 보다 큰지 작거나 같은지 판단한 다음에, 만일 더 큰 경우에는 (1330) 단계에서 상기 트랜스포트 블록을 세그멘테이션 하여 새롭게 CBS를 결정하고, 작거나 같은 경우에는 세그멘테이션 동작을 생략하고 상기 TBS를 CBS로 결정한 다음, (1340) 단계에서 상기 TBS 또는 CBS 값에 따라 적절히 LDPC 지수 행렬 또는 수열을 결정한다. 그 다음 (1350) 단계에서 상기 결정된 지수 행렬 또는 수열에 기반하여 LDPC 부호화를 수행한다.

구체적인 예로서 만일 (1310) 단계에서 TBS가 9216으로 결정되었다고 하고 시스템에서 주어진 max CBS = 8448라고 하자. 자명하게, (1320) 단계에서 TBS가 max CBS 보다 크다고 판단하기 때문에 (1330) 단계에서 적절히 세그멘테이션을 적용하여 CBS = 4608인 두 개의 정보어 블록 (또는 코드 블록)이 얻어진다. 따라서 (1340) 단계에서 CBS = 4608에 적합한 지수 행렬 또는 수열을 결정하여 (1350) 단계에서 상기 결정된 지수 행렬 또는 수열을 이용하여 LDPC 부호화를 수행할 수 있다.

LDPC 복호화 과정도 이와 유사하게 도 14와 같이 나타낼 수 있다. 만일 (1410) 단계에서 TBS가 9216으로 결정되었다면, (1420) 단계에서 TBS가 max CBS 보다 크다고 판단하여 (1430) 단계에서 세그멘테이션이 적용된 CBS의 크기 4608을 결정한다. 만일 (1420) 단계에서 TBS가 max CBS 보다 작거나 같다고 판단될 경우에는 TBS가 곧 CBS와 동일하게 결정된다. 이로부터 (1440) 단계에서 LDPC 부호의 지수 행렬 또는 수열을 결정한 다음, (1450) 단계에서 상기 결정된 지수 행렬 또는 수열을 이용하여 LDPC 부호화를 수행할 수 있다.

설계된 기본 행렬 또는 지수 행렬에 기반한 LDPC 부호화 및 복호화 과정의 또 다른 실시 예에 대한 흐름도를 도 15 및 도 16에 나타내었다.

먼저 도 15의 (1510) 단계와 같이 전송하고자 하는 트랜스포트 블록 크기 TBS를 결정한다. (1520) 단계에서 상기 TBS가 max CBS 보다 큰지 작거나 같은지 판단한 다음에, 만일 더 큰 경우에는 (1530) 단계에서 상기 트랜스포트 블록을 세그멘테이션 하여 새롭게 CBS를 결정하고, 작거나 같은 경우에는 세그멘테이션 동작을 생략하고 상기 TBS를 CBS로 결정한 다음, (1540) 단계에서는 상기 CBS를 기반으로 LDPC 부호화에 적용할 블록 크기 (Z) 값을 결정한다. 다음 (1550) 단계에서 상기 TBS 또는 CBS 또는 블록 크기 (Z) 값에 따라 적절히 LDPC 지수 행렬 또는 수열을 결정한다. 그 다음 (1560) 단계에서는 상기 결정된 블록 크기와 지수 행렬 또는 수열에 기반하여 LDPC 부호화를 수행한다. 참고로 상기 (1550) 단계에서는 경우에 따라서 상기 결정된 블록 크기에 기반하여 상기 결정된 LDPC 지수 행렬 또는 수열을 변환 하는 과정이 포함될 수도 있다.

LDPC 복호화 과정도 이와 유사하게 도 16과 같이 나타낼 수 있다. 만일 (1610) 단계에서 TBS가 결정되었다면 (1620) 단계에서 TBS가 max CBS 보다 큰지 작거나 같은지 판단한 다음, TBS가 max CBS 보다 크다면 (1630) 단계에서 세그멘테이션이 적용된 CBS의 크기를 결정한다. 만일 (1620) 단계에서 TBS가 max CBS 보다 작거나 같다고 판단될 경우에는 TBS가 곧 CBS와 동일하게 결정된다. 이로부터 (1640) 단계에서 LDPC 복호화에 적용할 블록 크기(Z) 값을 결정한 다음, (1650) 단계에서 상기 TBS 또는 CBS 또는 블록 크기(Z) 값에 적절히 LDPC 지수 행렬 또는 수열을 결정한다. 그 다음에는 (1660) 단계에서 상기 결정된 블록 크기와 지수 행렬 또는 수열을 이용하여 LDPC 복호화를 수행할 수 있다. 참고로 상기 (1650) 단계에서는 경우에 따라서 상기 결정된 블록 크기에 기반하여 상기 결정된 LDPC 지수 행렬 또는 수열을 변환 하는 과정이 포함될 수도 있다.

상기 실시 예에 따르면 도 11내지 도 16의 (1120), (1220), (1340), (1440), (1550), (1650) 단계에서 LDPC 부호의 지수 행렬 또는 수열을 결정하는 과정은 TBS 또는 CBS 또는 블록 크기(Z) 중에 하나에 의해 결정되는 경우에 대해서 기술하였으나, 다양한 다른 방법이 존재할 수도 있다.

설계된 기본 행렬 또는 지수 행렬에 기반한 LDPC 부호화 및 복호화 과정의 또 다른 실시 예에 대한 흐름도를 도 17 및 도 18에 나타내었다.

먼저 도 17의 (1710) 단계와 같이 전송하고자 하는 CBS 크기를 결정한다. (1720) 단계에서 상기 CBS 크기에 따라 LDPC 지수 행렬에서 상기 CBS에 대응되는 열의 개수 Kb 값과 블록 크기(Z)를 결정한다. 통상적으로 LDPC 부호의 지수 행렬에서는 정보어 비트에 대응되는 열의 개수가 고정되어 있다. 하지만, 다양한 CBS나 최적화된 성능을 제공하기 위하여 상기 정보어 비트에 대응되는 모든 열을 사용하지 않고 CBS에 따라 적절히 단축(제로 패딩)하여 사용할 수도 있다. 상기 Kb 값은 이러한 단축을 고려하여 정해지는 값이다. (1730) 단계에서 상기 CBS 또는 CBS 대응 열블록 개수(Kb) 또는 블록 크기(Z) 값에 따라 적절히 LDPC 지수 행렬 또는 수열을 결정한다. (1740) 단계에서는 상기 결정된 블록 크기와 지수 행렬 또는 수열에 기반하여 상기 결정된 LDPC 지수 행렬 또는 수열을 변환 하는 과정을 수행할 수도 있다. (1750) 단계에서는 상기 결정된 블록 크기와 지수 행렬 또는 수열에 기반하여 LDPC 부호화를 수행한다.

LDPC 복호화 과정도 이와 유사하게 도 18과 같이 나타낼 수 있다. 먼저 도 18의 (1810) 단계와 같이 수신된 데이터의 CBS 크기를 결정한다. (1820) 단계에서 상기 CBS 크기에 따라 LDPC 지수 행렬에서 상기 CBS에 대응되는 열의 개수 Kb 값과 블록 크기(Z)를 결정한다. (1830) 단계에서 상기 CBS 또는 CBS 대응 열블록 개수(Kb) 또는 블록 크기(Z) 값에 따라 적절히 LDPC 지수 행렬 또는 수열을 결정한다. (1840) 단계에서는 상기 결정된 블록 크기와 지수 행렬 또는 수열에 기반하여 상기 결정된 LDPC 지수 행렬 또는 수열을 변환 하는 과정을 수행할 수도 있다. (1850) 단계에서는 상기 결정된 블록 크기와 지수 행렬 또는 수열에 기반하여 LDPC 부호화를 수행한다.

상기 도 11 내지 도 18의 LDPC 부호의 기본 행렬 및 지수 행렬(또는 LDPC 수열)에 기반한 LDPC 부호화 및 복호화 과정의 실시 예에 있어서, 상기 LDPC 부호에 대해서 적절히 정보어 비트의 일부를 단축 (shortening) 하고 부호어 비트의 일부를 천공하여 다양한 부호율과 다양한 길이의 LDPC 부호화 및 복호화를 지원 가능하다. 예를 들어, 상기 도 11 내지 도 18에서 LDPC 부호화 및 복호화를 위해 결정된 기본 행렬 또는 지수 행렬에서 정보어 비트 일부에 단축을 적용한 다음, 처음 2 개의 열에 대응되는 정보어 비트를 항상 천공하고, 패리티 일부를 천공하면 다양한 정보어 길이(또는 코드 블록 길이)와 다양한 부호율을 지원할 수 있다.

뿐만 아니라 LDPC 부호의 단축 또는 제로 패딩 등을 이용하여 가변 정보어 길이나 가변 부호율을 지원할 때 단축 순서나 단축 방법에 따라 부호의 성능을 개선할 수 있다. 만일 단축 순서가 기 설정되어 있을 때, 이와 같이 주어진 기본 행렬의 일부 또는 전체를 적절히 순서를 재정렬함으로써 부호화 성능을 개선할 수 있다. 또한 특정 정보어 길이 (또는 코드 블록 길이 CBS)에 대해 블록 크기 또는 단축을 적용할 열 블록의 개수를 적절히 결정하여 성능을 개선할 수도 있다.

예를 들어, 주어진 LDPC 기본 행렬 또는 지수 행렬에서 LDPC 부호화 및 복호화를 위해 필요한 열의 개수를 Kb라 할 때 단축을 위해서 다음과 같이 CBS 값에 따라 적절한 규칙을 적용하여 Kb와 그에 대응되는 블록 크기 (Z)값을 결정하면 보다 우수한 성능을 얻을 수 있다. (예: A = 640, B = 560, C = 192)

if(CBS > A)

Kb=10;

elseif(CBS > B)

Kb=9;

elseif(CBS > C)

Kb=8;

else

Kb=6;

end

상기 예의 경우에는 블록 크기(Z) 값을 위에서 Kb 값이 결정되면, Z×Kb >= CBS를 만족하는 최소 값으로 결정할 수 있다. Kb 값을 결정하는 자유도가 높을수록 성능 개선에는 유리하지만, 시스템 구현 복잡도 면에서는 나빠지기 때문에 적절한 수준의 규칙을 적용해야 성능과 시스템 구현 효율성을 동시에 좋게 할 수 있다. 예를 들어 다음과 같이 규칙을 보다 자세하게 생성하면 성능은 더 좋아지나, 구현 복잡도가 증가하기 때문에 시스템의 요구 조건에 따라 적절한 규칙을 적용한다.

if(CBS > A)

Kb=10;

elseif(CBS > B)

Kb=9;

elseif(CBS > C)

Kb=8;

else

if(CBS is member of [48,96,176,184,192])

Kb=7;

else

Kb=6;

end

end

참고로 블록 크기(Z) 값을 Kb 값이 결정되면, Z×Kb >= CBS를 만족하는 최소 값으로 결정한다고 했을 때, 다음 수학식 19와 같이 Kb와 블록 크기(Z)를 결정할 수 있다.

[수학식 19]

CBS=40 => Kb=6 => Z=7

CBS=48 => Kb=7 => Z=7

CBS=56 => Kb=6 => Z=10

CBS=64 => Kb=6 => Z=11

CBS=72 => Kb=6 => Z=12

CBS=80 => Kb=6 => Z=14

CBS=200 => Kb=8 => Z=26

CBS=640 => Kb=9 => Z=72

CBS=1024=> Kb=10 => Z=104

상기 Kb와 블록 크기 값을 결정하는 방법은 일례일 뿐이며, 다양한 방법을 적용할 수 있다.

상기 수학식 15 내지 수학식 18에 기반하여 본 발명에서 제안하는 LDPC 부호의 설계 방법을 이용하여 설계된 LDPC 부호의 패리티 검사 행렬에 대응되는 기본 행렬 또는 지수 행렬에 대한 실시 예를 도 19 내지 도 21에 나타내었다. (도 19의 기본 행렬에서 빈 블록들은 원소가 0임을 의미한다. 도 20 내지 도 21의 지수 행렬에서 빈 블록들은 ZxZ 크기의 영행렬에 대응되는 부분을 나타내며, -1 과 같은 특정된 값으로도 표현 가능하다.) 상기 도 20 내지 도 21에 나타낸 LDPC 부호의 지수 행렬들은 상기 도 19의 동일한 기본 행렬을 가진다는 특징이 있다.

도 19a 내지 도 19i는 도 19의 기본 행렬을 구분하여, 각 부분을 확대하여 도시한 것이다. 도 19의 각 부분은 각 부분에 기재된 도면 번호에 해당하는 행렬에 대응된다. 따라서, 도 19a 내지 도 19i가 결합하여 도 19와 같은 형태의 하나의 기본 행렬을 구성할 수 있다. 또한, 이는 도 20 내지 도 21의 지수 행렬에 대해서도 동일하게 적용될 수 있다. 도 20 내지 도 21의 지수 행렬에서 각각의 빈 블록은 ZxZ 크기의 0 행렬에 대응됨을 의미한다.

도 20a 내지 도 20i는 도 20의 지수 행렬을 구분하여, 각 부분을 확대하여 도시한 것이다. 도 20은 각 부분에 기재된 도면 번호에 해당하는 도면의 행렬에 대응된다. 따라서, 도 20a 내지 도 20i가 결합하여 하나의 지수 행렬을 구성할 수 있다. 도 21은 도 20의 a, d 및 g에 대응되는 부분만을 도시한 것이다. 도 21의 B, C, E, F, H 및 I 부분은 도 20의 B, C, E, F, H 및 I 부분과 동일하다. 즉 도 20b, 20c, 20e, 20f, 20h 및 20i 부분에 도시된 바와 동일하다. 도 21을 도 20의 a, d 및 g 부분으로 하여 도 20b, 20c, 20e, 20f, 20h 및 20i를 결합하여 새로운 지수 행렬을 구성할 수 있다.

도 19 내지 도 21의 행렬은 42x52 크기의 기본 행렬 또는 LDPC 지수 행렬을 도시한 도면으로서 각 기본 행렬 및 지수 행렬에서 위 4개의 행과 앞에서부터 14개의 열로 구성된 부분 행렬은 차수가 1인 열이 없다. 이는 다시 말해 상기 부분 행렬로부터 리프팅을 적용하여 생성 가능한 패리티 검사 행렬은 차수가 1인 열 또는 열 블록이 없음을 의미한다. 상기 도 19 내지 도 21에 나타낸 기본 행렬 또는 지수 행렬은 모두 15번째 열부터 52번째 열까지는 모두 차수가 1인 특징을 가지고 있다. 즉, 상기 지수 행렬들의 5번째 행부터 42번째 행으로 구성된 38x52 크기의 기본 행렬 또는 지수 행렬은 단일 패리티 검사 부호(single parity-check code)에 대응됨을 특징으로 한다.

상기 도 20 내지 도 21에 나타낸 지수 행렬들은 각각 수학식 15 및 수학식 16에서 정의된 블록 크기 그룹을 고려하여 설계된 LDPC 부호에 각각 대응된다. 하지만 시스템의 요구 사항에 따라서 상기 블록 크기 그룹에 포함된 모든 블록 크기를 반드시 지원할 필요는 없다. 참고로 상기 도 20의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z1 또는 Z1', 상기 도 21의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z7 또는 Z7'에 대응되도록 설계되었다.

또한 시스템에 따라 상기 도 19 내지 도 21에 나타낸 기본 행렬 및 지수 행렬을 그대로 사용할 수도 있고, 그 일부만 사용될 수도 있다. 예를 들면, 상기 도 19 내지 도 21의 각 기본 행렬 및 지수 행렬들의 위 22개의 행으로 구성된 부분 행렬과 20x52 크기의 또 다른 지수 행렬을 연접함으로써 새로운 지수 행렬을 생성하여 LDPC 부호화 및 복호화 방법 및 장치에 적용할 수 있다.

마찬가지로 상기 도 19 내지 도 21에 나타낸 기본 행렬 및 지수 행렬에서 아래 23번째 행부터 마지막 행으로 구성된 부분 행렬과 22x52 크기의 또 다른 부분 행렬을 연접함으로써 새로운 지수 행렬을 생성하여 LDPC 부호화 및 복호화를 수행할 수 있다.

일반적으로 상기 도 19의 기본 행렬에서 적절히 행과 열을 선택하여 이루어진 부분 행렬을 새로운 기본 행렬로 적용하여 LDPC 부호화 및 복호화를 수행할 수도 있다. 마찬가지로 도 20 내지 도 21의 지수 행렬에서 적절히 행과 열을 선택하여 이루어진 부분 행렬을 새로운 지수 행렬로 적용하여 LDPC 부호화 및 복호화를 수행할 수도 있다. 또한 상기 도 19의 기본 행렬에서 적절히 행과 열을 재정렬 하여 상기 재정렬된 행렬을 기본 행렬로 간주하여 LDPC 부호화 및 복호화를 수행할 수도 있다. 마찬가지로 도 20 내지 도 21의 지수 행렬에서 적절히 행과 열을 재정렬하여 상기 재정렬된 행렬을 지수 행렬로 간주하여 LDPC 부호화 및 복호화를 수행할 수도 있다.

일반적으로 LDPC 부호는 부호율에 따라 부호어 비트의 천공을 적용하여 부호율을 조절할 수 있다. 상기 도 19 내지 도 21에 나타낸 기본 행렬 또는 지수 행렬에 기반한 LDPC 부호는 차수가 1인 열에 대응되는 패리티 비트를 천공할 경우에는 LDPC 복호기에서 패리티 검사 행렬에서 해당 부분을 사용하지 않고 복호를 수행할 수 있기 때문에 복호 복잡도가 줄어드는 장점이 있다. 하지만, 부호화 성능을 고려할 경우에는 패리티 비트의 천공 순서 또는 생성된 LDPC 부호어의 전송 순서를 조절함으로써 LDPC 부호의 성능을 개선할 수 있는 방법이 있다.

예를 들어 상기 도 19 내지 도 21에 대응되는 기본 행렬 또는 지수 행렬 중 앞 2개 열에 대응되는 정보어 비트를 천공하고, 18번째 열부터 52번째 열에 대응되는 차수가 1인 패리티 비트를 모두 천공하면 부호율이 10/15인 LDPC 부호어를 전송할 수 있게 된다. 일반적으로 상기 도 19 내지 도 21에 대응되는 기본 행렬 및 지수 행렬을 이용하여 LDPC 부호어를 생성한 다음 적절히 레이트 매칭을 적용하면 성능이 더 개선될 수도 있다. 상기 레이트 매칭은 부호어 비트의 인터리빙을 포함할 수도 있다. 물론 상기 레이트 매칭을 고려하여 상기 기본 행렬 또는 지수 행렬에서의 열의 순서를 적절히 재정렬하여 LDPC 부호화 및 복호화 방법 및 장치에 적용할 수도 있다.

통상적으로 상기 LDPC 부호화 과정은 먼저 LDPC 부호화를 적용할 입력 비트(또는 코드 블록) 크기를 결정한 다음에 그 크기에 따라 상기 LDPC 부호화를 적용할 블록 크기(Z)를 결정하고, 상기 블록 크기에 따라 적절한 LDPC 지수 행렬 또는 수열을 결정한 다음, 상기 블록 크기(Z)와 상기 결정된 지수 행렬 또는 LDPC 수열을 기반으로 LDPC 부호화를 수행한다. 이때 상기 LDPC 지수 행렬 또는 수열을 변환 없이 LDPC 부호화에 적용할 수도 있으며, 경우에 따라 상기 LDPC 지수 행렬 또는 수열을 블록 크기(Z)에 따라 적절히 변환하여 LDPC 부호화를 수행할 수 있다.

마찬가지로 LDPC 복호화 과정은 전송된 LDPC 부호어에 대한 입력 비트 (또는 코드 블록) 크기를 결정한 다음에 그 크기에 따라 LDPC 복호화를 적용할 블록 크기(Z)를 결정하고, 상기 블록 크기에 따라 적절한 LDPC 지수 행렬 또는 수열을 결정한 다음, 상기 블록 크기(Z)와 상기 결정된 지수 행렬 또는 LDPC 수열을 기반으로 LDPC 복호화를 수행한다. 이때 상기 LDPC 지수 행렬 또는 수열을 변환 없이 LDPC 복호화에 적용할 수도 있으며, 경우에 따라 상기 LDPC 지수 행렬 또는 수열을 블록 크기(Z)에 따라 적절히 변환하여 LDPC 복호화를 수행할 수 있다.

도 19에 나타낸 기본 행렬은 다양한 형태로 표현 가능한데 일례로 다음 수학식 20과 같은 수열을 이용하여 표현할 수도 있다. 수학식 20은 도 19의 기본 행렬에서 원소 1의 위치를 각 행 별로 나타낸 것이다. 예를 들어 상기 수학식 20에서 2 번째 수열의 2 번째 값 3의 의미는 기본 행렬에서 2번째 행의 3번째 열에 원소 1이 있음을 의미한다. (상기 예에서 수열 및 행렬에서의 원소의 시작 순서는 0부터 시작하는 것으로 간주하였다.)

[수학식 20]

0 1 2 3 6 9 10 11

0 3 4 5 6 7 8 9 11 12

0 1 3 4 8 10 12 13

1 2 4 5 6 7 8 9 10 13

0 1 11 14

0 1 5 7 11 15

0 5 7 9 11 16

1 5 7 11 13 17

0 1 12 18

1 8 10 11 19

0 1 6 7 20

0 7 9 13 21

1 3 11 22

0 1 8 13 23

1 6 11 13 24

0 10 11 25

1 9 11 12 26

1 5 11 12 27

0 6 7 28

0 1 10 29

1 4 11 30

0 8 13 31

1 2 32

0 3 5 33

1 2 9 34

0 5 35

2 7 12 13 36

0 6 37

1 2 5 38

0 4 39

2 5 7 9 40

1 13 41

0 5 12 42

2 7 10 43

0 12 13 44

1 5 11 45

0 2 7 46

10 13 47

1 5 11 48

0 7 12 49

2 10 13 50

1 5 11 51

마찬가지로 도 20 내지 도 21에 나타낸 지수 행렬은 다양한 형태로 표현 가능한데 일례로 다음 수학식 21 내지 수학식 22과 같이 각각 수열을 이용하여 표현할 수도 있다. 수학식 21 내지 수학식 22은 도 20 내지 도 21의 42x52 크기의 지수 행렬에서 각 원소를 행 별로 나타낸 것이다. 지수 행렬에서 ZxZ 크기의 영행렬에 대응되는 특정 원소 값(예: -1)은 제외할 수 있다. 예를 들어 상기 수학식 21에서 2 번째 수열의 2 번째 값 251의 의미는 도 20의 지수 행렬 2번째 행에서 ZxZ 크기의 영행렬에 대응되지 않는 2 번째 순환 순열 행렬의 지수 값(또는 비트의 순환 시프트 값)이 251임을 의미한다. (상기 예에서 수열 및 행렬에서의 원소의 시작 순서는 0부터 시작하는 것으로 간주하였다.)

[수학식 21]

190 219 193 18 182 0 0 0

203 4 212 173 46 45 172 213 0 0

164 125 251 238 240 1 0 0

73 228 129 95 226 246 81 209 0 0

217 168 73 0

210 76 177 110 224 0

115 204 29 59 124 0

138 161 181 123 179 0

44 138 195 0

194 4 192 105 0

36 80 243 25 0

224 189 89 238 0

207 133 233 0

147 184 226 3 0

228 14 31 33 0

22 138 38 0

61 74 105 2 0

46 38 83 5 0

6 6 248 0

202 212 250 0

232 156 251 0

35 249 36 0

106 166 0

109 10 181 0

166 29 221 0

138 38 0

226 55 28 150 0

5 115 0

64 3 240 0

12 177 0

3 109 96 241 0

9 237 0

25 78 51 0

227 130 91 0

177 254 220 0

177 48 46 0

22 0 236 0

231 191 0

50 11 191 0

16 253 207 0

1 243 129 0

218 8 202 0

[수학식 22]

143 19 176 165 196 13 0 0

18 27 3 102 185 17 14 180 0 0

126 163 47 183 132 1 0 0

36 48 18 111 203 3 191 160 0 0

43 27 117 0

136 49 36 132 62 0

7 34 198 168 12 0

163 78 143 107 58 0

101 177 22 0

186 27 205 81 0

125 60 177 51 0

39 29 35 8 0

18 155 49 0

32 53 95 186 0

91 20 52 109 0

174 108 102 0

125 31 54 176 0

57 201 142 35 0

129 203 140 0

110 124 52 0

196 35 114 0

10 122 23 0

202 126 0

52 170 13 0

113 161 88 0

197 194 0

164 172 49 161 0

168 193 0

14 186 46 0

50 27 0

70 17 50 6 0

115 189 0

110 0 163 0

206 97 136 0

81 29 108 0

95 207 46 0

82 57 48 0

74 20 0

15 42 49 0

47 96 174 0

62 24 167 0

52 18 49 0

상기 수학식 15 내지 수학식 18에 기반하여 본 발명에서 제안하는 LDPC 부호의 설계 방법을 이용하여 설계된 LDPC 부호의 패리티 검사 행렬에 대응되는 지수 행렬에 대한 다른 실시 예를 도 22 내지 도 36에 나타내었다. (도 22 내지 도 34의 지수 행렬에서 빈 블록들은 ZxZ 크기의 영행렬에 대응되는 부분을 나타내며, -1 과 같은 특정된 값으로도 표현 가능하다.) 상기 도 22 내지 도 36에 나타낸 LDPC 부호의 지수 행렬들은 상기 도 19의 동일한 기본 행렬을 가진다는 특징이 있다.

도 22 내지 도 36은 도 20의 a, d 및 g에 대응되는 부분만을 도시한 것이다. 도 22 내지 도 36의 B, C, E, F, H 및 I 부분은 도 20의 B, C, E, F, H 및 I 부분과 동일하다. 즉, 도 20b, 20c, 20e, 20f, 20h 및 20i 부분에 도시된 바와 동일하다. 도 22 내지 도 36을 도 20의 a, d 및 g 부분으로 하여 도 20b, 20c, 20e, 20f, 20h 및 20i를 결합하여 새로운 지수 행렬을 구성할 수 있다.

상기 도 22 내지 도 36에 나타낸 지수 행렬들은 각각 수학식 15 또는 수학식 16에서 정의된 블록 크기 그룹을 고려하여 설계된 LDPC 부호에 각각 대응된다. 하지만 시스템의 요구 사항에 따라서 상기 블록 크기 그룹에 포함된 모든 블록 크기를 반드시 지원할 필요는 없다.

예를 들어 상기 도 22의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z1 또는 Z1' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 256을 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다.

상기 도 23의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z2 또는 Z2' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 192를 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다.

상기 도 24의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z3 또는 Z3' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 160을 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다.

상기 도 25의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z4 또는 Z4' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 224를 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다.

상기 도 26의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z5 또는 Z5' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 144를 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다.

상기 도 27의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z6 또는 Z6' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 176를 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다.

상기 도 28의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z7 또는 Z7' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 208을 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다.

상기 도 29의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z8 또는 Z8' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 240을 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다.

상기 도 30의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z2 또는 Z2' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 384을 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다. 상기 도 30의 지수 행렬의 특징은 블록 크기 192에 대해 수학식 18과 같은 모듈로 연산을 취하면 도 23과 동일한 지수 행렬이 생성됨을 확인할 수 있다.

상기 도 31의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z3 또는 Z3' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 320을 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다. 상기 도 31의 지수 행렬의 특징은 블록 크기 160에 대해 수학식 18과 같은 모듈로 연산을 취하면 도 24와 동일한 지수 행렬이 생성됨을 확인할 수 있다.

상기 도 32의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z5 또는 Z5' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 288을 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다. 상기 도 31의 지수 행렬의 특징은 블록 크기 144에 대해 수학식 18과 같은 모듈로 연산을 취하면 도 26과 동일한 지수 행렬이 생성됨을 확인할 수 있다.

상기 도 33의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z6 또는 Z6' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 352를 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다. 상기 도 31의 지수 행렬의 특징은 블록 크기 176에 대해 수학식 18과 같은 모듈로 연산을 취하면 도 27과 동일한 지수 행렬이 생성됨을 확인할 수 있다.

상기 도 34의 지수 행렬은 수학식 15 또는 수학식 16에서 그룹 Z7 또는 Z7' 또는 그 부분 집합에 대응되는 블록 크기에 적합하도록 최적화 되었을 뿐만 아니라, Z = 208을 최대값으로 설정하였을 때 좋은 성능을 제공할 수 있도록 정의되어 있다. 참고로 상기 도 34의 지수 행렬은 도 28의 지수 행렬과 동일한 설계 파리미터를 가지지만 지수 행렬들은 설계할 때 요구되는 BLER 값이나 특정 성능이 요구되는 최소 SNR을 조금씩 변경하여 도출된 다른 실시 예이다.

도 20 및 도 21의 지수 행렬과 마찬가지로 상기 도 22 내지 도 34의 지수 행렬 또한 다음 수학식 23 내지 수학식 35와 같이 각각 수열을 이용하여 표현할 수도 있다. 수학식 23 내지 수학식 35는 도 22 내지 도 34의 42x52 크기의 지수 행렬에서 각 원소를 행 별로 나타낸 것이다. 각각 지수 행렬에서 빈 블록은 ZxZ 크기의 영행렬에 대응되는데 만일 해당 빈 블록을 특정 원소 값(예: -1) 등으로 표현할 경우에 그 값은 제외할 수도 있다. 또한 상기 수학식 23에서 2 번째 수열의 2 번째 값 245의 의미는 도 22의 지수 행렬 2번째 행에서 ZxZ 크기의 영행렬에 대응되지 않는 2 번째 순환 순열 행렬의 지수 값(또는 비트의 순환 시프트 값)이 245임을 의미한다. (상기 예에서 수열 및 행렬에서의 원소의 시작 순서는 0부터 시작하는 것으로 간주하였다.)

[수학식 23]

232 76 250 10 132 221 0 0

107 126 62 99 50 55 191 232 0 0

90 136 245 64 102 1 0 0

197 224 243 140 70 179 5 8 0 0

64 18 247 0

154 219 164 94 196 0

135 204 53 59 98 0

210 253 103 110 255 0

200 222 113 0

83 18 101 108 0

122 157 203 107 0

190 149 5 218 0

38 58 233 0

118 68 40 245 0

68 67 79 243 0

14 227 39 0

38 244 16 7 0

114 156 1 38 0

167 136 204 0

201 215 180 0

75 194 58 0

217 37 246 0

190 58 0

44 200 147 0

129 241 254 0

47 197 0

121 14 51 18 0

19 208 0

229 191 155 0

197 138 0

104 95 50 234 0

57 233 0

218 21 61 0

247 237 45 0

196 171 212 0

254 72 150 0

212 226 188 0

204 219 0

214 175 77 0

47 195 245 0

24 81 134 0

40 6 112 0

[수학식 24]

161 9 186 186 19 47 0 0

58 33 144 176 176 120 186 70 0 0

188 23 75 11 176 1 0 0

147 25 181 40 44 189 20 19 0 0

139 20 166 0

163 39 38 114 156 0

35 180 123 0 149 0

81 134 172 76 145 0

124 113 13 0

177 183 93 109 0

15 50 184 22 0

6 114 190 161 0

189 159 128 0

110 28 100 33 0

27 188 27 161 0

158 17 14 0

142 153 129 44 0

139 181 112 67 0

177 20 62 0

185 152 145 0

158 46 171 0

21 33 9 0

90 8 0

102 190 18 0

66 13 181 0

145 45 0

135 55 186 157 0

44 125 0

130 145 104 0

20 181 0

148 170 14 162 0

67 5 0

173 94 122 0

144 29 177 0

85 46 175 0

145 77 87 0

55 189 159 0

124 14 0

63 130 32 0

54 25 125 0

45 144 29 0

149 187 148 0

[수학식 25]

142 18 38 127 4 16 0 0

108 126 85 134 106 135 10 22 0 0

17 1 94 140 119 1 0 0

14 127 57 85 37 115 108 18 0 0

151 12 136 0

12 127 122 158 72 0

128 6 46 146 121 0

149 120 13 29 53 0

48 126 58 0

59 24 37 50 0

110 147 20 116 0

56 151 133 37 0

25 81 133 0

48 114 94 2 0

113 142 17 13 0

56 146 137 0

91 33 26 37 0

59 99 121 39 0

147 150 13 0

109 54 31 0

142 0 3 0

155 138 97 0

80 17 0

12 44 25 0

157 63 158 0

23 70 0

151 65 45 9 0

85 125 0

33 141 130 0

37 42 0

137 39 144 154 0

46 133 0

153 84 6 0

73 48 156 0

126 110 24 0

1 125 38 0

119 4 63 0

156 110 0

7 26 89 0

50 41 118 0

109 136 126 0

150 42 106 0

[수학식 26]

86 13 182 141 23 143 0 0

53 55 214 6 39 41 18 21 0 0

65 105 49 176 95 1 0 0

168 221 173 86 18 55 180 170 0 0

106 2 92 0

169 20 151 21 209 0

179 159 203 48 138 0

182 35 209 22 213 0

26 114 158 0

211 191 217 1 0

134 99 62 53 0

1 8 38 0 0

70 25 23 0

25 149 37 18 0

63 31 0 214 0

7 108 8 0

201 201 142 167 0

63 52 215 125 0

86 122 27 0

31 92 66 0

92 222 41 0

74 219 169 0

114 2 0

78 103 223 0

96 214 196 0

173 184 0

87 208 24 75 0

20 130 0

189 25 168 0

38 60 0

188 174 6 51 0

58 196 0

73 197 180 0

170 108 198 0

110 190 192 0

9 213 158 0

31 19 128 0

188 223 0

183 210 169 0

8 91 109 0

4 184 149 0

134 42 218 0

[수학식 27]

17 102 80 5 75 59 0 0

26 69 46 53 54 115 68 36 0 0

95 71 116 30 2 1 0 0

59 52 16 137 27 96 75 129 0 0

79 103 15 0

129 24 39 28 23 0

138 100 127 117 42 0

42 31 17 115 16 0

116 88 112 0

100 119 25 40 0

97 122 9 136 0

8 143 134 110 0

12 78 15 0

73 96 21 143 0

26 106 102 53 0

110 56 37 0

95 66 91 95 0

19 123 90 71 0

54 124 9 0

62 24 54 0

123 40 38 0

116 143 5 0

42 120 0

15 10 28 0

11 27 54 0

122 143 0

1 136 143 23 0

39 87 0

31 46 14 0

137 104 0

134 58 104 52 0

101 13 0

86 103 108 0

135 16 130 0

95 82 97 0

72 97 113 0

58 66 86 0

96 50 0

115 131 10 0

74 111 71 0

105 32 131 0

133 101 3 0

[수학식 28]

156 143 14 3 40 123 0 0

17 65 63 1 55 37 171 133 0 0

98 168 107 82 142 1 0 0

53 174 174 127 17 89 17 105 0 0

86 67 83 0

79 84 35 103 60 0

47 154 10 155 29 0

48 125 24 47 55 0

53 31 161 0

104 142 99 64 0

111 25 174 23 0

91 175 24 141 0

122 11 4 0

29 91 27 127 0

11 145 8 166 0

137 103 40 0

78 158 17 165 0

134 23 62 163 0

173 31 22 0

13 135 145 0

128 52 173 0

156 166 40 0

18 163 0

110 132 150 0

113 108 61 0

72 136 0

36 38 53 145 0

42 104 0

64 24 149 0

139 161 0

84 173 93 29 0

117 148 0

116 73 142 0

105 137 29 0

11 41 162 0

126 152 172 0

73 154 129 0

167 38 0

112 7 19 0

109 6 105 0

160 156 82 0

132 6 8 0

[수학식 29]

9 148 1 184 37 148 0 0

185 20 39 130 203 111 39 1 0 0

86 16 192 119 74 1 0 0

126 107 156 113 199 166 90 79 0 0

60 3 10 0

117 184 61 70 49 0

37 99 64 39 174 0

120 48 18 51 29 0

33 118 175 0

23 64 170 119 0

145 86 185 127 0

131 20 140 194 0

34 185 174 0

78 107 55 34 0

185 167 59 48 0

91 10 152 0

45 198 138 186 0

182 42 135 21 0

28 100 37 0

187 96 181 0

61 181 161 0

123 186 35 0

54 197 0

33 27 50 0

160 203 74 0

193 98 0

84 178 100 17 0

28 138 0

130 120 171 0

12 2 0

77 160 173 57 0

49 63 0

136 189 190 0

168 181 198 0

206 58 101 0

185 157 132 0

58 7 157 0

39 205 0

79 98 187 0

37 50 189 0

18 4 94 0

161 55 154 0

[수학식 30]

75 22 197 27 180 215 0 0

218 22 129 161 189 201 30 81 0 0

35 3 198 212 79 1 0 0

53 80 103 62 176 50 189 140 0 0

239 198 124 0

96 87 178 212 23 0

150 34 90 144 214 0

166 108 177 107 30 0

68 129 40 0

158 6 219 78 0

51 44 124 22 0

67 108 154 226 0

46 0 194 0

100 2 172 231 0

117 40 75 230 0

227 168 140 0

233 94 202 92 0

90 53 167 188 0

111 45 175 0

25 171 182 0

1 238 132 0

170 118 235 0

182 95 0

103 20 228 0

238 150 216 0

83 53 0

54 132 22 230 0

47 181 0

30 146 206 0

215 227 0

99 20 227 235 0

232 157 0

228 158 29 0

194 213 189 0

208 191 163 0

181 185 158 0

199 223 4 0

196 52 0

86 46 8 0

187 1 139 0

8 216 65 0

149 162 26 0

[수학식 31]

161 201 378 378 211 239 0 0

58 225 144 176 176 120 378 262 0 0

380 23 75 203 176 1 0 0

147 25 181 232 44 189 20 211 0 0

139 212 358 0

163 39 38 306 348 0

35 372 123 0 149 0

273 326 172 268 337 0

124 305 205 0

369 375 93 109 0

15 242 184 214 0

6 114 190 353 0

189 159 320 0

302 220 292 33 0

27 188 27 161 0

158 209 14 0

142 345 321 236 0

331 181 112 67 0

177 20 254 0

185 344 337 0

158 46 171 0

21 33 9 0

90 200 0

102 190 210 0

66 205 181 0

145 45 0

327 247 378 349 0

44 125 0

322 145 296 0

20 373 0

340 362 206 354 0

67 5 0

365 286 314 0

144 221 369 0

277 46 175 0

337 269 87 0

247 381 351 0

124 206 0

255 130 32 0

246 25 125 0

237 336 221 0

149 187 148 0

[수학식 32]

302 18 198 287 164 16 0 0

268 286 85 134 106 295 170 182 0 0

177 161 254 140 119 1 0 0

174 127 217 245 37 275 108 178 0 0

151 172 296 0

12 127 122 318 232 0

128 166 46 306 281 0

149 280 13 189 213 0

48 126 58 0

219 24 37 50 0

270 307 20 276 0

216 151 133 37 0

185 81 293 0

48 114 254 2 0

113 302 17 173 0

56 146 297 0

91 193 26 37 0

59 259 281 39 0

307 310 173 0

269 214 191 0

302 0 3 0

315 138 257 0

80 177 0

12 44 185 0

157 223 158 0

23 70 0

311 225 205 169 0

85 125 0

193 141 290 0

37 202 0

297 199 304 314 0

46 133 0

313 244 166 0

73 208 316 0

286 110 24 0

161 285 38 0

279 164 223 0

156 270 0

167 186 89 0

210 41 118 0

269 296 286 0

150 42 106 0

[수학식 33]

161 102 224 149 219 59 0 0

26 213 46 53 54 259 212 180 0 0

239 71 260 174 2 1 0 0

203 52 16 137 27 240 219 273 0 0

79 103 15 0

273 168 39 172 167 0

138 244 271 261 186 0

186 31 17 115 16 0

116 88 256 0

244 119 25 40 0

97 122 9 280 0

152 143 134 110 0

12 78 159 0

73 96 165 143 0

26 250 102 53 0

110 56 181 0

95 66 235 239 0

19 123 90 71 0

198 124 9 0

206 168 198 0

123 40 38 0

116 143 149 0

42 264 0

15 10 28 0

11 171 54 0

122 143 0

145 280 143 23 0

39 87 0

175 46 158 0

137 248 0

278 202 248 196 0

101 13 0

230 247 252 0

135 160 274 0

239 226 97 0

72 241 113 0

202 210 86 0

96 194 0

115 275 10 0

74 111 71 0

249 176 275 0

133 101 147 0

[수학식 34]

332 143 190 3 216 299 0 0

193 65 63 1 231 37 171 309 0 0

274 168 283 258 142 1 0 0

229 174 174 303 17 265 193 281 0 0

262 243 259 0

79 260 35 279 236 0

223 330 10 331 205 0

48 125 200 223 55 0

229 207 337 0

280 142 99 240 0

111 25 174 199 0

91 175 24 317 0

298 11 4 0

29 91 203 303 0

11 321 8 342 0

137 279 40 0

78 334 17 165 0

310 199 62 163 0

173 31 198 0

189 135 321 0

128 52 173 0

332 166 40 0

18 339 0

110 132 326 0

113 284 61 0

72 312 0

212 214 229 321 0

42 104 0

64 24 325 0

139 337 0

260 349 269 205 0

117 148 0

292 249 318 0

105 313 205 0

187 41 162 0

302 328 172 0

249 330 305 0

167 214 0

288 7 195 0

285 6 105 0

336 332 258 0

132 6 8 0

[수학식 35]

195 175 20 165 92 203 0 0

18 131 159 206 81 121 165 171 0 0

126 59 99 79 39 1 0 0

36 204 70 59 99 159 114 173 0 0

147 27 13 0

84 101 140 80 114 0

111 86 198 81 64 0

7 130 91 3 6

49 125 22

186 75 205 81

177 60 21 103

195 29 185 164

174 51 49

84 1 53 134

39 176 104 5

122 4 154

125 9 106 176

57 201 194 35

77 47 88

58 72 0

144 191 166

10 135 127

98 178

156 118 65

61 57 36

145 38

112 172 101 5

168 89

118 186 202

102 79

122 17 154 163

11 33

162 156 59

59 17 179

41 128 17

7 175 75

187 156 24

81 122

168 78 109

26 73 87

55 34 207

114 161 189

상기 도 22 내지 도 34 또는 수학식 23 내지 수학식 35에 나타낸 지수 행렬에 기반한 LDPC 부호 역시 도 20 및 도 21의 LDPC 지수 행렬과 마찬가지로 차수가 1인 열에 대응되는 패리티 비트를 천공할 경우에는 LDPC 복호기에서 패리티 검사 행렬에서 해당 부분을 사용하지 않고 복호를 수행할 수 있기 때문에 복호 복잡도가 줄어드는 장점이 있다. 하지만, 부호화 성능을 고려할 경우에는 패리티 비트의 천공 순서 또는 생성된 LDPC 부호어의 전송 순서를 조절함으로써 LDPC 부호의 성능을 개선할 수 있는 방법이 있다.

일반적으로 상기 도 19 내지 도 34에 대응되는 기본 행렬 및 지수 행렬을 이용하여 LDPC 부호어를 생성한 다음 적절히 레이트 매칭을 적용하면 성능이 더 개선될 수도 있다. 상기 레이트 매칭은 부호어 비트의 인터리빙을 포함할 수도 있다. 물론 상기 레이트 매칭을 고려하여 상기 기본 행렬 또는 지수 행렬에서의 열의 순서를 적절히 재정렬하여 LDPC 부호화 및 복호화 방법 및 장치에 적용할 수도 있다.