KR20180098661A - 전자기장 측정 시스템 - Google Patents

전자기장 측정 시스템 Download PDFInfo

- Publication number

- KR20180098661A KR20180098661A KR1020187022018A KR20187022018A KR20180098661A KR 20180098661 A KR20180098661 A KR 20180098661A KR 1020187022018 A KR1020187022018 A KR 1020187022018A KR 20187022018 A KR20187022018 A KR 20187022018A KR 20180098661 A KR20180098661 A KR 20180098661A

- Authority

- KR

- South Korea

- Prior art keywords

- probe

- transmission line

- conductive

- substrate

- conductive strip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R29/00—Arrangements for measuring or indicating electric quantities not covered by groups G01R19/00 - G01R27/00

- G01R29/08—Measuring electromagnetic field characteristics

- G01R29/0807—Measuring electromagnetic field characteristics characterised by the application

- G01R29/0814—Field measurements related to measuring influence on or from apparatus, components or humans, e.g. in ESD, EMI, EMC, EMP testing, measuring radiation leakage; detecting presence of micro- or radiowave emitters; dosimetry; testing shielding; measurements related to lightning

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R29/00—Arrangements for measuring or indicating electric quantities not covered by groups G01R19/00 - G01R27/00

- G01R29/08—Measuring electromagnetic field characteristics

- G01R29/0864—Measuring electromagnetic field characteristics characterised by constructional or functional features

- G01R29/0878—Sensors; antennas; probes; detectors

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/001—Measuring interference from external sources to, or emission from, the device under test, e.g. EMC, EMI, EMP or ESD testing

- G01R31/002—Measuring interference from external sources to, or emission from, the device under test, e.g. EMC, EMI, EMP or ESD testing where the device under test is an electronic circuit

Landscapes

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- General Physics & Mathematics (AREA)

- Measuring Leads Or Probes (AREA)

- Tests Of Electronic Circuits (AREA)

Abstract

Description

도 2는 전자기장 측정 시스템 내의 프로브 모듈의 개략적인 측면도이다.

도 3은 프로브 모듈의 개략적인 평면도이다.

도 4는 프로브 모듈의 개략적인 정면도이다.

도 5는 프로브 모듈의 개략적인 배면도이다.

도 6은 도 4 및 도 5에서 A-A 선으로 나타낸 평면을 따라 절단했을 때의 프로브 모듈의 상부의 개략적인 단면도이다.

도 7은 프로브 모듈 내의 프로브 기판 상의 프로브의 개략적인 평면도이다.

도 8은 프로브 모듈 내의 전송 라인 기판 내의 전송 라인 구조체의 개략적인 반투명 상면도이다.

도 9는 도 8에서 B-B 선으로 나타낸 평면을 따라 절단했을 때의 전송 라인 구조체 내에서의 프로브 결합부(probe coupling section)의 개략적인 단면도이다.

도 10은 도 8에서 C-C 선으로 나타낸 평면을 따라 절단했을 때의 전송 라인 구조체 내에서의 헤드부(head section)의 개략적인 단면도이다.

도 11은 도 8에서 D-D 선으로 나타낸 평면을 따라 절단했을 때의 전송 라인 구조체에서의 전이부(transition section)의 개략 단면도이다.

도 12는 도 8에서 E-E 선으로 나타낸 평면을 따라 절단했을 때의 전송 라인 구조체 내에서의 마이크로-스트립 라인부(micro-strip line section)의 개략적인 단면도이다.

Claims (15)

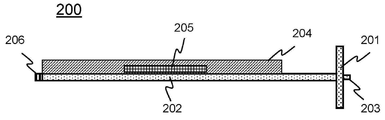

- 전자기장 측정 시스템(100)으로서,

- 제 1 프로브 소자(709), 제 2 프로브 소자(710) 및 기준 평면(reference plane)(711)을 갖는 프로브(700)를 포함하는 프로브 기판(701)으로서, 전자기장은 상기 기준 평면에 대하여 제 1 도전성 프로브 소자 내에서 제 1 프로브 신호를 유도하고 상기 기준 평면에 대하여 상기 제 2 프로브 소자 내에서 제 2 프로브 신호를 유도하는, 상기 프로브 기판(701); 및

- 상기 프로브에 결합된 전송 라인 구조체(800)를 포함하는 전송 라인 기판(202)으로서, 상기 전송 라인 구조체(800)는 제 1 프로브 신호 및 제 2 프로브 신호를 기초한 측정 결과들을 제공하도록 구성된 측정치 프로세싱 장치(measurement processing arrangement)(102)를 향해 제 1 프로브 신호 및 제 2 프로브 신호를 개별적으로 안내하도록 구성된, 상기 전송 라인 기판(202);을 포함하며,

상기 프로브 기판 및 전송 라인 기판은 T형 구조체를 형성하고, 상기 프로브 기판은 캡을 형성하고, 상기 전송 라인 기판은 상기 T형 구조체의 스템(stem)을 형성하며;

상기 제 1 프로브 소자와 제 2 프로브 소자는 상기 제 1 프로브 소자 및 제 2 프로브 소자 사이에 상기 전송 라인 기판에 수직인 대칭 축(712)이 존재하도록 배치되는, 전자기장 측정 시스템(100). - 제 1 항에 있어서,

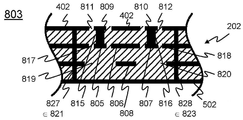

상기 전송 라인 구조체(800)는 헤드부(head section)(802)를 포함하며, 상기 헤드부(802)는,

- 상기 제 1 프로브 소자(709)에 도전적으로 결합된 제 1 도전성 스트립(805);

- 상기 제 2 프로브 소자(710)에 도전적으로 결합된 제 2 도전성 스트립(807); 및

- 상기 제 1 도전성 스트립 및 제 2 도전성 스트립 사이에 배치되고, 상기 프로브(700)의 상기 기준 평면(711)에 도전적으로 결합되는 중간 도전성 스트립(806)을 포함하는, 전자기장 측정 시스템(100). - 제 2 항에 있어서,

상기 전송 라인 구조체(800)의 헤드부(802)의 제 1 도전성 스트립(805) 및 제 2 도전성 스트립(807)은 두 개의 도전성 차폐 평면들(shielding planes)(402, 502) 사이에 개재되고,

상기 두 개의 도전성 차폐 평면들은 상기 프로브(700)의 도전성 기준 평면(711)에 도전적으로 결합되는, 전자기장 측정 시스템(100). - 제 3 항에 있어서,

상기 전송 라인 구조체(800)의 헤드부(802)의 제 1 도전성 스트립(805)과 제 2 도전성 스트립(807) 사이에 차폐 펜스(shielding fence)(822)가 배치되고,

상기 차폐 펜스는 상기 두 개의 도전성 차폐 평면들(402,502)과 상기 헤드부의 중간 도전성 스트립(806)을 서로 도전적으로 결합시키는 관통-홀 접속부들(through-hole connections)의 어레이에 의해 형성되는, 전자기장 측정 시스템(100). - 제 4 항에 있어서,

두 개의 추가의 차폐 펜스들(821,823)을 포함하며,

상기 두 개의 추가의 차폐 펜스들(821, 823) 사이에, 상기 전송 라인 구조체(800)의 헤드부(802)의 제 1 도전성 스트립(805)과 제 2 도전성 스트립(807)이 배치되며,

상기 차폐 펜스는 상기 두 개의 도전성 차폐 평면들(402,502)을 서로 도전적으로 결합시키는 관통-홀 접속부들의 어레이에 의해 형성되는, 전자기장 측정 시스템(100). - 제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 전송 라인 구조체(800)는 마이크로-스트립 라인부(804)를 포함하고, 상기 헤드부(803)는 상기 프로브(700)와 마이크로-스트립 라인부 사이에 개재되며,

상기 마이크로-스트립 라인부는:

- 상기 헤드부의 제 1 도전성 스트립(805)에 도전적으로 결합된 제 1 도전성 스트립(809);

- 상기 헤드부의 제 2 도전성 스트립(807)에 도전적으로 결합된 제 2 도전성 스트립(810); 및

- 상기 마이크로-스트립 라인부에서 상기 제 1 도전성 스트립 및 제 2 도전성 스트립과 평행하게 배치되고, 제 1 도전성 스트립 및 제 2 도전성 스트립과 마주하며, 상기 헤드부의 중간 도전성 스트립(806)에 도전적으로 결합된 접지 평면(ground plane)(813);을 포함하는, 전자기장 측정 시스템(100). - 제 6 항에 있어서,

상기 전송 라인 기판(800)은,

- 상기 두 개의 도전성 차폐 평면들 중 하나(402)를 포함하는 제 1 도전 층(601);

- 상기 헤드부(802)의 제 1 도전성 스트립(805), 제 2 도전성 스트립(807) 및 중간 도전성 스트립(806)을 포함하는 제 2 도전 층(603); 및

- 상기 두 개의 도전성 차폐 평면들 중 다른 하나(502)를 포함하는 제 3 도전 층(602);을 포함하는, 전자기장 측정 시스템(100). - 제 7 항에 있어서,

- 상기 제 1 도전성 층(601)은 상기 전송 라인 구조체(800)의 마이크로-스트립 라인부(804) 내의 제 1 도전성 스트립(809) 및 제 2 도전성 스트립(810)을 포함하며;

- 상기 제 2 도전 층(603)은 상기 마이크로-스트립 라인부의 접지 평면(813)을 포함하며;

- 상기 전송 라인 기판(202)은, 상기 마이크로-스트립 라인부의 제 1 도전성 스트립 및 제 2 도전성 스트립을, 상기 전송 라인 구조체의 헤드부(802)의 제 1 도전성 스트립(805) 및 제 2 도전성 스트립(807)에 각기 도전적으로 결합시키는 제 1 관통-홀 접속부(815) 및 제 2 관통-홀 접속부(816)를 포함하는, 전자기장 측정 시스템(100). - 제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

- 상기 프로브 기판(701)은 슬롯(702)을 포함하며;

- 상기 전송 라인 기판(202)은 상기 프로브 기판의 슬롯을 따라서 연장된 프로브 결합 탭(probe coupling tab)(703)을 포함하는, 전자기장 측정 시스템(100). - 제 9 항에 있어서,

상기 제 1 프로브 소자(709) 및 제 2 프로브 소자(710)는 상기 슬롯(702)의 일 측면 상에 배치되고, 상기 기준 평면(711)은 상기 슬롯의 다른 반대편 측면 상에 배치되는, 전자기장 측정 시스템(100). - 제 1 항 내지 제 10 항 중 어느 한 항에 있어서,

상기 제 1 프로브 소자(709) 및 제 2 프로브 소자(710)는 서로에 대해 직교하도록 배치되는, 전자기장 측정 시스템(100). - 제 1 항 내지 제 11 항 중 어느 한 항에 있어서,

상기 제 1 프로브 신호 및 제 2 프로브 신호를 가산하고 상기 제 2 프로브 신호로부터 제 1 프로브 신호를 감산하도록 구성된 회로(205,102)를 포함하는, 전자기장 측정 시스템(100). - 제 1 항 내지 제 12 항 중 어느 한 항에 있어서,

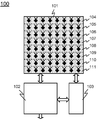

복수의 프로브 모듈(104 내지 111)을 포함하고,

상기 프로브 기판(201)과 전송 라인 기판(202)은 함께 프로브 모듈(200)을 형성하며,

다른 프로브 모듈들도 유사하게 구성되는, 전자기장 측정 시스템(100). - 제 13 항에 있어서,

각각의 프로브들은 2차원 그리드로서 배치되며,

상기 2차원 그리드 내에서 프로브(700)는 격자 점(grid point)을 구성하는, 전자기장 측정 시스템(100). - 제 1 항 내지 제 14 항 중 어느 한 항에 따른 전자기장 측정 시스템(100)을 사용하여 전자기장을 측정하는 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP15307164.2 | 2015-12-29 | ||

| EP15307164.2A EP3187887A1 (en) | 2015-12-29 | 2015-12-29 | Electromagnetic field measurement system |

| PCT/EP2016/082759 WO2017114854A1 (en) | 2015-12-29 | 2016-12-28 | Electromagnetic field measurement system |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20180098661A true KR20180098661A (ko) | 2018-09-04 |

| KR102868570B1 KR102868570B1 (ko) | 2025-10-10 |

Family

ID=55589634

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020187022018A Active KR102868570B1 (ko) | 2015-12-29 | 2016-12-28 | 전자기장 측정 시스템 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US10725078B2 (ko) |

| EP (2) | EP3187887A1 (ko) |

| JP (1) | JP6873491B2 (ko) |

| KR (1) | KR102868570B1 (ko) |

| CN (1) | CN108700622B (ko) |

| WO (1) | WO2017114854A1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20220121292A (ko) * | 2021-02-24 | 2022-09-01 | 주식회사 엘지에너지솔루션 | 스트립라인 클램프의 전기장 균일성 측정방법 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11310747B2 (en) * | 2019-06-12 | 2022-04-19 | Qualcomm Incorporated | Methods and apparatus for user equipment to differentiate human grip from protective covers |

| US20240302419A1 (en) * | 2021-03-09 | 2024-09-12 | Integral Geometry Science Inc. | Inspecting device and inspecting method |

| WO2024106028A1 (ja) * | 2022-11-16 | 2024-05-23 | パナソニックコネクト株式会社 | 電界検出方法および装置 |

| CN117783702B (zh) * | 2023-12-29 | 2024-08-02 | 上海交通大学 | 同时测量垂直磁场与垂直电场的双分量近场探头及系统 |

| CN120214546B (zh) * | 2025-05-22 | 2025-07-22 | 东莞市台易电子科技有限公司 | 一种探针测试设备及测试方法 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20120135221A (ko) * | 2009-12-31 | 2012-12-12 | 아트-피 | 전자기장 측정 시스템 |

| EP2610628A1 (en) * | 2011-12-30 | 2013-07-03 | Art-Fi | Measuring an electromagnetic field |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6359596B1 (en) * | 2000-07-28 | 2002-03-19 | Lockheed Martin Corporation | Integrated circuit mm-wave antenna structure |

| US6573801B1 (en) * | 2000-11-15 | 2003-06-03 | Intel Corporation | Electromagnetic coupler |

| JP4025084B2 (ja) * | 2002-02-04 | 2007-12-19 | 株式会社ルネサステクノロジ | Emi測定装置 |

| FR2859064B1 (fr) * | 2003-08-18 | 2005-12-30 | Satimo Sa | Dispositif de controle du debit d'absorption specifique d'objets rayonnants fabriques en serie et notamment de telephones portables |

| US8073641B2 (en) * | 2005-01-11 | 2011-12-06 | Taiyo Yuden Co., Ltd. | Electromagnetic field distribution measuring method, apparatus for the method, computer program and information recording medium |

| US8502546B2 (en) * | 2006-04-05 | 2013-08-06 | Emscan Corporation | Multichannel absorberless near field measurement system |

| KR102008038B1 (ko) | 2011-11-29 | 2019-08-06 | 아트-피 | 인체의 유전체 특성을 시뮬레이션한 조성물 및 sar 측정을 위한 이의 사용 |

-

2015

- 2015-12-29 EP EP15307164.2A patent/EP3187887A1/en not_active Withdrawn

-

2016

- 2016-12-28 EP EP16829248.0A patent/EP3397975B1/en active Active

- 2016-12-28 CN CN201680082827.9A patent/CN108700622B/zh active Active

- 2016-12-28 WO PCT/EP2016/082759 patent/WO2017114854A1/en not_active Ceased

- 2016-12-28 KR KR1020187022018A patent/KR102868570B1/ko active Active

- 2016-12-28 US US16/067,408 patent/US10725078B2/en active Active

- 2016-12-28 JP JP2018553302A patent/JP6873491B2/ja active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20120135221A (ko) * | 2009-12-31 | 2012-12-12 | 아트-피 | 전자기장 측정 시스템 |

| EP2610628A1 (en) * | 2011-12-30 | 2013-07-03 | Art-Fi | Measuring an electromagnetic field |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20220121292A (ko) * | 2021-02-24 | 2022-09-01 | 주식회사 엘지에너지솔루션 | 스트립라인 클램프의 전기장 균일성 측정방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP6873491B2 (ja) | 2021-05-19 |

| US20190004100A1 (en) | 2019-01-03 |

| EP3397975B1 (en) | 2020-02-12 |

| US10725078B2 (en) | 2020-07-28 |

| EP3187887A1 (en) | 2017-07-05 |

| CN108700622A (zh) | 2018-10-23 |

| EP3397975A1 (en) | 2018-11-07 |

| KR102868570B1 (ko) | 2025-10-10 |

| WO2017114854A1 (en) | 2017-07-06 |

| CN108700622B (zh) | 2020-07-03 |

| JP2019508712A (ja) | 2019-03-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20180098661A (ko) | 전자기장 측정 시스템 | |

| US7323874B2 (en) | Combined positron emission tomography and magnetic resonance tomography unit | |

| KR101759996B1 (ko) | 전자기장 측정 시스템 | |

| US20100275934A1 (en) | Magnetic Method and System for Locating A Target | |

| US10041987B2 (en) | Systems, devices and methods related to near-field electric and magnetic probes | |

| JP6259972B2 (ja) | マイクロ波受信用アンテナ及びマイクロ波受信用アンテナアレイ | |

| US12399203B2 (en) | Bridge-based impedance sensor system | |

| JP2014131199A (ja) | アンテナアレイ装置及び異常組織検出装置 | |

| US20050154284A1 (en) | Method and system for calibration of a marker localization sensing array | |

| US20150168564A1 (en) | Scintillating Fiber Dosimeter for Magnetic Resonance Imaging Enviroment | |

| US6900637B1 (en) | Phased array coil with center shifted sensitivity | |

| DE102016120246A1 (de) | Verfahren, Vorrichtung und Computerprogramm zum Bestimmen einer Information über eine Position eines Objekts, wobei das Objekt ein Magnetfeld emittiert | |

| JP2015516064A (ja) | 超広帯域測定ブリッジ | |

| CN103519814A (zh) | 具有合成孔径mri传感器的导管 | |

| US9535136B2 (en) | Magnetic field probe | |

| JP2007278781A (ja) | 半導体評価装置 | |

| Nowikow et al. | Network and Field Analysis of Koch Snowflake Fractal Geometry Radiofrequency Coils for Sodium MRI | |

| US20040238213A1 (en) | Uniform impedance printed circuit board | |

| Chen et al. | Frequency and time domain crosstalk signal analysis for integrated high-density circuits | |

| US7414414B2 (en) | Spatially distributed guarded impedance | |

| Anderson | A source of accurately calculable quasi-static magnetic fields | |

| Douarville-Blaise et al. | Eliminate crosstalk using symmetry in MIMO arrays of inductive antennas: an introduction to Pie-Chart antennas | |

| Chou et al. | Analysis and treatment of u-shape PCB I/O ports to reduce the EMI from image-plane noise | |

| Sachs et al. | ULTRA-WIDEBAND RADIO TECHNOLOGIES FOR COMMUNICATIONS, LOCALIZATION AND SENSOR APPLICATIONS | |

| US20160178715A1 (en) | Output combination of transistors in an mrt radio-frequency power amplifier |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

St.27 status event code: A-0-1-A10-A15-nap-PA0105 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| F11 | Ip right granted following substantive examination |

Free format text: ST27 STATUS EVENT CODE: A-2-4-F10-F11-EXM-PR0701 (AS PROVIDED BY THE NATIONAL OFFICE) |

|

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U12-oth-PR1002 Fee payment year number: 1 |

|

| U12 | Designation fee paid |

Free format text: ST27 STATUS EVENT CODE: A-2-2-U10-U12-OTH-PR1002 (AS PROVIDED BY THE NATIONAL OFFICE) Year of fee payment: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| Q13 | Ip right document published |

Free format text: ST27 STATUS EVENT CODE: A-4-4-Q10-Q13-NAP-PG1601 (AS PROVIDED BY THE NATIONAL OFFICE) |