KR20170127420A - 다수의 독립적인 마이크로컨트롤러들을 구비한 마이크로컨트롤러 디바이스 - Google Patents

다수의 독립적인 마이크로컨트롤러들을 구비한 마이크로컨트롤러 디바이스 Download PDFInfo

- Publication number

- KR20170127420A KR20170127420A KR1020177023569A KR20177023569A KR20170127420A KR 20170127420 A KR20170127420 A KR 20170127420A KR 1020177023569 A KR1020177023569 A KR 1020177023569A KR 20177023569 A KR20177023569 A KR 20177023569A KR 20170127420 A KR20170127420 A KR 20170127420A

- Authority

- KR

- South Korea

- Prior art keywords

- microcontroller

- pins

- system bus

- interface

- master

- Prior art date

Links

- 230000002093 peripheral effect Effects 0.000 claims abstract description 61

- 230000015654 memory Effects 0.000 claims abstract description 49

- 238000012545 processing Methods 0.000 claims abstract description 10

- 238000000034 method Methods 0.000 claims description 44

- 230000006870 function Effects 0.000 description 29

- 238000004891 communication Methods 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 230000009977 dual effect Effects 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 238000012546 transfer Methods 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000012544 monitoring process Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 230000000116 mitigating effect Effects 0.000 description 1

- 230000004043 responsiveness Effects 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/16—Combinations of two or more digital computers each having at least an arithmetic unit, a program unit and a register, e.g. for a simultaneous processing of several programs

- G06F15/163—Interprocessor communication

- G06F15/167—Interprocessor communication using a common memory, e.g. mailbox

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/22—Means for limiting or controlling the pin/gate ratio

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1673—Details of memory controller using buffers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/36—Handling requests for interconnection or transfer for access to common bus or bus system

- G06F13/362—Handling requests for interconnection or transfer for access to common bus or bus system with centralised access control

- G06F13/364—Handling requests for interconnection or transfer for access to common bus or bus system with centralised access control using independent requests or grants, e.g. using separated request and grant lines

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/382—Information transfer, e.g. on bus using universal interface adapter

- G06F13/385—Information transfer, e.g. on bus using universal interface adapter for adaptation of a particular data processing system to different peripheral devices

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4282—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus

-

- Y02B60/1228—

-

- Y02B60/1235—

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Software Systems (AREA)

- Microcomputers (AREA)

- Multi Processors (AREA)

Abstract

마이크로컨트롤러 디바이스는: 복수의 외부 핀들; 제 1 중앙 처리 유닛(CPU), 상기 제 1 CPU와 결합된 제 1 시스템 버스, 상기 제 1 시스템 버스와 결합된 제 1 메모리, 및 상기 제 1 시스템 버스와 결합된 제 1 복수의 주변 디바이스들을 갖는 제 1 마이크로컨트롤러; 및 제 2 중앙 처리 유닛(CPU), 상기 제 2 CPU와 결합된 제 2 시스템 버스, 상기 제 2 시스템 버스와 결합된 제 2 메모리, 및 상기 제 2 시스템 버스와 결합된 제 2 복수의 주변 디바이스들을 갖는 제 2 마이크로컨트롤러를 구비한 하우징을 가지며, 여기서 제 1 및 제 2 마이크로컨트롤러는 전용 인터페이스를 통해서만 통신한다.

Description

관련 출원에 대한 상호 참조

본 출원은, 2015년 3월 13일 출원된 동일 출원인에 의한 미국 가출원 번호 62/133,186 호의 우선이익을 주장하며, 상기 미국 가출원은 모든 목적들을 위해 본 출원에 참조로 통합된다.

기술 분야

본 개시는 마이크로컨트롤러들에 관한 것으로, 특히, 다수의 독립적인 프로세서 코어들을 구비한 마이크로컨트롤러 디바이스에 관한 것이다.

공지된 마이크로컨트롤러 디바이스들은 단일 중앙 처리 유닛(마이크로컨트롤러 코어), 및 타이머, 아날로그-디지털 컨버터, 디지털-아날로그 컨버터, 펄스 폭 변조 유닛들과 같은 복수의 관련된 주변 디바이스들; 메모리들; 입/출력(I/O) 포트들 등을 포함한다. 일반적으로 내부 시스템 버스 및 제어 로직은 마이크로컨트롤러 코어가 주변기기들에 개별적으로 액세스할 수 있도록 모든 구성요소들을 연결시킨다(link). 외부적으로, 마이크로컨트롤러는 복수의 외부 핀들을 포함하며, 이 핀들의 대부분은 일반적으로 I/O 포트와 연관되고, 각각의 포트 핀은 핀을 다른 주변 디바이스들과 공유함으로써 다기능을 제공할 수도 있다. 구성을 설정하는 동안에 사용자는 어떤 핀에 어떤 기능을 할당할지를 선택한다. 이러한 할당들은 또한, 프로그램의 실행 중에 변경될 수도 있다.

메인 CPU와 분리된 명령들을 실행할 수 있는 추가 가속기 유닛들을 포함하는 소정 마이크로컨트롤러들이 알려져 있다. 2개의 분리된 CPU들과 복수의 공통 주변기기들을 포함하는 다른 마이크로컨트롤러들이 알려져 있다. 따라서, 코어들 둘 다는 대기 시간을 추가하는 크로스바 스위치를 필요로 하는 모든 주변기기들을 공유하고, 여기서 크로스바 스위치는 고장에 취약하다. 기존의 멀티-코어 디바이스들은 스위치 매트릭스들을 이용하여, 다수의 프로세서들이 메모리 및 주변기기들과 같은 공유된 시스템 리소스들에 액세스할 수 있게 한다. 여러 코어들이 동일한 리소스에의 액세스를 요청할 수 있다. 충돌 해결 회로망(conflict resolution circuitry)은 대기 시간을 추가하고 성능을 저하시키며 비용을 추가한다. 스위치 매트릭스는 시스템의 단일 고장 지점이다. 일부 제조업체들은 복수의 스위치 매트릭스들을 구현할 수 있다. 이를 위해서는 스위치 매트릭스들 간의 고장 해결을 처리하는 로직이 훨씬 더 많이 필요하다. 다른 제조업체들은 서로 다른 소프트웨어 아키텍처들을 구비한 다수의 코어들을 사용한다. 이러한 서로 다른 코어들은 일부 전용 리소스들을 구비할 수 있지만 다른 리소스들은 공유된다.

하지만, 듀얼 또는 멀티-코어 마이크로컨트롤러 디바이스들을 보다 잘 구현할 필요가 있다.

일 실시예에 따르면, 마이크로컨트롤러 디바이스는: 복수의 외부 핀들; 제 1 중앙 처리 유닛(CPU), 상기 제 1 CPU와 결합된 제 1 시스템 버스, 상기 제 1 시스템 버스와 결합된 제 1 메모리, 및 상기 제 1 시스템 버스와 결합된 제 1 복수의 주변 디바이스들을 포함하는 제 1 마이크로컨트롤러; 및 제 2 중앙 처리 유닛(CPU), 상기 제 2 CPU와 결합된 제 2 시스템 버스, 상기 제 2 시스템 버스와 결합된 제 2 메모리, 및 상기 제 2 시스템 버스와 결합된 제 2 복수의 주변 디바이스들을 포함하는 제 2 마이크로컨트롤러를 포함할 수 있고, 여기서 제 1 및 제 2 마이크로컨트롤러는 전용 인터페이스를 통해서만 통신한다.

추가 실시예에 따르면, 상기 전용 인터페이스는 양방향 메일박스 인터페이스, 단방향 마스터-슬레이브 인터페이스 및 단방향 슬레이브-마스터 인터페이스를 포함할 수 있다. 추가 실시예에 따르면, 각각의 단방향 인터페이스는 FIFO 메모리를 포함할 수 있다. 추가 실시예에 따르면, 상기 제 1 마이크로컨트롤러는 마스터일 수 있고 상기 제 2 마이크로컨트롤러는 슬레이브일 수 있다. 추가 실시예에 따르면, 상기 제 2 마이크로컨트롤러의 프로그램 메모리는 상기 제 1 마이크로컨트롤러에 의해 기록 가능한 휘발성 메모리를 포함할 수 있다. 추가 실시예에 따르면, 상기 제 2 마이크로컨트롤러는 상기 제 1 마이크로컨트롤러보다 빠르게 클록킹될(clocked) 수 있다. 추가 실시예에 따르면, 상기 제 2 마이크로컨트롤러는 저전력 모드를 포함하는 전력 모드 제어 유닛을 포함하고, 상기 제 1 마이크로컨트롤러는 상기 제 2 마이크로컨트롤러의 전력 모드를 제어하도록 구성될 수 있다. 추가 실시예에 따르면, 상기 전력 제어 모드 유닛은 상기 제 2 마이크로컨트롤러가 어떠한 전력도 소모하지 않도록 상기 제 2 마이크로컨트롤러를 디스에이블하기 위해 동작 가능하다. 추가 실시예에 따르면, 각각의 마이크로컨트롤러는 16 비트의 데이터 버스 폭을 가질 수 있다. 추가 실시예에 따르면, 각각의 마이크로컨트롤러는 상기 마이크로컨트롤러와 관련된 상기 주변 디바이스들을 위해 상기 복수의 외부 핀들 중 적어도 일부를 선택하도록 프로그램 가능한 핀 선택 유닛을 더 포함할 수 있다. 추가 실시예에 따르면, 각각의 마이크로컨트롤러는 입/출력 핀들의 제어부를 상기 제 1 마이크로컨트롤러와 상기 제 2 마이크로컨트롤러 중 어느 하나에 할당하도록 제어 가능한 패드 소유권 멀티플렉서 유닛을 더 포함할 수 있다. 추가 실시예에 따르면, 각각의 마이크로컨트롤러는 임의의 판독 가능 외부 핀을 판독할 수 있지만, 상기 제 1 또는 제 2 마이크로컨트롤러에 할당된 핀들만이 각각의 마이크로컨트롤러에 의해 기록될 수 있다. 추가 실시예에 따르면, 각각의 마이크로컨트롤러의 주변기기들 각각의 적어도 일부는 복수의 외부 핀들 중 소정 외부 핀들에 할당될 수 있다.

또 하나의 실시예에 따르면, 마이크로컨트롤러 디바이스를 동작시키는 방법으로서, 상기 마이크로컨트롤러 디바이스는: 복수의 외부 핀들; 제 1 중앙 처리 유닛(CPU), 상기 제 1 CPU와 결합된 제 1 시스템 버스, 상기 제 1 시스템 버스와 결합된 제 1 메모리, 및 상기 제 1 시스템 버스와 결합된 제 1 복수의 주변 디바이스들을 포함하는 제 1 마이크로컨트롤러; 및 제 2 중앙 처리 유닛(CPU), 상기 제 2 CPU와 결합된 제 2 시스템 버스, 상기 제 2 시스템 버스와 결합된 제 2 메모리, 및 상기 제 2 시스템 버스와 결합된 제 2 복수의 주변 디바이스들을 포함하는 제 2 마이크로컨트롤러를 포함하고, 상기 방법은 전용 인터페이스를 통해서만 상기 제 1 마이크로컨트롤러와 상기 제 2 마이크로컨트롤러 사이에 통신하는 단계를 포함할 수 있다.

상기 방법의 추가 실시예에 따르면, 상기 전용 인터페이스는 양방향 메일박스 인터페이스, 단방향 마스터-슬레이브 인터페이스 및 단방향 슬레이브-마스터 인터페이스를 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 각각의 단방향 인터페이스는 FIFO 메모리를 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 제 1 마이크로컨트롤러는 마스터일 수 있고 상기 제 2 마이크로컨트롤러는 슬레이브일 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 제 2 마이크로컨트롤러의 프로그램 메모리는 휘발성 메모리를 포함할 수 있고, 여기서 상기 방법은 상기 제 1 마이크로컨트롤러에 의해 상기 제 2 마이크로컨트롤러의 상기 프로그램 메모리에 기록하는 단계를 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 방법은 상기 제 1 마이크로컨트롤러보다 빠르게 상기 제 2 마이크로컨트롤러를 클록킹하는 것을 더 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 제 2 마이크로컨트롤러는 저전력 모드를 포함하는 전력 모드 제어 유닛을 포함할 수 있고, 상기 방법은 제 1 마이크로컨트롤러에 의해 상기 제 2 마이크로컨트롤러의 전력 모드를 제어하는 단계를 더 포함한다. 상기 방법의 추가 실시예에 따르면, 상기 제 2 마이크로컨트롤러가 어떠한 전력도 소모하지 않도록, 전력 제어 모드 유닛에 의해 상기 제 2 마이크로컨트롤러를 디스에이블하는 단계를 포함할 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 방법은 각각의 마이크로컨트롤러에 대한 핀 소유권을 제어하는 단계를 더 포함할 수 있으며, 여기서 입/출력 핀들은 상기 제 1 마이크로컨트롤러와 상기 제 2 마이크로컨트롤러 중 어느 하나에 할당된다. 상기 방법의 추가 실시예에 따르면, 각각의 마이크로컨트롤러는 임의의 판독 가능 외부 핀을 판독할 수 있지만, 상기 제 1 또는 제 2 마이크로컨트롤러에 할당된 핀들만이 각각의 마이크로컨트롤러에 의해 기록될 수 있다. 상기 방법의 추가 실시예에 따르면, 상기 방법은: 상기 제 1 마이크로컨트롤러에 의해 복수의 외부 핀들 중 하나를 판독하는 단계, 상기 제 2 마이크로컨트롤러에 의해 복수의 외부 핀들 중 상기 하나를 판독하는 단계, 및 상기 전용 인터페이스에 의해 상기 복수의 외부 핀들 중 상기 하나로부터 판독된 값을 비교하는 단계를 더 포함할 수 있다.

도 1은 일 실시예에 따른 마이크로컨트롤러의 블록도이다.

도 2는 또 하나의 실시예에 따른 마이크로컨트롤러의 블록도이다.

도 3은 다양한 실시예들에 따른 마이크로컨트롤러용 하우징의 평면도이다.

도 4는 패드 소유권(pad ownership) 제어 메커니즘의 일 실시예를 도시한 도면이다.

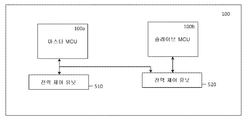

도 5는 일 실시예에 따른 마이크로컨트롤러들의 전력 제어를 도시한 도면이다.

도 2는 또 하나의 실시예에 따른 마이크로컨트롤러의 블록도이다.

도 3은 다양한 실시예들에 따른 마이크로컨트롤러용 하우징의 평면도이다.

도 4는 패드 소유권(pad ownership) 제어 메커니즘의 일 실시예를 도시한 도면이다.

도 5는 일 실시예에 따른 마이크로컨트롤러들의 전력 제어를 도시한 도면이다.

일반적으로 마이크로컨트롤러는 외부 부품들을 전혀 필요로 하지 않기 때문에 단일의 시스템 온 칩으로 간주된다. 따라서, 이러한 디바이스는 중앙 처리 유닛, 메모리 및 복수의 I/O 주변기기들을 포함한다. 게다가 I/O 포트들은 직접 디지털 제어에 사용될 수 있다. 이 I/O 포트들은 보통 주변 기능부들과 공유되며, 범용 I/O 포트 기능 또는 특정 주변 기능을 갖도록 프로그램될 수 있다.

예를 들어 28-핀 패키지와 같이 핀 수가 적은 패키지들에서는, 기존의 단일-코어 마이크로컨트롤러의 애플리케이션 성능은 2개의 프로세서 코어들 - 각각이 16 비트의 데이터 버스 폭을 가짐 - 을 제공함으로써 증가될 수 있다. 또한, 다양한 실시예들에 따라 실시간 제어 시스템을 위한 고객 소프트웨어 개발이 용이해질 수 있고, 증가된 안전 모니터링(ClassB)이 제공될 수 있고, 그리고 하드웨어, 소프트웨어 및 주변 리소스들을 여러 독립 마이크로컨트롤러들로 분리함으로써 에러 완화가 개선될 수 있다.

일부 실시예들에 따르면, 마이크로컨트롤러 디바이스에는 핀 수가 적은 패키지들(low pin count packages)(28 핀 내지 64 핀)의 단일 다이 상에 독립적인 MCU들의 다수의 인스턴스들이 제공될 수 있다. 따라서, 집적 회로 패키지는 예를 들어, 2개의 독립적인 마이크로컨트롤러들을 포함할 것이고, 이들 각각은 자체 메모리 및 복수의 관련된 주변 디바이스들을 구비할 것이다. 일부 실시예들에 따르면, 하나의 마이크로컨트롤러는 마스터 마이크로컨트롤러로 구성될 수 있고, 다른 마이크로컨트롤러는 슬레이브 마이크로컨트롤러일 수 있다. 마이크로컨트롤러들 둘 다가 동일하거나 유사한 주변 디바이스들을 가질 수 있지만, 주변 디바이스들은 서로 다를 수 있으며, 특히 적응된 특정 태스크들(이것을 위해 각각의 마이크로컨트롤러가 예정됨)일 수 있다. 또한, 데이터 및 프로그램 메모리의 크기들이 서로 다를 수 있으며, 여기서 마스터는 일반적으로 더 큰 프로그램 및 데이터 메모리들을 포함할 수 있다.

따라서, 다양한 실시예들에 따르면, 자체 전용 프로세서, 메모리 및 주변 리소스들을 구비한 2개(또는 그 이상)의 마이크로컨트롤러들을 단일 실리콘 다이에 어셈블한 것이 제공된다. 다수의 마이크로컨트롤러들은 디바이스 핀들을 공유하는데, 이로 인해 디바이스를 적은 핀 수의 패키지들에 포함시키는 것이 실행 가능해진다. 따라서 외부 핀들은 프로그램 제어(또는 구성 레지스터 제어) 하에 마스터 MCU와 슬레이브 MCU 중 어느 하나에 할당될 수 있다. 일부 실시예들에 대한 본 개시의 규칙에 따르면, 외부 핀들의 수는 모든 집적된 MCU들의 데이터 버스 폭의 합보다 적다. 예를 들어, 2-코어 MCU는 2개의 16-비트 MCU들을 포함할 수 있고 이들 각각은 16 비트의 데이터 버스 폭을 갖는다. 따라서 모든 집적된 MCU들의 데이터 버스 폭의 합은 32가 될 것이다. 28 핀 하우징 내에 이러한 디바이스를 구현할 때, 이러한 디바이스는 위에서 언급한 규칙을 따를 것이다.

다양한 실시예들에 따르면, 멀티-코어 MCU (멀티-프로세서) 디바이스에서, 외부 핀들의 수 <= 코어들의 수 × 각 프로세서의 비트 폭이다. 특히, 일부 실시예들에 따르면, 외부 핀들의 수는 마스터 프로세서의 데이터 버스 폭보다 적다. 예를 들어, 다양한 실시예들에 따른 듀얼 코어 마이크로컨트롤러는 이하에서 보다 상세히 설명되는 바와 같이 28 핀 하우징 내에 장착될 수 있다. 전술한 바와 같이, 다양한 실시예들은 다수의 마이크로 컨트롤러 유닛들(MCUs)을 갖는 마이크로컨트롤러 디바이스로 이루어지며, 이 마이크로 컨트롤러 유닛들 각각은 자체의 프로세서, 메모리 및 주변기기들을 갖는다.

복수의 MCU들은 외부 디바이스 핀들을 공유하도록 설계된다. 모든 MCU들은 그것의 전용 특수 기능 레지스터를 통해 핀의 판독(또는 관찰)을 가능케 하도록 구성될 수 있지만, 전용 레지스터를 통한 핀에의 기록(구동)은 비휘발성 메모리를 통해 제어된다. 따라서 비휘발성 메모리는 디바이스 핀들의 "소유권"을 정의하는데 사용되고, 이에 의해 충돌들을 방지한다. 소유권은 구성의 설정 시기(phase) 동안에 정의될 수 있는데, 예를 들면, 소유권은 디바이스가 한번 동작 모드에 있으면 변경될 수 없는 구성 레지스터들을 사용하여 디바이스의 프로그래밍 동안에 정의될 수 있다. 대안적으로, 특수 기능 레지스터들의 사용을 통해 동적 할당을 가능케 하는 특수 기능 레지스터들 및 프로시저들이 구현될 수 있다. 이러한 레지스터들의 부주의한 덮어쓰기는 기존의 EEPROM 쓰기 루틴들에서 사용되는 것들과 유사한 특수 쓰기 루틴들을 통해 방지될 수 있다. 외부 핀들 중 하나를 코어들 중 하나에 할당하는 것으로 인해 소프트웨어 및 하드웨어 실패들로부터 보호된다. 디바이스 핀들을 제어 가능하게 공유함으로써 멀티-코어 디바이스를 적은 핀 수의 패키지로 실용화할 수 있다.

다양한 실시예들에 따르면, 2개(또는 그 이상)의 마이크로컨트롤러들은 자체의 전용 프로세서, 메모리 및 주변 리소스들과 함께 단일 실리콘 다이 상에 어셈블되고, 여기서 코어들 간의 특정 통신 인터페이스가 제공된다. 마이크로컨트롤러들은 마스터 슬레이브 인터페이스(MasterSlave Interface; MSI)를 통해 서로 통신하며, MSI는 일 실시예에 의하면, 레지스터들(메일 박스들) 및 관련 상태 비트들과 인터럽트들(세미포어들(semiphores))의 세트일 수 있다.

고전적인 컴퓨터 아키텍처 방식은 여러 프로세서들이 스위치 매트릭스를 통해 메모리 및 주변기기들과 같은 디바이스 리소스들과 통신하도록 하는 것이다. 이러한 종래의 실시예들에서, 2개(또는 그 이상)의 프로세서들은 모든 시스템 리소스들을 공유한다. 스위치 매트릭스는 각각의 리소스에 대한 각각의 프로세서로부터 각각의 요청에 우선 순위를 할당해야 하며, 충돌들이 해결되어야 한다. 이 리소스 충돌 관리는 각각의 요청에 대기 (시간)을 크게 추가한다. 스위치 매트릭스들은 크며 단일 지점 고장들에 취약하다. 스위치 매트릭스들의 취약점들을 해결하는 고전적인 해결책은 스위치 매트릭스들을 복제하는 것이다. 이것은 고장들을 검출하고 어떤 스위치 매트릭스가 여전히 실행 가능한지를 검출하기 위해 아직도 더 많은 회로망을 필요로 한다. 다양한 실시예들은 리소스들을 공유하기 위해 스위치 매트릭스들을 사용하려고 시도하는 복잡성을 회피하고자, 그 대신에 단지 리소스들을 복제한다.

두 번째 전형적인 아키텍처는, 일부 주변기기들을 공유하지만 메모리 및 일부 주변기기들과 같은 자체 제한된 세트의 리소스들에 액세스하는 코프로세서(coprocessor)를 더한 프로세서의 개념이다. 전형적으로 이 아키텍처는, 복제 비용이 많이 들고 따라서 프로세서와 코프로세서 간에 공유되는 다수의 주변기기들을 가지고 있다. 전형적으로 프로세서와 코프로세서는 서로 다른 소프트웨어 아키텍처들을 가질 수 있고, 따라서 소프트웨어 생성을 위해 서로 다른 개발 도구들을 필요로 한다.

이러한 종래의 접근법들 대신에, 다양한 실시예들에 따른 예를 들어 도 1에 도시된 바와 같이, 전체 MCU(마이크로 컨트롤러 유닛)들은 각각이 전용 메모리 및 주변기기들을 가지며, 단일 칩으로 복제된다. 개별 MCU들은 디바이스 핀을 구동할 때 충돌들을 방지하기 위해 보안 비휘발성 레지스터들을 통해 디바이스 핀들을 공유하지만, 모든 MCU들은 MCU에 할당된 디바이스 핀뿐만 아니라 MCU들에 할당되지 않는 디바이스 핀들조차도 언제든지 판독할 수 있다. 도 1의 예는 그 결과 높은 핀 수의 디바이스가 된다.

도 1은 단일 집적 회로 하우징 내에 2개의 마이크로컨트롤러들을 갖는 듀얼 코어 마이크로컨트롤러(100)를 도시한다. 제 1 마이크로컨트롤러는 CPU(110), 시스템 버스(120) 및 복수의 주변기기들(130a..n) 외에도 데이터 메모리(140), 예컨대 16kbBytes RAM, 프로그램 메모리(150), 예컨대 128kBytes 플래시 메모리, 및 DMA 컨트롤러(160)를 포함한다. 시스템 버스는 2개의 버스들, 즉 도 1에 표시된 바와 같은 주변 버스와 메모리 버스로 분할될 수 있거나, 또는 모든 디바이스들을 연결하는 단일 시스템 버스가 구현될 수 있다. DMA 컨트롤러(160)와 같은 주변기기들 중 일부는 어떤 외부 연결도 갖지 않을 수 있고, PWM들, ADC들, 비교기들 및 일부 직렬 인터페이스들과 같은 다른 주변기기들은 소정의 외부 다기능 핀에 할당될 수 있다. 다른 직렬 인터페이스들, 터치 센서들, 타이머들, 비교기 출력부들과 같은 다른 주변기기들은 주변 핀 선택기 유닛(170)을 통해 복수의 외부 핀들 중 하나에 할당될 수 있다. 일부 핀들은 제 1 MCU의 하나보다 많은 주변기기에 할당 가능하고, 일반적으로 그것의 기능을 MCU의 범용 I/O 포트와 공유할 수 있다. 그러므로, 이 실시예는 2개의 패드 소유권 멀티플렉서들(180 및 280)을 제공한다. 디폴트 할당에서, 마스터 또는 슬레이브 MCU와 연관된 각각의 핀은 각각의 MCU의 범용 I/O 포트에 할당될 수 있지만, 패드 소유권 멀티플렉서(180)의 프로그램 제어하에 상기 주변기기들 중 하나에 할당될 수 있다. 일부 핀들(190)은 도 1에 도시된 바와 같이 직렬 프로그래밍 인터페이스, ADC 또는 임의의 다른 주변기기와 같은 주변기기에 디폴트로(by default) 할당될 수 있다. 상술한 바와 같이, 주변 핀 선택 유닛(180)은 또한 외부 핀들의 각각의 세트 중 임의의 세트에 할당될 주변기기의 일부 또는 전부를 할당하게 할 수 있다.

외부 핀들은 다이들(dice)에 전력을 공급하는데 사용되는 제 1 세트의 핀들을 포함한다. 이것은 예를 들어 도 2에 도시된 바와 같은 디지털 및 아날로그 전력 공급 핀들과 이러한 핀들의 여러 인스턴스들을 포함할 수 있다. 또한, 마스터 클리어 핀은 어떠한 다른 기능도 가질 수 없으며, 디바이스를 리셋 및/또는 프로그램하는데 사용될 수 있다. 나머지 두 번째 세트의 핀들은 일반적으로 입력/출력 핀들(I/O 핀들)이다. 그러나, 마이크로컨트롤러들 중 하나에 의해 제어되지 않는 일부 다른 핀들이 있을 수 있다. 본 개시에 따른 I/O 핀은, 입력 핀과 출력 핀 중 어느 하나이거나 전용 입력 또는 출력 기능을 갖는 핀이도록 프로그램 가능한 임의의 핀으로서 정의된다. 입력 핀은 각각의 주변기기의 설정에 따라 디지털 또는 아날로그 입력으로 사용될 수 있다. 유사하게 출력 핀은 각각의 주변기기의 설정에 따라 디지털 또는 아날로그 출력으로 사용될 수 있다. 전술한 바와 같이, 본 출원은 일반적으로 입력/출력 핀들을 지칭하며, 일부 핀들은 단지 입력 또는 출력 핀들로서만 사용될 수 있다. 모든 입력/출력 핀들은 신호들을 출력할 때 마이크로컨트롤러들 중 하나에 의해 제어되는 핀들이며, 이 핀들에 공급되는 신호들은 마이크로컨트롤러들 중 하나에 의해 수신된 신호들이다. 전력 공급 핀들은 일반적으로 이 기능을 가진 것들로 간주되지 않는다. 일부 다른 핀들도 또한, 이러한 기능을 갖지 않을 수 있는데, 예를 들면 디바이스는 발진기용 전용 핀들을 구비할 수 있다. 그러나, 이러한 핀들은 또한 도 3에 도시된 바와 같이 마이크로컨트롤러 I/O 기능들과 다중화될 수 있다. 도 3은 I/O 핀들로 간주되지 않을 핀들이 핀들(5-8, 19, 20)과 핀(27)이라는 것을 보여준다.

특수 기능 레지스터들이 패드 소유권 멀티플렉서들을 제어하는데 사용될 수 있다. 이 실시예에서, 각각의 마이크로컨트롤러 코어는 자신의 특수 기능 레지스터들에만 액세스할 수 있다. 그러나, 다른 또 하나의 실시예에 따르면, 마스터 MCU만이 2개의 패드 소유권 멀티플렉서들(180, 280)을 제어하는 특수 기능 레지스터들에 액세스할 수 있다. 또한, 마스터 CPU(110)는 직접 또는 특정 인터페이스를 통해 슬레이브 MCU의 프로그램 RAM(250)에 액세스할 수도 있다. 이 특징으로 인해, 마스터 MCU를 통해 슬레이브 MCU의 프로그램 RAM(250)의 프로그래밍/기록이 가능하게 된다.

이 실시예에서의 제 2 MCU는 핀들(290), CPU(210), 시스템 버스(220) 및 복수의 주변기기들(230a..n) 외에도 데이터 메모리(240), 예컨대 4kByte RAM, 프로그램 메모리(250), 예컨대 24kByte RAM, 및 DMA 컨트롤러(260)를 포함한다. 전술한 바와 같이, 프로그램 메모리(250)는 마스터 MCU를 통해 프로그래밍을 가능케 하도록 휘발성일 수 있다. 그러나, 다른 실시예들에 따라 다른 구현들이 가능하다. 모든 다른 유닛들은 마스터 MCU와 유사할 수 있다. 제 1 MCU와 유사한 특정 주변기기들에 외부 핀들(290) 중의 일부를 유연하게 할당시킬 수 있도록 제 2 주변 핀 선택 유닛(270)이 제공된다. 그러나, 이 실시예에서는, 2개의 MCU들 사이에 핀들을 공유하지 않는다.

도 1은 또한, 2개의 코어들 사이의 통신을 양방향으로 가능케 하는 양방향 메일박스 시스템(310)과 2개의 단방향 FIFO들(320 및 330)를 통해 2개의 MCU들 간의 통신 인터페이스를 도시한다. 메일박스들은 명령 또는 짧은 데이터를 각각의 다른 마이크로컨트롤러로 전송하는데 사용될 수 있다. 도 1 및 도 2에 도시된 바와 같은 복수의 메일박스들(310)이 구현될 수 있다. 일단 데이터 또는 명령이 메일박스에 기록되면, 수신 마이크로컨트롤러 내에 각각의 인터럽트가 생성되어 새로운 메시지(명령 또는 데이터)가 사용 가능함을 나타낼 것이다. 이로 인해 어떤 추가 지연없이 신속하게 정보를 전송할 수 있다.

또한, 2개의 마이크로컨트롤러들 간에 더 큰 데이터 전송을 가능케 하는 2개의 FIFO들(320 및 330)이 구현될 수 있다. FIFO들(320 및 330)은 메일박스(310)의 크기 제한들을 가지지 않기 때문에 더 큰 데이터 전송들을 가능케 한다. FIFO들(320, 330)이 비게(empty) 되지 않으면(또는 에러 조건을 만난다면), 마스터와 슬레이브는 동시에 그것을 액세스할 수 있다. 따라서, FIFO(320, 330)는 하나의 프로세서에 의해 판독되기 전에 다른 프로세서에 의해 로딩되어야 하는 메일박스(310)에 근거한 데이터 파이프보다 우수한 처리량을 제공할 수 있다. 그러나, FIFO(320, 330) 콘텐츠는 순서대로 로딩 및 언로딩되며, 메일박스 데이터 파이프 내의 데이터와 같이 랜덤하게 액세스 가능하지 않다. FIFO는 또한 (정의상) 단방향이다. 이로 인해 FIFO는 프로세서들 간에 데이터 블록들을 전송하기 위해 가장 빠른 수단을 필요로 하는 애플리케이션들에 더 적합하게 된다.

다수의 마이크로컨트롤러들은 공통 소프트웨어 아키텍처를 공유할 수 있다. 따라서, 일 실시예에 따르면, 동일한 마이크로컨트롤러 코어들이 다양한 집적 마이크로컨트롤러들에 사용된다. 마스터 및 하나 이상의 슬레이브 마이크로컨트롤러들을 제공하는 개념은 추가로 전력 소비를 줄일 수 있게 한다. 슬레이브 마이크로컨트롤러들은 디스에이블되도록 구성될 수 있으며, 이에 의해 많은 에너지를 필요로 하지 않는 슬립 모드에 있게 된다. 다른 구현들에 따르면, 디바이스 내의 마이크로컨트롤러는 완전히 턴 오프되어 에너지를 절약할 수 있다.

도 5는 이러한 시스템의 예시적인 제어 구조를 보여준다. 각각의 마이크로컨트롤러(100a, 100b)는 전용 전력 제어 유닛(510 및 520)을 각각 구비할 수 있다. 각각의 전력 제어 유닛(510, 520)으로 인해, 특정 전력 소비 모드 및 관련 처리 전력을 설정할 수 있다. 예를 들어, 각각의 마이크로컨트롤러(100a, 100b)는 슬립 모드 또는 저전력 모드로 설정될 수 있다. 전력 소비의 다양한 레벨들이 제공될 수 있다. 또한, 일 실시예에 따르면, 마스터 마이크로컨트롤러(100a)는 슬레이브 마이크로컨트롤러(100b)를 완전히 턴 오프할 수 있다. 이 모드에서는, 마이크로컨트롤러(100b)는 전력을 소비하지 않을 것이다.

코어들은 또한 서로 다른 속도들로 동작할 수 있다. 이 기능은 특히, 휘발성 메모리를 제 2 마이크로컨트롤러의 프로그램 메모리로서 이용할 때 구현될 수 있다. RAM과 같은 휘발성 메모리는 본질적으로 보다 빠르기 때문에 보다 빠른 액세스 시간을 가능케 하고 따라서 보다 높은 클록킹 속도를 가능케 한다. 마스터 코어는 빈번한 인터럽트들로 시스템 레벨 기능들을 처리하도록 구성될 수 있다. 마스터 코어는 또한 안전 준수 기능들, 통신들, 인터럽트 처리, 소프트웨어 업데이트들, 사용자 인터페이스 등을 처리할 수 있다. 모든 마이크로컨트롤러가 외부 핀들 중 어느 하나를 판독할 수 있는 특징으로 인해, 예컨대 동일한 디바이스 핀들을 모니터링하는 다수의 MCU들에 의해 안전성이 개선될 수 있다. 예를 들어, 일 실시예에 따르면, 2개의 마이크로컨트롤러들은 향상된 안전 기능을 제공하기 위한 소프트웨어를 포함할 수 있으며, 여기서 복수의 외부 핀들 중 하나의 핀은 제 1 및 제 2 마이크로컨트롤러에 의해 독립적으로 판독된다. 이후, 검색된 값들은 통신 인터페이스에 의해 비교될 수 있다. 예를 들어, 단일 핀의 경우(caser)에, 메일박스들 중 하나는 판독된 값을 다른 코어로 포워딩하는데 사용될 수 있다. 대안적으로, FIFO들(320, 330) 중 하나는 하나 이상의 값들을 포워딩하는데 사용될 수 있다. 상기 값들이 일치하지 않거나 또는 에러를 정정하기 위해 특정 소프트웨어 루틴, 인터럽트 또는 재설정이 실행될 수 있는 경우에, 시스템은 경고를 출력할 수 있다.

다양한 실시예들에 따르면, 시간에 민감한 코드(time sensitive code)는 분할될 수 있는데, 이로 인해 코드 개발 및 지원이 용이하게 된다. 슬레이브 코어는 임계 대기 시간(critical latency), 모터 제어, 디지털 전력 제어 기능을 가진 제어 루프들과 같이 전용의 그리고 보다 결정론적인 애플리케이션 성능을 위해 사용될 수 있다. 따라서 슬레이브 마이크로컨트롤러로서 그것은 마스터 마이크로컨트롤러를 위한 추가 프로그래밍 가능 주변기기로 간주될 수 있다. 이러한 아키텍처의 이점은 단계 기능 성능 향상이다. 두 개의 코어들은 기본적으로 실행 속도를 두 배로 높인다. 위에서 언급했듯이, 시간 임계 기능들과 시스템 기능들은 분리되어 서로 다른 코어들에 할당될 수 있다. 제어 루프 응답성은 최적화될 수 있고, 인터럽트들은 최소화될 수 있으며, 그리고 모터 알고리즘 구현은 단순화될 수 있다. 마스터 코어의 실행 속도는 일 실시예에 따라 예를 들면 100 MIPS일 수 있지만; 슬레이브 코어 타겟은 더 빠른 프로그램 메모리, 예컨대 휘발성 랜덤 액세스 메모리를 제공함으로써, > 100 MIPS의 처리 파워를 가질 수 있다. 따라서, 슬레이브 마이크로컨트롤러는 일반적으로 마스터 마이크로컨트롤러보다 더 빠를 수 있다.

필요한 외부 핀들의 수는 일부 실시예들에 따라 도 2에 도시된 바와 같이 2개의 MCU들 간의 주변기기들에 사용되는 핀들을 공유함으로써 더욱 줄일 수 있다. 도 2는 도 1에 도시된 실시예에 반하여, 감소된 개수의 핀들(420)을 갖는 패키지 내의 멀티-코어 디바이스의 블록도를 도시한다. 도 2는 특히, 2개의 개별 MCU들을 구비한 듀얼 코어 마이크로컨트롤러의 28-핀 버전을 보여준다. 여기서는 단지 하나의 패드 소유권 멀티플렉서(410)가 제공될 수 있으며, 패드 소유권 멀티플렉서(410)는 예를 들어 특수 기능 레지스터들을 통해, 마스터 MCU에 의해서만 제어될 수 있다. 그러나, 일부 실시예들에 따르면, MCU들 둘 다가 액세스를 가질 수 있으며, 일 실시예에서 마스터 MCU가 슬레이브 MCU를 능가하는 우선 순위를 가질 수 있다.

이용 가능한 I/O 핀들 수가 감소됨에도 불구하고 각각의 MCU에는 여전히 동일하거나 훨씬 더 많은 핀들이 제공된다. 특히, 소정 주변기기들만을 필요로 하는 저비용 애플리케이션들은 이 해결책의 이점을 누리는데, 그 이유는 이러한 로우-핀 디바이스가 무엇보다도 인쇄 회로 기판의 비용을 줄여주기 때문이다. 패드 소유권 멀티플렉서(410)는 각각의 MCU의 범용 포트 기능성을 외부 핀들과 공유하는 것뿐만 아니라 마스터 MCU와 슬레이브 MCU 중 어느 하나의 주변기기들 중 하나에 할당하는 것을 가능케 한다.

도 2는 또한, 4개의 디지털 전력 공급 핀들(Vdd 및 Vss), 리셋 및 프로그래밍에 사용되는 비(non)-멀티플렉싱된 마스터 클리어 기능 핀, 및 2개의 아날로그 전력 공급 핀들(AVdd 및 AVss)을 보여준다. 나머지 21개의 핀들은 마스터 MCU와 슬레이브 MCU 중 어느 하나에 할당될 수 있는 외부 I/O 핀들이다. 따라서, 특정 구성들에서 모든 21개의 I/O 핀들은 슬레이브 MCU의 기능을 코프로세서(co-processor)의 기능으로 감소시키는 마스터 MCU에 할당될 수 있다. 유사하게, 또 하나의 구성은 모든 21개의 I/O 핀들을 슬레이브 MCU에 할당할 수 있다. 마스터 MCU와 슬레이브 MCU 할당 간에 임의의 할당량(ration)을 갖는 임의의 다른 할당도 가능하다.

도 4는 도 1의 패드 소유권 멀티플렉서들(180, 280) 또는 도 2의 패드 소유권 멀티플렉서들(410)의 가능한 제어를 도시한다. 제어는 구성 레지스터들(430)을 통해 달성될 수 있다. 이러한 레지스터들은 외부 프로그래머 또는 에뮬레이터 디바이스의 설정에 따라 자동으로 프로그램된다. 따라서, 일단 프로그램되면, 디바이스(100)의 동작 중에는 설정을 변경할 수 없다. 대안적으로, 특수 기능 레지스터들이 소유권 패드 멀티플렉서들(180, 280/410)을 제어하는데 사용될 수 있다. 이러한 실시예에서는 동적 제어가 가능하다. 우발적인 겹쳐 쓰기를 피하기 위해, EEPROM들에 사용된 것들과 유사한 기록 메커니즘, 예를 들면 시간 프레임 내에 쓰여진 일련의 특수 코드들이 사용될 수 있다.

도 3은 28-핀 패키지 내의 디바이스의 실제 핀아웃(pinout)을 보여준다. 슬레이브 주변기기들은 접두사 "S1"으로 표시된다. 도 3은 특히 각 핀의 멀티-기능 할당을 보여준다. 도 3은 이하에서 보다 상세하게 설명되는 바와 같이, 더 나은 가독성(legibility)을 위해, 외부 핀들에 할당될 수 있는 모든 기능들을 반드시 보여주지는 않는다. 여기서, 전형적으로 RAx는 5 비트를 갖는 범용 I/O 포트 A에 대한 핀들을 나타내고, RBx는 16-비트 포트 RB를 나타낸다. 전술한 바와 같이, 도 3은 더 나은 가독성을 위해 I/O 포트들 A 및 B의 단일 세트만을 보여준다. 그러나, 마스터 및 슬레이브 MCU에 의해 독립적으로 제어되는 2개의 개별 세트들이 구현되어 독립적으로 할당될 수 있다. 일 실시예에 따르면, 각각의 포트 핀은 도 3에 도시된 바와 같이 일반적인 핀 관련성을 가지고(with) 마스터와 슬레이브 중 어느 하나에 할당될 수 있다. 일 실시예에 따르면, 마스터 MCU로의 할당들은 슬레이브 MCU로의 할당을 능가하는 우선순위를 가질 수 있다. 다른 실시예들에 따르면, 마스터 MCU 및 슬레이브 MCU 용 포트들이 서로 다른 핀들에 할당될 수 있다.

ANx는 마스터 MCU용 아날로그 입력부들을 나타내고 S1ANx는 슬레이브 MCU용 아날로그 입력부들을 나타낸다. 포트 핀들과 유사하게, 외부 핀들에 대한 다른 관련성들이 마스터 및 슬레이브 MCU를 위해 선택될 수 있다. 용량형 분압기 주변기기가 구현되는 경우, 각각의 아날로그 핀이 또한 용량형 분압기 기능부에 할당될 수 있으며, 여기서 마스터 MCU와 슬레이브 MCU용 개별 유닛들이 제공될 수 있다. RPx는 주변 핀 선택 유닛들에 의해 할당된 16개의 핀들을 나타낸다. I/O 포트들과 유사하게, 마스터 및 슬레이브 MCU는 각각 예를 들어, 이용 가능한 16개의 핀들을 가질 수 있지만, 도 3은 (다시 더 나은 가독성을 위해) 단 하나의 세트만을 보여준다. 다른 실시예들에 따르면, 서로 다른 개수의 주변 핀 선택 핀들이 사용될 수 있는데, 예를 들면 이 핀들 중 8개는 마스터에 할당되고 8개 핀들은 슬레이브 MCU에 할당될 수 있다. 다시, 다른 개수의 핀들 및/또는 이러한 주변 핀 선택 유닛들의 할당들이 선택될 수 있다. 펄스 폭 변조기 핀들과 같은 다른 핀 기능들은 PWM과 같은 각각의 머리글자(acronym)들을 사용하는데, 머리글자의 처음에 있는 S1은 일반적으로 그 유닛이 슬레이브 MCU에 속한다는 것을 나타낸다.

위에서 언급했듯이 각 핀은 디폴트로 특정 기능부에 할당될 수 있다. 예를 들어, 핀들(1-3)은 디폴트로 마스터 MCU의 아날로그 입력부들로서 지정될 수 있다. 핀(4)과 핀(11)은 디폴트로 슬레이브 MCU의 아날로그 입력부들로서 지정될 수 있다. 핀(9)과 핀(10)은 디폴트로 발진기 입력 핀들일 수 있지만, 내부 발진기들이 사용될 때에는 다른 기능부들에 할당될 수도 있다. 핀들(12-13)은 마스터 MCU와만 상호 작용하는 동기식 직렬 프로그래밍 인터페이스(PGED2, PGEC2)에 디폴트로 할당될 수 있다. 핀들(14-18 및 21-26)은 디폴트로 PORTB 비트들(5-15)에 할당되고 핀(28)은 PORTA의 비트(0)에 할당된다. 위의 할당은 단지 예시일 뿐이며, 다른 할당들도 가능하다.

Claims (24)

- 마이크로컨트롤러 디바이스로서,

복수의 외부 핀들;

제 1 중앙 처리 유닛(CPU), 상기 제 1 CPU와 결합된 제 1 시스템 버스, 상기 제 1 시스템 버스와 결합된 제 1 메모리, 및 상기 제 1 시스템 버스와 결합된 제 1 복수의 주변 디바이스들을 포함하는 제 1 마이크로컨트롤러; 및

제 2 중앙 처리 유닛(CPU), 상기 제 2 CPU와 결합된 제 2 시스템 버스, 상기 제 2 시스템 버스와 결합된 제 2 메모리, 및 상기 제 2 시스템 버스와 결합된 제 2 복수의 주변 디바이스들을 포함하는 제 2 마이크로컨트롤러를 포함하고,

제 1 및 제 2 마이크로컨트롤러는 전용 인터페이스를 통해서만 통신하는, 마이크로컨트롤러 디바이스. - 제 1 항에 있어서,

상기 전용 인터페이스는 양방향 메일박스 인터페이스, 단방향 마스터-슬레이브 인터페이스 및 단방향 슬레이브-마스터 인터페이스를 포함하는, 마이크로컨트롤러 디바이스. - 제 2 항에 있어서,

각각의 단방향 인터페이스는 FIFO 메모리를 포함하는, 마이크로컨트롤러 디바이스. - 제 1 항 또는 제 2 항에 있어서,

상기 제 1 마이크로컨트롤러는 마스터이고 상기 제 2 마이크로컨트롤러는 슬레이브인, 마이크로컨트롤러 디바이스. - 제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 제 2 마이크로컨트롤러의 프로그램 메모리는 상기 제 1 마이크로컨트롤러에 의해 기록 가능한 휘발성 메모리를 포함하는, 마이크로컨트롤러 디바이스. - 제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 제 2 마이크로컨트롤러는 상기 제 1 마이크로컨트롤러보다 빠르게 클록킹되는(clocked), 마이크로컨트롤러 디바이스. - 제 1 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 제 2 마이크로컨트롤러는 저전력 모드를 포함하는 전력 모드 제어 유닛을 포함하고,

상기 제 1 마이크로컨트롤러는 상기 제 2 마이크로컨트롤러의 전력 모드를 제어하도록 구성되는, 마이크로컨트롤러 디바이스. - 제 7 항에 있어서,

상기 전력 제어 모드 유닛은 상기 제 2 마이크로컨트롤러가 어떠한 전력도 소모하지 않도록 상기 제 2 마이크로컨트롤러를 디스에이블하기 위해 동작 가능한, 마이크로컨트롤러 디바이스. - 제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

각각의 마이크로컨트롤러는 16 비트의 데이터 버스 폭을 갖는, 마이크로컨트롤러 디바이스. - 제 1 항 내지 제 9 항 중 어느 한 항에 있어서,

각각의 마이크로컨트롤러는 상기 마이크로컨트롤러와 관련된 상기 주변 디바이스들을 위해 상기 복수의 외부 핀들 중 적어도 일부를 선택하도록 프로그램 가능한 핀 선택 유닛을 더 포함하는, 마이크로컨트롤러 디바이스. - 제 1 항 내지 제 10 항 중 어느 한 항에 있어서,

각각의 마이크로컨트롤러는 입/출력 핀들의 제어부를 상기 제 1 마이크로컨트롤러와 상기 제 2 마이크로컨트롤러 중 어느 하나에 할당하도록 제어 가능한 패드 소유권 멀티플렉서 유닛을 더 포함하는, 마이크로컨트롤러 디바이스. - 제 1 항 내지 제 11 항 중 어느 한 항에 있어서,

각각의 마이크로컨트롤러는 임의의 판독 가능 외부 핀을 판독할 수 있지만, 상기 제 1 또는 제 2 마이크로컨트롤러에 할당된 핀들만이 각각의 마이크로컨트롤러에 의해 기록될 수 있는, 마이크로컨트롤러 디바이스. - 제 1 항 내지 제 12 항 중 어느 한 항에 있어서,

각각의 마이크로컨트롤러의 주변기기들 각각의 적어도 일부는 복수의 외부 핀들 중 소정 외부 핀들에 할당되는, 마이크로컨트롤러 디바이스. - 마이크로컨트롤러 디바이스를 동작시키는 방법으로서,

상기 마이크로컨트롤러 디바이스는,

복수의 외부 핀들;

제 1 중앙 처리 유닛(CPU), 상기 제 1 CPU와 결합된 제 1 시스템 버스, 상기 제 1 시스템 버스와 결합된 제 1 메모리, 및 상기 제 1 시스템 버스와 결합된 제 1 복수의 주변 디바이스들을 포함하는 제 1 마이크로컨트롤러; 및

제 2 중앙 처리 유닛(CPU), 상기 제 2 CPU와 결합된 제 2 시스템 버스, 상기 제 2 시스템 버스와 결합된 제 2 메모리, 및 상기 제 2 시스템 버스와 결합된 제 2 복수의 주변 디바이스들을 포함하는 제 2 마이크로컨트롤러를 포함하고,

상기 방법은 전용 인터페이스를 통해서만 상기 제 1 마이크로컨트롤러와 상기 제 2 마이크로컨트롤러 사이에 통신하는 것을 포함하는, 방법. - 제 14 항에 있어서,

상기 전용 인터페이스는 양방향 메일박스 인터페이스, 단방향 마스터-슬레이브 인터페이스 및 단방향 슬레이브-마스터 인터페이스를 포함하는, 방법. - 제 15 항에 있어서,

각각의 단방향 인터페이스는 FIFO 메모리를 포함하는, 방법. - 제 14 항 내지 제 16 항 중 어느 한 항에 있어서,

상기 제 1 마이크로컨트롤러는 마스터이고 상기 제 2 마이크로컨트롤러는 슬레이브인, 방법. - 제 14 항 내지 제 17 항 중 어느 한 항에 있어서,

상기 제 2 마이크로컨트롤러의 프로그램 메모리는 휘발성 메모리를 포함하고,

상기 방법은 상기 제 1 마이크로컨트롤러에 의해 상기 제 2 마이크로컨트롤러의 상기 프로그램 메모리에 기록하는 단계를 포함하는, 방법. - 제 14 항 내지 제 18 항 중 어느 한 항에 있어서,

상기 제 1 마이크로컨트롤러보다 빠르게 상기 제 2 마이크로컨트롤러를 클록킹하는 것을 더 포함하는 방법. - 제 14 항 내지 제 19 항 중 어느 한 항에 있어서,

상기 제 2 마이크로컨트롤러는 저전력 모드를 포함하는 전력 모드 제어 유닛을 포함하고,

상기 방법은 제 1 마이크로컨트롤러에 의해 상기 제 2 마이크로컨트롤러의 전력 모드를 제어하는 단계를 더 포함하는, 방법. - 제 14 항 내지 제 20 항 중 어느 한 항에 있어서,

상기 제 2 마이크로컨트롤러가 어떠한 전력도 소모하지 않도록, 전력 제어 모드 유닛에 의해 상기 제 2 마이크로컨트롤러를 디스에이블하는 단계를 포함하는, 방법. - 제 14 항 내지 제 21 항 중 어느 한 항에 있어서,

각각의 마이크로컨트롤러에 대한 핀 소유권을 제어하는 단계를 더 포함하고,

입/출력 핀들은 상기 제 1 마이크로컨트롤러와 상기 제 2 마이크로컨트롤러 중 어느 하나에 할당되는, 방법. - 제 14 항 내지 제 22 항 중 어느 한 항에 있어서,

각각의 마이크로컨트롤러는 임의의 판독 가능 외부 핀을 판독할 수 있지만, 상기 제 1 또는 제 2 마이크로컨트롤러에 할당된 핀들만이 각각의 마이크로컨트롤러에 의해 기록될 수 있는, 방법. - 제 14 항 내지 제 23 항 중 어느 한 항에 있어서,

상기 제 1 마이크로컨트롤러에 의해 복수의 외부 핀들 중 하나를 판독하는 단계,

상기 제 2 마이크로컨트롤러에 의해 복수의 외부 핀들 중 상기 하나를 판독하는 단계, 및

상기 전용 인터페이스에 의해 상기 복수의 외부 핀들 중 상기 하나로부터 판독된 값을 비교하는 단계를 더 포함하는, 방법.

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201562133186P | 2015-03-13 | 2015-03-13 | |

| US62/133,186 | 2015-03-13 | ||

| US15/065,027 US10002103B2 (en) | 2015-03-13 | 2016-03-09 | Low-pin microcontroller device with multiple independent microcontrollers |

| US15/065,027 | 2016-03-09 | ||

| PCT/US2016/021977 WO2016149086A2 (en) | 2015-03-13 | 2016-03-11 | Microcontroller device with multiple independent microcontrollers |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20170127420A true KR20170127420A (ko) | 2017-11-21 |

Family

ID=56888472

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177023569A KR20170127420A (ko) | 2015-03-13 | 2016-03-11 | 다수의 독립적인 마이크로컨트롤러들을 구비한 마이크로컨트롤러 디바이스 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US10002103B2 (ko) |

| EP (1) | EP3268869B1 (ko) |

| JP (1) | JP2018512662A (ko) |

| KR (1) | KR20170127420A (ko) |

| CN (1) | CN107430564B (ko) |

| TW (1) | TW201638771A (ko) |

| WO (1) | WO2016149086A2 (ko) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9921982B2 (en) * | 2014-06-05 | 2018-03-20 | Microchip Technology Incorporated | Device and method to assign device pin ownership for multi-processor core devices |

| US9921988B2 (en) * | 2014-06-05 | 2018-03-20 | Microchip Technology Incorporated | Device and method to assign device pin functionality for multi-processor core devices |

| US10002102B2 (en) * | 2015-03-13 | 2018-06-19 | Microchip Technology Incorporated | Low-pin microcontroller device with multiple independent microcontrollers |

| US10352998B2 (en) * | 2017-10-17 | 2019-07-16 | Microchip Technology Incorporated | Multi-processor core device with MBIST |

| GB201909270D0 (en) * | 2019-06-27 | 2019-08-14 | Nordic Semiconductor Asa | Microcontroller system with GPIOS |

| US11397809B2 (en) * | 2019-09-23 | 2022-07-26 | Stmicroelectronics International N.V. | Protection scheme for sensor segmentation in virtualization application |

| CN111930676B (zh) * | 2020-09-17 | 2020-12-29 | 湖北芯擎科技有限公司 | 多处理器间的通信方法、装置、系统及存储介质 |

| TWI769094B (zh) * | 2021-10-07 | 2022-06-21 | 瑞昱半導體股份有限公司 | 多晶粒封裝 |

| TWI823680B (zh) * | 2022-11-18 | 2023-11-21 | 新唐科技股份有限公司 | 資料傳輸裝置和方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6163829A (en) | 1998-04-17 | 2000-12-19 | Intelect Systems Corporation | DSP interrupt control for handling multiple interrupts |

| US6496880B1 (en) * | 1999-08-26 | 2002-12-17 | Agere Systems Inc. | Shared I/O ports for multi-core designs |

| US6615890B1 (en) | 2000-06-09 | 2003-09-09 | Venture Tape Corp. | Tape applicator for glazing applications |

| TWI358635B (en) * | 2008-02-26 | 2012-02-21 | Mstar Semiconductor Inc | Power managing method for a multi-microprocessor s |

| US8356130B2 (en) * | 2009-08-14 | 2013-01-15 | Advanced Micro Devices, Inc. | Mechanism for recording undeliverable user-level interrupts |

| CN102024170A (zh) * | 2009-09-17 | 2011-04-20 | 阿丹电子企业股份有限公司 | 单向主动式电子标签及其参数设定方法 |

| US9021284B2 (en) * | 2011-09-08 | 2015-04-28 | Infineon Technologies Ag | Standby operation with additional micro-controller |

| US9405575B2 (en) * | 2013-09-09 | 2016-08-02 | Apple Inc. | Use of multi-thread hardware for efficient sampling |

| US10002102B2 (en) * | 2015-03-13 | 2018-06-19 | Microchip Technology Incorporated | Low-pin microcontroller device with multiple independent microcontrollers |

| US10120815B2 (en) * | 2015-06-18 | 2018-11-06 | Microchip Technology Incorporated | Configurable mailbox data buffer apparatus |

-

2016

- 2016-03-09 US US15/065,027 patent/US10002103B2/en active Active

- 2016-03-11 EP EP16715158.8A patent/EP3268869B1/en active Active

- 2016-03-11 KR KR1020177023569A patent/KR20170127420A/ko unknown

- 2016-03-11 WO PCT/US2016/021977 patent/WO2016149086A2/en active Application Filing

- 2016-03-11 CN CN201680013744.4A patent/CN107430564B/zh active Active

- 2016-03-11 TW TW105107700A patent/TW201638771A/zh unknown

- 2016-03-11 JP JP2017546995A patent/JP2018512662A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US20160267047A1 (en) | 2016-09-15 |

| JP2018512662A (ja) | 2018-05-17 |

| TW201638771A (zh) | 2016-11-01 |

| CN107430564B (zh) | 2020-09-15 |

| WO2016149086A3 (en) | 2016-11-03 |

| CN107430564A (zh) | 2017-12-01 |

| EP3268869B1 (en) | 2024-12-25 |

| US10002103B2 (en) | 2018-06-19 |

| WO2016149086A2 (en) | 2016-09-22 |

| EP3268869A2 (en) | 2018-01-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10002103B2 (en) | Low-pin microcontroller device with multiple independent microcontrollers | |

| US10002102B2 (en) | Low-pin microcontroller device with multiple independent microcontrollers | |

| US11868290B2 (en) | Communication interface between host system and state machine using event slot registers | |

| US10846251B1 (en) | Scratchpad-based operating system for multi-core embedded systems | |

| US20060168429A1 (en) | Deterministic microcontroller with configurable input/output interface | |

| JP4226085B2 (ja) | マイクロプロセッサ及びマルチプロセッサシステム | |

| EP0355462B1 (en) | Dedicated service processor with inter-channel communication features | |

| Houdek et al. | Towards predictable execution model on ARM-based heterogeneous platforms | |

| US20240378171A1 (en) | Circuit architecture mapping signals to functions for state machine execution | |

| JP2007219816A (ja) | マルチプロセッサシステム | |

| CN113934516A (zh) | 一种锁管理方法、装置及设备 | |

| CN105373496B (zh) | 微型计算机 | |

| CN112306652A (zh) | 带有上下文提示的功能的唤醒和调度 | |

| US7526579B2 (en) | Configurable input/output interface for an application specific product | |

| US20140164659A1 (en) | Regulating access to slave devices | |

| US8402260B2 (en) | Data processing apparatus having address conversion circuit | |

| KR102665338B1 (ko) | 노후 평균화를 위한 부팅시 의사 랜덤 논리 대 물리 코어 할당 | |

| US20240220436A1 (en) | Supporting multiple controller circuits on a multiplexed communication bus | |

| US7680967B2 (en) | Configurable application specific standard product with configurable I/O | |

| WO2006081092A2 (en) | Deterministic microcontroller with configurable input/output interface | |

| WO2016053146A1 (ru) | Компьютерная система | |

| KR20240115575A (ko) | 컨트롤러의 클록을 제어하는 방법 및 스토리지 시스템 | |

| JP2007026184A (ja) | 機能処理電子回路およびその制御手法 | |

| US20060168421A1 (en) | Method of providing microcontroller cache memory | |

| JPS62274453A (ja) | マルチプロセツサ制御回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

Patent event date: 20170823 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PG1501 | Laying open of application | ||

| PC1203 | Withdrawal of no request for examination |