KR20130025357A - 복수의 재료에 대하여 타겟 에칭 프로세스 측정 기준을 달성하는 가스 클러스터 이온 빔 에칭 프로세스 - Google Patents

복수의 재료에 대하여 타겟 에칭 프로세스 측정 기준을 달성하는 가스 클러스터 이온 빔 에칭 프로세스 Download PDFInfo

- Publication number

- KR20130025357A KR20130025357A KR1020120096825A KR20120096825A KR20130025357A KR 20130025357 A KR20130025357 A KR 20130025357A KR 1020120096825 A KR1020120096825 A KR 1020120096825A KR 20120096825 A KR20120096825 A KR 20120096825A KR 20130025357 A KR20130025357 A KR 20130025357A

- Authority

- KR

- South Korea

- Prior art keywords

- gcib

- etching

- substrate

- gas

- etch

- Prior art date

Links

- 239000000463 material Substances 0.000 title claims abstract description 220

- 238000000034 method Methods 0.000 title claims abstract description 214

- 230000008569 process Effects 0.000 title claims abstract description 162

- 238000005530 etching Methods 0.000 title claims abstract description 140

- 238000010884 ion-beam technique Methods 0.000 title claims abstract description 16

- 239000000758 substrate Substances 0.000 claims abstract description 170

- 238000005259 measurement Methods 0.000 claims abstract description 38

- 230000003746 surface roughness Effects 0.000 claims abstract description 20

- 230000001678 irradiating effect Effects 0.000 claims abstract description 7

- 239000000203 mixture Substances 0.000 claims description 67

- 230000001133 acceleration Effects 0.000 claims description 45

- 229920002120 photoresistant polymer Polymers 0.000 claims description 40

- 238000009826 distribution Methods 0.000 claims description 29

- 229910052751 metal Inorganic materials 0.000 claims description 22

- 239000002184 metal Substances 0.000 claims description 22

- 229910052799 carbon Inorganic materials 0.000 claims description 21

- 239000004065 semiconductor Substances 0.000 claims description 20

- 229910052710 silicon Inorganic materials 0.000 claims description 20

- 229910052801 chlorine Inorganic materials 0.000 claims description 18

- 229910052736 halogen Inorganic materials 0.000 claims description 16

- 150000002367 halogens Chemical class 0.000 claims description 16

- 230000008859 change Effects 0.000 claims description 14

- 229910052731 fluorine Inorganic materials 0.000 claims description 13

- 229910052739 hydrogen Inorganic materials 0.000 claims description 13

- 230000002829 reductive effect Effects 0.000 claims description 13

- 239000010703 silicon Substances 0.000 claims description 12

- 229910052794 bromium Inorganic materials 0.000 claims description 11

- 229910052760 oxygen Inorganic materials 0.000 claims description 11

- 229910052732 germanium Inorganic materials 0.000 claims description 10

- 229910052757 nitrogen Inorganic materials 0.000 claims description 10

- 150000004820 halides Chemical class 0.000 claims description 6

- 150000004770 chalcogenides Chemical class 0.000 claims description 5

- 239000000654 additive Substances 0.000 claims 1

- 230000000996 additive effect Effects 0.000 claims 1

- 150000001875 compounds Chemical class 0.000 abstract description 16

- 230000006837 decompression Effects 0.000 abstract 4

- 102100021934 Cyclin-D1-binding protein 1 Human genes 0.000 abstract 1

- 101000897488 Homo sapiens Cyclin-D1-binding protein 1 Proteins 0.000 abstract 1

- 239000007789 gas Substances 0.000 description 165

- 239000010410 layer Substances 0.000 description 68

- 238000012545 processing Methods 0.000 description 64

- 239000000460 chlorine Substances 0.000 description 37

- 229910004298 SiO 2 Inorganic materials 0.000 description 35

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 32

- 210000004457 myocytus nodalis Anatomy 0.000 description 26

- 229910052581 Si3N4 Inorganic materials 0.000 description 25

- 230000003287 optical effect Effects 0.000 description 25

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 25

- 150000002500 ions Chemical class 0.000 description 24

- 238000005315 distribution function Methods 0.000 description 18

- 239000000377 silicon dioxide Substances 0.000 description 16

- 235000012239 silicon dioxide Nutrition 0.000 description 16

- 210000004027 cell Anatomy 0.000 description 13

- 230000007423 decrease Effects 0.000 description 13

- 230000006870 function Effects 0.000 description 13

- 230000010354 integration Effects 0.000 description 12

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 11

- 230000033001 locomotion Effects 0.000 description 11

- 238000000151 deposition Methods 0.000 description 9

- KYKAJFCTULSVSH-UHFFFAOYSA-N chloro(fluoro)methane Chemical compound F[C]Cl KYKAJFCTULSVSH-UHFFFAOYSA-N 0.000 description 8

- 238000011282 treatment Methods 0.000 description 8

- 125000004773 chlorofluoromethyl group Chemical group [H]C(F)(Cl)* 0.000 description 7

- 238000000605 extraction Methods 0.000 description 7

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 7

- 239000002585 base Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 238000005086 pumping Methods 0.000 description 6

- 229910052786 argon Inorganic materials 0.000 description 5

- 230000008021 deposition Effects 0.000 description 5

- 238000013461 design Methods 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 239000003989 dielectric material Substances 0.000 description 4

- 229910052734 helium Inorganic materials 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 230000010287 polarization Effects 0.000 description 4

- 239000000523 sample Substances 0.000 description 4

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 4

- 229910010271 silicon carbide Inorganic materials 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- 229910052717 sulfur Inorganic materials 0.000 description 4

- 229910052785 arsenic Inorganic materials 0.000 description 3

- 239000012159 carrier gas Substances 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 230000001276 controlling effect Effects 0.000 description 3

- 238000012937 correction Methods 0.000 description 3

- -1 germanium nitrides Chemical class 0.000 description 3

- 239000011261 inert gas Substances 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 229910052743 krypton Inorganic materials 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 3

- 229910052754 neon Inorganic materials 0.000 description 3

- 239000013307 optical fiber Substances 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- 229910001848 post-transition metal Inorganic materials 0.000 description 3

- 229910052723 transition metal Inorganic materials 0.000 description 3

- 150000003624 transition metals Chemical class 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 241000157282 Aesculus Species 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- 229910003321 CoFe Inorganic materials 0.000 description 2

- 229910001030 Iron–nickel alloy Inorganic materials 0.000 description 2

- 229910004166 TaN Inorganic materials 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 229910002091 carbon monoxide Inorganic materials 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 229910021419 crystalline silicon Inorganic materials 0.000 description 2

- 239000003085 diluting agent Substances 0.000 description 2

- 239000006185 dispersion Substances 0.000 description 2

- 239000010408 film Substances 0.000 description 2

- 230000004907 flux Effects 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 229910052735 hafnium Inorganic materials 0.000 description 2

- 235000010181 horse chestnut Nutrition 0.000 description 2

- 229910052740 iodine Inorganic materials 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 239000000178 monomer Substances 0.000 description 2

- 230000007935 neutral effect Effects 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910000510 noble metal Inorganic materials 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229910052761 rare earth metal Inorganic materials 0.000 description 2

- 150000002910 rare earth metals Chemical class 0.000 description 2

- 229910052711 selenium Inorganic materials 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- 229910052714 tellurium Inorganic materials 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 229910052724 xenon Inorganic materials 0.000 description 2

- 229910017083 AlN Inorganic materials 0.000 description 1

- 229910014265 BrCl Inorganic materials 0.000 description 1

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 241000282994 Cervidae Species 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- 229910005540 GaP Inorganic materials 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 229910000673 Indium arsenide Inorganic materials 0.000 description 1

- 101710112672 Probable tape measure protein Proteins 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 101710204224 Tape measure protein Proteins 0.000 description 1

- 229910010038 TiAl Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 101001015052 Zea mays Trypsin/factor XIIA inhibitor Proteins 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 1

- CODNYICXDISAEA-UHFFFAOYSA-N bromine monochloride Chemical compound BrCl CODNYICXDISAEA-UHFFFAOYSA-N 0.000 description 1

- 229910052793 cadmium Inorganic materials 0.000 description 1

- 150000001768 cations Chemical class 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000005108 dry cleaning Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000010292 electrical insulation Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000013213 extrapolation Methods 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 239000007792 gaseous phase Substances 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000002784 hot electron Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- RPQDHPTXJYYUPQ-UHFFFAOYSA-N indium arsenide Chemical compound [In]#[As] RPQDHPTXJYYUPQ-UHFFFAOYSA-N 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 150000001247 metal acetylides Chemical class 0.000 description 1

- 229910001092 metal group alloy Inorganic materials 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910052976 metal sulfide Inorganic materials 0.000 description 1

- 238000001465 metallisation Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000037361 pathway Effects 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 239000012071 phase Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 239000000376 reactant Substances 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- 150000004771 selenides Chemical class 0.000 description 1

- SBIBMFFZSBJNJF-UHFFFAOYSA-N selenium;zinc Chemical compound [Se]=[Zn] SBIBMFFZSBJNJF-UHFFFAOYSA-N 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 241000894007 species Species 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 150000004763 sulfides Chemical class 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 150000004772 tellurides Chemical class 0.000 description 1

- 238000012549 training Methods 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

- 238000004846 x-ray emission Methods 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/3065—Plasma etching; Reactive-ion etching

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23F—NON-MECHANICAL REMOVAL OF METALLIC MATERIAL FROM SURFACE; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL; MULTI-STEP PROCESSES FOR SURFACE TREATMENT OF METALLIC MATERIAL INVOLVING AT LEAST ONE PROCESS PROVIDED FOR IN CLASS C23 AND AT LEAST ONE PROCESS COVERED BY SUBCLASS C21D OR C22F OR CLASS C25

- C23F4/00—Processes for removing metallic material from surfaces, not provided for in group C23F1/00 or C23F3/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

- H01L21/31122—Etching inorganic layers by chemical means by dry-etching of layers not containing Si, e.g. PZT, Al2O3

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31127—Etching organic layers

- H01L21/31133—Etching organic layers by chemical means

- H01L21/31138—Etching organic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32133—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only

- H01L21/32135—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only

- H01L21/32136—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only using plasmas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32133—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only

- H01L21/32135—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only

- H01L21/32136—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only using plasmas

- H01L21/32137—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only using plasmas of silicon-containing layers

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Plasma & Fusion (AREA)

- Inorganic Chemistry (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Drying Of Semiconductors (AREA)

Abstract

본원에는 다양한 재료의 가스 클러스터 이온 빔(GCIB) 에칭 처리를 실행하는 방법 및 시스템이 기재되어 있다. 특히, GCIB 에칭 처리는, 하나 이상의 타겟 에칭 프로세스 측정 기준을 달성하도록, GCIB에 대하여 GCIB 프로세스 조건의 하나 이상의 GCIB 특성을 세팅하는 것을 포함한다.

Description

본 발명은 가스 클러스터 이온 빔(GCIB) 처리에 관한 것이다.

통상적으로, 집적 회로(IC)의 제조 과정에서, 반도체 생산 설비는, 반도체 기판 상에 패터닝된 비아 또는 컨택트 내에서 혹은 세선(細線)을 따라 재료를 제거 혹은 에칭하는 데 (드라이) 플라즈마 에칭 프로세스를 이용한다. 플라즈마 에칭 프로세스가 성공하려면, 하나의 재료를 선택적으로 에칭하면서 다른 재료를 실질적으로 더 낮은 비율로 에칭하기에 적합한 화학 반응물을 에칭 케미스트리가 가질 필요가 있다. 또한, 플라즈마 에칭 프로세스가 성공하려면, 에칭 프로세스를 기판에 균일하게 적용하는 상태에서, 만족스러운 프로파일 제어를 달성 가능한 것이 요구된다.

현재의 IC 소자에서, Si-함유 및 Ge-함유 재료는 반도체 처리에서 주축이 되고 있다. 그러나, IC 소자의 다양한 전기 특성을 향상시키기 위해, 보다 이색적인 재료가 또한 반도체 처리에 도입되고 있다. 예를 들어, FEOL(front-end-of-line) 반도체 처리에서는, 고유전상수(high-k) 재료가 트랜지스터 게이트 유전체로서 사용하기에 바람직하다. 이러한 역할에 사용되던 초기의 고유전상수 재료로는 산화탄탈륨 및 산화알루미늄 재료가 있었다. 현재에는, 하프늄계 유전체와 가능하다면 란타늄계 유전체가 게이트 유전체로서 생산에 들어갈 것으로 예상된다. 또한, FEOL 반도체 처리에서는, 금속 함유 재료가 다음 세대의 전자 디바이스에서의 트랜지스터 게이트 전극으로서 사용하기에 바람직하다. 현재, Ti, Ta, 및/또는 Ar(예컨대, TiN, TaN, Al2O3 및 TiAl)를 함유한 금속 전극이 금속 전극으로서 생산에 들어갈 것으로 예상된다. 물론, 반도체 처리에의 새로운 재료의 도입은, FEOL 작업에만 국한되는 것이라, BEOL(back-end-of-line) 작업에서의 금속 배선 프로세스의 추세이기도 하다. 또한, 진보된 메모리 디바이스에서, Fe, Co, Ni 및 그 합금 뿐만 아니라 귀금속을 비롯한 새롭고 이색적인 재료가 사용 및 도입되고 있다.

전자 디바이스 처리에서 현재의 재료와 전술한 새롭게 출연된 재료를 이용함에 따라, 기존의 층 및/또는 구조의 무결성을 유지하면서 상기 현재의 재료와 새로운 재료를 에칭하는 성능이, 강력한 도전에 직면하게 되고 있다. 종래의 에칭 프로세스는, 상기한 재료의 실용 에칭률을 달성하지 못하거나, 하위 혹은 상위 재료에 대하여 만족스러운 에칭 선택비를 획득하지 못한다. 또한, 종래의 에칭 프로세스는, 기판에 걸쳐 균일하게 적용되는 만족스러운 프로파일 제어를 달성하지 못한다.

본 발명의 실시형태는 GCIB 처리에 관한 것이다. 특히, 본 발명의 실시형태는 GCIB 에칭 처리에 관한 것이다. 또한, 본 발명의 실시형태는 타겟 에칭 프로세스 측정 기준을 달성하는 다양한 재료의 GCIB 에칭 처리에 관한 것이다.

일 실시형태에 따라, 기판 상의 재료를 에칭하는 방법을 기술한다. 이 방법은, 표면을 갖는 기판을 유지하는 기판 홀더 주변에 감압 환경을 유지하는 단계와, 기판을 상기 감압 환경 내에 확실히 유지시키는 단계를 포함한다. 이 방법은 또한, 제1 재료의 에칭률, 제2 재료의 에칭률, 제1 재료와 제2 재료 사이의 에칭 선택비, 제1 재료의 표면 거칠기, 제2 재료의 표면 거칠기, 제1 재료의 에칭 프로파일 및 제2 재료의 에칭 프로파일을 포함하는 하나 이상의 타겟 에칭 프로세스 측정 기준을 선택하는 단계; 적어도 하나의 에칭 가스를 함유하는 가압 가스로부터 가스 클러스터 이온 빔(GCIB)을 형성하는 단계; 상기 하나 이상의 타겟 에칭 프로세스 측정 기준을 달성하도록, GCIB에 대하여 GCIB 프로세스 조건의 하나 이상의 GCIB 특성을 세팅하는 단계; 감압 환경을 통해 GCIB을 가속시키는 단계; 및 제1 재료와 제2 재료 중 적어도 하나를 에칭하도록, 기판의 표면의 적어도 일부분에 GCIB을 조사하는 단계를 포함한다.

본 발명에 따른 다양한 재료의 가스 클러스터 이온 빔(GCIB) 에칭 처리를 실행하는 방법 및 시스템은, GCIB에 대하여 GCIB 프로세스 조건의 하나 이상의 GCIB 특성을 세팅함으로써, 하나 이상의 타겟 에칭 프로세스 측정 기준을 달성한다.

도 1은 일 실시형태에 따라 기판을 에칭하는 방법을 예시하는 흐름도이다.

도 2a 내지 도 2c는 다른 실시형태에 따라 기판을 에칭하는 방법을 예시하는 모식도이다.

도 3a는 GCIB에 대한 빔 에너지 분포 함수를 개략적으로 예시하는 그래프이다.

도 3b는 GCIB에 대한 빔 각도 분포 함수를 개략적으로 예시하는 그래프이다.

도 4a 내지 도 4l은 기판 상에서의 재료 에칭에 관한 예시적인 데이터를 보여주는 그래프이다.

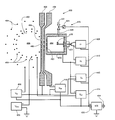

도 5는 GCIB 처리 시스템을 예시하는 도면이다.

도 6은 GCIB 처리 시스템을 예시하는 다른 도면이다.

도 7은 GCIB 처리 시스템을 예시하는 또 다른 도면이다.

도 8은 GCIB 처리 시스템에 대한 이온화원을 예시하는 도면이다.

도 9는 GCIB 처리 시스템에 대한 다른 이온화원을 예시하는 도면이다.

도 2a 내지 도 2c는 다른 실시형태에 따라 기판을 에칭하는 방법을 예시하는 모식도이다.

도 3a는 GCIB에 대한 빔 에너지 분포 함수를 개략적으로 예시하는 그래프이다.

도 3b는 GCIB에 대한 빔 각도 분포 함수를 개략적으로 예시하는 그래프이다.

도 4a 내지 도 4l은 기판 상에서의 재료 에칭에 관한 예시적인 데이터를 보여주는 그래프이다.

도 5는 GCIB 처리 시스템을 예시하는 도면이다.

도 6은 GCIB 처리 시스템을 예시하는 다른 도면이다.

도 7은 GCIB 처리 시스템을 예시하는 또 다른 도면이다.

도 8은 GCIB 처리 시스템에 대한 이온화원을 예시하는 도면이다.

도 9는 GCIB 처리 시스템에 대한 다른 이온화원을 예시하는 도면이다.

가스 클러스터 이온 빔(GCIB) 처리를 이용하여 기판 상에서 실리콘-함유층, Ge-함유층, 금속-함유층 및 반도체층을 에칭하는 방법을, 여러 실시형태에 기술한다. 당업자는, 다양한 실시형태가 하나 이상의 특정한 세부 사항을 갖지 않고서 실시될 수도 있고, 또는 다른 대체물 및/또는 추가적인 방법, 물질, 또는 구성 요소를 갖고서 실시될 수도 있다는 것을 인지할 것이다. 다른 경우에 있어서는, 본 발명의 다양한 실시형태의 양태가 모호해지는 것을 피하기 위해, 공지의 구조, 재료, 또는 작업은 상세히 도시 혹은 설명되어 있지 않다. 이와 마찬가지로, 본 발명을 완전하게 이해시키기 위해, 구체적인 수, 재료 및 구성이 설명을 목적으로 기재되어 있다. 그렇지만, 본 발명은 구체적인 세부 사항 없이 실시될 수 있다. 또한, 도면에 도시된 여러 실시형태는 예시적인 대표예이며 일정한 비례로 도시될 필요가 없는 것으로 이해된다.

본 명세서의 전반의 어구 "일 실시형태" 또는 "실시형태"는, 실시형태와 연계되어 설명되는 개개의 피처, 구조, 재료, 또는 특징이 본 발명의 적어도 하나의 실시형태에 포함된다는 것을 의미하지만, 이들이 모든 실시형태에 존재한다는 것을 의미하지는 않는다. 따라서, 본 명세서의 전반의 여러 곳에 나타나 있는 어구 "일 실시형태에서" 또는 "실시형태에서"는, 본 발명의 동일한 실시형태를 거론하는 것은 아니다. 또한, 특징부, 구조, 재료, 또는 특성은 하나 이상의 실시형태에서 임의의 적절한 방식으로 조합될 수 있다. 다른 실시예에서는, 다양한 추가 층 및/또는 구조가 포함될 수 있거나 및/또는 기술된 특징이 생략될 수 있다.

본원에 사용되고 있는 바와 같이 "기판"은 일반적으로 본 발명에 따라 처리되는 대상물을 지칭한다. 기판은 디바이스, 특히 반도체 또는 그 밖의 전자 디바이스의 임의의 재료 부분 또는 구조를 포함할 수 있고, 예를 들어 반도체 웨이퍼 등의 베이스 기판 구조, 또는 베이스 기판 구조에 혹은 그 위에 놓이는 박막 등의 층일 수도 있다. 따라서, 기판은 임의의 특정 베이스 구조, 상위층 혹은 하위층, 패터닝된 혹은 패터닝되지 않은 구조에 국한되는 의미를 갖는 것이 아니라, 임의의 상기 층 혹은 베이스 구조와, 층 및/또는 베이스 구조의 임의의 조합을 포함하는 것으로 고려된다. 이하의 설명은 특정 타입의 기판을 참조로 하지만, 이는 단지 예시를 하기 위함이며 한정의 의도는 없다.

앞에서 부분적으로 설명한 바와 같이, 에칭률, 에칭 선택비, CD(임계 치수) 제어를 비롯한 프로파일 제어, 및 표면 거칠기는, 다른 프로세스 결과들보다, 성공적인 패턴 에칭을 결정하는 데 필수적인 측정 기준을 제공한다. 예로서, 피처 패턴(feature pattern)을 기판 상의 재료층에 전사하는 경우에는, 패턴 프로파일과 패턴 표면 및 인접 표면의 표면 거칠기를 제어하면서, 적절한 프로세스 처리량을 얻기에 충분한 비율로 하나의 재료를 선택적으로 에칭하는 것이 중요하다. 또한, 기판 상의 재료층에 형성된 모든 피처 패턴에 대하여 에칭률, 에칭 선택비 및 에칭 프로파일을 균일하게 제어하는 것, 및/또는 기판 상의 재료층에 형성된 피처 패턴에 대한 상기 파라미터의 제어를 공간적으로 조정하는 것이 중요하다.

따라서, 여러 실시형태에 따라, 기판 상의 재료, 예컨대 Si-함유 재료, Ge-함유 재료, 금속-함유 재료, 반도체 재료, 및/또는 칼코게나이드 재료 등을 에칭하는 방법을 설명한다. 이제 몇몇 도면에 걸쳐서 유사한 도면부호가 대응 부분을 표시하고 있는 도면을 참조해 보면, 도 1은 일 실시형태에 따라 기판 상의 여러 재료를 에칭하는 방법을 예시하는 흐름도(1)를 제공한다. 또한, 예시적인 기판 에칭 방법이 도 2a 및 도 2b에 도식적으로 묘사되어 있다.

흐름도(1)에 예시된 방법은, 가스 클러스터 이온 빔(GCIB) 처리 시스템에서 기판(22)을 유지하는 기판 홀더 주변에 감압 환경을 유지하는 단계(10)로 시작된다. 기판(22)은 제1 재료와, 제2 재료, 그리고 제1 재료 및/또는 제2 재료를 노출시키는 표면을 포함할 수 있다. GCIB 처리 시스템은 도 5, 도 6 또는 도 7에서 후술하는 GCIB 처리 시스템(100, 100', 또는 100") 중 어느 하나 또는 이들의 임의의 조합을 포함할 수 있다.

도 2a에 예시된 바와 같이, 기판(22)의 적어도 일부분(20)의 위에 놓이는 재료층(24)이 GCIB(25)를 사용하여 에칭될 수 있다. 예로서, 제1 재료는 재료층(24)을 포함할 수 있고, 제2 재료는 기판(22)을 포함할 수 있다. 제1 재료 및/또는 제2 재료를 노출시키는 표면은, 재료층(24)의 에칭 과정에서의 재료층(24)의 상면을 포함할 수 있고, 또는 일단 재료층(24)에서 에칭이 진행되었을 때의 재료층(24)과 기판(22) 사이의 계면을 포함할 수 있다.

별법으로서, 도 2b에 예시된 바와 같이, 기판(22)의 적어도 일부분(20')의 위에 놓이는 재료층(24')은, 마스크층(26)에 형성된 제1 패턴(27)을 재료층(24')에 전사하여 이 재료층에 제2 패턴(28)을 생성하도록, GCIB(25')를 이용하여 에칭될 수 있다. 예로서, 제1 재료는 마스크층(26)을 포함할 수 있고, 제2 재료는 재료층(24')을 포함할 수 있다. 제1 재료 및/또는 제2 재료를 노출시키는 표면은, 마스크층(26)의 노출 표면과 재료층(24')의 노출 표면을 포함할 수 있다.

도 2b에 예시된 바와 같이, 제1 패턴(27)이 형성되어 있는 마스크층(26)은 재료층(24')에 혹은 그 위에 마련된다. 마스크층(26)은 기판(22)을 포토레지스트 등의 방사선 감수성 재료의 층으로 피복함으로써 형성될 수 있다. 예를 들어, 포토레지스트는 스핀 코팅 기술, 예컨대 트랙 시스템에 의해 가능해지는 프로세스를 이용하여 기판에 도포될 수 있다. 또한, 예를 들어 포토레지스트를 리소그래피 시스템을 이용하여 화상 패턴에 노출시키고, 그 후에 이 화상 패턴을 현상액에서 현상시켜 포토레지스트층에 패턴을 형성한다.

포토레지스트층은 248 ㎚(나노미터) 레지스트, 193 ㎚ 레지스트, 157 ㎚ 레지스트 또는 EUV(극자외선) 레지스트를 포함할 수 있다. 포토레지스트층은 트랙 시스템을 이용하여 형성될 수 있다. 예를 들어, 트랙 시스템은 도쿄 엘렉트론 가부시키가이샤(TEL)에서 시판한 CLEAN TRACK ACT 8, ACT 12, 또는 LITHIUS 레지스트 코팅 및 현상 시스템을 포함할 수 있다. 기판 상에 포토레지스트 막을 형성하기 위한 다른 시스템 및 방법은, 스핀 온 레지스트 기술 분야의 당업자에게 잘 알려져 있다.

전자기(EM)선의 패턴에 대한 노출은 드라이 또는 웨트 포토-리소그래피 시스템에서 행해질 수 있다. 상기 화상 패턴은 임의의 적절한 종래의 스테핑 리소그래픽 시스템 또는 스캐닝 리소그래픽 시스템을 이용하여 형성될 수 있다. 예를 들어, 포토-리소그래피 시스템은 ASML Netherlands B.V.(네덜란드 5504 데에르 벨트호벤 드 런 6501 소재) 또는 Canon USA, Inc., Semiconductor Equipment Division(미국 캘리포니아주 95134 산 호세 3300 노쓰 퍼스트 스트리트 소재)에서 시판하고 있다.

현상 프로세스는 트랙 시스템 등의 현상 시스템에서 기판을 현상액에 노출시키는 것을 포함할 수 있다. 예를 들어, 트랙 시스템은 도쿄 엘렉트론 가부시키가이샤(TEL)에서 시판한 CLEAN TRACK ACT 8, ACT 12, 또는 LITHIUS 레지스트 코팅 및 현상 시스템을 포함할 수 있다.

포토레지스트층은 웨트 스트리핑 프로세스, 드라이 플라즈마 애싱 프로세스, 또는 드라이 비(非)플라즈마 애싱 프로세스를 이용하여 제거될 수 있다.

마스크층(26)은 복수의 층을 포함할 수 있고, 이 경우 마스크층(26)에 형성된 제1 패턴(27)은 습식 처리 기술, 건식 처리 기술, 또는 두 기술의 조합을 이용하여 형성될 수 있다. 이러한 단일 층 또는 복수의 층을 갖는 마스크층(26)의 형성은, 리소그래피 및 패턴 에칭 기술 분야의 당업자에게 알려져 있다. 일단 제1 패턴(27)이 마스크층(26)에 형성되면, 마스크층(26)은 하위층을 패터닝하는 데 이용될 수 있다.

또한, 별법으로서 도 2c에 예시된 바와 같이, 기판(22)의 적어도 일부분(20")의 위에 놓이는 제1 재료층(24") 및 제2 재료층(24"')을 GCIB(25")를 이용하여 에칭하여, 예컨대 제1 재료층(24") 및 제2 재료층(24"')을 평탄화할 수도 있다. 예로서, 제1 재료는 제1 재료층(24")을 포함할 수 있고, 제2 재료는 제2 재료층(24"')을 포함할 수 있다. 제1 재료 및/또는 제2 재료를 노출시키는 표면은, 제1 재료층(24")의 노출 표면과 제2 재료층(24"')의 노출 표면을 포함할 수 있다.

상기 방법은 GCIB 처리 시스템의 감압 환경 내에 기판(22)을 확실하게 유지시키는 단계(11)로 진행된다. 기판(22)의 온도는 제어될 수도 있고, 또는 제어되지 않을 수도 있다. 예를 들어, 기판(22)은 GCIB 처리 프로세스 과정에서 가열 또는 냉각될 수 있다. 또한, 기판(22)은 도체 재료, 반도체 재료, 또는 유전체 재료, 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다. 예를 들어, 기판(22)은 실리콘, SOI(Silicon-on-insulator), 게르마늄, 또는 이들의 조합 등의 반도체 재료를 포함할 수 있다. 또한, 기판(22)은 예를 들어 결정 실리콘을 포함할 수 있다.

또한, 기판(22)은 기판(22)의 일부분(20, 20', 20") 상에 제1 및/또는 제2 재료층(24, 24', 24", 24"', 26)을 포함할 수 있다. 제1 및/또는 제2 재료층(24, 24', 24", 24"', 26)은 Si-함유 재료 및/또는 Ge-함유 재료를 포함할 수 있다. 상기 Si-함유 재료는 Si와 O, N, C 및 Ge로 이루어진 군에서 선택된 적어도 하나의 원소를 포함할 수 있다. 상기 Ge-함유 재료는 Ge와 O, N, C 및 Si로 이루어진 군에서 선택된 적어도 하나의 원소를 포함할 수 있다.

예를 들어, 제1 및/또는 제2 재료층(24, 24', 24", 24"', 26)은 실리콘, 도프된 실리콘, 언도프된 실리콘, 비정질 실리콘, 단결정 실리콘, 다결정 실리콘, 산화실리콘(SiOx, 여기서 x>0; 예컨대 SiO2), 질화실리콘(SiNy, 여기서 y>0; 예컨대 SiN1 .33 또는 Si3N4), 탄화규소(SiCz, 여기서 z>0), 산질화규소(SiOxNy, 여기서 x, y>0), 옥시탄화규소(SiOxCy, 여기서 x, y>0), 탄질화규소(SiCxNy, 여기서 x, y>0), 또는 실리콘-게르마늄(SixGe1 -x, 여기서 x는 Si의 원자분율이고, 1-x는 Ge의 원자분율임, 0<1-x<1)을 포함할 수 있다. 앞서 열거한 재료 중 어느 하나에는, B, C, H, N, P, As, Sb, O, S, Se, Te, F, Cl, Br 및 I로 이루어진 군에서 선택된 원소가 도프 또는 주입될 수 있다. 또한, 앞서 열거한 재료 중 어느 하나에는, 금속, 알칼리 금속, 알칼리 토류 금속, 희토류 금속, 전이 금속, 또는 전이후 금속이 도프 또는 주입될 수 있다. 또한, 앞서 열거한 재료 중 어느 하나는 비정질상 또는 결정상일 수 있다.

또한, 제1 및/또는 제2 재료층(24, 24', 24", 24"', 26)은 금속-함유 재료를 포함할 수 있다. 상기 금속-함유 재료는 알칼리 금속, 알칼리 토류 금속, 전이 금속, 전이후 금속, 귀금속, 또는 희토류 금속을 포함할 수 있다. 상기 금속-함유 재료는 Sc, Y, Zr, Hf, Nb, Ta, V, Cr, Mo, W, Mn, Re, Fe, Ru, Co, Rh, Ni, Pd, Pt, Cu, Ag, Au, Zn, Cd, B, Al, Ga, In 및 Sn으로 이루어진 군에서 선택된 전이 금속 또는 전이후 금속을 포함할 수 있다. 상기 금속-함유 재료는 금속, 금속 합금, 금속 산화물, 금속 질화물, 금속 탄화물, 금속 규화물, 금속 게르마늄화물, 금속 황화물 등을 포함할 수 있다.

또한, 제1 및/또는 제2 재료층(24, 24', 24", 24"', 26)은 반도체 재료도 포함할 수 있다. 상기 반도체 재료는 Ⅲ-V족 화합물(예컨대, GaAs, GaN, GaP, InAs, InN, InP 등), Ⅱ-V족 화합물(예컨대, Cd3P2 등), 또는 Ⅱ-Ⅵ족 화합물(예컨대, ZnO, ZnSe, ZnS 등)(Ⅱ, Ⅲ, V, Ⅵ족은 원소주기율표에서의 전통적인 혹은 구식의 IUPAC 표기법과 관련이 있다; 개정된 혹은 신식의 IUPAC 표기법에 따르면, 상기한 족은 각각 2, 13, 15, 16족을 지칭한다) 등의 화합물 반도체를 포함할 수 있다. 또한, 재료층(24, 24')은 칼코게나이드(예컨대, 황화물, 셀렌화물, 텔루르화물)를 포함할 수 있다.

또한, 제1 및/또는 제2 재료층(24, 24', 24", 24"', 26)은 포토레지스트(예컨대, 앞서 열거한 레지스트 재료 중 하나), 소프트 마스크층, 하드 마스크층, 반사방지 코팅(ARC)층, 유기 평탄화층(OPL), 또는 유기 유전체층(ODL), 또는 이들 중 2 이상의 조합을 포함할 수 있다.

한 예에서, 제1 재료는 포토레지스트를 포함하고, 제2 재료는 Si-함유 재료, Ge-함유 재료, 금속-함유 재료, 반도체 재료, 또는 칼코게나이드 재료를 포함한다. 다른 예에서, 제1 재료는 실리콘을 포함하고, 제2 재료는 Si와 O, N, C 및 Ge로 이루어진 군에서 선택된 하나 이상의 원소를 갖는 Si-함유 재료를 포함한다. 실리콘은 도프된 Si, 언도프된 Si, 결정 Si, 비정질 Si, 단결정 Si(혹은 단일 결정 Si), 다결정 Si 등을 포함할 수 있다. 다른 예에서, 제1 재료는 Si-함유 재료를 포함하고, 제2 재료는 Ge-함유 재료를 포함한다. 또 다른 예에서, 제1 재료는 Si-함유 재료를 포함하고, 제2 재료는 금속-함유 재료를 포함한다.

단계 12에서는, 하나 이상의 타겟 에칭 프로세스가 선택된다. 앞에서 언급하였고 뒤에서 좀 더 세밀하게 거론되는 바와 같이, 타겟 에칭 프로세스 측정 기준은 제1 재료의 에칭률, 제2 재료의 에칭률, 제1 재료와 제2 재료 사이의 에칭 선택비, 제1 재료의 표면 거칠기, 제2 재료의 표면 거칠기, 제1 재료의 에칭 프로파일 및 제2 재료의 에칭 프로파일을 포함할 수 있다.

단계 13에서는, 적어도 하나의 에칭 가스를 함유하는 가압 가스 혼합물로부터 가스 클러스터 이온 빔(GCIB)이 형성된다. 상기 적어도 하나의 에칭 가스는 할로겐 원소를 포함할 수 있다. 상기 적어도 하나의 에칭 가스는 할로겐 원소와 C, H, N 및 S로 이루어진 군에서 선택된 하나 이상의 원소를 포함할 수 있다.

예를 들어, 상기 적어도 하나의 에칭 가스는 F2, Cl2, Br2, NF3 또는 SF6을 포함할 수 있다. 또한, 예를 들어 상기 적어도 하나의 에칭 가스는 HF, HCl, HBr, 또는 HI 등의 할로겐화물을 포함할 수 있다. 또한, 예를 들어 상기 적어도 하나의 에칭 가스는, 단일 치환 할로메탄(예컨대, CH3F, CH3Cl, CH3Br, CH3I), 2치환 할로메탄(예컨대, CH2F2, CH2ClF, CH2BrF, CH2FI, CH2Cl2, CH2BrCl, CH2ClI, CH2Br2, CH2BrI, CH2I2), 3치환 할로메탄(예컨대, CHF3, CHClF2, CHBrF2, CHF2I, CHCl2F, CHBrClF, CHClFI, CHBr2F, CHBrFI, CHFI2, CHCl3, CHBrCl2, CHCl2I, CHBr2Cl, CHBrClI, CHClI2, CHBr3, CHBr2I, CHBrI2, CHI3), 또는 4치환 할로메탄(예컨대, CF4, CClF3, CBrF3, CF3I, CCl2F2, CBrClF2, CClF2I, CBr2F2, CBrF2I, CF2I2, CCl3F, CBrCl2F, CCl2FI, CBr2ClF, CBrClFI, CClFI2, CBr3F, CBr2FI, CBrFI2, CFI3, CCl4, CBrCl3, CCl3I, CBr2Cl2, CBrCl2I, CCl2I2, CBr3Cl, CBr2ClI, CBrClI2, CClI3, CBr4, CBr3I, CBr2I2, CBrI3, Cl4) 등의 할로메탄을 포함할 수 있다.

GCIB를 형성하려면, 비교적 높은 압력(예컨대, 1 대기압 이상)에서 단독 혹은 캐리어 가스(예컨대, 희가스 원소 또는 질소)와 함께 기상으로 존재하는 에칭 가스의 성분이 선택되어야 한다.

일 실시형태에서, Si-함유 및/또는 Ge-함유 재료를 에칭하는 경우, 상기 적어도 하나의 에칭 가스는 F, Cl 및 Br로 이루어진 군에서 선택된 할로겐 원소를 포함한다. 상기 적어도 하나의 에칭 가스는 C와 H 중 어느 하나 또는 양자 모두를 더 포함할 수 있다. 예를 들어, 상기 적어도 하나의 에칭 가스는 할로겐화물 또는 할로메탄을 포함할 수 있다. 또한, 예를 들어, 상기 적어도 하나의 에칭 가스는 SF6, NF3, F2, Cl2, Br2, HF, HCl, HBr, CClF3, CBrF3, CHClF2, 또는 C2ClF5, 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다.

다른 실시형태에서, Si-함유 및/또는 Ge-함유 재료를 에칭하는 경우, 상기 적어도 하나의 에칭 가스는 서로 다른 두 할로겐 원소를 포함한다. 제1 할로겐 원소는 Cl 및 Br로 이루어진 군에서 선택될 수 있고, 제2 할로겐 원소는 F를 포함할 수 있다. 상기 적어도 하나의 에칭 가스는 C와 H 중 어느 하나 또는 양자 모두를 더 포함할 수 있다. 예를 들어, 상기 적어도 하나의 에칭 가스는 할로메탄을 포함할 수 있다. 또한, 예를 들어, 상기 적어도 하나의 에칭 가스는 CClF3, CBrF3, CHClF2, 또는 C2ClF5, 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다.

다른 실시형태에서, Si와 O, N, C 및 Ge로 이루어진 군에서 선택된 하나 이상의 원소를 갖는 Si-함유 재료를 에칭하는 경우, 상기 적어도 하나의 에칭 가스는 C, H 및 할로겐 원소를 포함한다. 예를 들어, 에칭 가스는 할로메탄을 포함할 수 있다. 또한, 예를 들어 에칭 가스는 CH3F, CH3Cl, CH3Br, CHF3, CHClF2, CHBrF2, CH2F2, CH2ClF, CH2BrF, CHCl2F, CHBr2F, CHCl3, CHBrCl2, CHBr2Cl, 또는 CHBr3, 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다.

다른 실시형태에서, 금속 함유 재료를 에칭하는 경우, 에칭 가스는 F, Cl 및 Br로 이루어진 군에서 선택된 할로겐 원소를 포함한다. 상기 에칭 가스는 C와 H 중 어느 하나 또는 양자 모두를 더 포함할 수 있다. 예를 들어, 상기 에칭 가스는 할로겐화물 또는 할로메탄을 포함할 수 있다. 또한, 예를 들어, 상기 에칭 가스는 SF6, NF3, F2, Cl2, Br2, HF, HCl, HBr, CClF3, CBrF3, CHClF2, 또는 C2ClF5, 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다.

다른 실시형태에서, 금속 함유 재료를 에칭하는 경우, 상기 에칭 가스는 서로 다른 두 할로겐 원소를 포함한다. 제1 할로겐 원소는 Cl 및 Br로 이루어진 군에서 선택될 수 있고, 제2 할로겐 원소는 F를 포함할 수 있다. 상기 에칭 가스는 C와 H 중 어느 하나 또는 양자 모두를 더 포함할 수 있다. 예를 들어, 상기 에칭 가스는 할로메탄을 포함할 수 있다. 또한, 예를 들어, 상기 에칭 가스는 CClF3, CBrF3, CHClF2, 또는 C2ClF5, 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다.

또 다른 실시형태에서, 칼코게나이드 재료를 에칭하는 경우, 에칭 가스는 할로겐 원소를 포함한다. 예를 들어, 상기 에칭 가스는 할로겐화물 또는 할로메탄을 포함할 수 있다. 또한, 예를 들어 에칭 가스는 F2, Cl2, Br2, HF, HCl, HBr, NF3, SF6, CH3F, CH3Cl, CH3Br, CHF3, CHClF2, CHBrF2, CH2F2, CH2ClF, CH2BrF, CHCl2F, CHBr2F, CHCl3, CHBrCl2, CHBr2Cl, 또는 CHBr3, 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다.

적어도 하나의 에칭 가스는 제1 에칭 가스와 제2 에칭 가스를 포함할 수 있다. 일 실시형태에서, 제1 에칭 가스는 Cl 또는 Br을 함유하고, 제2 에칭 가스는 F를 함유한다. 예를 들어, 제1 에칭 가스는 Cl2를 함유할 수 있고, 제2 에칭 가스는 NF3를 함유할 수 있다. 다른 실시형태에서, 제1 에칭 가스는 할로메탄 또는 할로겐화물을 함유하고, 제2 에칭 가스는 F, Cl, 또는 Br을 함유한다. 다른 실시형태에서, 제1 에칭 가스는 C, H 및 할로겐 원소를 함유하고, 제2 에칭 가스는 F, Cl, 또는 Br을 함유한다. 예를 들어, 제1 에칭 가스는 CHF3, CHCl3, 또는 CHBr3를 함유할 수 있고, 제2 에칭 가스는 NF3 또는 Cl2를 함유할 수 있다. 제1 에칭 가스와 제2 에칭 가스는 GCIB에 연속적으로 도입될 수 있다. 별법으로서, 제1 에칭 가스와 제2 에칭 가스는 GCIB에 번갈아 순차적으로 도입될 수 있다.

가압 가스 혼합물은 할로겐 원소를 함유하는 화합물; F 및 C를 함유하는 화합물; H 및 C를 함유하는 화합물; 또는 C, H 및 F를 함유하는 화합물, 또는 이들 중 2 이상의 임의의 조합을 더 포함할 수 있다. 또한, 가압 가스 혼합물은 염소-함유 화합물, 불소-함유 화합물, 또는 브롬-함유 화합물을 더 포함할 수 있다. 또한, 가압 가스 혼합물은 C, F, H, Cl 및 Br로 이루어진 군에서 선택된 하나 이상의 원소를 함유하는 화합물을 더 포함할 수 있다. 또한, 가압 가스 혼합물은 실리콘-함유 화합물, 게르마늄-함유 화합물, 질소-함유 화합물, 산소-함유 화합물, 또는 탄소-함유 화합물, 또는 이들 중 2 이상의 임의의 조합을 더 포함할 수 있다. 또한, 가압 가스 혼합물은 B, C, H, Si, Ge, N, P, As, O, S, F, Cl 및 Br로 이루어진 군에서 선택된 하나 이상의 원소를 더 포함할 수 있다. 또한, 가압 가스 혼합물은 He, Ne, Ar, Kr, Xe, O2, CO, CO2, N2, NO, NO2, N2O, NH3, F2, HF, SF6, 또는 NF3, 또는 이들 중 2 이상의 임의의 조합을 더 포함할 수 있다.

더 나아가, GCIB는, 적어도 하나의 도펀트, 또는 박막을 증착 혹은 성장시키기 위한 성막 성분, 또는 이들 중 2 이상의 임의의 조합을 포함하는 가압 가스 혼합물로부터 생성될 수 있다.

다른 실시형태에서, GCIB는 에칭 가스를 함유하는 제1 가압 가스 혼합물과 성막 가스를 함유하는 제2 가압 가스 혼합물을 번갈아 순차적으로 사용함으로써 생성될 수 있다. 또 다른 실시형태에서, GCIB의 조성 및/또는 정체 압력은 에칭 동안에 조정될 수 있다.

단계 14에서는, 하나 이상의 타겟 에칭 프로세스 측정 기준을 달성하도록, GCIB에 대하여 GCIB 프로세스 조건의 하나 이상의 GCIB 특성을 세팅한다. 앞서 언급한 타겟 에칭 프로세스 측정 기준, 예컨대 에칭률, 에칭 선택비, 표면 거칠기 제어, 프로파일 제어 등을 달성하기 위해, GCIB는, 빔 가속 전위, 하나 이상의 빔 초점 전위 및 빔 조사량을 선택하는 단계; 빔 가속 전위에 따라 GCIB를 가속하는 단계; 하나 이상의 빔 초점 전위에 따라 GCIB를 포커싱하는 단계; 및 빔 조사량에 따라 기판의 적어도 일부분에 가속된 GCIB를 조사하는 단계를 행함으로써 생성될 수 있다.

또한, 전술한 GCIB 특성 이외에, 빔 에너지, 빔 에너지 분포, 빔 각도 분포, 빔 발산각, 정체 압력, 정체 온도, 질량 유량, 클러스터 크기, 클러스터 크기 분포, 빔 크기, 빔 조성, 빔 전극 전위, 또는 가스 노즐 디자인(예컨대 노즐목 직경, 노즐 길이, 및/또는 노즐 확산 섹션 반각)이 선택될 수 있다. 예를 들어 앞서 언급한 타겟 에칭 프로세스 측정 기준을 달성하기 위해, 전술한 GCIB 특성 중 하나 이상을 선택할 수 있다. 또한, 예를 들어 앞서 언급한 타겟 에칭 프로세스 측정 기준을 제어하기 위해, 전술한 GCIB 특성 중 하나 이상을 변경할 수 있다.

도 3a는 GCIB에 대한 빔 에너지 분포 함수를 개략적으로 예시하는 그래프이다. 예를 들어, 도 3a는 몇몇 빔 에너지 분포(30A, 30B, 30C, 30D)를 그래프로 보여주는데, 이들 빔 에너지 분포를 35 방향으로 관통해 지나감에 따라, 피크 빔 에너지는 감소하고 빔 에너지 분포는 넓어진다.

GCIB에 대한 빔 에너지 분포 함수는, 각 GCIB를 압력 증가 영역을 통과하는 GCIB 경로를 따르는 방향으로 가게 하여 GCIB의 적어도 일부가 상기 압력 증가 영역을 가로지르게 함으로써 변경될 수 있다. 빔 에너지 분포에 대한 변경의 범위는, GCIB 경로의 적어도 일부분을 따라서의 압력-거리(d) 적분으로 특정될 수 있다. 압력-거리 적분의 값이 [압력 및/또는 경로 길이(d)의 증가에 따라] 증가하면, 빔 에너지 분포는 넓어지고 피크 에너지는 줄어든다. 압력-거리 적분의 값이 [압력 및/또는 경로 길이(d)의 감소에 따라] 감소하면, 빔 에너지 분포는 좁아지고 피크 에너지는 증대된다. 예로서, 빔 발산을 증대시키기 위해 빔 에너지 분포를 넓힐 수 있고, 또는 빔 발산을 감소시키기 위해 빔 에너지 분포를 좁힐 수 있다.

GCIB 경로의 적어도 일부분을 따라서의 압력-거리 적분은 약 0.0001 torr-cm 이상일 수 있다. 별법으로서, GCIB 경로의 적어도 일부분을 따라서의 압력-거리 적분은 약 0.001 torr-cm 이상일 수 있다. 또 다른 별법으로서, GCIB 경로의 적어도 일부분을 따라서의 압력-거리 적분은 약 0.01 torr-cm 이상일 수 있다. 예로서, GCIB 경로의 적어도 일부분을 따라서의 압력-거리 적분은 약 0.0001 torr-cm 내지 0.01 torr-cm 이상일 수 있다. 다른 예로서, GCIB 경로의 적어도 일부분을 따라서의 압력-거리 적분은 약 0.001 torr-cm 내지 0.01 torr-cm 이상일 수 있다.

별법으로서, GCIB에 대한 빔 에너지 분포 함수는, 각 GCIB의 전하 상태를 조정 혹은 변경함으로써 변경될 수 있다. 예를 들어, 상기 전하 상태는, 가스 클러스터의 전자 충돌 유도 이온화에 사용되는 전자에 대한 전자 플럭스, 전자 에너지, 또는 전자 에너지 분포를 조정함으로써 변경될 수 있다.

도 3b는 GCIB에 대한 빔 각도 분포 함수를 개략적으로 예시하는 그래프이다. 예를 들어, 도 3b는 입사 방향 45(즉, 상대각이 0°에서의 제1 피크(42) 및 제1 폭(44)[예컨대, 반치전폭(FWHM)]에 의해 특징지워지는 제1 빔 각도 분포 함수(40)를 그래프로 보여준다. 또한, 예를 들어, 도 3b는 입사 방향 45(즉, 상대각이 0°에서의 제2 피크(42') 및 제2 폭(44')[예컨대, 반치전폭(FWHM)]에 의해 특징지워지는 제2 빔 각도 분포 함수(40')를 그래프로 보여준다. 제1 빔 각도 분포 함수(40)는 좁은 분포(또는 상대적으로 좁은 빔 발산각)를 나타내는 반면에, 제2 빔 각도 분포 함수(40')는 상대적으로 넓은 분포(또는 상대적으로 넓은 빔 발산각)를 나타낸다. 따라서, 기판에의 수직 입사에 관한 GCIB의 방향성은, 빔 각도 분포 함수를 변경함으로써[예컨대, 제1 빔 각도 분포 함수(40)와 제2 빔 각도 분포 함수(40') 사이의 각도 분포를 변경함으로써] 조정될 수 있다. 빔 각도 분포 함수 또는 빔 발산각은 빔 에너지 분포 함수 변경과 관련하여 앞서 설명한 기술을 이용하여 변경될 수 있다.

일 실시형태에서, GCIB 프로세스 조건의 하나 이상의 GCIB 특성은, GCIB 조성, 빔 조사량, 빔 가속 전위, 빔 초점 전위, 빔 에너지, 빔 에너지 분포, 빔 각도 분포, 빔 발산각, 상기 GCIB 조성의 유량, 정체 압력, 정체 온도, 상기 GCIB가 통과하는 압력 증가 영역에 대한 백그라운드 가스 압력, 또는 상기 GCIB가 통과하는 압력 증가 영역에 대한 백그라운드 가스 유량(예컨대, 이하에 좀 더 세밀하게 거론되는 P-셀 값)을 포함할 수 있다.

다른 실시형태에서, 하나 이상의 타겟 에칭 프로세스 측정 기준을 달성하기 위한 하나 이상의 GCIB 특성 세팅은, 제1 재료 및/또는 제2 재료에 대한 타겟 에칭률, 제1 재료와 제2 재료 사이의 타겟 에칭 선택비, 및 제1 재료 및/또는 제2 재료에 대한 타겟 표면 거칠기 중 2 이상을 달성하기 위해, GCIB 조성, 빔 가속 전위, GCIB 조성의 유량 및 GCIB가 통과하는 압력 증가 영역에 대한 백그라운드 가스 유량을 세팅하는 것을 포함한다.

이하에 나타내어지는 바와 같이, 하나 이상의 GCIB 특성은, 제1 재료와 제2 재료 사이의 타겟 에칭 선택비를 1보다 작은 값, 실질적으로 1에 근사한 값, 및 1보다 큰 값으로 변경하도록 조정될 수 있다. 또한, 이하에 나타내어지는 바와 같이, 하나 이상의 GCIB 특성은, 제1 재료 및/또는 제2 재료에 대한 타겟 표면 거칠기를 5 옹스트롬 이하의 값으로 변경하도록 조정될 수 있다. 더 나아가, 하나 아상의 GCIB 특성은, 제1 및/또는 제2 재료에 대하여 비교적 높은 에칭률의 조건을 달성하도록, 또는 제1 및/또는 제2 재료에 대하여 비교적 낮은 에칭률의 조건을 달성하도록 조정될 수 있다.

단계 15에서는, GCIB는 기판(22)을 향하여 감압 환경을 통과하면서 빔 가속 전위에 따라 가속된다. GCIB의 경우, 빔 가속 전위는 100 kV 이하의 범위일 수 있고, 빔 에너지는 100 keV 이하의 범위일 수 있으며, 클러스터 크기는 수만 atom 이하의 범위일 수 있고, 빔 조사량은 약 1x1017 클러스터/㎠ 이하의 범위일 수 있다. 예를 들어, GCIB의 빔 가속 전위는 약 1 kV 내지 약 70 kV의 범위일 수 있다(즉, 평균 클러스터 전하 상태를 1이라 상정하면, 빔 에너지는 약 1 keV 내지 약 70 keV의 범위일 수 있다). 또한, 예를 들어 GCIB의 빔 조사량은 약 1x1012 클러스터/㎠ 내지 약 1x1014 클러스터/㎠의 범위일 수 있다.

약 0.25 eV/atom 내지 약 100 eV/atom의 범위의 원자당 에너지의 비를 갖는 GCIB가 설정될 수 있다. 별법으로서, 0.25 eV/atom 내지 약 10 eV/atom의 범위의 원자당 에너지의 비를 갖는 GCIB가 설정될 수 있다. 별법으로서, 1 eV/atom 내지 약 10 eV/atom의 범위의 원자당 에너지의 비를 갖는 GCIB가 설정될 수 있다.

소기의 원자당 에너지의 비를 갖는 GCIB를 설정하는 것은, 빔 가속 전위, GCIB의 형성을 위한 정체 압력, 또는 가스 유량, 또는 이들의 임의의 조합을 선택하는 것을 포함할 수 있다. 빔 가속 전위는 이온 클러스터당 빔 에너지 혹은 에너지를 증가 혹은 감소시키는 데 사용될 수 있다. 예를 들어, 빔 가속 전위의 증가로 인하여, 최대 빔 에너지가 증가되고, 이에 따라 소정의 클러스터 크기에 대한 원자당 에너지의 비가 증대된다. 또한, 정체 압력은 소정의 클러스터에 대한 클러스터 크기를 증가 혹은 감소시키는 데 사용될 수 있다. 예를 들어, GCIB의 형성 과정에서의 정체 압력의 증가로 인하여, 클러스터 크기(즉, 클러스터당 원자의 수)가 증가되고, 이에 따라 소정의 빔 가속 전위에 대한 원자당 에너지의 비가 감소된다.

여기서, 빔 조사량은 단위 면적당 클러스터의 수의 단위로서 주어진다. 그러나, 빔 조사량은 빔 전류 및/또는 시간(예컨대, GCIB 체류 시간)도 포함할 수 있다. 예를 들어, 빔 전류는 일정한 값으로 측정 및 유지될 수 있는 반면에, 시간은 빔 조사량을 변경하도록 달라진다. 별법으로서, 예를 들어, 클러스터가 단위 면적당 기판의 표면을 타격하는 비율(즉, 단위 시간에 대한 단위 면적당 클러스터의 수)은 일정하게 유지될 수 있는 반면에, 시간은 빔 조사량을 변경하도록 달라진다.

단계 16에서는, 기판(22) 상의 제1 재료와 제2 재료 중의 적어도 하나를 에칭하도록 기판(22)의 표면의 적어도 일부분에 GCIB를 조사한다.

도 1에 기재된 방법은, 하나 이상의 새로운 타겟 에칭 프로세스 측정 기준을 만들도록 하나 이상의 타겟 에칭 프로세스 측정 기준을 변경하는 단계와, 상기 하나 이상의 새로운 타겟 에칭 프로세스 측정 기준을 달성하도록 GCIB에 대하여 추가적인 GCIB 프로세스 조건의 하나 이상의 추가적인 GCIB 특성을 세팅하는 단계를 더 포함할 수 있다.

다른 실시형태에 따르면, 기판(22)에 GCIB를 조사할 뿐만 아니라, 다른 GCIB가 추가적인 제어 및/또는 기능을 위해 사용될 수 있다. 다른 GCIB, 예컨대 제2 GCIB에 의해 기판(22)을 조사하는 것은, GCIB의 사용 이전, 도중, 또는 이후에 진행될 수 있다. 예를 들어, 다른 GCIB는 기판(22)의 일부분에 불순물을 도프하는 데 사용될 수 있다. 추가적으로, 예를 들어, 다른 GCIB는 기판(22)의 특성을 변경하도록 기판(22)의 일부분을 개질하는 데 사용될 수 있다. 추가적으로, 예를 들어, 다른 GCIB는 추가적인 재료를 기판(22)으로부터 제거하도록 기판(22)의 일부분을 에칭하는 데 사용될 수 있다. 추가적으로, 예를 들어, 다른 GCIB는 추가적인 재료 또는 할로겐-함유 잔류물 등의 잔류물을 기판(22)으로부터 제거하도록 기판(22)의 일부분을 세정하는 데 사용될 수 있다. 또한, 예를 들어, 다른 GCIB는 기판(22)의 일부분에 재료를 성장 혹은 증착시키는 데 사용될 수 있다. 도핑, 개질, 에칭, 세정, 성장, 또는 증착은, He, Ne, Ar, Xe, Kr, B, C, Se, Te, Si, Ge, N, P, As, O, S, F, Cl 및 Br로 이루어진 군에서 선택된 하나 이상의 원소를 도입하는 것을 포함할 수 있다.

다른 실시형태에 따르면, 기판(22)에 있어서 GCIB가 조사되는 적어도 일부분(20, 20', 20")은 GCIB의 조사 이전 또는 이후에 세정될 수 있다. 예를 들어, 세정 프로세스는 건식 세정 프로세스 및/또는 습식 세정 프로세스를 포함할 수 있다. 또한, 기판(22)에 있어서 GCIB가 조사되는 적어도 일부분(20, 20', 20")은 GCIB의 조사 이후에 어닐링될 수 있다.

다른 실시형태에 따르면, 기판(22)을 준비 및/또는 에칭할 때, 기판(22) 또는 피처 패턴(28)을 교정 처리할 수 있다. 교정 처리 도중에, 현장내 혹은 현장밖에서 GCIB 처리 시스템에 연결된 계측 시스템을 이용하여, 계측 데이터를 획득할 수 있다. 상기 계측 시스템은, 광학 진단 시스템, X선 형광 분광 시스템, 4점 탐침 시스템, 투과형 전자 현미경(TEM), 원자력 현미경, 주사형 전자 현미경(SEM) 등(이들에 한정되는 것은 아님)을 비롯한 다양한 기판 진단 시스템을 포함할 ㅅ 있다. 또한, 상기 계측 시스템은, 광학 디지털 형상 측정기(ODP), 산란계, 타원편광계, 반사계, 간섭계, 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다.

예를 들어, 상기 계측 시스템은 광학 산란 측정 시스템을 구성할 수 있다. 이 산란 측정 시스템은, 빔 프로파일 타원편광 측정(타원편광계) 및 빔 프로파일 반사 측정(반사계)을 포함하며 Therma-Wave, Inc.(미국 94539 캘리포니아주 프레몬트 1250 릴라이언스 웨이 소재) 또는 Nanometrics, Inc.(미국 95035 캘리포니아주 밀피타스 1550 벅아이 드라이브 소재)에서 시판하는 산란계를 포함할 수 있다. 또한, 예를 들어, 현장 계측 시스템은 기판 상의 계측 데이터를 측정하도록 구성된 통합 광학 디지털 형상 측정(iODP) 산란 측정 모듈을 포함할 수 있다.

계측 데이터는, 예컨대 기판, 기판에 형성된 임의의 층 혹은 서브층, 및/또는 기판 상의 디바이스의 임의의 부분과 연관된 기하학적, 기계적, 전기적 및/또는 광학적 파라미터 등의 파라미터 데이터를 포함할 수 있다. 예를 들어, 계측 데이터는 전술한 계측 시스템에 의해 측정 가능한 임의의 파라미터를 포함할 수 있다. 또한, 예를 들어, 계측 데이터는, 막 두께, 표면 및/또는 계면의 거칠기, 표면 오염, 피처 깊이, 트렌치 깊이, 비아 깊이, 피처 폭, 트렌치 폭, 비아 폭, 임계 치수(CD), 전기 저항, 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다.

계측 데이터는 기판 상의 2 이상의 위치에서 측정될 수 있다. 또한, 이 데이터는 하나 이상의 기판에 대하여 획득 및 수집될 수 있다. 하나 이상의 기판은, 예를 들어 한 카세트의 기판을 포함할 수 있다. 하나 이상의 기판 중 적어도 하나에서의 2 이상의 위치에서 계측 데이터를 측정하고, 예를 들어 하나 이상의 기판 각각에서의 복수의 위치에서 계측 데이터를 획득할 수 있다. 그 후에, 복수의 기판 각각에서의 상기 복수의 위치를, 데이터 피팅 알고리즘을 이용하여 측정 부위로부터 미측정 부위로 확장할 수 있다. 예를 들어, 데이터 피팅 알고리즘은 내삽법(선형 혹은 비선형) 또는 외삽법(선형 혹은 비선형) 또는 이들의 조합을 포함할 수 있다.

일단 하나 이상의 기판에 대하여 계측 시스템을 이용하여 계측 데이터를 수집하면, 계측 데이터는 교정 데이터를 연산하는 컨트롤러에 제공된다. 계측 데이터는 물리적 접속(예컨대, 케이블) 또는 무선 접속 또는 이들의 조합을 통해 계측 시스템과 컨트롤러 사이에서 통신될 수 있다. 또한, 계측 데이터는 인트라넷 혹은 인터넷 접속을 통해 통신될 수 있다. 별법으로서, 계측 데이터는 컴퓨터 판독 가능한 매체를 통해 계측 시스템과 컨트롤러 사이에서 통신될 수 있다.

교정 데이터는 기판의 위치 특정 처리를 위하여 연산될 수 있다. 소정의 기판에 대한 교정 데이터는, 착신 계측 데이터와 연관된 파라미터 데이터와, 소정의 기판에 대한 타겟 파라미터 데이터 사이의 변화를 확보하기 위해, GCIB 조사량을 기판 상의 위치의 함수로서 조절하는 프로세스 조건을 포함한다. 예를 들어, 소정의 기판에 대한 교정 데이터는, 소정의 기판에 대한 파라미터 데이터의 불균일성을 교정하기 위해 GCIB를 사용하는 프로세스 조건을 결정하는 것을 포함할 수 있다. 별법으로서, 예를 들어, 소정의 기판에 대한 교정 데이터는, 소정의 기판에 대한 파라미터 데이터의 특별히 의도된 불균일성을 형성하기 위해 GCIB를 사용하는 프로세스 조건을 결정하는 것을 포함할 수 있다.

소기의 파라미터 데이터의 변화와 GCIB 조사량 사이에 수립된 관계와, GCIB 조사량과 GCIB 처리 파라미터의 세트를 포함하는 GCIB 프로세스 조건 사이에 수립된 관계를 이용하여, 컨트롤러는 각 기판에 대한 교정 데이터를 결정한다. 예를 들어, 착신 계측 데이터와 연관된 파라미터 데이터를 취득하고, 착신 파라미터 데이터와 타겟 파라미터 데이터 사이의 차이를 연산하며, 이 차이를 피팅하기 위해 GCIB 처리 패턴(즉, 에칭 패턴 혹은 증착 패턴 또는 양자 모두)을 뒤바꾸고, 그리고 파라미터 데이터의 변화와 GCIB 조사량 사이의 관계를 이용하여 GCIB 처리 패턴을 확보하도록 빔 조사량 윤곽을 만드는 데, 수학적 알고리즘이 이용될 수 있다. 그 후에, 예를 들어, 이렇게 산출된 빔 조사량 윤곽에 빔 조사량과 GCIB 프로세스 조건 사이의 관계를 이용하여 영향을 미치기 위해, GCIB 처리 파라미터를 결정할 수 있다. GCIB 처리 파라미터는 빔 조사량, 빔 에리어, 빔 프로파일, 빔 강도, 빔 주사율, 또는 노출 시간(또는 빔 체류 시간), 또는 이들 중 2 이상의 임의의 조합을 포함할 수 있다.

본 실시형태에는, 수학적 알고리즘의 선택에 대한 많은 수의 서로 다른 기법이 성공적으로 채용될 수 있다. 다른 실시형태에서, 빔 조사량 윤곽은 소기의 파라미터 데이터의 변화를 확보하기 위해 추가적인 재료를 선택적으로 증착시킬 수 있다.

교정 데이터는 GCIB를 이용하여 기판에 적용될 수 있다. 교정 처리 도중에, GCIB는 평활화, 비정질화, 개질, 도핑, 에칭, 성장, 또는 증착, 또는 이들 중 2 이상의 임의의 조합을 행하도록 구성될 수 있다. 기판에 대한 교정 데이터를 적용하면, 기판 결함의 교정, 기판 표면 평면성의 교정, 층 두께의 교정, 또는 층 접착의 개선이 가능해진다. 일단 GCIB의 세목에 대한 처리가 행해지면, 기판의 균일성 또는 기판에 대한 파라미터 데이터의 분포를 현장내 혹은 현장밖에서 검사할 수 있고, 프로세스는 적절하게 완료 또는 개선될 수 있다.

이제 도 4a 내지 도 4l을 살펴보면, 기판 상에서의 재료 에칭에 관한 예시적인 데이터가 그래프로 도시되어 있다. 도 4a는 정규화된 이산화규소(SiO2)의 에칭률을 열두가지 GCIB 처리 조건의 함수로서 보여주는 막대 그래프이다. 열두가지 GCIB 에칭 프로세스에 대한 GCIB 프로세스 조건이 표 1에 제공되어 있다. 각 GCIB 프로세스 조건에 대한 에칭률은, 표 1에 GCIB 프로세스 조건 "A"로 기재된 Ar GCIB를 이용한 에칭률에 의해 정규화된다.

표 1에서, 각 GCIB 프로세스 조건은, GCIB 조성과, 빔 가속 전위(kV), 그리고 빔 에너지 분포 함수의 변경과 관련이 있는 P-셀 값을 제공한다. GCIB 조성에 관련하여, 표기 "5%NF3/N2"는 N2에서의 NF3의 상대량(몰/몰%)을 나타낸다. P-셀 값과 관련하여서는, 전술한 바와 같이, P-셀 값은, GCIB와 백그라운드 가스 사이에 충돌을 일으켜 빔 에너지 분포 함수를 확장시키도록, 압력 증가 영역에 도입된 백그라운드 가스의 유량(sccm, 분당 표준 입방 센티미터)과 관련이 있다. 예를 들어, GCIB가 가로지르는 압력 셀에서의 압력은, 백그라운드 가스를 40 sccm의 유량(P-셀 값 "40")(또는 압력-거리 적분 약 0.005 torr-cm)으로 압력 셀에 도입함으로써 상승된다.

도 4a에 예시된 바와 같이, 광범위한 GCIB 프로세스 조건에 대하여, 이산화규소(SiO2)의 에칭률을 결정하였다. GCIB 프로세스 조건 "A"에서와 같이, GCIB가 Ar만을 함유하는 경우, 에칭률은 순전히 물리적인 요소, 예컨대 스퍼터링에 의해 움직여진다. 그러나, 도 4a와 표 1은, 에칭 프로세스에 대한 화학적 요소를 제공하여 에칭률을 증가시키는 데 GCIB 조성이 선택될 수 있다는 것을 시사한다.

도 4b에 예시된 바와 같이, 막대 그래프가 이산화규소(SiO2)와 포토레지스트 사이의 에칭 선택비를 표 1의 GCIB 프로세스 조건의 함수로서 보여준다. 에칭 선택비는 포토레지스트(P.R.)의 에칭률에 대한 이산화규소(SiO2)의 에칭률(즉, E/R SiO2 / E/R P.R.)에 관한 것이다. 도 4b를 검토해 보면, CHF3계 GCIB 조성과 Cl2계 GCIB 조성이 1보다 큰 에칭 선택비를 제공한다는 것이 나타난다.

도 4c는 이산화규소(SiO2)와 포토레지스트(P.R.)의 에칭률을 GCIB 프로세스 조건 및 P-셀 값의 함수로서 보여주는 데이터 그래프이다. 세가지 GCIB 에칭 프로세스에 대한 GCIB 프로세스 조건이 표 2에 제공되어 있다. 표 2에서, 각 GCIB 프로세스 조건은, GCIB 조성과, 빔 가속 전위(kV), 그리고 각 GCIB 조성의 각 화학 성분에 대한 유량(sccm)을 제공한다. 도 4c에서 명백한 바와 같이, 상기 세가지 GCIB 프로세스 조건 중 임의의 것을 이용한 이산화규소와 포토레지스트의 에칭률은, P-셀 값이 증가함에 따라 감소한다.

도 4d에 예시된 바와 같이, 막대 그래프가 이산화규소(SiO2)와 포토레지스트 사이의 에칭 선택비를 표 2의 GCIB 프로세스 조건의 함수로서 보여준다. 에칭 선택비는 포토레지스트(P.R.)의 에칭률에 대한 이산화규소(SiO2)의 에칭률(즉, E/R SiO2 / E/R P.R.)에 관한 것이다. 도 4d를 검토해 보면, (1) P-셀 값을 증가시킴에 따라, SiO2와 P.R. 사이의 에칭 선택비가 증가된다는 것; (2) 할로메탄 조성에 산소를, 특히 높은 P-셀 값으로 첨가함에 따라, SiO2와 P.R. 사이의 에칭 선택비가 약간 증가될 수 있다는 것; 및 (3) CHF3계 GCIB 조성이 Cl2계 GCIB 조성보다 높은 SiO2와 P.R. 사이의 에칭 선택비를 제공한다는 것이 나타난다.

도 4e에 도시된 바와 같이, 이산화규소(SiO2)의 에칭 표면의 표면 거칠기의 데이터 그래프가, 표 2의 GCIB 프로세스 조건과 P-셀 값의 함수로서 표시되어 있다. 표면 거칠기(Ra, 옹스트롬으로 측정, A)는 평균 거칠기를 나타낸다. 조도(粗度)는 계면 및/또는 표면의 요철의 크기일 수 있다. 예를 들어, 표면 거칠기 등의 조도는, 최대 거칠기(Rmax), 평균 거칠기(Ra)(도 4e에 도시) 자승 평균 평방근(rms) 거칠기(Rq)로서 수학적으로 특정될 수 있다. 도 4e를 검토해 보면, (1) P-셀 값을 증가시킴에 따라, SiO2 표면의 평균 거칠기가 감소된다는 것; 및 (2) CHF3계 GCIB 조성이 Cl2계 GCIB 조성보다 SiO2에 약간 높은 평균 거칠기를 제공한다는 것이 나타난다.

도 4f에 도시된 바와 같이, 막대 그래프가 이산화규소(SiO2)의 에칭률 및 이산화규소(SiO2)와 포토레지스트 사이의 에칭 선택비를 표 3의 GCIB 프로세스 조건의 함수로서 보여준다. 에칭 선택비는 포토레지스트(P.R.)의 에칭률에 대한 이산화규소(SiO2)의 에칭률(즉, E/R SiO2 / E/R P.R.)에 관한 것이다. 표 3의 세가지 GCIB 프로세스 조건에 대한 GCIB 조성은 표 2의 것과 동일하지만, 약간 낮은 표면 거칠기(3 옹스트롬 이하의 규모)를 확보하기 위해 몇몇 GCIB 프로세스 조건이 조정되어 있다.

표 3은 빔 가속 전위, P-셀 값, GCIB 조성에서의 각 가압 가스의 유량, 및 결과 에칭 선택비 및 평균 거칠기를 제공한다. 도 4f는 대응하는 관련 에칭률 및 에칭 선택비를 보여준다. 분명히, CHF3계 GCIB 조성에서는 비교적 높은 에칭 선택비와 함께 비교적 낮은 표면 거칠기가 달성된다.

도 4g는 다결정 실리콘(Si) 대비(對比) 포토레지스트(P.R.), 이산화규소(SiO2) 및 질화규소(SiN)의 에칭 선택비를 20%CHF3/He의 GCIB 조성에 대한 유량의 함수로서 보여주는 막대 그래프이다. GCIB 프로세스 조건은 60 kV의 빔 가속 전위와 0의 P-셀 값을 더 포함한다. 유량이 350 sccm으로부터 550 sccm으로 증가됨에 따라, Si 대비 P.R., SiO2 및 SiN의 에칭 선택비가 1보다 큰 값으로부터 1보다 낮은 값으로 감쇠된다.

도 4h는 이산화규소(SiO2)와 다결정 실리콘(Si) 사이의 에칭 선택비를 10%CHF3/He의 GCIB 조성에 대한 GCIB 프로세스 조건의 함수로서 보여주는 막대 그래프이다. 도 4h에 도시된 바와 같이, P-셀 값이 증가되면 SiO2와 Si 사이의 에칭 선택비가 증가되는 반면에, 유량이 증가되면 SiO2와 Si 사이의 에칭 선택비가 감소된다.

표 4에는, 몇몇 GCIB 프로세스 조건과, (SiO2와 Si 사이의) 결과 에칭 선택비, 그리고 평균 거칠기가 제공된다. GCIB 조성, 빔 가속 전위, P-셀 값 및 유량을 비롯한 여러 GCIB 프로세스 조건을 조정함으로써, 약 1 옹스트롬 내지 약 4 옹스트롬 범위의 평균 거칠기를 확보하면서, 에칭 선택비를 약 1 내지 약 12의 값으로 달리할 수 있다.

도 4i는 SiO2의 에칭률, 다결정 실리콘(Si)의 에칭률, 및 SiO2와 Si 사이의 에칭 선택비를 10%CHF3/O2의 GCIB 조성에 첨가된 He의 유량의 함수로서 보여주는 데이터 그래프이다. 에칭 선택비의 피크값(약 12. 2)에 대한 GCIB 프로세스 조건이 표 4에 제공되어 있다(6열 참조). He 유량을 변경하면서, GCIB 프로세스 조건의 나머지 파라미터를 일정하게 유지하였다.

도 4j는 다결정 실리콘(Si) 대비 포토레지스트(P.R.), 이산화규소(SiO2) 및 질화규소(SiN)의 에칭 선택비를 10%CClF3/He의 GCIB 조성에 대한 P-셀 값의 함수로서 보여주는 막대 그래프이다. GCIB 프로세스 조건은 60 kV의 빔 가속 전위와 450 sccm의 유량을 더 포함한다. P-셀 값이 0으로부터 40으로 증가됨에 따라, Si 대비 P.R.의 에칭 선택비는 감소되는 반면에, Si 대비 SiO2 및 SiN의 에칭 선택비는 증가된다.

도 4k는 다결정 실리콘(Si) 대비 포토레지스트(P.R.), 이산화규소(SiO2) 및 질화규소(SiN)의 에칭 선택비를 10%CClF3/He의 GCIB 조성에 대한 빔 가속 전위의 함수로서 보여주는 막대 그래프이다. GCIB 프로세스 조건은 0의 P-셀 값과 450 sccm의 유량을 더 포함한다. 빔 가속 전위가 60 kV로부터 10 kV로 감소됨에 따라, Si 대비 P.R., SiO2 및 SiN의 에칭 선택비가 감소된다.

표 5에는, 몇몇 GCIB 프로세스 조건과, (Si와 SiO2 사이의) 결과 에칭 선택비, 그리고 Si의 평균 거칠기가 제공된다. 각 GCIB 프로세스 조건에는, He에 10% CBrF3를 함유하는 GCIB 조성이 나열되어 있다. 몇몇 경우에, N2가 GCIB에 첨가된다. GCIB 조성, 빔 가속 전위, P-셀 값 및 유량을 비롯한 여러 GCIB 프로세스 조건을 조정함으로써, 약 3 옹스트롬 내지 약 30 옹스트롬 범위의 평균 거칠기를 확보하면서, 에칭 선택비를 약 0.3 내지 약 2.5의 값으로 달리할 수 있다. 예를 들어, 빔 가속 전위의 증가, P-셀 값의 증가, 및 에칭 화합물의 유량의 감소와 연계하여 N2를 첨가하면 평균 거칠기가 최소화된다.

표 6에는, 몇몇 GCIB 프로세스 조건과, (Si와 SiO2 사이의) 결과 에칭 선택비, 그리고 Si의 평균 거칠기가 제공된다. 각 GCIB 프로세스 조건에는, He에 20% CF4를 함유하는 GCIB 조성이 나열되어 있다. GCIB 조성, 빔 가속 전위, P-셀 값 및 유량을 비롯한 여러 GCIB 조건을 조정함으로써, 약 2 옹스트롬 내지 약 19 옹스트롬 범위의 평균 거칠기를 확보하면서, 에칭 선택비를 약 0.32 내지 약 0.54의 값으로 달리할 수 있다.

표 7에는, 몇몇 GCIB 프로세스 조건과, (Si와 SiN 사이의) 결과 에칭 선택비, 그리고 Si의 평균 거칠기가 제공된다. 각 GCIB 프로세스 조건에는, N2에 20% NF3를 함유하는 GCIB 조성이 나열되어 있다. GCIB 조성, 빔 가속 전위, P-셀 값 및 유량을 비롯한 여러 GCIB 조건을 조정함으로써, 약 2 옹스트롬 내지 약 60 옹스트롬 범위의 평균 거칠기를 확보하면서, 에칭 선택비를 약 1 내지 약 4의 값으로 달리할 수 있다. 평균 거칠기를 희생하여, 높은 에칭률과 에칭 선택비를 확보할 수 있다. 또한, Si와 SiN 사이의 에칭 선택비는 p-도프 Si와 SiN 사이의 에칭 선택비와 유사한 것으로 보인다.

표 8에는, 몇몇 GCIB 프로세스 조건과, (Si와 SiN 사이의) 결과 에칭 선택비, 그리고 Si의 평균 거칠기가 제공된다. 각 GCIB 프로세스 조건에는, N2에 2% 내지 6%의 Cl2를 함유하는 GCIB 조성이 나열되어 있다. 몇몇 경우에, He, Ar, 또는 N2가 GCIB에 첨가된다. GCIB 조성, 빔 가속 전위, P-셀 값 및 유량을 비롯한 여러 GCIB 조건을 조정함으로써, 약 12 옹스트롬 내지 약 105 옹스트롬 범위의 평균 거칠기를 확보하면서, 에칭 선택비를 1 미만의 값과 약 11의 값 사이로 달리할 수 있다.

표 9에는, 몇몇 GCIB 프로세스 조건과, (Si와 SiN 사이의) 결과 에칭 선택비, 그리고 Si의 평균 거칠기가 제공된다. 각 GCIB 프로세스 조건에는, He에 4% 내지 6%의 Cl2를 함유하는 GCIB 조성이 나열되어 있다. GCIB 조성, 빔 가속 전위, P-셀 값 및 유량을 비롯한 여러 GCIB 조건을 조정함으로써, 약 5 옹스트롬 내지 약 40 옹스트롬 범위의 평균 거칠기를 확보하면서, 에칭 선택비를 약 1.4 내지 약 6의 값으로 달리할 수 있다. Cl2에 대한 캐리어로서 He를 사용하는 것이, Cl2에 대한 캐리어로서 N2를 사용하는 것보다 평균 거칠기를 낮게 하는 것으로 보인다.

표 10에는, 몇몇 GCIB 프로세스 조건과, (Si와 SiN 사이의) 결과 에칭 선택비, 그리고 Si의 평균 거칠기가 제공된다. 각 GCIB 프로세스 조건에는, He에 35%의 HCl을 함유하는 GCIB 조성이 나열되어 있다. GCIB 조성, 빔 가속 전위, P-셀 값 및 유량을 비롯한 여러 GCIB 조건을 조정함으로써, 약 15 옹스트롬 내지 약 25 옹스트롬 범위의 평균 거칠기를 확보하면서, 에칭 선택비를 약 2 내지 약 7의 값으로 달리할 수 있다.

도 4l에는, 기판 상에서의 재료 에칭에 관한 예시적인 데이터가 그래프로 도시되어 있다. 도 4l은 세가지 GCIB 에칭 프로세스에 대한, NiFe, Cu, CoFe, Al, Al2O3, Ru, W, Mo, TaN, Ta, AlN, SiO2, SiN, Si, SiC, 포토레지스트(P.R.), 및 SiCOH 등의 몇몇 재료의 에칭률을 보여주는 막대 그래프이다. GCIB 프로세스는, (A) Ar; (B) 5% NF3/N2; 및 (C) 4% Cl2/He를 포함한다. 세가지 GCIB 에칭 프로세스에 대한 GCIB 프로세스 조건이 표 11에 제공되어 있다.

표 11에서, 각 GCIB 프로세스 조건은, GCIB 조성과, 빔 가속 전위(kV)와, 빔 에너지 분포 함수의 변경과 관련된 P-셀 값, 그리고 GCIB 조성의 유량을 제공한다.

도 4l에 예시된 바와 같이, F계 GCIB 화학 작용과는 대조적으로, Cl계 GCIB 화학 작용을 이용하면, CoFe, NiFe 및 Al 등의 몇몇 금속-함유 재료의 에칭률이 향상되는 경향이 있다. 또한, GCIB 프로세스 조건 "A"에서와 같이, GCIB가 Ar만을 함유하는 경우, 에칭률은 순전히 물리적인 요소, 예컨대 스퍼터링에 의해 움직여진다. 그러나, 도 4l과 표 11은, 에칭 프로세스에 대한 화학적 요소를 제공하여 에칭률을 증가시키는 데 GCIB 조성이 선택될 수 있다는 것을 시사한다.

이제 도 5를 참조해 보면, 일 실시형태에 따라 전술한 바와 같이 기판을 처리하는 GCIB 처리 시스템(100)이 도시되어 있다. GCIB 처리 시스템(100)은 진공 용기(102), 처리 대상인 기판(152)이 위에 부착되는 기판 홀더(150), 및 진공 펌핑 시스템(170A, 170B 및 170C)을 포함한다. 기판(152)은 반도체 기판, 웨이퍼, 평판 디스플레이(FPD), 액정 디스플레이(LCD), 또는 임의의 다른 피가공물일 수 있다. GCIB 처리 시스템(100)은 기판(152)을 처리하기 위해 GCIB를 생성하도록 구성되어 있다.

도 5의 GCIB 처리 시스템(100)을 계속 참조하면, 진공 용기(102)는 감압 인클로저(enclosure)를 제공하는 3개의 연통 챔버, 즉 소스 챔버(104), 이온화/가속 챔버(106), 및 처리 챔버(108)를 포함한다. 상기 3개의 챔버는 각각 진공 펌핑 시스템(170A, 170B 및 170C)에 의해 적절한 작동 압력으로 진공화된다. 상기 3개의 연통 챔버(104, 106, 108)에서는, 가스 클러스터 빔이 제1 챔버[소스 챔버(104)]에서 형성될 수 있고, 가스 클러스터 빔이 이온화 및 가속되는 제2 챔버[이온화/가속 챔버(106)]에서 GCIB가 형성될 수 있다. 이후에, 제3 챔버[처리 챔버(108)]에서는, 가속된 GCIB가 기판(152)을 처리하는 데 이용될 수 있다.

도 5에 도시된 바와 같이, GCIB 처리 시스템(100)은, 하나 이상의 가스 또는 가스의 혼합물을 진공 용기(102)에 도입하도록 구성된 하나 이상의 가스 공급원을 포함할 수 있다. 예를 들어, 제1 가스 공급원(111)에 저장된 제1 가스 조성물이 압력을 받아 제1 가스 제어 밸브(113A)를 통해 가스 계량 밸브(들)(113)에 들어가게 된다. 또한, 예를 들어, 제2 가스 공급원(112)에 저장된 제2 가스 조성물이 압력을 받아 제2 가스 제어 밸브(113B)를 통해 가스 계량 밸브(들)(113)에 들어가게 된다. 또한, 예를 들어, 제1 가스 조성물 또는 제2 가스 조성물 또는 양자 모두는 응축 가능한 불활성 가스, 캐리어 가스, 또는 희석 가스를 포함할 수 있다. 예를 들어, 불활성 가스, 캐리어 가스, 또는 희석 가스는 희가스, 즉 He, Ne, Ar, Kr, Xe, 또는 Rn을 포함할 수 있다.

또한, 제1 가스 공급원(111) 및 제2 가스 공급원(112)은 이온화된 클러스터를 생산하는 데 단독으로 또는 서로 조합되어 이용될 수 있다. 재료 조성물은 재료층과 반응하거나 재료층에 도입되는 것이 요망되는 성분의 주요 원자 또는 분자 종을 포함할 수 있다.

제1 가스 조성물 또는 제2 가스 조성물 또는 양자 모두를 포함하는 고압의, 응축 가능한 가스는 가스 공급 튜브(114)를 통해 정체 챔버(116) 내로 도입되고, 적절한 형상의 노즐(110)을 통해 실질적으로 낮은 압력의 진공 내로 빠져나온다. 고압의 응축 가능한 가스가 정체 챔버(116)로부터 소스 챔버(104)의 저압 영역으로 팽창함에 따라, 가스 속도는 초음파 속도로 가속되고 가스 클러스터 빔(118)은 노즐(110)로부터 나온다.

정적 엔탈피로서의 제트의 고유 냉각은 운동 에너지로 교환되고, 그 결과 제트의 팽창이 일어나며, 가스 제트의 일부분이 응축되고, 수개 내지 수천개의 약하게 결합된 원자 또는 분자로 각각 이루어지는 클러스터를 갖는 가스 클러스터 빔(118)이 형성된다. 소스 챔버(104)와 이온화/가속 챔버(106) 사이에서 노즐(110)의 출구의 하류측에 위치 결정된 가스 스키머(gas skimmer)(120)가, 가스 클러스터 빔(118)의 둘레 가장자리에 있으며 클러스터로 응축되지 않은 가스 분자를, 가스 클러스터 빔(118)의 코어에 있으며 클러스터를 형성한 가스 분자로부터 부분적으로 분리시킨다. 다른 이유도 있지만, 이와 같이 가스 클러스터 빔(118)의 일부분을 선택함으로써, 높은 압력이 유해할 수 있는 하류측 영역[예컨대, 이온화 장치(122) 및 처리 챔버(108)]의 압력이 감소될 수 있다. 또한, 가스 스키머(120)는 이온화/가속 챔버(106)에 들어가는 가스 클러스터 빔에 대한 초기 치수를 한정한다.

GCIB 처리 시스템(100)은 또한 하나 이상의 스키머 개구를 갖는 복수의 노즐을 포함할 수 있다. 복수의 가스 클러스터 이온 빔 시스템의 디자인에 관한 더 상세한 내용은, 2009년 4월 23일자로 "Multiple Nozzle Gas Cluster Ion Beam System"이란 명칭으로 출원된 미국 특허 출원 공개 제2010/0193701A1와, 2010년 3월 26일자로 "Multiple Nozzle Gas Cluster Ion Beam Processing System and Method of Operating"이란 명칭으로 출원된 미국 특허 출원 공개 제2010/0193472A1에 제공되어 있고, 이들 특허 출원의 내용은 그 전체가 본원에 참조로 인용되어 있다.

가스 클러스터 빔(118)이 소스 챔버(104)에서 형성된 후, 가스 클러스터 빔(118)을 구성하는 가스 클러스터가 이온화 장치(122)에 의해 이온화되어 GCIB(128)를 형성한다. 이온화 장치(122)는 하나 이상의 필라멘트(124)로부터 전자를 생성하는 전자 충격 이온화 장치를 포함할 수 있고, 이 전자는 가속화되고 이온화/가속 챔버(106) 내부에 있는 가스 클러스터 빔(118)의 가스 클러스터와 충돌하도록 가속 및 유도된다. 가스 클러스터와 충돌 충격시, 충분한 에너지의 전자가 가스 클러스터 내의 분자로부터의 전자를 방출시켜 이온화된 분자를 발생시킨다. 가스 클러스터의 이온화로 인하여, 일반적으로 네트 양전하(net positive charge)를 갖는 하전된 가스 클러스터 이온이 이주하게 될 수 있다.

도 5에 도시된 바와 같이, 빔 전자기기(130)를 이용하여 GCIB(128)를 이온화, 인출, 가속화 및 포커싱한다. 빔 전자기기(130)는, 이온화 장치의 필라멘트(124)를 가열하도록 전압(VF)을 제공하는 필라멘트 전원(136)을 포함한다.

또한, 빔 전자기기(130)는, 이온화 장치(122)로부터 클러스터 이온을 인출하는 적절히 바이어스된 고전압 전극(126)의 세트를 이온화/가속 챔버(106)에 포함한다. 이후에, 고전압 전극(126)은 인출된 클러스터 이온을 소기의 에너지까지 가속하고, GCIB(128)를 한정하도록 포커싱한다. GCIB(128)에서 클러스터 이온의 운동 에너지는 통상 약 1000 전자볼트(1 keV) 내지 수십 keV의 범위이다. 예를 들어, GCIB(128)는 1 keV 내지 100 keV까지 가속될 수 있다.

도 5에 도시된 바와 같이, 빔 전자기기(130)는, 이온화 장치의 필라멘트(124)로부터 방출된 전자를 가속시키고 이 전자를 가스 클러스터 빔(118)의 가스 클러스터에 부딪히게 하여 클러스터 이온을 생성하도록, 이온화 장치(122)의 애노드에 전압(VA)을 제공하는 애노드 전원(138)을 더 포함한다.

또한, 도 5에 도시된 바와 같이, 빔 전자기기(130)는, 이온화 장치(122)의 이온화 영역으로부터 이온을 인출하고 GCIB(128)를 형성하기 위해 적어도 하나의 고전압 전극(126)을 바이어스하는 전압(VEE)을 제공하는 인출 전원(138)을 포함한다. 예를 들어, 인출 전원(138)은 이온화 장치(122)의 애노드 전압 이하인 전압을 고전압 전극(126)의 제1 전극에 제공한다.

또한, 빔 전자기기(130)는, 이온화 장치(122)에 대하여 고전압 전극(126) 중의 하나를 바이어스하는 전압(VACC)을 제공하여서, 총 GCIB 가속 에너지를 VACC 전자볼트(eV)와 대략 동일하게 만드는 가속 장치 전원(140)을 포함할 수 있다. 예를 들어, 가속 장치 전원(140)은, 이온화 장치(122)의 애노드 전압 및 제1 전극의 인출 전압 이하인 전압을 고전압 전극(126)의 제2 전극에 제공한다.

더 나아가, 빔 전자기기(130)는, GCIB(128)를 포커싱하기 위해 고전압 전극(126)의 일부를 전위(예컨대, VL1 및 VL2)로 바이어스하도록 제공될 수 있는 렌즈 전원(142, 144)을 포함할 수 있다. 예를 들어, 렌즈 전원(142)은, 이온화 장치(122)의 애노드 전압, 제1 전극의 인출 전압 및 제2 전극의 가속 장치 전압 이하인 전압을 고전압 전극(126)의 제3 전극에 제공할 수 있고, 렌즈 전원(144)은, 이온화 장치(122)의 애노드 전압, 제1 전극의 인출 전압, 제2 전극의 가속 장치 전압 및 제3 전극의 제1 렌즈 전압 이하인 전압을 고전압 전극(126)의 제4 전극에 제공할 수 있다.

이온화 및 인출 방안에 많은 변수가 사용될 수 있음에 주의한다. 본원에 기재된 방안은 설명 용도에 유용하지만, 다른 인출 방안에는 이온화 장치 및 인출 전극(들)(또는 광학 소자)의 제1 요소를 VACC 상태로 두는 것이 포함된다. 이는 통상적으로 이온화 장치 전원에 대한 제어 전압을 프로그래밍하는 광파이버를 필요로 하지만, 전체적인 광학 소자 트레이닝은 더 간단하게 만든다. 본원에 기재된 발명은 이온화 장치 및 인출 렌즈 바이어스의 상세한 내용과는 무관하게 유용하다.

이온화/가속 챔버(106)에 있어서 고전압 전극(126)의 하류측에 있는 빔 필터(146)는, GCIB(128)로부터 모노머, 또는 모노머 및 가벼운 클러스터 이온을 제거하여, 처리 챔버(108)에 들어가는 여과된 프로세스 GCIB(128A)를 형성하는 데 사용될 수 있다. 일 실시형태에서, 빔 필터(146)는 100 미만의 원자 또는 분자 또는 양자 모두를 갖는 클러스터의 수를 실질적으로 감소시킨다. 빔 필터는, 상기 여과 프로세스에 도움을 주기 위해 GCIB(128)를 가로질러 자기장을 부여하는 자석 어셈블리를 포함할 수 있다.

도 5를 계속 참조해 보면, 이온화/가속 챔버(106)에 있어서 GCIB(128)의 경로에 빔 게이트(148)가 배치되어 있다. 빔 게이트(148)는, GCIB(128)가 이온화/가속 챔버(106)로부터 처리 챔버(108)로 통과하여 프로세스 GCIB(128A)를 형성하는 것이 허용되는 개방 상태와, GCIB(128)가 처리 챔버(108)에 들어가는 것이 차단되는 폐쇄 상태를 갖는다. 제어 케이블은 제어 시스템(190)으로부터의 제어 신호를 빔 게이트(148)로 전도한다. 제어 신호는 개방 상태 또는 폐쇄 상태 사이에서 빔 게이트(148)를 통제하여 전환시킨다.

웨이퍼 또는 반도체 웨이퍼, 평판 디스플레이(FPD), 액정 디스플레이(LCD), 또는 GCIB 처리에 의해 처리되는 다른 기판일 수 있는 기판(152)은, 처리 챔버(108)에서 프로세스 GCIB(128A)의 경로에 배치된다. 대부분의 용례가 공간적으로 균일한 결과를 갖게 큰 기판을 처리하는 것을 고려하기 때문에, 스캐닝 시스템은 공간적으로 균질한 결과를 도출하게 프로세스 GCIB(128A)를 큰 영역에 걸쳐 균일하게 스캔하는 것이 바람직할 수 있다.

X-스캔 액추에이터(160)는, X-스캔 운동[지면(紙面)의 안과 밖]의 방향으로 기판 홀더(150)의 선형 운동을 제공한다. Y-스캔 액추에이터(162)는, X-스캔 운동에 대해 통상 직각을 이루는 Y-스캔 운동(164)의 방향으로 기판 홀더(150)의 선형 운동을 제공한다. X-스캔 및 Y-스캔 운동을 조합하여, 기판 홀더(150)에 의해 유지된 기판(152)을 프로세스 GCIB(128A)를 통과하게 래스터형 스캔 운동 방식으로 병진시킴으로써, 기판(152)을 처리하는 프로세스 GCIB(128A)로 기판(152)의 표면을 균일하게(또는 다른 방식으로 프로그램하여) 조사하게 한다.

프로세스 GCIB(128A)가 기판(152) 표면에 대하여 빔 입사각(166)을 갖도록, 기판 홀더(150)는 기판(152)을 프로세스 GCIB(128A)의 축에 대하여 각도를 이루어 배치한다. 빔 입사각(166)은 90도 또는 다른 각도일 수 있지만, 통상 90도이거나 90도에 가깝다. Y-스캐닝 동안, 기판(152) 및 기판 홀더(150)는 도시된 위치로부터 각각 도면 부호 152A 및 150A로 나타내어진 대체 위치 "A"로 이동한다. 두 위치 사이를 이동할 때, 기판(152)은 프로세스 GCIB(128A)를 통해 스캐닝되고, 양 극단의 위치에서는 프로세스 GCIB(128A)의 경로의 완전히 밖으로 완전히 이동(오버 스캔)된다는 것을 유의하라. 도 5에 명백하게 도시되어 있지는 않았지만, 유사한 스캐닝 및 오버-스캔이 (통상) 직교하는 X-스캔 운동 방향(지면의 안과 밖)으로 수행된다.

기판 홀더(150)가 프로세스 GCIB(128A)의 경로 밖으로 스캐닝될 때, 프로세스 GCIB(128A)의 샘플을 인터셉트하도록, 빔 전류 센서(180)가 프로세스 GCIB(128A)의 경로에서 기판 홀더(150) 이후에 배치될 수 있다. 빔 전류 센서(180)는 통상, 빔-진입 개구를 제외하고는 폐쇄되어 있는 패러데이 컵 등이며, 통상 전기 절연 마운트(182)를 이용해 진공 용기(102)의 벽에 부착되어 있다.

도 5에 도시된 바와 같이, 제어 시스템(190)은, 전기 케이블을 통해 X-스캔 액추에이터(160) 및 Y-스캔 액추에이터(162)에 접속되어 있으며, 기판(152)을 프로세스 GCIB(128A)의 내외로 위치시키고, 기판(152)을 프로세스 GCIB(128A)에 대해 균일하게 스캔하여 프로세스 GCIB(128A)로 기판(152)에 소기의 처리를 달성하도록, X-스캔 액추에이터(160) 및 Y-스캔 액추에이터(162)를 제어한다. 제어 시스템(190)은, 빔 전류 센서(180)에 의해 수집된 샘플 빔 전류를 전기 케이블을 통해 받아서, GCIB를 모니터링하며, 소정의 조사량이 전달되었을 때, 프로세스 GCIB(128A)로부터 기판(152)을 제거함으로써, 기판(152)이 받는 GCIB(128) 조사량을 제어한다.

도 6에 도시된 실시형태에서, GCIB 처리 시스템(100')은 도 5의 실시형태와 유사하며, 두 축에서 기판(252)을 유지 및 이동시켜 프로세스 GCIB(128A)에 대해 기판(252)을 효율적으로 스캐닝하도록 동작 가능한 X-Y 위치 결정 테이블(253)을 더 포함한다. 예를 들어, X-운동은 지면 안과 밖으로의 운동을 포함할 수 있고, Y-운동은 방향 264를 따르는 운동을 포함할 수 있다.

프로세스 GCIB(128A)는, 기판(252)의 표면 상의 투사 충돌 영역(286)에서 기판(252)의 표면에 대해 빔 입사각(266)을 이루며 기판(252)과 충돌한다. X-Y 운동에 의해, X-Y 위치 결정 테이블(253)은 프로세스 GCIB(128A)의 경로에서 기판(252)의 표면의 각각의 부분을 위치 결정할 수 있어, 표면의 모든 영역이 프로세스 GCIB(128A)로 처리하는 투사 충돌 영역(286)과 일치하게 될 수 있다. X-Y 컨트롤러(262)는 X-축 방향과 Y-축 방향 각각에서의 위치 및 속도를 제어하기 위해 전기 케이블을 통해 X-Y 위치 결정 테이블(253)에 전기 신호를 제공한다. X-Y 컨트롤러(262)는 전기 케이블을 통해 제어 시스템(190)으로부터 제어 신호를 받아 제어 시스템(190)에 의해 작동될 수 있다. X-Y 위치 결정 테이블(253)은, 종래의 X-Y 테이블 위치 결정 기술에 따라 연속 동작 또는 단계적 동작에 의해 이동하여, 상기 투사 충돌 영역(286) 내에 기판(252)의 서로 다른 영역을 위치시킨다. 일 실시형태에서, 기판(252)의 임의의 부분을, 프로세스 GCIB(128A)로 GCIB 처리하는 투사 충돌 영역(286)을 통과하게, 프로그램 가능한 속도로 스캔하도록, X-Y 위치 결정 테이블(253)은 제어 시스템(190)에 의해 프로그램되어 작동 가능하다.

위치 결정 테이블(253)의 기판 유지면(254)은 전기 전도성을 갖고, 제어 시스템(190)에 의해 작동되는 선량(線量) 계측 프로세서에 접속되어 있다. 위치 결정 테이블(253)의 전기 절연층(255)은 위치 결정 테이블(253)의 베이스부(260)로부터 기판(252) 및 기판 유지면(254)을 절연한다. 충돌하는 프로세스 GCIB(128A)에 의해 기판(252)에 유도된 전하는, 기판(252) 및 기판 유지면(254)을 통해 전도되고, 선량 측정을 위해 신호가 위치 결정 테이블(253)을 통하여 제어 시스템(190)에 연결된다. 선량 측정에는, GCIB 처리 조사량을 결정하도록 GCIB 전류를 통합하는 통합 방법이 포함된다. 특정 분위기 하에서는, 전자 플러드(electron flood)라 종종 불리는 전자의 타겟-중화 소스(도시 생략)가, 프로세스 GCIB(128A)를 중화시키는 데 사용될 수 있다. 이러한 경우에, 패러데이 컵[도시되어 있지 않으나, 도 5의 빔 전류 센서(180)와 유사할 수 있음]이, 추가된 전하의 소스에도 불구하고 정확한 선량 계측을 보장하는 데 사용될 수 있는데, 이러한 이유는 통상의 패러데이 컵이 고에너지 양이온에 대해서만 진입 및 피측정을 허용하기 때문이다.

작동시, 제어 시스템(190)은, 기판(252)을 프로세스 GCIB(128A)로 조사하도록, 빔 게이트의 개구(148)에 신호를 보낸다. 제어 시스템(190)은, 기판(252)이 받은 축적 조사량을 연산하기 위해, 기판(252)에 의해 수집된 GCIB 전류의 측정을 모니터링한다. 기판(252)이 받은 조사량이 소정의 조사량에 도달하면, 제어 시스템(190)은 빔 게이트(148)를 폐쇄하고, 기판(252)의 처리가 완료된다. 기판(252)의 소정 영역에서 받은 GCIB 조사량의 측정에 기초하여, 제어 시스템(190)은 기판(252)의 서로 다른 영역을 처리하기에 적합한 빔 체류 시간을 달성하도록, 스캔 속도를 조절할 수 있다.

별법으로서, 프로세스 GCIB(128A)는 기판(252)의 표면에 걸쳐 고정된 패턴의 일정 속도로 스캐닝될 수 있지만; GCIB 강도는 의도적으로 불균일한 조사량을 샘플에 전달하도록 변조(Z-축 변조라고도 함)된다. GCIB 강도는, GCIB 공급원으로부터의 가스 흐름에 변화를 주는 것; 필라멘트 전압(VF) 또는 애노드 전압(VA)을 바꾸어 이온화 장치(122)를 조절하는 것; 렌즈 전압(VL1 및 또는 VL2)을 바꾸어 렌즈 초점을 조절하는 것; 또는 가변 빔 블록(variable beam block), 조정 가능한 셔터, 또는 가변 조리개로 GCIB의 일부분을 기계적으로 차단하는 것 등을 비롯한, 임의의 다양한 방법에 의해, GCIB 처리 시스템(100')에서 변조될 수 있다. 변조 변량은 연속적인 아날로그 변량일 수 있고, 또는 시간 변조 스위칭 또는 게이팅일 수 있다.

처리 챔버(108)는 현장 계측 시스템을 더 포함할 수 있다. 예를 들어, 현장 계측 시스템은, 입사 광학 신호(284)로 기판(252)을 조사하도록 구성된 광학 송신기(280)와 기판(252)으로부터의 산란 광학 신호(288)를 받도록 구성된 광학 수신기(282)를 갖는 광학 진단 시스템을 포함할 수 있다. 이 광학 진단 시스템은, 입사 광학 신호(284) 및 산란 광학 신호(288)의 처리 챔버(108)에 대한 출입 통과를 허용하는 광학 윈도우를 포함한다. 또한, 광학 송신기(280) 및 광학 수신기(282)는 각각 송신 광학 소자와 수신 광학 소자를 포함할 수 있다. 광학 송신기(280)는 제어 시스템(190)으로부터의 제어 전기 신호를 수신하고 응답한다. 광학 수신기(282)는 측정 신호를 제어 시스템(190)에 돌려보낸다.

현장 측정 시스템은 GCIB 처리의 프로세스를 모니터링하도록 구성된 임의의 기기를 포함할 수 있다. 일 실시형태에 따르면, 상기 현장 계측 시스템은 광학 산란 측정 시스템을 구성할 수 있다. 이 산란 측정 시스템은, 빔 프로파일 타원편광 측정(타원편광계) 및 빔 프로파일 반사 측정(반사계)을 포함하며 Therma-Wave, Inc.(미국 94539 캘리포니아주 프레몬트 1250 릴라이언스 웨이 소재) 또는 Nanometrics, Inc.(미국 95035 캘리포니아주 밀피타스 1550 벅아이 드라이브 소재)에서 시판하는 산란계를 포함할 수 있다.

예를 들어, 현장 계측 시스템은, GCIB 처리 시스템(100')에서의 처리 공정의 실행의 결과로 얻어지는 프로세스 성능 데이터를 측정하도록 구성된, 통합 광학 디지털 형상 측정(iODP) 산란 측정 모듈을 포함할 수 있다. 상기 계측 시스템은 예를 들어 처리 프로세스의 결과로 얻어지는 계측 데이터를 측정 또는 모니터링할 수 있다. 예를 들어, 상기 계측 데이터는, 처리 프로세스를 특정하는 프로세스 성능 데이터, 예컨대 프로세스 속도, 프로세스 상대 속도, 피처 프로파일 각도, 임계 치수, 피처 두께 또는 깊이, 피처 형상 등을 결정하는 데 이용될 수 있다. 예를 들어, 기판 상에 재료를 방향성을 부여하여 증착하는 프로세스에서, 프로세스 성능 데이터는, 피처(즉, 비아, 라인 등)의 상측, 중간 또는 하측 CD 등의 임계 치수(CD), 피처 깊이, 재료 두께, 측벽 각도, 측벽 형상, 증착률, 상대 증착률, 공간적 분포에 관한 임의의 파라미터, 임의의 공간적 분포의 균일성을 특정하는 파라미터 등을 포함할 수 있다. 제어 시스템(190)으로부터의 제어 신호를 통해 X-Y 위치 결정 테이블(253)을 작동하면, 현장 계측 시스템은 기판(252)의 하나 이상의 특징을 맵핑할 수 있다.

도 7에 도시된 실시형태에서, GCIB 처리 시스템(100'')은 도 5의 실시형태와 유사할 수 있고, 예를 들어 이온화/가속 챔버(106)의 출구 영역에 또는 그 부근에 위치된 압력 셀 챔버(350)를 더 포함한다. 압력 셀 챔버(350)는, 압력 셀 챔버(350)의 압력을 상승시키기 위해 압력 셀 챔버(350)에 백그라운드 가스를 공급하도록 구성된 불활성 가스 공급원(352)과, 압력 셀 챔버(350)에서 상승된 압력을 측정하도록 구성된 압력 센서(354)를 포함한다.

압력 셀 챔버(350)는, GCIB(128)의 빔 에너지 분포를 변경하여 변경된 처리 GCIB(128A')를 생성하도록 구성될 수 있다. 이러한 빔 에너지 분포의 변경은, GCIB의 적어도 일부가 압력 증가 영역을 가로지르도록, GCIB(128)를 압력 셀 챔버(350) 내에 있는 압력 증가 영역을 통과하는 GCIB 경로를 따르게 지향시킴으로써 달성된다. 빔 에너지 분포에 대한 변경의 범위는, GCIB 경로의 적어도 일부분을 따라서의 압력-거리 적분으로 특정될 수 있는데, 여기서 거리[또는 압력 셀 챔버(350)의 길이]는 경로 길이(d)로 나타내어진다. 압력-거리 적분의 값이 [압력 및/또는 경로 길이(d)의 증가에 따라] 증가하면, 빔 에너지 분포는 넓어지고 피크 에너지는 줄어든다. 압력-거리 적분의 값이 [압력 및/또는 경로 길이(d)의 감소에 따라] 감소하면, 빔 에너지 분포는 좁아지고 피크 에너지는 증대된다. 압력 셀의 디자인에 관한 더 상세한 사항은 "Method and apparatus for improved processing with a gas-cluster ion beam"라는 명칭의 미국 특허 제7,060,989호로부터 결정될 수 있으며; 이 특허의 내용은 그 전체가 참조로 본원에 인용되어 있다.

제어 시스템(190)은 마이크로프로세서와, 메모리, 그리고 GCIB 처리 시스템(100)(또는 100', 100")과의 통신 및 입력 기동을 행할 뿐만 아니라 GCIB 처리 시스템(100)(또는 100', 100")로부터의 출력을 모니터링하기에 충분한 제어 전압을 발생시킬 수 있는 디지털 I/O 포트를 포함한다. 또한, 제어 시스템(190)은 진공 펌핑 시스템(170A, 170B 및 170C), 제1 가스 공급원(111), 제2 가스 공급원(112), 제1 가스 제어 밸브(113A), 제2 가스 제어 밸브(113B), 빔 전자기기(130), 빔 필터(146), 빔 게이트(148), X-스캔 액추에이터(160), Y-스캔 액추에이터(162), 및 빔 전류 센서(180)와 연결되어 정보를 교환할 수 있다. 예컨대, 기판(152) 상에 GCIB 프로세스를 실시하기 위해 프로세스 레시피에 따라 전술한 GCIB 처리 시스템(100)의 구성 요소들에 대한 입력을 기동하는 데에, 메모리에 기억된 프로그램을 사용할 수 있다.

그러나, 제어 시스템(190)은, 메모리에 담긴 하나 이상의 명령의 하나 이상의 시퀀스를 실행하는 프로세서에 응답하여, 본 발명의 마이크로프로세서 기반 처리 단계의 일부 또는 전체를 수행하는 범용 컴퓨터 시스템으로 구현될 수 있다. 이러한 명령은, 하드 디스크 또는 착탈식 미디어 드라이브와 같은 다른 컴퓨터 판독 가능한 매체로부터 컨트롤러의 메모리에 읽혀 들여질 수 있다. 멀티 프로세싱 형태의 하나 이상의 프로세서도 또한 메인 메모리에 담긴 명령의 시퀀스를 실행하는 컨트롤러의 마이크로프로세서로서 채용될 수 있다. 다른 실시예에서, 하드웨어에 내장된 회로(hard-wired circuitry)가 소프트웨어 명령을 대신해 또는 소프트웨어 명령과 함께 사용될 수 있다. 따라서, 실시예는 하드웨어 회로와 소프트웨어의 임의의 특정한 조합에 제한되지 않는다.

제어 시스템(190)은 전술한 바와 같은 다수의 처리 요소를 구성하는 데 사용될 수 있고, 제어 시스템(190)은 처리 요소로부터의 데이터를 수집하고, 제공하며, 처리하고, 저장하며, 디스플레이할 수 있다. 제어 시스템(190)은 하나 이상의 처리 요소를 제어하기 위한 다수의 애플리케이션 뿐만 아니라 다수의 컨트롤러를 포함할 수 있다. 예를 들어, 제어 시스템(190)은, 사용자로 하여금 하나 이상의 처리 요소를 모니터 및/또는 제어할 수 있게 하는 인터페이스를 제공할 수 있는 그래픽 사용자 인터페이스(GUI) 구성 요소(도시 생략)를 포함할 수 있다.

제어 시스템(190)은 GCIB 처리 시스템(100)(또는 100', 100")에 대해 가까이 위치할 수 있고, 또는 GCIB 처리 시스템(100)(또는 100', 100")에 대해 원거리에 위치할 수 있다. 예를 들어, 제어 시스템(190)은 직접 접속, 인트라넷, 및/또는 인터넷을 이용하여 GCIB 처리 시스템(100)과 데이터를 교환할 수 있다. 제어 시스템(190)은, 예를 들어 고객 사이트(즉, 디바이스 생산 회사 등)에 있는 인트라넷에 연결될 수 있고, 또는 예를 들어 판매자 사이트(즉, 장비 제조자)에 있는 인트라넷에 연결될 수 있다. 별법으로서 또는 추가적으로, 제어 시스템(190)은 인터넷에 연결될 수 있다. 또한, 다른 컴퓨터(즉, 컨트롤러, 서버 등)가, 직접 접속, 인트라넷, 및/또는 인터넷을 통하여 데이터를 교환하도록 제어 시스템(190)에 액세스할 수 있다.

기판(152)(또는 252)은 클램핑 시스템(도시되지 않음), 예컨대 기계적 클램핑 시스템 또는 전기적 클램핑 시스템(예를 들면, 정전기적 클램핑 시스템) 등을 통해 기판 홀더(150)[또는 기판 홀더(250)]에 부착될 수 있다. 또한, 기판 홀더(150)(또는 250)는 기판 홀더(150)(또는 250) 및 기판(152)(또는 252)의 온도를 조정 및/또는 제어하도록 구성된 가열 시스템(도시 생략) 또는 냉각 시스템(도시 생략)을 포함할 수 있다.

진공 펌핑 시스템(170A, 170B 및 170C)은, 펌핑 속도를 약 초당 5,000 리터(및 그 이상)까지 올릴 수 있는 터보 분자 진공 펌프(TMP)와, 챔버 압력을 조절하기 위한 게이트 밸브를 포함할 수 있다. 통상의 진공 처리 장치에는, 초당 1,000 내지 3,000 리터의 TMP가 채용될 수 있다. TMP는 통상 약 50 mTorr 미만의 저압 처리에 유용하다. 도시되어 있지 않지만, 압력 셀 챔버(350)도 진공 펌핑 시스템을 포함할 수 있음은 물론이다. 또한, 챔버 압력을 모니터하기 위한 장치(도시 생략)가 진공 용기(102) 또는 3개의 진공 챔버(104, 106, 108) 중 임의의 것에 연결될 수 있다. 압력-측정 장치는, 예를 들어 정전 용량식 마노미터 또는 전리 진공계일 수 있다.

이제 도 8을 참조해 보면, 가스 클러스터 제트[가스 클러스터 빔(118), 도 5, 도 6 및 도 7)를 이온화하기 위한 이온화 장치(122, 도 5, 도 6 및 도 7)의 단면(300)이 도시되어 있다. 단면(300)은 GCIB(128)의 축에 대해 수직이다. 통상의 가스 클러스터 크기(2000 내지 15000 atom)의 경우, 가스 스키머(120, 도 5, 도 6 및 도 7)를 떠나서 이온화 장치기(122, 도 5, 도 6 및 도 7)에 들어가는 클러스터는 약 130 전자볼트(eV) 내지 1000 전자볼트(eV)의 운동 에너지로 이동할 것이다. 이러한 낮은 에너지에서, 이온화 장치(122) 내에서의 공간 전하적 중성으로부터의 임의의 이탈은 제트의 신속한 분산을 야기하고 빔 전류의 상당한 손상을 야기할 것이다. 도 8은 자기-중화 이온화 장치를 도시하고 있다. 다른 이온화 장치와 마찬가지로, 가스 클러스터는 전자 충격에 의해 이온화된다. 이러한 디자인에서, 열-전자(7개의 예가 310으로 표시됨)가 복수의 선형 열이온 필라멘트(302a, 302b 및 302c)(통상 텅스텐)로부터 방출되고, 전자-반사 전극(306a, 306b 및 306c) 및 빔-형성 전극(304a, 304b 및 304c)에 의해 제공된 적절한 전기장의 작용에 의해 인출 및 포커싱된다. 열-전자(310)는 가스 클러스터 제트 및 제트 축을 통과한 후, 반대측 빔-형성 전극(304b)에 부딪혀 저에너지 2차 전자(예를 들어 나타낸 312, 314 및 316으로 표시)를 생성한다.

(간소화를 위해) 도시하지는 않았지만, 선형 열이온 필라멘트(302b 및 302c)도 또한 열-전자를 생성하며, 이 열-전자는 이후에 저에너지 2차 전자를 생성한다. 모든 2차 전자는, 공간 전하 중성을 유지하는데 필요한 대로, 양으로 이온화된 가스 클러스터 제트에 끌려갈 수 있는 저에너지 전자를 제공함으로써, 이온화된 클러스터 제트가 공간 전하 중성을 유지하는 것을 보장하는 데 기여한다. 빔-형성 전극(304a, 304b 및 304c)은 선형 열이온 필라멘트(302a, 302b 및 302c)에 대해 양으로 바이어스되고, 전자-반사 전극(306a, 306b 및 306c)은 선형 열이온 필라멘트(302a, 302b 및 302c)에 대해 음으로 바이어스된다. 절연체(308a, 308b, 308c, 308d, 308e 및 308f)는 전극(304a, 304b, 304c, 306a, 306b 및 306c)을 전기적으로 절연하고 지지한다. 예를 들어, 이러한 자기-중화 이온화 장치는 효과적이며, 1000 마이크로 Amp 이상의 아르곤 GCIB를 달성한다.

별법으로서, 이온화 장치는 클러스터를 이온화하기 위해 플라즈마로부터의 전자 인출을 이용할 수 있다. 이러한 이온화 장치의 기하학적 구조는 전술한 3개의 필라멘트 이온화 장치와는 꽤 상이하지만, 작동 원리 및 이온화 장치의 제어는 매우 유사하다. 이제 도 9를 참조해 보면, 가스 클러스터 제트[가스 클러스터 빔(118), 도 5, 도 6 및 도 7)를 이온화하기 위한 이온화 장치(122, 도 5, 도 6 및 도 7)의 단면(400)이 도시되어 있다. 단면(400)은 GCIB(128)의 축에 대해 수직이다. 통상의 가스 클러스터 크기(2000 내지 15000 atom)의 경우, 가스 스키머(120, 도 5, 도 6 및 도 7)를 떠나서 이온화 장치기(122, 도 5, 도 6 및 도 7)에 들어가는 클러스터는 약 130 전자볼트(eV) 내지 1000 전자볼트(eV)의 운동 에너지로 이동할 것이다. 이러한 낮은 에너지에서, 이온화 장치(122) 내에서의 공간 전하적 중성으로부터의 임의의 이탈은 제트의 신속한 분산을 야기하고 빔 전류의 상당한 손상을 야기할 것이다. 도 9는 자기-중화 이온화 장치를 도시하고 있다. 다른 이온화 장치와 마찬가지로, 가스 클러스터는 전자 충격에 의해 이온화된다.