KR20070082956A - 액정표시패널용 어레이 기판 - Google Patents

액정표시패널용 어레이 기판 Download PDFInfo

- Publication number

- KR20070082956A KR20070082956A KR1020060016063A KR20060016063A KR20070082956A KR 20070082956 A KR20070082956 A KR 20070082956A KR 1020060016063 A KR1020060016063 A KR 1020060016063A KR 20060016063 A KR20060016063 A KR 20060016063A KR 20070082956 A KR20070082956 A KR 20070082956A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- electrode

- electrode layer

- array substrate

- pad

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13454—Drivers integrated on the active matrix substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133388—Constructional arrangements; Manufacturing methods with constructional differences between the display region and the peripheral region

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Nonlinear Science (AREA)

- General Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

비표시 영역에 위치하는 커패시터가 차지하는 면적을 최소화하면서 고용량의 커패시터를 구현할 수 있는 구조를 갖는 어레이 기판이 개시된다. 상기 어레이 기판은 표시 영역 및 주변 영역을 갖는 기판, 상기 기판의 표시 영역에 형성되는 박막 트랜지스터 및 상기 기판의 주변 영역에 형성되는 커패시터를 포함한다. 상기 어레이 기판은 하부에 위치하는 제1 서브 커패시터 및 상부에 위치하는 제2 서브 커패시터가 병렬로 연결되는 구조를 갖는 커패시터를 포함하기 때문에 면적의 증가 없이 상기 커패시터의 용량을 증가시킬 수 있다. 또한, 일반적인 액정표시패널의 전극이 형성되는 공정이 진행될 때 상기 커패시터의 전극이 형성될 수 있기 때문에 별도의 추가 공정 없이 고용량을 갖는 커패시터를 구현할 수 있다.

Description

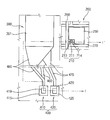

도 1은 본 발명의 제1 실시예에 따른 어레이 기판을 개략적으로 나타내는 평면도이다.

도 2는 도 1에 도시된 커패시터 및 화소부를 확대한 평면도이다.

도 3은 도 2에 도시된 Ⅰ-Ⅰ'선에 따라 절단한 단면도이다.

도 4는 도 2에 도시된 제1 및 제2 서브 커패시터가 병렬 연결된 경우 커패시터의 전기 용량의 증가를 설명하기 위한 개념도이다.

도 5는 본 발명의 제2 실시예에 따른 어레이 기판의 커패시터 및 화소부를 확대한 평면도이다.

도 6은 도 5에 도시된 II-II'선에 따라 절단한 단면도이다.

도 7은 본 발명의 제3 실시예에 따른 어레이 기판의 커패시터 및 화소부를 확대한 평면도이다.

도 8은 도 7에 도시된 III-III'선에 따라 절단한 단면도이다.

*도면의 주요부분에 대한 부호의 설명*

DA : 표시 영역 PA : 주변 영역

100 : 기판 200 : 화소부

210 : 박막 트랜지스터 211 : 게이트 전극

213 : 소스 전극 214 : 드레인 전극

250 : 투명 전극 255 : 반사 전극

300 : 커패시터 310 : 제1 서브 커패시터

311 : 하부 전극층 315 : 제1 유전층

330 : 중간 전극층 350 : 제2 서브 커패시터

351 : 상부 전극층 355 : 제2 유전층

390 : 컨택부 400 : 패드부

410 : 제1 패드 411 : 제1 패드 전극

420 : 제2 패드 421 : 제2 패드 전극

460 : 제1 전압 인가 배선 470 : 제2 전압 인가 배선

480 : 제3 전압 인가 배선 485 : 제4 전압 인가 배선

500 : 어레이 기판

본 발명은 액정표시패널용 어레이 기판에 관한 것으로서, 보다 상세하게는 고용량의 커패시터를 구현할 수 있는 구조를 갖는 어레이 기판에 관한 것이다.

대표적인 평판표시장치인 액정표시장치(Liquid Crystal Display : LCD)는 액정(Liquid Crystal)의 전기적 및 광학적 특성을 이용하여 영상을 표시한다. 상기 액정표시장치(LCD)는 다른 표시장치에 비해 두께가 얇고 무게가 가벼우며, 낮은 소비전력 및 낮은 구동전압에서 작동하는 장점을 갖고 있어 산업 전반에 걸쳐 많이 사용되고 있다.

일반적으로, 액정표시장치는 어레이 기판, 상기 어레이 기판에 대향하는 컬러필터 기판 및 양 기판 사이에 개재되어 액정을 포함하는 액정표시패널을 구비한다. 또한, 상기 어레이 기판에는 다수의 박막 트랜지스터, 다수의 게이트 배선 및 드레인 배선이 형성된다.

상기 박막 트랜지스터를 구동하기 위한 구동 회로는 별도의 PCB(printed circuit board)에 실장되어 TCP(tape carrier pakage)에 의해 상기 어레이 기판에 연결될 수도 있고, 상기 어레이 기판의 외곽 영역에 직접 형성될 수도 있다.

특히, 구동 회로가 어레이 기판상에 형성되는 구조를 갖는 액정표시패널의 어레이 기판상에는, 예컨대, 전압을 안정시키거나 전하(charge)를 펌핑(pumping)하는 용도로 사용되는 커패시터가 형성될 수 있다.

커패시터의 용량을 증가시키기 위해서는 커패시터가 차지하는 면적을 크게할 필요가 있다. 그러나, 액정표시패널의 비표시 영역 (또는 주변 영역)의 면적이 작을 경우에는 커패시터의 용량을 증가시키기 위해 커패시터의 면적을 크게 하는 것에 한계가 있다.

따라서, 커패시터가 차지하는 면적을 더 증가시키지 않고 고용량을 구현할 수 있는 구조를 갖는 커패시터가 필요하다.

본 발명의 목적은 커패시터가 차지하는 면적을 최소화하면서 고용량의 커패시터를 구현할 수 있는 구조를 갖는 어레이 기판을 제공함에 있다.

본 발명의 다른 목적은 별도의 추가 공정 없이 고용량을 구현할 수 있는 구조를 갖는 어레이 기판을 제공함에 있다.

상술한 목적을 달성하기 위한 본 발명의 일 실시예에 따른 어레이 기판은 다수의 화소부를 포함하는 표시 영역 및 상기 표시 영역의 외곽에 위치하는 주변 영역을 갖는 기판, 상기 기판의 표시 영역에 형성되고 게이트 전극, 소스 전극 및 드레인 전극을 포함하는 박막 트랜지스터 및 상기 기판의 주변 영역에 형성되고 제1 서브 커패시터 및 제2 서브 커패시터를 포함하는 커패시터를 포함한다.

상기 제1 서브 커패시터는 하부 전극층, 상기 하부 전극층 위에 형성되는 중간 전극층 및 상기 하부 전극층과 상기 중간 전극층 사이에 개재되는 제1 유전층을 갖는 제1 서브 커패시터를 포함한다.

상기 제2 서브 커패시터는 상기 제1 서브 커패시터의 상부에 배치되고, 상기 중간 전극층, 상기 중간 전극층 위에 형성되는 상부 전극층 및 상기 중간 전극층과 상기 상부 전극층 사이에 개재되는 제2 유전층을 갖는 제2 서브 커패시터를 포함한다.

상기 제1 서브 커패시터의 하부 전극층은 상기 박막 트랜지스터의 게이트 전극을 형성하는 층과 동일한 층으로부터 형성될 수 있다. 상기 중간 전극층은 상기 박막 트랜지스터의 소스 및 드레인 전극을 형성하는 층과 동일한 층으로부터 형성 될 수 있다.

상기 어레이 기판은 상기 박막 트렌지스터의 게이트 전극 위에 형성되는 게이트 절연층을 더 포함하고, 상기 제1 서브 커패시터의 제1 유전층은 상기 게이트 절연층을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 어레이 기판은 상기 박막 트렌지스터의 드레인 전극과 전기적으로 연결되는 투명 전극을 더 포함하고, 상기 제2 서브 커패시터의 상부 전극층은 상기 투명 전극을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 어레이 기판은 상기 박막 트렌지스터의 소스 및 드레인 전극 위에 형성되는 패시베이션층을 더 포함하고, 상기 제2 서브 커패시터의 제2 유전층은 상기 패시베이션층을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 어레이 기판은 상기 박막 트렌지스터 위에 형성되는 반사 전극을 더 포함하는 경우 상기 제2 서브 커패시터의 상부 전극층은 상기 반사 전극을 형성하는 층과 동일한 층으로부터 형성될 수도 있다.

상기 제1 서브 커패시터의 하부 전극층과 상기 제2 서브 커패시터의 상부 전극층은 전기적으로 연결되어 상기 제1 서브 커패시터 및 상기 제2 서브 커패시터가 병렬 연결된다.

본 발명의 다른 실시예에 따른 어레이 기판은 다수의 화소부를 포함하는 표시 영역 및 상기 표시 영역의 외곽에 위치하는 주변 영역을 갖는 기판, 상기 기판의 표시 영역에 형성되고 게이트 전극, 소스 전극 및 드레인 전극을 포함하는 박막 트랜지스터, 상기 기판의 주변 영역에 형성되고 제1 서브 커패시터 및 제2 서브 커 패시터를 포함하는 커패시터 및 상기 커패시터에 전압을 인가하기 위해 상기 기판의 주변 영역에 형성되는 패드부를 포함한다.

상기 제1 서브 커패시터는 하부 전극층, 상기 하부 전극층 위에 형성되는 중간 전극층 및 상기 하부 전극층과 상기 중간 전극층 사이에 개재되는 제1 유전층을 갖는 제1 서브 커패시터를 포함한다.

상기 제2 서브 커패시터는 상기 제1 서브 커패시터의 상부에 배치되고, 상기 중간 전극층, 상기 중간 전극층 위에 형성되는 상부 전극층 및 상기 중간 전극층과 상기 상부 전극층 사이에 개재되는 제2 유전층을 갖는 제2 서브 커패시터를 포함한다.

상기 패드부는 상기 제1 서브 커패시터의 하부 전극층과 상기 제2 서브 커패시터의 상부 전극층에 전기적으로 연결되는 제1 패드 및 상기 중간 전극층에 전기적으로 연결되는 제2 패드를 포함한다.

상기 제1 서브 커패시터의 하부 전극층과 상기 제2 서브 커패시터의 상부 전극층은 상기 제1 패드에서 전기적으로 연결되어 상기 제1 서브 커패시터 및 상기 제2 서브 커패시터가 병렬 연결된다.

상기 제1 서브 커패시터의 하부 전극층으로부터 연장된 제1 전압 인가 배선을 더 포함하고, 상기 하부 전극층과 상기 제1 패드는 상기 제1 전압 인가 배선을 통해서 전기적으로 연결될 수 있다. 상기 제1 패드는 상기 제1 전압 인가 배선으로부터 연장된 제1 패드 전극을 포함한다.

상기 제1 서브 커패시터의 하부 전극층, 상기 제1 전압 인가 배선 및 상기 제1 패드 전극은 상기 박막 트랜지스터의 게이트 전극을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 어레이 기판은 상기 제2 서브 커패시터의 상부 전극층으로부터 연장된 제3 전압 인가 배선을 더 포함할 수 있고, 상기 제1 패드는 상기 제3 전압 인가 배선으로부터 연장된 제1 덮개 전극을 더 포함할 수도 있다.

상기 어레이 기판이 상기 박막 트렌지스터의 드레인 전극과 전기적으로 연결되는 투명 전극을 더 포함하는 경우, 상기 제2 서브 커패시터의 상부 전극층, 상기 제3 전압 인가 배선 및 상기 제1 덮개 전극은 상기 투명 전극을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제1 패드는 상기 제1 패드 전극과 상기 제1 덮개 전극사이에 개재되는 제1 중간층을 더 포함하고, 상기 제1 중간층은 상기 제1 서브 커패시터의 제1 유전층을 형성하는 층과 동일한 층으로부터 형성될 수 있다. 상기 어레이 기판이 상기 게이트 전극 위에 형성되는 게이트 절연층을 더 포함하는 경우, 상기 제1 서브 커패시터의 제1 유전층 및 상기 제1 중간층은 상기 게이트 절연층을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제1 패드는 상기 제1 중간층을 관통하는 제1 콘택홀을 더 포함하고, 상기 제1 패드 전극과 상기 제1 덮개 전극은 상기 제1 콘택홀에서 서로 접촉할 수 있다.

상기 어레이 기판이 상기 박막 트렌지스터 위에 형성되는 반사 전극을 더 포함하는 경우에는 상기 제2 서브 커패시터의 상부 전극층 및 상기 제3 전압 인가 배 선은 상기 반사 전극을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 어레이 기판은 상기 중간 전극층으로부터 연장된 제2 전압 인가 배선을 더 포함하고, 상기 중간 전극층과 상기 제2 패드는 상기 제2 전압 인가 배선을 통해서 전기적으로 연결될 수 있다. 상기 제2 패드는 상기 제2 전압 인가 배선으로부터 연장된 제2 패드 전극을 포함할 수 있다.

상기 중간 전극층, 상기 제2 전압 인가 배선 및 상기 제2 패드 전극은 상기 박막 트랜지스터의 소스 및 드레인 전극을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제2 패드는 상기 제2 패드 전극 위에 형성되는 제2 덮개 전극을 더 포함할 수 있다. 상기 어레이 기판이 상기 박막 트렌지스터의 드레인 전극과 전기적으로 연결되는 투명 전극을 더 포함하는 경우 상기 제2 덮개 전극은 상기 투명 전극을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

본 발명의 또 다른 실시예에 따른 어레이 기판은 다수의 화소부를 포함하는 표시 영역 및 상기 표시 영역의 외곽에 위치하는 주변 영역을 갖는 기판, 상기 기판의 표시 영역에 형성되고 게이트 전극, 소스 전극 및 드레인 전극을 포함하는 박막 트랜지스터 및 상기 기판의 주변 영역에 형성되고 제1 서브 커패시터, 제2 서브 커패시터 및 컨택부를 포함하는 커패시터를 포함한다.

상기 제1 서브 커패시터는 하부 전극층, 상기 하부 전극층 위에 형성되는 중간 전극층 및 상기 하부 전극층과 상기 중간 전극층 사이에 개재되는 제1 유전층을 갖는 제1 서브 커패시터를 포함한다.

상기 제2 서브 커패시터는 상기 제1 서브 커패시터의 상부에 배치되고, 상기 중간 전극층, 상기 중간 전극층 위에 형성되는 상부 전극층 및 상기 중간 전극층과 상기 상부 전극층 사이에 개재되는 제2 유전층을 갖는 제2 서브 커패시터를 포함한다.

상기 컨택부는 상기 제1 서브 커패시터의 제1 유전층 및 상기 제2 서브 커패시터의 제2 유전층을 관통한다. 여기서, 상기 제1 서브 커패시터의 하부 전극층과 상기 제2 서브 커패시터의 상부 전극층은 상기 콘택부에서 서로 접촉하여 상기 제1 서브 커패시터와 상기 제2 서브 커패시터는 병렬 연결된다.

본 발명에 따른 어레이 기판은 하부에 위치하는 제1 서브 커패시터 및 상부에 위치하는 제2 서브 커패시터가 병렬로 연결되는 구조를 갖는 커패시터를 포함하기 때문에 면적의 증가 없이 상기 커패시터의 용량을 증가시킬 수 있다.

또한, 박막 트랜지스터의 게이트 전극 및 소스/드레인 전극이 형성되는 공정이나 투명 전극 또는 반사 전극이 도포되는 공정이 진행될 때 상기 커패시터의 전극이 형성될 수 있기 때문에 별도의 추가 공정 없이 고용량을 갖는 커패시터를 구현할 수 있다.

이하, 본 발명의 실시예에 따른 액정표시패널에 대해 첨부도면을 참조하여 상세히 설명한다.

도 1은 본 발명의 제1 실시예에 따른 어레이 기판을 개략적으로 나타내는 평면도이고, 도 2는 도 1에 도시된 커패시터 및 화소부를 확대한 평면도이며, 도 3은 도 2에 도시된 Ⅰ-Ⅰ'선에 따라 절단한 단면도이다.

도 1 내지 도 3을 참조하면, 본 발명의 일 실시예에 따른 어레이 기판(500)은 표시 영역(DA)과 주변 영역(PA)을 갖는 기판(100), 상기 기판(100)의 표시 영역(DA)에 형성되는 박막 트랜지스터(210) 및 상기 기판(100)의 주변 영역(PA)에 형성되는 커패시터(300)를 포함한다.

상기 기판(100)의 표시 영역(DA)은 다수의 게이트 라인(260) 및 다수의 데이터 라인(270)에 의해 정의되는 다수의 화소부(200)를 포함한다. 상기 화소부(200)에는 상기 박막 트랜지스터(210)가 상기 화소부(200)들마다 형성된다.

상기 박막 트랜지스터(210)는 상기 게이트 라인(260)에 전기적으로 연결되는 게이트 전극(211), 상기 데이터 라인(270)에 전기적으로 연결되는 소스 전극(213) 및 드레인 전극(214)을 포함한다. 상기 박막 트랜지스터(210)는 상기 소스/드레인 전극(213,214)과 상기 게이트 전극(211) 사이에 형성되는 아모르퍼스(amorphous) 실리콘층(217) 및 n+ 아모르퍼스(amorphous) 실리콘층(218)을 더 포함할 수도 있다.

상기 박막 트랜지스터(210)의 게이트 전극(211) 위에는 게이트 절연층(220)이 형성된다. 상기 게이트 절연층(220)은, 예컨대, 질화 실리콘(SiNx) 또는 산화 실리콘(SiOx)으로 이루어진다. 또한, 상기 박막 트랜지스터(210)의 소스/드레인 전극(213,214) 위에는 패시베이션층(230)이 형성될 수도 있다. 상기 패시베이션층(230)은, 예컨대, 질화 실리콘(SiNx), 산화 실리콘(SiOx) 또는 유기 절연물질로 이루어진다.

상기 표시 영역(DA)의 화소부(200)에는 상기 박막 트랜지스터(210)의 드레인 전극(220)과 전기적으로 연결되는 투명 전극(250)이 도포된다. 상기 투명 전극(250)은, 예컨대, ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide) 또는 ZO(Zinc Oxide)와 같은 투명한 도전성 물질로 이루어진다.

상기 기판(100)의 주변 영역(PA)에는 상기 박막 트랜지스터(210)를 구동하는 구동 회로부(490)가 형성될 수 있다. 본 실시예에서는 상기 구동 회로부(490)가 상기 게이트 라인(260)과 전기적으로 연결되는 게이트 구동부(491) 및 상기 데이터 라인(270)과 전기적으로 연결되는 데이터 구동부(492)로 나뉘어져 있다. 그러나, 다른 실시예에서는 게이트 구동부와 상기 데이터 구동부가 하나의 구동 회로부에 형성될 수도 있다.

상기 기판(100)의 주변 영역(PA)에는 적어도 하나 이상의 커패시터(300)가 형성된다. 상기 커패시터(300)는, 예컨대, 상기 구동 회로부(490) 또는 상기 박막 트랜지스터(210)로 인가되는 전압을 안정화하는 회로에 사용될 수도 있고, 표시패널에 사용되는 전압을 승압하거나 반전(invert)시키는 차지 펌프(charge pump) 회로의 플라잉 커패시터(flying capacitor)로 사용될 수도 있다.

상기 커패시터(300)는 하부에 위치하는 제1 서브 커패시터(310) 및 상기 제1 서브 커패시터(310)의 상부에 위치하는 제2 서브 커패시터(350)를 포함한다.

상기 제1 서브 커패시터(310)는 하부 전극층(311), 상기 하부 전극층(311) 위에 형성되는 중간 전극층(330) 및 상기 하부 전극층(311)과 상기 중간 전극층(330) 사이에 개재되는 제1 유전층(315)을 포함한다.

또한, 상기 제2 서브 커패시터(350)는 상기 중간 전극층(330), 상기 중간 전 극층(330) 위에 형성되는 상부 전극층(351) 및 상기 중간 전극층(330)과 상기 상부 전극층(351) 사이에 개재되는 제2 유전층(355)을 포함한다.

상기 하부 전극층(311), 상기 중간 전극층(330) 및 상기 상부 전극층(351)은, 예컨대, 구리 또는 알루미늄과 같은 금속으로 이루어질 수도 있고, ITO(Indium Tin Oxide) 또는 IZO(Indium Zinc Oxide)와 같은 도전성 산화물로 이루어질 수도 있다.

한편, 별도의 공정이 추가되지 않도록 하기 위하여, 상기 박막 트랜지스터(200)의 게이트 전극(211), 상기 박막 트랜지스터(200)의 소스/드레인 전극(213,214) 또는 상기 투명 전극(250)을 형성하는 공정이 진행될 때에 상기 하부 전극층(311), 상기 중간 전극층(330) 및 상기 상부 전극층(351)을 형성하는 공정이 동시에 진행될 수 있다.

예를 들어, 상기 제1 서브 커패시터(310)의 하부 전극층(311)은 상기 박막 트랜지스터(200)의 게이트 전극(211)을 형성하는 층과 동일한 층으로부터 형성될 수 있고, 상기 중간 전극층(330)은 상기 박막 트랜지스터(200)의 소스 및 드레인 전극(213,214)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

또한, 상기 제2 서브 커패시터(350)의 상부 전극층(351)은 상기 투명 전극(250)을 형성하는 층과 동일한 층으로부터 형성될 수 있다. 만약, 상기 어레이 기판(500)이 반사 전극(미도시)을 더 포함한다면, 상기 제2 서브 커패시터(350)의 상부 전극층(351)은 상기 반사 전극(미도시)을 형성하는 층과 동일한 층으로부터 형성될 수도 있다.

마찬가지로, 별도의 추가 공정 없이 상기 제1 유전층(315) 및 상기 제2 유전층(355)을 형성하기 위해, 상기 제1 서브 커패시터(310)의 제1 유전층(315)은 상기 게이트 절연층(220)을 형성하는 층과 동일한 층으로부터 형성될 수 있고, 상기 제2 서브 커패시터(350)의 제2 유전층(355)은 상기 패시베이션층(230)을 형성하는 층과 동일한 층으로부터 형성될 수도 있다.

상기 어레이 기판(500)은 상기 커패시터(300)에 전압을 인가하기 위해 상기 기판(100)의 주변 영역(PA)에 형성되는 패드부(400)를 더 포함할 수 있다.

본 실시예에서, 상기 패드부(400)는 상기 제1 서브 커패시터(310)의 하부 전극층(311)과 상기 제2 서브 커패시터(350)의 상부 전극층(351)에 전기적으로 연결되는 제1 패드(410) 및 상기 중간 전극층(330)에 전기적으로 연결되는 제2 패드(420)를 포함한다.

상기 제1 패드(410)는 상기 제1 서브 커패시터(310)의 하부 전극층(311)으로부터 연장된 제1 전압 인가 배선(460)을 통해서 상기 하부 전극층(311)과 전기적으로 연결될 수 있다. 그러나, 상기 제1 패드(410)가 상기 하부 전극층(311)과 전기적으로 연결되는 방법은 여기에 한정되지 않는다. 즉, 상기 연결 배선이 반드시 상기 제1 서브 커패시터(310)의 하부 전극층(311)으로부터 연장될 필요는 없고, 상기 제1 패드(410)와 상기 하부 전극층(311)을 전기적으로 연결하는 별도의 배선이 형성될 수도 있다.

상기 제1 패드(410)와 상기 제1 서브 커패시터(310)의 하부 전극층(311)이 상기 하부 전극층(311)으로부터 연장된 제1 전압 인가 배선(460)을 통해서 전기적 으로 연결되는 경우에는, 상기 제1 패드(410)는 상기 제1 전압 인가 배선(460)으로부터 연장된 제1 패드 전극(411)을 포함할 수도 있다. 이에 따라, 상기 제1 서브 커패시터(310)의 하부 전극층(311), 상기 제1 전압 인가 배선(460) 및 상기 제1 패드 전극(411)은 일체로 형성될 수 있다.

상기 하부 전극층(311), 상기 제1 전압 인가 배선(460) 및 상기 제1 패드 전극(411)은, 예컨대, 상기 박막 트랜지스터(210)의 게이트 전극(211)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제1 패드(410)는 상기 제2 서브 커패시터(350)의 상부 전극층(351)으로부터 연장된 제3 전압 인가 배선(480)을 통해서 상기 상부 전극층(351)과 전기적으로 연결될 수도 있다.

상기 제2 서브 커패시터(350)의 상부 전극층(351), 상기 상부 전극층(351)으로부터 연장된 제3 전압 인가 배선(480)은 상기 투명 전극(250)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제1 패드(410)는 상기 제1 패드 전극(411) 위에 형성되는 제1 덮개 전극(415)을 더 포함할 수 있다. 상기 제1 덮개 전극(415)은 상기 제1 패드 전극(411)이 부식되는 것을 방지하거나 상기 제1 패드(410)에 걸리는 저항을 낮추는 역할을 한다.

상기 제1 덮개 전극(415)은, 예컨대, ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide)와 같이 내식성(corrosion-resistance)과 도전성을 동시에 갖는 물질로 이루어지는 것이 바람직하다.

상기 제2 서브 커패시터(350)의 상부 전극층(351), 상기 상부 전극층(351)으로부터 연장된 제3 전압 인가 배선(480)이 상기 투명 전극(250)을 형성하는 층과 동일한 층으로부터 형성될 경우에는 상기 제1 덮개 전극(415)가 상기 제3 전압 인가 배선(480)으로부터 연장되어 형성될 수 있다. 즉, 상기 상부 전극층(351), 상기 제3 전압 인가 배선(480) 및 상기 제1 덮개 전극(415)가 일체로 형성될 수 있다.

상기 제1 패드(410)는 상기 제1 패드 전극(411)과 상기 제1 덮개 전극(415) 사이에 형성되는 제1 중간층(412)을 더 포함할 수 있다. 상기 제1 중간층(412)은 상기 제1 서브 커패시터(310)의 제1 유전층(315)을 형성하는 층과 동일한 층으로부터 형성될 수 있다. 상기 제1 서브 커패시터(310)의 제1 유전층(315) 및 상기 제1 중간층(412)은 상기 게이트 절연층(220)을 형성하는 층과 동일한 층으로부터 형성될 수 있다. 또한, 상기 제1 중간층(412)과 상기 제1 덮개 전극(415) 사이에는 제3 중간층(413)이 더 형성될 수도 있다.

본 실시예에서는 상기 제1 서브 커패시터(310)의 하부 전극층(311)에 전기적으로 연결된 상기 제1 패드(410)의 제1 패드 전극(411)과 상기 제2 서브 커패시터(350)의 상부 전극층(351)에 전기적으로 연결된 상기 제1 패드(410)의 제1 덮개 전극(415)이 상기 제1 중간층(412)을 관통하는 제1 콘택홀(419)에서 서로 접촉하여, 상기 하부 전극층(311)과 상기 상부 전극층(351)이 서로 전기적으로 연결된다.

도 4는 도 2에 도시된 제1 및 제2 서브 커패시터가 병렬 연결된 경우 커패시터의 전기 용량의 증가를 설명하기 위한 개념도이다.

도 4에 도시된 바와 같이, 상기 하부 전극층(311)과 상기 상부 전극층(351) 이 서로 전기적으로 연결되면, 상기 제1 서브 커패시터(310)와 상기 제2 서브 커패시터(350)가 병렬 연결된다.

두 개의 서브 커패시터가 병렬로 연결될 경우, 전체 커패시터의 용량(capacitance)은 각각의 서브 커패시터의 용량의 합과 같다. 즉, 상기 커패시터(300)의 용량은 상기 제1 서브 커패시터(310)의 용량(C1)과 상기 제2 서브 커패시터(350)의 용량(C2)의 합과 같다. 따라서, 본 발명에 따르면, 상기 제1 서브 커패시터(310)위에 상기 제2 서브 커패시터(350)가 위치하고 상기 제1 및 제2 서브 커패시터(310,350)가 병렬 연결되는 구조를 통해서, 면적의 증가 없이 상기 커패시터(300)의 용량을 증가시킬 수 있다.

다시 도 2 및 도 3을 참조하면, 상기 제2 패드(420)는 상기 중간 전극층(330)으로부터 연장된 제2 전압 인가 배선(470)을 통해서 상기 중간 전극층(330)과 전기적으로 연결될 수 있다. 그러나, 상기 제2 패드(420)가 상기 중간 전극층(330)과 전기적으로 연결되는 방법은 여기에 한정되지 않는다. 즉, 상기 연결 배선이 반드시 상기 중간 전극층(330)으로부터 연장될 필요는 없고, 상기 제2 패드(420)와 상기 중간 전극층(330)을 전기적으로 연결하는 별도의 배선이 형성될 수도 있다.

상기 제2 패드(420)와 상기 중간 전극층(330)이 상기 중간 전극층(330)으로부터 연장된 제2 전압 인가 배선(470)을 통해서 전기적으로 연결되는 경우에는, 상기 제2 패드(420)는 상기 제2 전압 인가 배선(470)으로부터 연장된 제2 패드 전극(421)을 포함할 수도 있다. 이에 따라, 상기 중간 전극층(330), 상기 제2 전압 인가 배선(470) 및 상기 제2 패드 전극(421)은 일체로 형성될 수 있다.

상기 중간 전극층(330), 상기 제2 전압 인가 배선(470) 및 상기 제2 패드 전극(421)은, 예컨대, 상기 박막 트랜지스터(210)의 소스 및 드레인 전극(213,214)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제2 패드(420)는 상기 제2 패드 전극(421) 위에 형성되는 제2 덮개 전극(425)을 더 포함할 수 있다. 상기 제2 덮개 전극(425)은 상기 제2 패드 전극(421)이 부식되는 것을 방지하거나 상기 제2 패드(420)에 걸리는 저항을 낮추는 역할을 한다.

상기 제2 덮개 전극(425)은 상기 제1 덮개 전극(415)과 마찬가지로, 예컨대, ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide)와 같이 내식성과 도전성을 동시에 갖는 물질로 이루어지는 것이 바람직하다.

상기 제2 패드(420)는 상기 제2 패드 전극(421)과 상기 제2 덮개 전극(425) 사이에 형성되는 제2 중간층(423)을 더 포함할 수 있다. 상기 제2 중간층(423)은 상기 제2 서브 커패시터(350)의 제2 유전층(355)을 형성하는 층과 동일한 층으로부터 형성될 수 있다. 상기 제2 서브 커패시터(350)의 제2 유전층(355) 및 상기 제2 중간층(423)은 상기 패시베이션층(230)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제2 중간층(423)과 상기 기판(100) 사이에는 제4 중간층(422)이 더 형성될 수도 있다. 또한, 상기 제2 덮개 전극(425)은 상기 제2 패드(420)내에 형성된 제2 콘택홀(429)에서 상기 제2 패드 전극(421)과 접촉할 수도 있다.

도 5는 본 발명의 제2 실시예에 따른 어레이 기판의 커패시터 및 화소부를 확대한 평면도이며, 도 6은 도 5에 도시된 II-II'선에 따라 절단한 단면도이다.

도 5 및 도 6을 참조하면, 본 발명의 제2 실시예에 따른 어레이 기판(600)은 표시 영역과 주변 영역을 갖는 기판(100), 상기 기판(100)의 표시영역에 형성되는 박막 트랜지스터(210) 및 상기 기판(100)의 주변 영역에 형성되는 커패시터(300)를 포함한다.

도 5 및 도 6에 도시된 상기 커패시터(300)가 상기 어레이 기판(600)상에 배치되는 위치는 도 1에 도시된 어레이 기판(500)에 도시된 커패시터(300)가 배치되는 위치와 실질적으로 동일하므로, 상기 커패시터가 형성되는 위치와 관련된 반복되는 설명은 생략한다. 또한, 도 1 내지 도 3에 도시된 어레이 기판(500)의 구성 요소와 유사하거나 실질적으로 동일한 구성 요소에 대해서는 동일한 참조 번호를 사용하고, 반복되는 상세한 설명은 생략하기로 한다.

도 2에 도시된 화소부(200)가 투과형 방식(transmissive type)의 액정표시패널에 적용되는 것인 반면, 도 5에 도시된 화소부(200)는 반사-투과형 방식(transflective type)의 액정표시패널에 적용된다.

상기 화소부(200)는 하부로부터 제공되는 광을 투과시키는 투과창(283) 및 상부로부터 제공되는 광을 반사하는 반사 영역(280)을 포함한다. 도 6에 도시된 화소부(200)는 상기 반사 영역(280)의 단면의 일부를 나타낸다.

상기 화소부(200)의 반사 영역(280)에는 박막 트랜지스터(210)가 형성된다. 상기 박막 트랜지스터(210)는 게이트 전극(211), 소스 전극(213) 및 드레인 전극(214)을 포함한다. 상기 박막 트랜지스터(210)는 상기 소스/드레인 전극(213,214) 과 상기 게이트 전극(211) 사이에 형성되는 아모르퍼스(amorphous) 실리콘층(217) 및 n+ 아모르퍼스(amorphous) 실리콘층(218)을 더 포함할 수도 있다.

상기 박막 트랜지스터(210)의 게이트 전극(211) 위에는 게이트 절연층(220)이 형성되고, 상기 박막 트랜지스터(210)의 소스/드레인 전극(213,214) 위에는 패시베이션층(230)이 형성될 수도 있다.

상기 박막 트랜지스터(210)의 상부에는 유기 절연층(235)이 형성된다. 상기 유기 절연층(235)의 상부면은 반사 효율을 높이기 위해서 물결(wave) 모양으로 패터닝될 수 있다.

상기 유기 절연층(235)의 상면에는 투명하고 도전적인 물질로 이루어진 투명전극(250)이 도포된다. 상기 투명전극 위에는 상부로부터 제공되는 광을 반사하는 반사 전극(255)이 도포된다. 상기 반사 전극(255)은, 예컨대, 몰리브덴(Mo)-알루미늄(Al) 합금, 몰리브덴(Mo)-텅스텐(W) 합금 또는 알루미늄(Al)-네오디뮴(Nd) 합금등으로 이루어진다. 한편, 다른 실시예에서는 상기 유기 절연층(235)의 상면에 투명 전극(250)이 도포되지 않고, 반사 전극(255)이 직접 도포될 수도 있다.

상기 투명 전극(250) 및 상기 반사 전극(255)은 상기 유기 절연층(235)을 관통하는 제3 콘택홀(290)에서 상기 박막 트랜지스터(210)의 드레인 전극(214)과 접촉하여 전기적으로 연결된다.

상기 커패시터(300)는 하부에 위치하는 제1 서브 커패시터(310) 및 상기 제1 서브 커패시터(310)의 상부에 위치하는 제2 서브 커패시터(360)를 포함한다.

상기 제1 서브 커패시터(310)는 하부 전극층(311), 상기 하부 전극층(311) 위에 형성되는 중간 전극층(330) 및 상기 하부 전극층(311)과 상기 중간 전극층(330) 사이에 개재되는 제1 유전층(315)을 포함한다.

또한, 상기 제2 서브 커패시터(360)는 상기 중간 전극층(330), 상기 중간 전극층(330) 위에 형성되는 상부 전극층(361) 및 상기 중간 전극층(330)과 상기 상부 전극층(361) 사이에 개재되는 제2 유전층(365)을 포함한다.

한편, 별도의 공정이 추가되지 않도록 하기 위하여, 상기 박막 트랜지스터(200)의 게이트 전극(211), 상기 박막 트랜지스터(200)의 소스/드레인 전극(213,214), 상기 투명 전극(250) 또는 상기 반사 전극(255)을 형성하는 공정이 진행될 때에 상기 하부 전극층(311), 상기 중간 전극층(330) 및 상기 상부 전극층(361)을 형성하는 공정이 동시에 진행될 수 있다.

예를 들어, 상기 제1 서브 커패시터(310)의 하부 전극층(311)은 상기 박막 트랜지스터(200)의 게이트 전극(211)을 형성하는 층과 동일한 층으로부터 형성될 수 있고, 상기 중간 전극층(330)은 상기 박막 트랜지스터(200)의 소스 및 드레인 전극(213,214)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

본 실시예에서는, 상기 제2 서브 커패시터(360)의 상부 전극층(361)이 상기 반사 전극(255)을 형성하는 층과 동일한 층으로부터 형성된다.

상기 어레이 기판(600)은 상기 제1 서브 커패시터(310)의 하부 전극층(311)과 상기 제2 서브 커패시터(360)의 상부 전극층(361)에 전기적으로 연결되는 제1 패드(410) 및 상기 중간 전극층(330)에 전기적으로 연결되는 제2 패드(420)를 포함한다.

상기 제1 패드(410)는 상기 제1 서브 커패시터(310)의 하부 전극층(311)으로부터 연장된 제1 전압 인가 배선(460)을 통해서 상기 하부 전극층(311)과 전기적으로 연결될 수 있다. 또한, 상기 제1 패드(410)는 상기 제1 전압 인가 배선(460)으로부터 연장된 제1 패드 전극(411)을 포함할 수도 있다. 이때, 상기 하부 전극층(311), 상기 제1 전압 인가 배선(460) 및 상기 제1 패드 전극(411)은, 예컨대, 상기 박막 트랜지스터(210)의 게이트 전극(211)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제1 패드(410)는 상기 제1 패드 전극(411) 위에 형성되는 제1 덮개 전극(415)을 더 포함할 수 있다. 상기 제1 덮개 전극(415)은, 예컨대, ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide)와 같이 내식성(corrosion-resistance)과 도전성을 동시에 갖는 물질로 이루어지는 것이 바람직하다.

상기 제1 패드(410)의 제1 덮개 전극(415)은 상기 제2 서브 커패시터(360)의 상부 전극층(361)으로부터 연장된 제4 전압 인가 배선(485)을 통해서 상기 상부 전극층(361)과 전기적으로 연결될 수도 있다.

예컨대, 상기 제2 서브 커패시터(360)의 상부 전극층(361)이 상기 반사 전극(255)을 형성하는 층과 동일한 층으로부터 형성되는 경우에는, 상기 제4 전압 인가 배선(485)도 상기 반사 전극(255)을 형성하는 층과 동일한 층으로부터 형성된다.

본 실시예에서는, 상기 제1 서브 커패시터(310)의 하부 전극층(311)과 상기 제2 서브 커패시터(360)의 상부 전극층(361)이 상기 제1 패드(410)에 형성된 제1 콘택홀(419)에서 서로 접촉하여 전기적으로 연결된다.

이에 따라, 상기 제1 서브 커패시터(310)와 상기 제2 서브 커패시터(360)가 병렬 연결되기 때문에, 도 4를 통해서 설명한 바와 같이 면적의 증가 없이 상기 커패시터(300)의 용량을 증가시킬 수 있다.

위에서 언급한 사항을 제외하면, 상기 제1 패드(410)의 구조는 도 4에 도시된 제1 패드(410)의 구조와 유사하므로, 반복되는 상세한 설명은 생략한다.

상기 제2 패드(420)는 제2 콘택홀(429)이 형성되지 않은 것을 제외하면, 도 3에 도시된 제2 패드(420)와 실질적으로 동일하므로, 반복되는 상세한 설명은 생략한다. 다만, 상기 제2 패드(420)는 필요에 따라 도 3에 도시된 바와 같이 제2 콘택홀(429)을 포함할 수도 있다.

도 7은 본 발명의 제3 실시예에 따른 어레이 기판의 커패시터 및 화소부를 확대한 평면도이며, 도 8은 도 7에 도시된 III-III'선에 따라 절단한 단면도이다.

도 7 및 도 8을 참조하면, 본 발명의 제3 실시예에 따른 어레이 기판(700)은 표시 영역과 주변 영역을 갖는 기판(100), 상기 기판(100)의 표시영역에 형성되는 박막 트랜지스터(210) 및 상기 기판(100)의 주변 영역에 형성되는 커패시터(300)를 포함한다.

도 7 및 도 8에 도시된 상기 커패시터(300)가 상기 어레이 기판(700)상에 배치되는 위치는 도 1에 도시된 어레이 기판(500)에 도시된 커패시터(300)가 배치되는 위치와 실질적으로 동일하므로, 상기 커패시터가 형성되는 위치와 관련된 반복되는 설명은 생략한다. 또한, 도 1 내지 도 3에 도시된 어레이 기판(500)의 구성 요소와 유사하거나 실질적으로 동일한 구성 요소에 대해서는 동일한 참조 번호를 사용하고, 반복되는 상세한 설명은 생략하기로 한다.

상기 커패시터(300)는 하부에 위치하는 제1 서브 커패시터(310), 상기 제1 서브 커패시터(310)의 상부에 위치하는 제2 서브 커패시터(350)를 포함한다.

상기 제1 서브 커패시터(310)는 하부 전극층(311), 상기 하부 전극층(311) 위에 형성되는 중간 전극층(330) 및 상기 하부 전극층(311)과 상기 중간 전극층(330) 사이에 개재되는 제1 유전층(315)을 포함한다.

또한, 상기 제2 서브 커패시터(350)는 상기 중간 전극층(330), 상기 중간 전극층(330) 위에 형성되는 상부 전극층(351) 및 상기 중간 전극층(330)과 상기 상부 전극층(351) 사이에 개재되는 제2 유전층(355)을 포함한다.

상기 커패시터(300)는 상기 제1 서브 커패시터(310)의 제1 유전층(315) 및 상기 제2 서브 커패시터(350)의 제2 유전층(355)을 관통하는 적어도 하나 이상의 콘택부(390)를 더 포함한다.

본 실시예에서는 상기 콘택부(390)는 상기 커패시터(300)의 외곽에 형성되어 있으나, 본 발명이 여기에 한정되는 것은 아니다. 즉, 상기 콘택부(390)는 상기 커패시터의 내부에 형성될 수도 있다.

상기 제1 서브 커패시터(310)의 하부 전극층(311)과 상기 제2 서브 커패시터(350)의 상부 전극층(351)은 상기 콘택부(390)에서 서로 접촉한다. 이에 따라, 상기 제1 서브 커패시터(310)와 상기 제2 서브 커패시터(50)는 병렬 연결된다. 상기 제1 서브 커패시터(310)와 상기 제2 서브 커패시터(350)가 병렬 연결되기 때문에, 도 4를 통해서 설명한 바와 같이 면적의 증가 없이 상기 커패시터(300)의 용량을 증가시킬 수 있다.

한편, 별도의 공정이 추가되지 않도록 하기 위하여, 상기 박막 트랜지스터(200)의 게이트 전극(211), 상기 박막 트랜지스터(200)의 소스/드레인 전극(213,214), 상기 투명 전극(250) 또는 상기 반사 전극(255)을 형성하는 공정이 진행될 때에 상기 하부 전극층(311), 상기 중간 전극층(330) 및 상기 상부 전극층(351)을 형성하는 공정이 동시에 진행될 수 있다.

예를 들어, 상기 제1 서브 커패시터(310)의 하부 전극층(311)은 상기 박막 트랜지스터(200)의 게이트 전극(211)을 형성하는 층과 동일한 층으로부터 형성될 수 있고, 상기 중간 전극층(330)은 상기 박막 트랜지스터(200)의 소스 및 드레인 전극(213,214)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

또한, 상기 제2 서브 커패시터(350)의 상부 전극층(351)은 상기 투명 전극(250)을 형성하는 층과 동일한 층으로부터 형성될 수 있다. 만약, 상기 어레이 기판(500)이 반사 전극(미도시)을 더 포함한다면, 상기 제2 서브 커패시터(350)의 상부 전극층(351)은 상기 반사 전극(미도시)을 형성하는 층과 동일한 층으로부터 형성될 수도 있다.

상기 어레이 기판(700)은 상기 제1 서브 커패시터(310)의 하부 전극층(311)과 전기적으로 연결되는 제1 패드(410) 및 상기 중간 전극층(330)에 전기적으로 연결되는 제2 패드(420)를 포함한다.

상기 제1 패드(410)는 상기 제1 서브 커패시터(310)의 하부 전극층(311)으로부터 연장된 제1 전압 인가 배선(460)을 통해서 상기 하부 전극층(311)과 전기적으 로 연결될 수 있다. 또한, 상기 제1 패드(410)는 상기 제1 전압 인가 배선(460)으로부터 연장된 제1 패드 전극(411)을 포함할 수도 있다. 이때, 상기 하부 전극층(311), 상기 제1 전압 인가 배선(460) 및 상기 제1 패드 전극(411)은, 예컨대, 상기 박막 트랜지스터(210)의 게이트 전극(211)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제2 패드(410)는 상기 제2 서브 커패시터(310)의 상부 전극층(351)으로부터 연장된 제2 전압 인가 배선(470)을 통해서 상기 상부 전극층(351)과 전기적으로 연결될 수 있다. 또한, 상기 제2 패드(410)는 상기 제2 전압 인가 배선(470)으로부터 연장된 제2 패드 전극(421)을 포함할 수도 있다. 이때, 상기 상부 전극층(351), 상기 제2 전압 인가 배선(470) 및 상기 제2 패드 전극(421)은, 예컨대, 상기 박막 트랜지스터(210)의 소스 및 드레인 전극(213,214)을 형성하는 층과 동일한 층으로부터 형성될 수 있다.

상기 제1 패드(410)는 상기 제1 패드 전극(411) 위에 형성되는 제1 덮개 전극(415)을 더 포함할 수 있고, 상기 제2 패드(420)는 상기 제2 패드 전극(421) 위에 형성되는 제2 덮개 전극(425)을 더 포함할 수 있다.

상기 제1 및 제2 덮개 전극(415,425)은 상기 제1 및 제2 패드 전극(411,421)이 부식되는 것을 방지하거나 상기 제1 및 제2 패드(410,420)에 걸리는 저항을 낮추는 역할을 한다.

상기 제1 및 제2 덮개 전극(415,425)은, 예컨대, ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide)와 같이 내식성(corrosion-resistance)과 도전성을 동시에 갖는 물질로 이루어지는 것이 바람직하다.

상술한 바와 같이 본 발명에 따른 어레이 기판은 하부에 위치하는 제1 서브 커패시터 및 상부에 위치하는 제1 서브 커패시터가 병렬로 연결되는 구조를 갖는 커패시터를 포함하기 때문에 면적의 증가 없이 상기 커패시터의 용량을 증가시킬 수 있다.

또한, 박막 트랜지스터의 게이트 전극 및 소스/드레인 전극이 형성되는 공정이나 투명 전극 또는 반사 전극이 도포되는 공정이 진행될 때 상기 제1 및 제2 서브 커패시터의 각각의 전극들이 형성될 수 있기 때문에 별도의 추가 공정 없이 고용량을 갖는 커패시터를 구현할 수 있다.

본 발명은 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

Claims (43)

- 다수의 화소부를 포함하는 표시 영역 및 상기 표시 영역의 외곽에 위치하는 주변 영역을 갖는 기판;상기 기판의 표시 영역에 형성되고, 게이트 전극, 소스 전극 및 드레인 전극을 포함하는 박막 트랜지스터; 및상기 기판의 주변 영역에 형성되고,하부 전극층, 상기 하부 전극층 위에 형성되는 중간 전극층 및 상기 하부 전극층과 상기 중간 전극층 사이에 개재되는 제1 유전층을 갖는 제1 서브 커패시터; 및상기 제1 서브 커패시터의 상부에 배치되고, 상기 중간 전극층, 상기 중간 전극층 위에 형성되는 상부 전극층 및 상기 중간 전극층과 상기 상부 전극층 사이에 개재되는 제2 유전층을 갖는 제2 서브 커패시터를 포함하는 커패시터를 포함하는 어레이 기판.

- 제1항에 있어서, 상기 제1 서브 커패시터의 하부 전극층은 상기 박막 트랜지스터의 게이트 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제2항에 있어서, 상기 중간 전극층은 상기 박막 트랜지스터의 소스 및 드레 인 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제3항에 있어서, 상기 박막 트랜지스터의 게이트 전극 위에 형성되는 게이트 절연층을 더 포함하고, 상기 제1 서브 커패시터의 제1 유전층은 상기 게이트 절연층을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제3항에 있어서, 상기 박막 트랜지스터의 드레인 전극과 전기적으로 연결되는 투명 전극을 더 포함하고, 상기 제2 서브 커패시터의 상부 전극층은 상기 투명 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제5항에 있어서, 상기 박막 트랜지스터의 소스 및 드레인 전극 위에 형성되는 패시베이션층을 더 포함하고, 상기 제2 서브 커패시터의 제2 유전층은 상기 패시베이션층을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제3항에 있어서, 상기 박막 트랜지스터 위에 형성되는 반사 전극을 더 포함하고, 상기 제2 서브 커패시터의 상부 전극층은 상기 반사 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제1항에 있어서, 상기 제1 서브 커패시터의 하부 전극층과 상기 제2 서브 커패시터의 상부 전극층은 전기적으로 연결되어 상기 제1 서브 커패시터 및 상기 제2 서브 커패시터가 병렬 연결되는 것을 특징으로 하는 어레이 기판.

- 다수의 화소부를 포함하는 표시 영역 및 상기 표시 영역의 외곽에 위치하는 주변 영역을 갖는 기판;상기 기판의 표시 영역에 형성되고, 게이트 전극, 소스 전극 및 드레인 전극을 포함하는 박막 트랜지스터;상기 기판의 주변 영역에 형성되고, 제1 서브 커패시터 및 상기 제1 서브 커패시터의 상부에 배치되는 제2 서브 커패시터를 포함하는 커패시터; 및상기 커패시터에 전압을 인가하기 위해 상기 기판의 주변 영역에 형성되는 패드부를 포함하는 어레이 기판.

- 제9항에 있어서, 상기 제1 서브 커패시터는 하부 전극층, 상기 하부 전극층 위에 형성되는 중간 전극층 및 상기 하부 전극층과 상기 중간 전극층 사이에 개재되는 제1 유전층을 포함하는 것을 특징으로 하는 어레이 기판.

- 제10항에 있어서, 상기 제2 서브 커패시터는 상기 중간 전극층, 상기 중간 전극층 위에 형성되는 상부 전극층 및 상기 중간 전극층과 상기 상부 전극층 사이 에 개재되는 제2 유전층을 포함하는 것을 특징으로 하는 어레이 기판.

- 제11항에 있어서, 상기 패드부는 상기 제1 서브 커패시터의 하부 전극층과 상기 제2 서브 커패시터의 상부 전극층에 전기적으로 연결되는 제1 패드 및 상기 중간 전극층에 전기적으로 연결되는 제2 패드를 포함하는 것을 특징으로 하는 어레이 기판.

- 제12항에 있어서, 상기 제1 서브 커패시터의 하부 전극층과 상기 제2 서브 커패시터의 상부 전극층은 상기 제1 패드에서 전기적으로 연결되어 상기 제1 서브 커패시터 및 상기 제2 서브 커패시터가 병렬 연결되는 것을 특징으로 하는 어레이 기판.

- 제13항에 있어서, 상기 제1 서브 커패시터의 하부 전극층으로부터 연장된 제1 전압 인가 배선을 더 포함하고, 상기 하부 전극층과 상기 제1 패드는 상기 제1 전압 인가 배선을 통해서 전기적으로 연결되는 것을 특징으로 하는 어레이 기판.

- 제14항에 있어서, 상기 제1 패드는 상기 제1 전압 인가 배선으로부터 연장된 제1 패드 전극을 포함하는 것을 특징으로 하는 어레이 기판.

- 제15항에 있어서, 상기 제1 서브 커패시터의 하부 전극층, 상기 제1 전압 인 가 배선 및 상기 제1 패드 전극은 상기 박막 트랜지스터의 게이트 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제15항에 있어서, 상기 제2 서브 커패시터의 상부 전극층으로부터 연장된 제3 전압 인가 배선을 더 포함하는 것을 특징으로 하는 어레이 기판.

- 제17항에 있어서, 상기 제1 패드는 상기 제3 전압 인가 배선으로부터 연장된 제1 덮개 전극을 더 포함하는 것을 특징으로 하는 어레이 기판.

- 제18항에 있어서, 상기 박막 트랜지스터의 드레인 전극과 전기적으로 연결되는 투명 전극을 더 포함하고, 상기 제2 서브 커패시터의 상부 전극층, 상기 제3 전압 인가 배선 및 상기 제1 덮개 전극은 상기 투명 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제18항에 있어서, 상기 제1 패드는 상기 제1 패드 전극과 상기 제1 덮개 전극사이에 개재되는 제1 중간층을 더 포함하는 것을 특징으로 하는 어레이 기판.

- 제20항에 있어서, 상기 제1 중간층은 상기 제1 서브 커패시터의 제1 유전층을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제21항에 있어서, 상기 게이트 전극 위에 형성되는 게이트 절연층을 더 포함하고, 상기 제1 서브 커패시터의 제1 유전층 및 상기 제1 중간층은 상기 게이트 절연층을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제20항에 있어서, 상기 제1 패드는 상기 제1 중간층을 관통하는 제1 콘택홀을 더 포함하고, 상기 제1 패드 전극과 상기 제1 덮개 전극은 상기 제1 콘택홀에서 서로 접촉하는 것을 특징으로 하는 어레이 기판.

- 제17항에 있어서, 상기 박막 트랜지스터 위에 형성되는 반사 전극을 더 포함하고, 상기 제2 서브 커패시터의 상부 전극층 및 상기 제3 전압 인가 배선은 상기 반사 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제13항에 있어서, 상기 중간 전극층으로부터 연장된 제2 전압 인가 배선을 더 포함하고, 상기 중간 전극층과 상기 제2 패드는 상기 제2 전압 인가 배선을 통해서 전기적으로 연결되는 것을 특징으로 하는 어레이 기판.

- 제25항에 있어서, 상기 제2 패드는 상기 제2 전압 인가 배선으로부터 연장된 제2 패드 전극을 포함하는 것을 특징으로 하는 어레이 기판.

- 제26항에 있어서, 상기 중간 전극층, 상기 제2 전압 인가 배선 및 상기 제2 패드 전극은 상기 박막 트랜지스터의 소스 및 드레인 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제27항에 있어서, 상기 제2 패드는 상기 제2 패드 전극 위에 형성되는 제2 덮개 전극을 더 포함하는 것을 특징으로 하는 어레이 기판.

- 제28항에 있어서, 상기 박막 트랜지스터의 드레인 전극과 전기적으로 연결되는 투명 전극을 더 포함하고, 상기 제2 덮개 전극은 상기 투명 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 다수의 화소부를 포함하는 표시 영역 및 상기 표시 영역의 외곽에 위치하는 주변 영역을 갖는 기판;상기 기판의 표시 영역에 형성되고, 게이트 전극, 소스 전극 및 드레인 전극을 포함하는 박막 트랜지스터; 및상기 기판의 주변 영역에 형성되고,하부 전극층, 상기 하부 전극층 위에 형성되는 중간 전극층 및 상기 하부 전극층과 상기 중간 전극층 사이에 개재되는 제1 유전층을 갖는 제1 서브 커패시터;상기 제1 서브 커패시터의 상부에 배치되고, 상기 중간 전극층, 상기 중간 전극층 위에 형성되는 상부 전극층 및 상기 중간 전극층과 상기 상부 전극층 사이에 개재되는 제2 유전층을 갖는 제2 서브 커패시터; 및상기 제1 서브 커패시터의 제1 유전층 및 상기 제2 서브 커패시터의 제2 유전층을 관통하는 콘택부를 포함하는 커패시터를 포함하고,상기 제1 서브 커패시터의 하부 전극층과 상기 제2 서브 커패시터의 상부 전극층은 상기 콘택부에서 서로 접촉하여 상기 제1 서브 커패시터와 상기 제2 서브 커패시터는 병렬 연결되는 것을 특징으로 하는 어레이 기판.

- 제30항에 있어서, 상기 제1 서브 커패시터의 하부 전극층은 상기 박막 트랜지스터의 게이트 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제31항에 있어서, 상기 중간 전극층은 상기 박막 트랜지스터의 소스 및 드레인 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제32항에 있어서, 상기 박막 트랜지스터의 드레인 전극과 전기적으로 연결되는 투명 전극을 더 포함하고, 상기 제2 서브 커패시터의 상부 전극층은 상기 투명 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기 판.

- 제32항에 있어서, 상기 박막 트랜지스터 위에 형성되는 반사 전극을 더 포함하고, 상기 제2 서브 커패시터의 상부 전극층은 상기 반사 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제30항에 있어서, 상기 제1 서브 커패시터의 하부 전극층과 전기적으로 연결되는 제1 패드 및 상기 중간 전극층과 전기적으로 연결되는 제2 패드를 더 포함하는 것을 특징으로 하는 어레이 기판.

- 제31항에 있어서, 상기 하부 전극층으로부터 연장된 제1 전압 인가 배선을 더 포함하고, 상기 하부 전극층과 상기 제1 패드는 제1 전압 인가 배선을 통해서 전기적으로 연결되는 것을 특징으로 하는 어레이 기판.

- 제36항에 있어서, 상기 제1 패드는 상기 제1 전압 인가 배선으로부터 연장된 제1 패드 전극을 포함하는 것을 특징으로 하는 어레이 기판.

- 제37항에 있어서, 상기 하부 전극층, 상기 제1 전압 인가 배선 및 상기 제1 패드 전극은 상기 박막 트랜지스터의 게이트 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제38항에 있어서, 상기 제1 패드는 상기 제1 패드 전극 위에 형성되는 제1 덮개 전극을 더 포함하는 것을 특징으로 하는 어레이 기판.

- 제35항에 있어서, 상기 어레이 기판은 상기 중간 전극층으로부터 연장된 제2 전압 인가 배선을 더 포함하고, 상기 중간 전극층과 상기 제2 패드는 상기 제2 전압 인가 배선을 통해서 전기적으로 연결되는 것을 특징으로 하는 어레이 기판.

- 제40항에 있어서, 상기 제2 패드는 상기 제2 전압 인가 배선으로부터 연장된 제2 패드 전극을 포함하는 것을 특징으로 하는 어레이 기판.

- 제41항에 있어서, 상기 중간 전극층, 상기 제2 전압 인가 배선 및 상기 제2 패드 전극은 상기 박막 트랜지스터의 소스 및 드레인 전극을 형성하는 층과 동일한 층으로부터 형성되는 것을 특징으로 하는 어레이 기판.

- 제41항에 있어서, 상기 제2 패드는 상기 제2 패드 전극 위에 형성되는 제2 덮개 전극을 더 포함하는 것을 특징으로 하는 어레이 기판.

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060016063A KR20070082956A (ko) | 2006-02-20 | 2006-02-20 | 액정표시패널용 어레이 기판 |

| US11/652,838 US20070194313A1 (en) | 2006-02-20 | 2007-01-12 | Array substrate for liquid crystal display panel |

| CNA2007100067656A CN101025532A (zh) | 2006-02-20 | 2007-02-06 | 液晶显示面板的阵列基板 |

| JP2007036657A JP2007226225A (ja) | 2006-02-20 | 2007-02-16 | アレイ基板 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060016063A KR20070082956A (ko) | 2006-02-20 | 2006-02-20 | 액정표시패널용 어레이 기판 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20070082956A true KR20070082956A (ko) | 2007-08-23 |

Family

ID=38427282

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020060016063A KR20070082956A (ko) | 2006-02-20 | 2006-02-20 | 액정표시패널용 어레이 기판 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20070194313A1 (ko) |

| JP (1) | JP2007226225A (ko) |

| KR (1) | KR20070082956A (ko) |

| CN (1) | CN101025532A (ko) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101303500B (zh) * | 2008-07-08 | 2010-04-14 | 友达光电股份有限公司 | 液晶显示面板及液晶显示面板的制作方法 |

| TWI457676B (zh) * | 2011-12-09 | 2014-10-21 | Au Optronics Corp | 畫素結構及其製造方法 |

| CN103094295B (zh) | 2013-01-23 | 2016-05-25 | 北京京东方光电科技有限公司 | 平板探测器及其制作方法、摄像装置 |

| CN104716154B (zh) * | 2013-12-11 | 2018-12-18 | 昆山国显光电有限公司 | 一种有机发光显示装置及其制备方法 |

| CN103943634A (zh) * | 2014-03-17 | 2014-07-23 | 京东方科技集团股份有限公司 | 阵列基板、显示装置及其电容结构 |

| KR102545253B1 (ko) * | 2015-05-28 | 2023-06-19 | 엘지디스플레이 주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR20180076688A (ko) * | 2016-12-28 | 2018-07-06 | 엘지디스플레이 주식회사 | 표시 장치 |

| JP2019066719A (ja) * | 2017-10-03 | 2019-04-25 | シャープ株式会社 | 表示パネル |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002040486A (ja) * | 2000-05-19 | 2002-02-06 | Seiko Epson Corp | 電気光学装置、その製造方法および電子機器 |

| US7760317B2 (en) * | 2003-10-14 | 2010-07-20 | Lg Display Co., Ltd. | Thin film transistor array substrate and fabricating method thereof, liquid crystal display using the same and fabricating method thereof, and method of inspecting liquid crystal display |

| US7038259B2 (en) * | 2003-10-22 | 2006-05-02 | Micron Technology, Inc. | Dual capacitor structure for imagers and method of formation |

-

2006

- 2006-02-20 KR KR1020060016063A patent/KR20070082956A/ko not_active Application Discontinuation

-

2007

- 2007-01-12 US US11/652,838 patent/US20070194313A1/en not_active Abandoned

- 2007-02-06 CN CNA2007100067656A patent/CN101025532A/zh active Pending

- 2007-02-16 JP JP2007036657A patent/JP2007226225A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US20070194313A1 (en) | 2007-08-23 |

| CN101025532A (zh) | 2007-08-29 |

| JP2007226225A (ja) | 2007-09-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10338443B2 (en) | Amorphous silicon thin film transistor-liquid crystal display device and method of manufacturing the same | |

| US7855767B2 (en) | Transflective liquid crystal display | |

| KR100567690B1 (ko) | 액정표시장치 | |

| US7787066B2 (en) | Display panel, display apparatus having the same, and method of manufacturing the same | |

| US7636145B2 (en) | Display apparatus and method of manufacturing the same | |

| KR20070082956A (ko) | 액정표시패널용 어레이 기판 | |

| US20130148072A1 (en) | Narrow bezel-type liquid crystal display device | |

| KR20040024666A (ko) | 액정 표시 장치 및 이의 제조방법 | |

| US6839120B2 (en) | Reflective or transflective liquid crystal display device and method for manufacturing the same | |

| US7535520B2 (en) | Thin film transistor array panel for liquid crystal display | |

| US20140146260A1 (en) | Display device | |

| KR20120061129A (ko) | 표시 장치 | |

| US9472579B2 (en) | Array substrate with improved pad region | |

| JP2018025671A (ja) | 表示装置 | |

| KR101389923B1 (ko) | 고개구율 어레이 기판, 액정 표시 장치 및 이들의 제조방법 | |

| KR101376067B1 (ko) | 표시기판, 이를 갖는 표시패널 및 이의 구동방법 | |

| US7838879B2 (en) | Array substrate having enhanced aperture ratio, method of manufacturing the same and display device having the same | |

| US20060158577A1 (en) | Thin film transistor array panel for liquid crystal display and liquid crystal display | |

| JP2008090147A (ja) | 接続端子基板及びこれを用いた電子装置 | |

| EP3961713A1 (en) | Display device and method for providing the same | |

| KR100947536B1 (ko) | 박막 트랜지스터-액정표시장치 | |

| KR20090067420A (ko) | 액정표시장치 및 그 제조방법 | |

| KR20080001191A (ko) | 박막 트랜지스터 어레이 기판 및 그 제조방법 | |

| KR20040098869A (ko) | 액정표시장치의 패드구조 | |

| KR20060014328A (ko) | 표시패널 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |