KR101841930B1 - Method of spreading a plurality of interrupts, interrupt spreader, and system on-chip having the same - Google Patents

Method of spreading a plurality of interrupts, interrupt spreader, and system on-chip having the same Download PDFInfo

- Publication number

- KR101841930B1 KR101841930B1 KR1020120008822A KR20120008822A KR101841930B1 KR 101841930 B1 KR101841930 B1 KR 101841930B1 KR 1020120008822 A KR1020120008822 A KR 1020120008822A KR 20120008822 A KR20120008822 A KR 20120008822A KR 101841930 B1 KR101841930 B1 KR 101841930B1

- Authority

- KR

- South Korea

- Prior art keywords

- interrupt

- interrupt request

- processors

- nirq

- request signal

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/48—Program initiating; Program switching, e.g. by interrupt

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/3243—Power saving in microcontroller unit

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/3287—Power saving characterised by the action undertaken by switching off individual functional units in the computer system

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/24—Handling requests for interconnection or transfer for access to input/output bus using interrupt

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/48—Program initiating; Program switching, e.g. by interrupt

- G06F9/4806—Task transfer initiation or dispatching

- G06F9/4812—Task transfer initiation or dispatching by interrupt, e.g. masked

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/50—Allocation of resources, e.g. of the central processing unit [CPU]

- G06F9/5094—Allocation of resources, e.g. of the central processing unit [CPU] where the allocation takes into account power or heat criteria

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D30/00—Reducing energy consumption in communication networks

- Y02D30/50—Reducing energy consumption in communication networks in wire-line communication networks, e.g. low power modes or reduced link rate

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Software Systems (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- Bus Control (AREA)

- Power Sources (AREA)

- Microcomputers (AREA)

Abstract

인터럽트 스프레드 방법은 복수의 인터럽트 요청 신호들을 수신하고, 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 작은지 여부를 판단하며, 상기 시간 간격이 기 설정된 간격보다 작은 경우 상기 시간 간격을 기 설정된 간격으로 조절하고, 인터럽트 요청 신호들을 복수의 프로세서들에 각각 출력할 수 있다. 이에, 인터럽트 스프레드 방법은 짧은 시간 내에 연속적으로 생성되는 인터럽트들에 의하여 프로세서들이 급작스러운 웨이크-업을 하는 것을 방지할 수 있다.The interrupt spread method includes receiving a plurality of interrupt request signals, determining whether each time interval between interrupt request signals is less than a predetermined interval, and if the time interval is smaller than the predetermined interval, And output the interrupt request signals to the plurality of processors, respectively. Thus, the interrupt spread method can prevent processors from suddenly waking up due to interrupts generated continuously in a short time.

Description

본 발명은 멀티 프로세서 시스템(또는, 멀티 코어 시스템)에 관한 것으로서, 더욱 상세하게는 복수의 인터럽트 소스들에서 생성되는 복수의 인터럽트들에 대한 인터럽트 스프레드 방법, 인터럽트 스프레드 장치 및 이를 구비하는 시스템 온-칩에 관한 것이다.The present invention relates to a multiprocessor system (or multicore system), and more particularly, to an interrupt spread method for a plurality of interrupts generated in a plurality of interrupt sources, an interrupt spread device, and a system on- .

일반적으로, 전자 기기는 인터럽트 처리를 위한 인터럽트 컨트롤러를 구비하고, 인터럽트 소스들이 복수의 인터럽트들을 생성하면, 인터럽트들에 우선순위를 부여하여 프로세서에 출력할 수 있다. 최근에는 전자 기기의 소형화 및 경량화 추세에 따라 시스템 온-칩(System On-Chip; SOC)이 널리 사용되고, 시스템 온-칩에는 모듈 형태의 복수의 아이피(Intellectual Property; IP)들 및 복수의 프로세서들(또는, 복수의 코어(core)들을 가진 프로세서)이 실장될 수 있다.Generally, an electronic device has an interrupt controller for interrupt processing, and when the interrupt sources generate a plurality of interrupts, the interrupts can be prioritized and output to the processor. In recent years, system on-chip (SOC) has been widely used in accordance with the trend of downsizing and lightening of electronic devices, and a plurality of Intellectual Property (IP) (Or a processor having a plurality of cores) can be mounted.

한편, 시스템 온-칩에 실장되는 복수의 프로세서들은 전력 소모를 줄이기 위하여 저전력 모드로 빈번하게 진입을 하게 되고, 인터럽트 소스들로부터 인터럽트들이 생성되어 인터럽트 요청 신호가 입력되면 저전력 모드에서 각각 탈출할 수 있다. 이 때, 시스템 온-칩에 실장되는 복수의 프로세서들이 저전력 모드에서 동시에 탈출하게 되는 경우, 급작스러운 웨이크-업(wake-up)으로 인하여 상기 프로세서들 내부에 인러쉬 전류(in-rush current)가 생성될 수 있다.On the other hand, a plurality of processors mounted on the system on-chip frequently enter the low-power mode to reduce power consumption, and when interrupts are generated from the interrupt sources and an interrupt request signal is input, . In this case, when a plurality of processors mounted on the system-on-chip are simultaneously escaping in the low power mode, an in-rush current is generated in the processors due to sudden wake-up Lt; / RTI >

본 발명의 일 목적은 복수의 인터럽트 소스들에서 짧은 시간 내에 연속적으로 생성되는 복수의 인터럽트들에 의하여 인액티브 상태(예를 들어, 파워 다운 상태, 파워 오프 상태 등)에 있는 복수의 프로세서들(또는, 멀티 코어 프로세서의 복수의 코어들)이 짧은 시간 내에 액티브 상태(예를 들어, 파워 온 상태 등)로 연속적으로 변경되는 것(즉, 급작스러운 웨이크-업)을 방지할 수 있는 인터럽트 스프레드 방법을 제공하는 것이다.It is an object of the present invention to provide a system and method for a plurality of processors (or processors) in an inactive state (e.g., a power down state, a power off state, etc.) by a plurality of interrupts consecutively generated in a short time in a plurality of interrupt sources (I.e., a sudden wake-up) in a short period of time (for example, a plurality of cores of a multi-core processor), an active state .

본 발명의 다른 목적은 복수의 인터럽트 소스들에서 짧은 시간 내에 연속적으로 생성되는 복수의 인터럽트들에 의하여 인액티브 상태(예를 들어, 파워 다운 상태, 파워 오프 상태 등)에 있는 복수의 프로세서들(또는, 멀티 코어 프로세서의 복수의 코어들)이 짧은 시간 내에 액티브 상태(예를 들어, 파워 온 상태 등)로 연속적으로 변경되는 것(즉, 급작스러운 웨이크-업)을 방지할 수 있는 인터럽트 스프레드 장치를 제공하는 것이다.It is another object of the present invention to provide a system and method for a plurality of processors (or processors) in an inactive state (e.g., a power down state, a power off state, etc.) by a plurality of interrupts consecutively generated in a short time in a plurality of interrupt sources , An interrupt spread device capable of preventing continuous change (i.e., abrupt wake-up) of an active state (e.g., a plurality of cores of a multicore processor) in an active state .

본 발명의 또 다른 목적은 상기 인터럽트 스프레드 장치를 구비하는 시스템 온-칩을 제공하는 것이다.It is still another object of the present invention to provide a system on-chip having the interrupt spread device.

다만, 본 발명의 해결하고자 하는 과제는 상기 언급된 과제에 한정되는 것이 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.It is to be understood, however, that the present invention is not limited to the above-described embodiments and various modifications may be made without departing from the spirit and scope of the invention.

본 발명의 일 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 인터럽트 스프레드 방법은 복수의 인터럽트 요청 신호들을 수신하는 단계, 상기 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 작은지 여부를 판단하는 단계, 상기 시간 간격이 상기 기 설정된 간격보다 작은 경우 상기 시간 간격을 상기 기 설정된 간격으로 조절하는 단계, 및 상기 인터럽트 요청 신호들을 복수의 프로세서들에 각각 출력하는 단계를 포함할 수 있다.According to an aspect of the present invention, there is provided an interrupt spread method including receiving a plurality of interrupt request signals, determining whether each of the interrupt request signals is less than a predetermined interval Adjusting the time interval to a predetermined interval when the time interval is smaller than the preset interval, and outputting the interrupt request signals to the plurality of processors, respectively .

일 실시예에 의하면, 상기 인터럽트 요청 신호들은 복수의 인터럽트 소스(source)들로부터 출력되는 복수의 인터럽트들에 기초하여 생성되고, 상기 인터럽트 요청 신호들 각각은 상기 프로세서들에 각각 할당될 수 있다.According to one embodiment, the interrupt request signals are generated based on a plurality of interrupts output from a plurality of interrupt sources, and each of the interrupt request signals may be respectively assigned to the processors.

일 실시예에 의하면, 상기 기 설정된 간격은 상기 프로세서들이 인액티브(inactive) 상태에서 액티브(active) 상태로 변경될 때, 상기 프로세서들 내부에 인러쉬 전류가 생성되지 않는 범위 내에서 결정될 수 있다.According to one embodiment, the predetermined interval may be determined within a range in which an inrush current is not generated in the processors when the processors are changed from an inactive state to an active state.

일 실시예에 의하면, 상기 기 설정된 간격으로 조절하는 단계는 제 k(단, k는 1이상인 정수) 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 제 k 시간 간격이 0보다 큰 경우, 상기 제 k 시간 간격이 상기 기 설정된 간격으로 될 때까지 상기 제 k+1 인터럽트 요청 신호의 출력을 지연시키는 단계를 포함할 수 있다.According to an embodiment of the present invention, the step of adjusting at the predetermined interval may include: when kth time interval between the k-th (k is an integer equal to or greater than 1) interrupt request signal and the (k + And delaying the output of the (k + 1) -th interrupt request signal until the k-th time interval becomes the predetermined interval.

일 실시예에 의하면, 상기 기 설정된 간격으로 조절하는 단계는 기 설정된 우선순위에 따라 상기 인터럽트 요청 신호들의 출력 순서를 변경하는 단계를 더 포함할 수 있다.According to an embodiment of the present invention, the adjusting step may further include changing an output order of the interrupt request signals according to a predetermined priority.

일 실시예에 의하면, 상기 기 설정된 간격으로 조절하는 단계는 상기 제 k 시간 간격이 0인 경우, 상기 기 설정된 우선순위에 따라 상기 제 k 인터럽트 요청 신호와 상기 제 k+1 인터럽트 요청 신호 중에서 하나의 출력을 상기 기 설정된 간격만큼 지연시키는 단계를 더 포함할 수 있다.According to an embodiment of the present invention, when the k-th time interval is 0, the controlling of the k-th interrupt request signal and the (k + 1) And delaying the output by the predetermined interval.

본 발명의 일 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 인터럽트 스프레드 방법은 복수의 인터럽트 요청 신호들을 수신하는 단계, 상기 인터럽트 요청 신호들이 각각 출력될 복수의 프로세서들을 액티브(active) 상태인 프로세서들과 인액티브(inactive) 상태인 프로세서들로 분류하는 단계, 상기 인터럽트 요청 신호들 중에서 상기 액티브 상태인 프로세서들에 출력될 비대상(non-target) 인터럽트 요청 신호들을 상기 액티브 상태인 프로세서들에 각각 출력하는 단계, 상기 인터럽트 요청 신호들 중에서 상기 인액티브 상태인 프로세서들에 출력될 대상(target) 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 작은지 여부를 판단하는 단계, 상기 시간 간격이 상기 기 설정된 간격보다 작은 경우 상기 시간 간격을 상기 기 설정된 간격으로 조절하는 단계, 및 상기 대상 인터럽트 요청 신호들을 상기 인액티브 상태인 프로세서들에 각각 출력하는 단계를 포함할 수 있다.According to an aspect of the present invention, there is provided an interrupt spread method comprising: receiving a plurality of interrupt request signals; The method of

일 실시예에 의하면, 상기 기 설정된 간격으로 조절하는 단계는 인접하는 제 k(단, k는 1이상인 정수) 대상 인터럽트 요청 신호와 제 k+1 대상 인터럽트 요청 신호 사이의 제 k 시간 간격이 0보다 큰 경우, 상기 제 k 시간 간격이 상기 기 설정된 간격으로 될 때까지 상기 제 k+1 대상 인터럽트 요청 신호의 출력을 지연시키는 단계를 포함할 수 있다.According to an embodiment of the present invention, the step of adjusting at the predetermined interval may include a step of setting a k-th time interval between the k-th target interrupt request signal and the k-th target interrupt request signal of the k-th contiguous k And if the kth time interval is greater than the predetermined time, delaying the output of the (k + 1) th target interrupt request signal until the kth time interval becomes the predetermined interval.

일 실시예에 의하면, 상기 기 설정된 간격으로 조절하는 단계는 기 설정된 우선순위에 따라 상기 대상 인터럽트 요청 신호들의 출력 순서를 변경하는 단계를 더 포함할 수 있다.According to an embodiment of the present invention, the adjusting step may further include changing an output order of the target interrupt request signals according to a predetermined priority.

일 실시예에 의하면, 상기 기 설정된 간격으로 조절하는 단계는 상기 제 k 시간 간격이 0인 경우, 상기 기 설정된 우선순위에 따라 상기 제 k 대상 인터럽트 요청 신호와 상기 제 k+1 대상 인터럽트 요청 신호 중에서 하나의 출력을 상기 기 설정된 간격만큼 지연시키는 단계를 더 포함할 수 있다.According to an embodiment of the present invention, when the k-th time interval is 0, the controlling of the k-th target interrupt request signal and the (k + 1) th target interrupt request signal And delaying one output by the predetermined interval.

본 발명의 다른 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 인터럽트 스프레드 장치는 제 1 내지 제 m(단, m은 2이상의 정수) 인터럽트 요청 신호들을 수신하고, 상기 제 1 내지 제 m 인터럽트 요청 신호들을 적어도 기 설정된 간격 이상을 두어 제 1 내지 제 m 프로세서들에 각각 출력하는 제 1 내지 제 m 인터럽트 홀더들, 및 상기 제 1 내지 제 m 인터럽트 요청 신호들 중에서 인접하는 인터럽트 요청 신호들 사이의 시간 간격이 상기 기 설정된 간격보다 작은 경우 상기 시간 간격을 상기 기 설정된 간격으로 조절하는 인터럽트 아비터를 포함할 수 있다.According to another aspect of the present invention, there is provided an interrupt spreading apparatus for receiving first to m-th (m is an integer of 2 or more) interrupt request signals, First to m-th interrupt holders for outputting request signals to the first to m-th processors while leaving request signals at least over a predetermined interval, and first to m-th interrupt holders for outputting the interrupt request signals among adjacent interrupt request signals And an interrupt arbiter for adjusting the time interval to a predetermined interval when the time interval is smaller than the predetermined interval.

일 실시예에 의하면, 상기 제 1 내지 제 m 인터럽트 요청 신호들은 복수의 인터럽트 소스들로부터 출력되는 복수의 인터럽트들에 기초하여 생성되고, 상기 제 1 내지 제 m 인터럽트 요청 신호들은 상기 제 1 내지 제 m 인터럽트 홀더들에 각각 수신될 수 있다.According to an embodiment, the first to m-th interrupt request signals are generated based on a plurality of interrupts output from a plurality of interrupt sources, and the first to m-th interrupt request signals are generated by the first to m- Interrupt holders, respectively.

일 실시예에 의하면, 상기 제 1 내지 제 m 인터럽트 홀더들은 상기 제 1 내지 제 m 프로세서들에 각각 연결되고, 상기 제 1 내지 제 m 인터럽트 요청 신호들을 적어도 상기 기 설정된 간격 이상을 두어 상기 제 1 내지 제 m 프로세서들에 각각 출력할 수 있다.According to an embodiment, the first through the m-th interrupt holders are connected to the first through m-th processors, respectively, and the first through m-th interrupt request signals are connected to the first through m- Lt; RTI ID = 0.0 > m processors. ≪ / RTI >

일 실시예에 의하면, 상기 기 설정된 간격은 상기 제 1 내지 제 m 프로세서들이 인액티브 상태에서 액티브 상태로 변경될 때, 상기 제 1 내지 제 m 프로세서들 내부에 인러쉬 전류가 생성되지 않는 범위 내에서 결정될 수 있다.According to an embodiment of the present invention, the predetermined interval is set to a value within a range in which an inrush current is not generated in the first to mth processors when the first to mth processors are changed from an inactive state to an active state Can be determined.

일 실시예에 의하면, 상기 제 1 내지 제 m 인터럽트 홀더들은 상기 제 1 내지 제 m 인터럽트 요청 신호들을 각각 수신하면, 상기 인터럽트 아비터에 출력 요청 신호를 송신하고, 상기 인터럽트 아비터로부터 출력 허가 신호를 수신하면, 상기 제 1 내지 제 m 인터럽트 요청 신호들을 상기 제 1 내지 제 m 프로세서들에 각각 출력할 수 있다.According to an embodiment, when the first to m-th interrupt holders receive the first to m-th interrupt request signals, they transmit an output request signal to the interrupt arbiter, and when they receive the output enable signal from the interrupt arbitrator And output the first to m-th interrupt request signals to the first to m-th processors, respectively.

일 실시예에 의하면, 상기 제 1 내지 제 m 인터럽트 홀더들 각각은 상기 제 1 내지 제 m 인터럽트 요청 신호들이 수신되지 않았음을 나타내는 아이들 스테이트(idle state), 상기 인터럽트 아비터로부터 상기 출력 허가 신호를 기다리고 있음을 나타내는 웨이트 스테이트(wait state) 및 상기 제 1 내지 제 m 인터럽트 요청 신호들이 상기 제 1 내지 제 m 프로세서들에 출력하고 있음을 나타내는 어서트 스테이트(assert state)로 구성된 스테이트 머신(state machine)으로 구현될 수 있다.According to an embodiment, each of the first through m-th interrupt holders may wait for the output permission signal from the interrupt arbiter in an idle state indicating that the first through the m-th interrupt request signals are not received, And an assert state indicating that the first to the m-th interrupt request signals are output to the first to m-th processors, respectively, and a state machine Can be implemented.

일 실시예에 의하면, 상기 인터럽트 아비터는 상기 제 1 내지 제 m 인터럽트 홀더들로부터 각각 상기 출력 요청 신호를 수신하면, 상기 제 1 내지 제 m 인터럽트 홀더들에 상기 출력 허가 신호를 순차적으로 출력하여, 상기 제 1 내지 제 m 인터럽트 요청 신호들이 적어도 상기 기 설정된 간격 이상으로 상기 제 1 내지 제 m 프로세서들에 각각 출력되도록 제어할 수 있다.According to an embodiment, the interrupt arbiter sequentially outputs the output permission signal to the first through m-th interrupt holders when receiving the output request signal from the first through m-th interrupt holders, And to control the first through m-th interrupt request signals to be output to the first through m-th processors at least over the predetermined interval.

일 실시예에 의하면, 상기 인터럽트 아비터는 상기 제 1 내지 제 m 인터럽트 요청 신호들 중에서 어느 하나도 상기 제 1 내지 제 m 프로세서들에 출력되고 있지 않음을 나타내는 아이들 스테이트, 및 상기 제 1 내지 제 n 인터럽트 요청 신호들 중에서 적어도 하나 이상이 상기 제 1 내지 제 m 프로세서들에 출력되고 있음을 나타내는 웨이트 스테이트로 구성된 스테이트 머신으로 구현될 수 있다.According to an embodiment, the interrupt arbiter includes an idle state indicating that any one of the first through m-th interrupt request signals is not output to the first through m-th processors, And a weight state indicating that at least one of the signals is being output to the first to m-th processors.

일 실시예에 의하면, 상기 인터럽트 아비터는 기 설정된 우선순위에 따라 상기 제 1 내지 제 m 인터럽트 요청 신호들의 출력 순서를 변경할 수 있다.According to an embodiment, the interrupt arbiter may change the output order of the first to m-th interrupt request signals according to a predetermined priority.

일 실시예에 의하면, 상기 인터럽트 아비터는 상기 제 1 내지 제 m 프로세서들을 액티브 상태인 프로세서들로 구성된 제 1 그룹과 인액티브 상태인 프로세서들로 구성된 제 2 그룹으로 분류하고, 상기 제 1 내지 제 m 인터럽트 요청 신호들 중에서 상기 제 1 그룹에 할당된 인터럽트 요청 신호들에 대해서는 상기 기 설정된 간격으로 조절하지 않고, 상기 제 1 내지 제 m 인터럽트 요청 신호들 중에서 상기 제 2 그룹에 할당된 인터럽트 요청 신호들에 대해서만 상기 기 설정된 간격으로 조절할 수 있다.According to one embodiment, the interrupt arbiter classifies the first through m-th processors into a first group composed of processors in an active state and a second group composed of processors in an inactive state, and the first through m- The interrupt request signals allocated to the first group among the interrupt request signals are not adjusted at the predetermined intervals and the interrupt request signals allocated to the second group among the first to the m- Can be adjusted at the predetermined interval.

본 발명의 또 다른 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 시스템 온-칩은 복수의 인터럽트들을 생성하는 복수의 인터럽트 소스들, 상기 인터럽트들에 기초하여 제 1 내지 제 m(단, m은 2이상의 정수) 인터럽트 요청 신호들을 생성하는 인터럽트 컨트롤러, 상기 제 1 내지 제 m 인터럽트 요청 신호들 중에서 인접하는 인터럽트 요청 신호들 사이의 시간 간격을 적어도 기 설정된 간격 이상으로 조절하는 인터럽트 스프레드 장치, 및 상기 제 1 내지 제 m 인터럽트 요청 신호들에 응답하여 상기 인터럽트 소스들을 위한 인터럽트 처리를 각각 수행하는 제 1 내지 제 m 프로세서들을 포함할 수 있다.According to still another aspect of the present invention, there is provided a system on-chip comprising a plurality of interrupt sources for generating a plurality of interrupts, first to m-th m is an integer greater than or equal to 2) interrupt request signals; an interrupt spread device for adjusting a time interval between adjacent interrupt request signals among the first to the m-th interrupt request signals to at least a predetermined interval; And first to m-th processors for performing interrupt processing for the interrupt sources in response to the first to m-th interrupt request signals, respectively.

일 실시예에 의하면, 상기 인터럽트 스프레드 장치는 상기 제 1 내지 제 m 인터럽트 요청 신호들을 수신하고, 상기 제 1 내지 제 m 인터럽트 요청 신호들을 적어도 상기 기 설정된 간격 이상을 두어 상기 제 1 내지 제 m 프로세서들에 각각 출력하는 제 1 내지 제 m 인터럽트 홀더들, 및 상기 제 1 내지 제 m 인터럽트 요청 신호들 중에서 상기 인접하는 인터럽트 요청 신호들 사이의 상기 시간 간격이 상기 기 설정된 간격보다 작은 경우 상기 시간 간격을 상기 기 설정된 간격으로 조절하는 인터럽트 아비터를 포함할 수 있다.According to an embodiment, the interrupt spread device receives the first through m-th interrupt request signals and transmits the first through m-th interrupt request signals to the first through m- And outputting the interrupt request signals to the first to mth interrupt holders when the time interval between the adjacent interrupt request signals is less than the preset interval, And an interrupt arbiter for adjusting the interrupt interval at a predetermined interval.

일 실시예에 의하면, 상기 제 1 내지 제 m 인터럽트 요청 신호들은 상기 제 1 내지 제 m 인터럽트 홀더들에 각각 수신되고, 상기 제 1 내지 제 m 인터럽트 홀더들은 상기 제 1 내지 제 m 프로세서들에 각각 연결될 수 있다.According to an embodiment, the first to the m-th interrupt request signals are received in the first to m-th interrupt holders, respectively, and the first to m-th interrupt holders are connected to the first to m- .

일 실시예에 의하면, 상기 인터럽트 아비터는 기 설정된 우선순위에 따라 상기 제 1 내지 제 m 인터럽트 요청 신호들의 출력 순서를 변경할 수 있다.According to an embodiment, the interrupt arbiter may change the output order of the first to m-th interrupt request signals according to a predetermined priority.

일 실시예에 의하면, 상기 인터럽트 아비터는 상기 제 1 내지 제 m 프로세서들을 액티브 상태인 프로세서들로 구성된 제 1 그룹과 인액티브 상태인 프로세서들로 구성된 제 2 그룹으로 분류하고, 상기 제 1 내지 제 m 인터럽트 요청 신호들 중에서 상기 제 1 그룹에 할당된 인터럽트 요청 신호들에 대해서는 상기 기 설정된 간격으로 조절하지 않고, 상기 제 1 내지 제 m 인터럽트 요청 신호들 중에서 상기 제 2 그룹에 할당된 인터럽트 요청 신호들에 대해서만 상기 기 설정된 간격으로 조절할 수 있다.According to one embodiment, the interrupt arbiter classifies the first through m-th processors into a first group composed of processors in an active state and a second group composed of processors in an inactive state, and the first through m- The interrupt request signals allocated to the first group among the interrupt request signals are not adjusted at the predetermined intervals and the interrupt request signals allocated to the second group among the first to the m- Can be adjusted at the predetermined interval.

일 실시예에 의하면, 상기 시스템 온-칩은 휴대폰, 스마트폰, 스마트패드 등과 같은 모바일 기기에 구비될 수 있다.According to one embodiment, the system on-chip may be provided in a mobile device such as a mobile phone, a smart phone, a smart pad, and the like.

본 발명의 또 다른 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 인터럽트 처리 방법은 복수의 프로세서들 중에서 일부가 액티브(active) 상태이고, 다른 일부는 인액티브(inactive) 상태인 상황에서, 복수의 인터럽트 소스들이 복수의 인터럽트들을 생성하면, 상기 프로세서들로 하여금 상기 인터럽트들을 처리할 수 있다. 구체적으로, 상기 인터럽트 처리 방법은 인터럽트 컨트롤러로 하여금 상기 인터럽트 소스들로부터 상기 인터럽트들을 수신하고, 상기 인터럽트들을 기 설정된 방식에 따라 상기 프로세서들 각각에 할당하여 복수의 인터럽트 요청 신호들을 출력하게 하고, 인터럽트 스프레더로 하여금 상기 인터럽트 컨트롤러로부터 상기 인터럽트 요청 신호들을 수신하고, 상기 인터럽트 요청 신호들을 상기 액티브 상태인 프로세서들에 출력될 비대상 인터럽트 요청 신호들과 상기 인액티브 상태인 프로세서들에 출력될 대상 인터럽트 요청 신호들로 분류하게 하며, 상기 인터럽트 스프레더로 하여금 상기 비대상 인터럽트 요청 신호들을 각각 상기 액티브 상태인 프로세서들에 바로 출력하게 하고, 상기 인터럽트 스프레더가 상기 대상 인터럽트 요청 신호들 사이의 시간 간격이 기 설정된 간격보다 작은지 여부를 판단하고, 상기 시간 간격이 상기 기 설정된 간격보다 작은 경우, 상기 시간 간격을 상기 기 설정된 간격으로 조절하게 하며, 상기 인터럽트 스프레더가 상기 대상 인터럽트 요청 신호들을 각각 상기 인액티브 상태인 프로세서들에 순차적으로 출력하게 할 수 있다.According to another aspect of the present invention, there is provided an interrupt processing method, wherein in a state where a part of a plurality of processors is in an active state and another part is in an inactive state, When a plurality of interrupt sources generate a plurality of interrupts, the processors can process the interrupts. Specifically, the interrupt processing method may include causing the interrupt controller to receive the interrupts from the interrupt sources, to allocate the interrupts to each of the processors according to a predetermined method to output a plurality of interrupt request signals, For receiving the interrupt request signals from the interrupt controller and outputting the interrupt request signals to non-target interrupt request signals to be output to the active processors and target interrupt request signals to be output to the inactive processors And causes the interrupt spreader to output the non-target interrupt request signals directly to the processors in the active state, and the interrupt spreader may cause the interrupt spreader to output the non- Determines whether the time interval is smaller than a predetermined interval, and adjusts the time interval to the predetermined interval when the time interval is smaller than the preset interval, and the interrupt spreader sets the target interrupt request signals And sequentially output the information to processors in the inactive state.

본 발명의 실시예들에 따른 인터럽트 스프레드 방법은 복수의 인터럽트 소스들이 짧은 시간 내에 복수의 인터럽트들을 연속적으로 출력할 때, 상기 인터럽트들에 기초하여 생성되는 복수의 인터럽트 요청 신호들 사이의 각각의 시간 간격을 적어도 기 설정된 간격 이상으로 조절함으로써, 인액티브 상태(예를 들어, 파워 다운 상태, 파워 오프 상태 등)에 있는 복수의 프로세서들(또는, 멀티 코어 프로세서의 복수의 코어들)이 짧은 시간 내에 액티브 상태(예를 들어, 파워 온 상태 등)로 연속적으로 변경되는 것(즉, 급작스러운 웨이크-업)을 방지할 수 있다. 이에, 상기 프로세서들 내부에 인러쉬 전류가 생성되는 것을 방지할 수 있다.An interrupt spreading method according to embodiments of the present invention is a method for interrupting a plurality of interrupt sources in a short time when successively outputting a plurality of interrupts in a short time, (Or a plurality of cores of a multicore processor) in an inactive state (e.g., a power down state, a power off state, etc.) can be activated It is possible to prevent a continuous change (i.e., abrupt wake-up) to a state (e.g., power-on state, etc.). Accordingly, an inrush current can be prevented from being generated in the processors.

본 발명의 실시예들에 따른 인터럽트 스프레드 장치는 복수의 인터럽트 소스들이 짧은 시간 내에 복수의 인터럽트들을 연속적으로 출력할 때, 상기 인터럽트들에 기초하여 생성되는 복수의 인터럽트 요청 신호들 사이의 각각의 시간 간격을 적어도 기 설정된 간격 이상으로 조절함으로써, 인액티브 상태(예를 들어, 파워 다운 상태, 파워 오프 상태 등)에 있는 복수의 프로세서들(예를 들어, 멀티 코어 프로세서의 복수의 코어들)이 짧은 시간 내에 액티브 상태(예를 들어, 파워 온 상태 등)로 연속적으로 변경되는 것(즉, 급작스러운 웨이크-업)을 방지할 수 있다. 이에, 상기 프로세서들 내부에 인러쉬 전류가 생성되는 것을 방지할 수 있다.An interrupt spread device according to embodiments of the present invention includes a plurality of interrupt sources for generating a plurality of interrupts in succession when a plurality of interrupt sources continuously output a plurality of interrupts in a short time, (E.g., a plurality of cores of a multicore processor) in an inactive state (e.g., power-down state, power-off state, etc.) (I.e., sudden wake-up) in an active state (e.g., a power-on state, etc.) Accordingly, an inrush current can be prevented from being generated in the processors.

본 발명의 실시예들에 따른 시스템 온-칩은 상기 인터럽트 스프레드 장치를 구비함으로써, 인액티브 상태(예를 들어, 파워 다운 상태, 파워 오프 상태 등)에 있는 복수의 프로세서들(예를 들어, 멀티 코어 프로세서의 복수의 코어들)이 짧은 시간 내에 액티브 상태(예를 들어, 파워 온 상태 등)로 연속적으로 변경됨(즉, 급작스러운 웨이크-업)에 따른 오동작을 방지하여 높은 동작 안정성을 확보할 수 있다.The system on-chip according to embodiments of the present invention may be provided with the interrupt spread device so that a plurality of processors in an inactive state (for example, a power-down state, a power-off state, (I.e., a plurality of cores of the core processor) are continuously changed in an active state (for example, a power-on state, etc.) within a short time (that is, sudden wake-up) have.

다만, 본 발명의 효과는 상기 언급한 효과에 한정되는 것이 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.However, the effects of the present invention are not limited to the above-mentioned effects, and may be variously expanded without departing from the spirit and scope of the present invention.

도 1은 본 발명의 일 실시예에 따른 인터럽트 스프레드 방법을 나타내는 순서도이다.

도 2a 및 도 2b는 도 1의 인터럽트 스프레드 방법이 수행되는 일 예를 나타내는 도면들이다.

도 3a 및 도 3b는 도 1의 인터럽트 스프레드 방법이 수행되는 다른 예를 나타내는 도면들이다.

도 4a 및 도 4b는 도 1의 인터럽트 스프레드 방법이 수행되는 또 다른 예를 나타내는 도면들이다.

도 5는 본 발명의 다른 실시예에 따른 인터럽트 스프레드 방법을 나타내는 순서도이다.

도 6a 및 도 6b는 도 5의 인터럽트 스프레드 방법이 수행되는 일 예를 나타내는 도면들이다.

도 7은 본 발명의 또 다른 실시예에 따른 인터럽트 스프레드 방법을 나타내는 순서도이다.

도 8a 및 도 8b는 도 7의 인터럽트 스프레드 방법이 수행되는 일 예를 나타내는 도면들이다.

도 9는 본 발명의 또 다른 실시예에 따른 인터럽트 스프레드 방법을 나타내는 순서도이다.

도 10은 도 9의 인터럽트 스프레드 방법을 설명하기 위한 도면이다.

도 11은 본 발명의 일 실시예에 따른 인터럽트 스프레드 장치를 나타내는 블록도이다.

도 12는 도 11의 인터럽트 스프레드 장치에 구비된 인터럽트 홀더의 스테이트 머신을 나타내는 도면이다.

도 13은 도 11의 인터럽트 스프레드 장치에 구비된 인터럽트 아비터의 스테이트 머신을 나타내는 도면이다.

도 14는 도 11의 인터럽트 스프레드 장치가 동작하는 일 예를 나타내는 타이밍도이다.

도 15는 본 발명의 일 실시예에 따른 시스템 온-칩을 나타내는 블록도이다.

도 16은 도 15의 시스템 온-칩에서 인터럽트 스프레드 장치가 동작하는 일 예를 나타내는 도면이다.

도 17은 도 15의 시스템 온-칩에서 인터럽트 스프레드 장치가 동작하는 다른 예를 나타내는 도면이다.

도 18은 도 15의 시스템 온-칩에서 인터럽트 스프레드 장치가 동작하는 또 다른 예를 나타내는 도면이다.

도 19는 임의의 시스템 온-칩이 인터럽트 스프레드 장치를 구비하고 있는지 여부를 검증하는 방법의 일 예를 나타내는 순서도이다.

도 20은 임의의 시스템 온-칩이 인터럽트 스프레드 장치를 구비하고 있는지 여부를 검증하는 방법의 일 예를 설명하기 위한 도면이다.

도 21은 임의의 시스템 온-칩이 인터럽트 스프레드 장치를 구비하고 있는지 여부를 검증하는 방법의 다른 예를 나타내는 순서도이다.

도 22는 본 발명의 일 실시예에 따른 멀티 코어 시스템을 나타내는 블록도이다.

도 23은 도 22의 멀티 코어 시스템이 스마트폰으로 구현되는 일 예를 나타내는 도면이다.1 is a flowchart illustrating an interrupt spread method according to an embodiment of the present invention.

FIGS. 2A and 2B are diagrams illustrating an example in which the interrupt spread method of FIG. 1 is performed.

FIGS. 3A and 3B are diagrams showing another example in which the interrupt spread method of FIG. 1 is performed. FIG.

4A and 4B are diagrams showing still another example in which the interrupt spread method of FIG. 1 is performed.

5 is a flowchart illustrating an interrupt spread method according to another embodiment of the present invention.

6A and 6B are diagrams illustrating an example in which the interrupt spread method of FIG. 5 is performed.

7 is a flowchart showing an interrupt spread method according to another embodiment of the present invention.

8A and 8B are diagrams illustrating an example in which the interrupt spread method of FIG. 7 is performed.

9 is a flowchart showing an interrupt spread method according to another embodiment of the present invention.

10 is a diagram for explaining the interrupt spread method of FIG.

11 is a block diagram showing an interrupt spread device according to an embodiment of the present invention.

12 is a diagram showing a state machine of an interrupt holder provided in the interrupt spread device of FIG.

13 is a diagram showing a state machine of an interrupt arbiter provided in the interrupt spread device of FIG.

14 is a timing chart showing an example of the operation of the interrupt spread device of FIG.

15 is a block diagram illustrating a system on-chip according to one embodiment of the present invention.

16 is a diagram showing an example in which the interrupt spread device operates in the system on-chip of FIG.

17 is a diagram showing another example of the operation of the interrupt spread device in the system on-chip of FIG.

FIG. 18 is a diagram showing another example in which the interrupt spread device operates in the system on-chip of FIG.

19 is a flowchart showing an example of a method for verifying whether or not any system on-chip has an interrupt spread device.

FIG. 20 is a diagram for explaining an example of a method for verifying whether or not an arbitrary system on-chip has an interrupt spread device.

Fig. 21 is a flowchart showing another example of a method for verifying whether or not any system on-chip has an interrupt spread device.

22 is a block diagram illustrating a multicore system in accordance with an embodiment of the present invention.

23 is a diagram showing an example in which the multicore system of FIG. 22 is implemented as a smartphone.

본문에 개시되어 있는 본 발명의 실시예들에 대해서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예를 설명하기 위한 목적으로 예시된 것으로, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며 본문에 설명된 실시예들에 한정되는 것으로 해석되어서는 아니 된다.For the embodiments of the invention disclosed herein, specific structural and functional descriptions are set forth for the purpose of describing an embodiment of the invention only, and it is to be understood that the embodiments of the invention may be practiced in various forms, The present invention should not be construed as limited to the embodiments described in Figs.

본 발명은 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있는바, 특정 실시예들을 도면에 예시하고 본문에 상세하게 설명하고자 한다. 그러나 이는 본 발명을 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.The present invention is capable of various modifications and various forms, and specific embodiments are illustrated in the drawings and described in detail in the text. It is to be understood, however, that the invention is not intended to be limited to the particular forms disclosed, but on the contrary, is intended to cover all modifications, equivalents, and alternatives falling within the spirit and scope of the invention.

제 1, 제 2 등의 용어는 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로 사용될 수 있다. 예를 들어, 본 발명의 권리 범위로부터 이탈되지 않은 채 제 1 구성요소는 제 2 구성요소로 명명될 수 있고, 유사하게 제 2 구성요소도 제 1 구성요소로 명명될 수 있다.The terms first, second, etc. may be used to describe various components, but the components should not be limited by the terms. The terms may be used for the purpose of distinguishing one component from another. For example, without departing from the scope of the present invention, the first component may be referred to as a second component, and similarly, the second component may also be referred to as a first component.

어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.It is to be understood that when an element is referred to as being "connected" or "connected" to another element, it may be directly connected or connected to the other element, . On the other hand, when an element is referred to as being "directly connected" or "directly connected" to another element, it should be understood that there are no other elements in between. Other expressions that describe the relationship between components, such as "between" and "between" or "neighboring to" and "directly adjacent to" should be interpreted as well.

본 출원에서 사용한 용어는 단지 특정한 실시예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 출원에서, "포함하다" 또는 "가지다" 등의 용어는 설시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.The terminology used in this application is used only to describe a specific embodiment and is not intended to limit the invention. The singular expressions include plural expressions unless the context clearly dictates otherwise. In the present application, the terms "comprise", "having", and the like are intended to specify the presence of stated features, integers, steps, operations, elements, components, or combinations thereof, , Steps, operations, components, parts, or combinations thereof, as a matter of principle.

다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미이다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미인 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.Unless otherwise defined, all terms used herein, including technical or scientific terms, have the same meaning as commonly understood by one of ordinary skill in the art to which this invention belongs. Terms such as those defined in commonly used dictionaries should be construed as meaning consistent with meaning in the context of the relevant art and are not to be construed as ideal or overly formal in meaning unless expressly defined in the present application .

이하, 첨부한 도면들을 참조하여, 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다. 도면상의 동일한 구성요소에 대해서는 동일한 참조부호를 사용하고 동일한 구성요소에 대해서 중복된 설명은 생략한다.Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the accompanying drawings. The same reference numerals are used for the same constituent elements in the drawings and redundant explanations for the same constituent elements are omitted.

도 1은 본 발명의 일 실시예에 따른 인터럽트 스프레드 방법을 나타내는 순서도이다.1 is a flowchart illustrating an interrupt spread method according to an embodiment of the present invention.

도 1을 참조하면, 도 1의 인터럽트 스프레드 방법은 복수의 인터럽트 요청 신호들을 수신(Step S120)하고, 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 작은지 여부를 판단(Step S140)할 수 있다. 이 때, 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 작으면, 도 1의 인터럽트 스프레드 방법은 인터럽트 요청 신호들 사이의 각각의 시간 간격을 기 설정된 간격으로 조절(Step S160)할 수 있다. 반면에, 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 크면, 도 1의 인터럽트 스프레드 방법은 인터럽트 요청 신호들 사이의 각각의 시간 간격을 그대로 유지(Step S165)시킬 수 있다. 이후, 도 1의 인터럽트 스프레드 방법은 인터럽트 요청 신호들을 복수의 프로세서들에 각각 출력(Step S180)할 수 있다. 한편, 복수의 프로세서들 각각은 독립적인 프로세서들에 상응할 수 있고, 멀티 코어 프로세서(예를 들어, 듀얼 코어 프로세서, 쿼드 코어 프로세서 등)의 복수의 코어(core)들에 상응할 수도 있다. 한편, 설명의 편의를 위하여, 본 명세서에서는 액티브(active) 상태와 인액티브(inactive) 상태로 구분하였지만, 인액티브 상태는 파워 다운 상태(power-down state), 파워 오프 상태(power-off state)와 같은 저전력 모드의 다양한 상태들을 모두 포함하는 개념으로 해석되어야 한다. 이하, 도 1의 인터럽트 스프레드 방법에 대하여 구체적으로 설명하기로 한다.Referring to FIG. 1, the interrupt spread method of FIG. 1 receives a plurality of interrupt request signals (Step S120) and determines whether each time interval between interrupt request signals is smaller than a preset interval (Step S140) can do. In this case, if each time interval between the interrupt request signals is smaller than the predetermined interval, the interrupt spread method of FIG. 1 can adjust each time interval between the interrupt request signals at a predetermined interval (Step S160) have. On the other hand, if each time interval between the interrupt request signals is larger than the predetermined interval, the interrupt spread method of FIG. 1 can maintain the respective time intervals between the interrupt request signals (Step S165). Then, the interrupt spread method of FIG. 1 may output the interrupt request signals to the plurality of processors, respectively (Step S180). On the other hand, each of the plurality of processors may correspond to independent processors and may correspond to a plurality of cores of a multicore processor (e.g., a dual core processor, a quad core processor, etc.). Although the active state is divided into an active state and an inactive state in this specification, the inactive state is a power-down state, a power-off state, Such as < RTI ID = 0.0 > a < / RTI > low power mode. Hereinafter, the interrupt spread method of FIG. 1 will be described in detail.

도 1의 인터럽트 스프레드 방법은 인터럽트 요청 신호들을 순차적으로 수신(Step S120)할 수 있다. 일 실시예에서, 인터럽트 요청 신호들은 인터럽트 소스(interrupt source)들로부터 출력되는 인터럽트들에 기초하여 생성될 수 있고, 인터럽트 요청 신호들은 프로세서들에 각각 할당될 수 있다. 인터럽트 소스들은 각각 멀티 코어 시스템(또는, 멀티 프로세서 시스템) 내에서 소정의 동작을 수행하는 아이피(Intellectual Property; IP)들로서, 시스템 온-칩(System On-Chip; SOC)을 구성하는 여러 구성 요소들 예를 들어, 비디오 모듈, 사운드 모듈, 디스플레이 모듈, 메모리 모듈, 통신 모듈, 카메라 모듈 등과 같은 소정의 모듈들에 상응할 수 있다. 일반적으로, 인터럽트 소스들은 하나의 시스템 온-칩 내에 대략 수십 내지 수백 개 정도가 실장될 수 있다. 이러한 인터럽트 소스들이 인터럽트들을 발생시키면, 상기 인터럽트들에 기초하여 생성된 인터럽트 요청 신호들이 프로세서들에 각각 입력될 수 있고, 상기 프로세서들은 인터럽트 요청 신호들에 응답하여 상기 인터럽트 소스들을 위한 인터럽트 처리를 각각 수행할 수 있다. 최근, 전자 기기의 소형화 및 경량화 추세에 따라, 복수의 아이피들과 복수의 프로세서들이 하나의 칩에 실장되는 시스템 온-칩이 널리 사용되고 있고, 시스템 온-칩 내부의 프로세서들은 전력 소모를 줄이기 위하여 저전력 모드로 빈번하게 진입을 하기 때문에, 상기 인터럽트 소스들로부터 생성된 인터럽트들에 기초하여 복수의 프로세서들이 저전력 모드에서 동시에 탈출(즉, 급작스러운 웨이크-업)하게 되면, 상기 프로세서들 내부에 인러쉬 전류(in-rush current)가 생성되어 인러쉬 전류에 의한 오동작이 야기될 수 있다. 특히, 시스템 온-칩의 사이즈가 점점 작아짐에 따라 다이나믹 전류(dynamic current)의 변화에 따른 인러쉬 전류의 발생은 시스템 온-칩의 동작 안정성에 큰 문제가 되고 있다.The interrupt spread method of FIG. 1 may sequentially receive interrupt request signals (Step S120). In one embodiment, interrupt request signals may be generated based on interrupts output from interrupt sources, and interrupt request signals may be assigned to processors, respectively. Each of the interrupt sources is an Intellectual Property (IP) that performs a predetermined operation in a multicore system (or a multiprocessor system), and includes various components constituting a system on-chip (SOC) For example, it may correspond to certain modules such as a video module, a sound module, a display module, a memory module, a communication module, a camera module, and the like. Generally, the interrupt sources can be implemented in a single system on-chip, in the order of tens to hundreds. When these interrupt sources generate interrupts, interrupt request signals generated based on the interrupts can be input to the processors, respectively, and the processors perform interrupt processing for the interrupt sources in response to the interrupt request signals, respectively can do. In recent years, system-on-chips where a plurality of IPs and a plurality of processors are mounted on a single chip have been widely used in order to miniaturize and lighten electronic devices. In order to reduce power consumption, Mode, so that when a plurality of processors simultaneously escape (i.e., abruptly wake up) in a low power mode based on interrupts generated from the interrupt sources, an inrush current an in-rush current may be generated, which may cause malfunction due to the inrush current. Particularly, as the size of the system on-chip becomes smaller, the generation of the inrush current due to the change of the dynamic current becomes a serious problem in the operation stability of the system on-chip.

이에, 도 1의 인터럽트 스프레드 방법은 인터럽트 요청 신호들이 수신되면, 이러한 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 작은지 여부를 판단(Step S140)할 수 있다. 일 실시예에서, 기 설정된 간격은 복수의 프로세서들이 인액티브 상태에서 액티브 상태로 변경될 때, 상기 프로세서들 내부에 인러쉬 전류가 생성되지 않는 범위 내에서 결정될 수 있다. 이 때, 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 작으면, 도 1의 인터럽트 스프레드 방법은 인터럽트 요청 신호들 사이의 각각의 시간 간격을 기 설정된 간격으로 조절(Step S160)할 수 있다. 반면에, 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 크면, 도 1의 인터럽트 스프레드 방법은 인터럽트 요청 신호들 사이의 각각의 시간 간격을 그대로 유지(Step S165)시킬 수 있다. 다시 말하면, 도 1의 인터럽트 스프레드 방법은 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 작은 경우에만, 그 시간 간격을 기 설정된 간격으로 조절하여 프로세서들에 각각 출력하고, 인터럽트 요청 신호들 사이의 각각의 시간 간격이 기 설정된 간격보다 큰 경우에는, 그 시간 간격을 조절하지 않은 채 프로세서들에 각각 출력할 수 있다. 그 결과, 인터럽트 요청 신호들은 기 설정된 간격 이상을 두어 프로세서들에 각각 입력될 수 있다.In the interrupt spread method of FIG. 1, when the interrupt request signals are received, it is determined whether each time interval between the interrupt request signals is smaller than a predetermined interval (Step S140). In one embodiment, the predetermined interval may be determined within a range in which an inrush current is not generated within the processors when a plurality of processors are changed from an inactive state to an active state. In this case, if each time interval between the interrupt request signals is smaller than the predetermined interval, the interrupt spread method of FIG. 1 can adjust each time interval between the interrupt request signals at a predetermined interval (Step S160) have. On the other hand, if each time interval between the interrupt request signals is larger than the predetermined interval, the interrupt spread method of FIG. 1 can maintain the respective time intervals between the interrupt request signals (Step S165). In other words, in the case of the interrupt spread method of FIG. 1, only when each time interval between interrupt request signals is smaller than a predetermined interval, the time interval is adjusted to a predetermined interval and output to each of the processors, Can be output to the processors without adjusting the time interval, respectively. As a result, the interrupt request signals can be input to the processors with a predetermined interval or more.

구체적으로, 도 1의 인터럽트 스프레드 방법은, 인터럽트 요청 신호들 사이의 각각의 시간 간격을 기 설정된 간격으로 조절(Step S160)함에 있어서, 순차적으로 입력되고 인접하는 제 k(단, k는 1이상인 정수) 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 제 k 시간 간격이 0보다 큰 경우, 상기 제 k 시간 간격이 기 설정된 간격으로 될 때까지 제 k+1 인터럽트 요청 신호의 출력을 지연시킬 수 있다. 즉, 순차적으로 입력되고 인접하는 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 제 k 시간 간격이 기 설정된 간격보다 작음에도 불구하고, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호가 그대로 두 개의 프로세서들에 각각 출력되면, 두 개의 프로세서들이 짧은 시간 내에 급작스러운 웨이크-업을 하게 되므로, 상기 프로세서들 내부에 인러쉬 전류가 생성될 수 있다. 그러므로, 도 1의 인터럽트 스프레드 방법은 제 k+1 인터럽트 요청 신호의 출력을 지연시킴으로써 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 제 k 시간 간격이 기 설정된 간격이 되도록 조절하는 것이다. 한편, 도 1의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 제 k 시간 간격이 0인 경우(즉, 동시에 입력되는 경우)에는, 기 설정된 우선순위에 따라 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 중에서 하나의 출력을 기 설정된 간격만큼 지연시킬 수 있다. 그 결과, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호가 동시에 입력되더라도, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 제 k 시간 간격이 기 설정된 간격이 되므로, 상기 프로세서들 내부에 인러쉬 전류가 생성되지 않게 된다.Specifically, in the interrupt spread method of FIG. 1, each time interval between interrupt request signals is adjusted at a predetermined interval (Step S160). In step S160, K interrupt request signal until the k-th time interval becomes a predetermined interval when the k-th time interval between the interrupt request signal and the (k + 1) -th interrupt request signal is greater than zero have. That is, even though the k-th time interval between the k-th interrupt request signal and the k-th interrupt request signal that are sequentially input and adjacent to each other is smaller than a preset interval, the k-th interrupt request signal and the (k + 1) Is directly output to the two processors, an inrush current can be generated in the processors because the two processors are caused to suddenly wake up in a short time. Therefore, the interrupt spread method of FIG. 1 delays the output of the (k + 1) -th interrupt request signal so that the k-th time interval between the k-th interrupt request signal and the (k + 1) -th interrupt request signal becomes a predetermined interval. 1, when the k-th time interval between the k-th interrupt request signal and the (k + 1) -th interrupt request signal is 0 (i.e., simultaneously input), the interrupt spread method It is possible to delay one output from the interrupt request signal and the (k + 1) -th interrupt request signal by a predetermined interval. As a result, even though the k-th interrupt request signal and the (k + 1) -th interrupt request signal are input simultaneously, the k-th time interval between the k-th interrupt request signal and the (k + An in-rush current is not generated inside.

나아가, 도 1의 인터럽트 스프레드 방법은, 인터럽트 요청 신호들 사이의 각각의 시간 간격을 기 설정된 간격으로 조절(Step S160)함에 있어서, 기 설정된 우선순위에 따라 인터럽트 요청 신호들의 출력 순서를 변경할 수 있다. 예를 들어, 제 k 인터럽트 요청 신호, 제 k+1 인터럽트 요청 신호 및 제 k+2 인터럽트 요청 신호가 순차적으로 입력되고, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 제 k 시간 간격 및 제 k+1 인터럽트 요청 신호와 제 k+2 인터럽트 요청 신호 사이의 제 k+1 시간 간격이 모두 기 설정된 간격보다 작은 경우에, 도 1의 인터럽트 스프레드 방법은 상기 제 k 시간 간격이 기 설정된 간격이 되도록 제 k+1 인터럽트 요청 신호의 출력을 지연시킨 후, 상기 제 k+1 시간 간격이 기 설정된 간격이 되도록 제 k+2 인터럽트 요청 신호의 출력을 지연시키게 된다. 그러나, 도 1의 인터럽트 스프레드 방법은 요구되는 조건에 따라 제 k 인터럽트 요청 신호, 제 k+1 인터럽트 요청 신호 및 제 k+2 인터럽트 요청 신호의 출력을 기 설정된 우선순위에 기초하여 비순차적으로 지연시킬 수 있다. 예를 들어, 제 k 인터럽트 요청 신호, 제 k+1 인터럽트 요청 신호 및 제 k+2 인터럽트 요청 신호가 순차적으로 입력되고, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 제 k 시간 간격 및 제 k+1 인터럽트 요청 신호와 제 k+2 인터럽트 요청 신호 사이의 제 k+1 시간 간격이 모두 기 설정된 간격보다 작은 경우에, 제 k 인터럽트 요청 신호의 우선순위가 가장 높고 제 k+1 인터럽트 요청 신호의 우선순위가 가장 낮다면, 도 1의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호, 제 k+2 인터럽트 요청 신호 및 제 k+1 인터럽트 요청 신호 순으로 출력시킬 수 있다.In addition, the interrupt spread method of FIG. 1 may change the output order of the interrupt request signals according to a predetermined priority in adjusting the time interval between the interrupt request signals at predetermined intervals (Step S160). For example, the k-th interrupt request signal, the k + 1-th interrupt request signal, and the (k + 2) -th interrupt request signal are sequentially input, And the (k + 1) -th time interval between the k + 1-th interrupt request signal and the (k + 2) -th interrupt request signal are all less than a predetermined interval, the interrupt spread method of FIG. 1 interrupt request signal to delay the output of the (k + 1) -th interrupt request signal so that the (k + 1) -th time interval becomes a predetermined interval. However, the interrupt spread method of FIG. 1 may delay the outputs of the k-th interrupt request signal, the (k + 1) -th interrupt request signal, and the (k + 2) -th interrupt request signal in a non- . For example, the k-th interrupt request signal, the k + 1-th interrupt request signal, and the (k + 2) -th interrupt request signal are sequentially input, And the (k + 1) -th time interval between the k + 1-th interrupt request signal and the (k + 2) -th interrupt request signal are all less than a predetermined interval, If the priority of the request signal is the lowest, the interrupt spread method of FIG. 1 may output the k-th interrupt request signal, the (k + 2) -th interrupt request signal, and the (k + 1) -th interrupt request signal.

일반적으로, 프로세서는 인터럽트 요청 신호가 수신되면, 인액티브 상태에서 액티브 상태로 변경된 후, 인터럽트 처리(즉, 인터럽트 서비스)를 수행하게 된다. 이 때, 프로세서 내부를 구성하는 다수의 트랜지스터들이 갑작스럽게 동작을 시작하면서 인러쉬 전류가 생성되게 된다. 특히, 저전력 프로세서의 경우에는, 인액티브 상태에서 소모 전력을 줄이기 위해 다수의 클럭 게이팅 회로(clock gating circuit)를 구비하기 때문에, 인액티브 상태에서 대부분의 클럭들이 토글(toggle)하지 않다가, 저전력 프로세서가 인액티브 상태에서 액티브 상태로 변경되면, 대부분의 클럭들이 토글을 동시에 시작하게 되어 인러쉬 전류가 크게 생성될 수 있다. 이 때, 복수의 프로세서들이 짧은 시간 내에 급작스러운 웨이크-업을 하게 되면, 복수의 프로세서들에서 생성된 인러쉬 전류가 더해져서, 주변 회로의 전력 공급이 불안정하게 됨으로써 오동작이 발생할 수 있다. 이에, 도 1의 인터럽트 스프레드 방법은 복수의 인터럽트 소스들이 짧은 시간 내에 복수의 인터럽트들을 연속적으로 출력할 때, 상기 인터럽트들에 기초하여 생성되는 복수의 인터럽트 요청 신호들 사이의 시간 간격을 적어도 기 설정된 간격 이상으로 조절함으로써, 인액티브 상태에 있는 복수의 프로세서들(예를 들어, 멀티 코어 프로세서 등)이 짧은 시간 내에 액티브 상태로 연속적으로 변경되는 것(즉, 급작스러운 웨이크-업)을 방지할 수 있다. 그 결과, 시스템 온-칩에서 복수의 프로세서들(또는, 멀티 코어 프로세서의 복수의 코어들) 내부에 급작스러운 웨이크-업에 의한 인러쉬 전류가 생성되는 것이 방지되어, 시스템 온-칩 및 이를 포함하는 전자 기기는 높은 동작 안정성을 확보할 수 있다. 한편, 도 1에서는 복수의 프로세서들이 액티브 상태인지 인액티브 상태인지 여부와 상관없이, 모든 프로세서들에 입력되는 인터럽트 요청 신호들에 대하여 도 1의 인터럽트 스프레드 방법이 적용되는 것으로 설명되었지만, 인액티브 상태인 프로세서들에 입력되는 인터럽트 요청 신호들에 대해서만 도 1의 인터럽트 스프레드 방법이 적용될 수도 있다.Generally, when an interrupt request signal is received, the processor changes from an inactive state to an active state, and then performs an interrupt processing (i.e., an interrupt service). At this time, the inrush current is generated while the plurality of transistors constituting the inside of the processor suddenly start operating. Particularly, in the case of a low-power processor, since most clocks are not toggled in the inactive state because a plurality of clock gating circuits are provided to reduce power consumption in an inactive state, Is changed from the inactive state to the active state, most of the clocks start the toggle at the same time, so that the inrush current can be largely generated. At this time, if a plurality of processors suddenly wake up within a short time, an inrush current generated by a plurality of processors is added, and the power supply of the peripheral circuit becomes unstable, so that malfunction may occur. The interrupt spread method of FIG. 1 is characterized in that when a plurality of interrupt sources successively output a plurality of interrupts in a short time, a time interval between a plurality of interrupt request signals generated based on the interrupts is set to at least a predetermined interval , It is possible to prevent a plurality of processors (e.g., multicore processors, etc.) in an inactive state from being continuously changed to an active state in a short time (i.e., sudden wake-up) . As a result, an inrush current due to a sudden wake-up in a plurality of processors (or a plurality of cores of a multicore processor) is prevented from being generated in the system on-chip, The electronic device can secure high operation stability. 1, the interrupt spread method of FIG. 1 is applied to the interrupt request signals input to all processors irrespective of whether the plurality of processors are in an active state or an active state. However, The interrupt spread method of FIG. 1 may be applied only to the interrupt request signals input to the processors.

도 2a 및 도 2b는 도 1의 인터럽트 스프레드 방법이 수행되는 일 예를 나타내는 도면들이다.FIGS. 2A and 2B are diagrams illustrating an example in which the interrupt spread method of FIG. 1 is performed.

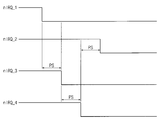

도 2a 및 도 2b를 참조하면, 도 2a는 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 순차적으로 입력되는 것을 보여주고 있고, 도 2b는 도 1의 인터럽트 스프레드 방법에 의하여 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 제 1 내지 제 4 프로세서들에 순차적으로 출력되는 것을 보여주고 있다.Referring to FIGS. 2A and 2B, FIG. 2A shows that the first to fourth interrupt request signals nIRQ_1,..., NIRQ_4 are sequentially input. FIG. The first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4 are sequentially output to the first to fourth processors.

구체적으로, 도 1의 인터럽트 스프레드 방법은 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)을 순차적으로 수신할 수 있다. 도 2a에 도시된 바와 같이, 제 1 인터럽트 요청 신호(nIRQ_1)와 제 2 인터럽트 요청 신호(nIRQ_2) 사이의 제 1 시간 간격(S1)은 기 설정된 간격(PS)보다 작고, 제 2 인터럽트 요청 신호(nIRQ_2)와 제 3 인터럽트 요청 신호(nIRQ_3) 사이의 제 2 시간 간격(S2)도 기 설정된 간격(PS)보다 작으며, 제 3 인터럽트 요청 신호(nIRQ_3)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 3 시간 간격(S3)도 기 설정된 간격(PS)보다 작다. 이에, 도 2b에 도시된 바와 같이, 도 1의 인터럽트 스프레드 방법은 제 1 인터럽트 요청 신호(nIRQ_1)와 제 2 인터럽트 요청 신호(nIRQ_2) 사이의 제 1 시간 간격(S1)이 기 설정된 간격(PS)이 되도록 제 2 인터럽트 요청 신호(nIRQ_2)의 출력을 지연시키고, 제 2 인터럽트 요청 신호(nIRQ_2)와 제 3 인터럽트 요청 신호(nIRQ_3) 사이의 제 2 시간 간격(S2)이 기 설정된 간격(PS)이 되도록 제 3 인터럽트 요청 신호(nIRQ_3)의 출력을 지연시키며, 제 3 인터럽트 요청 신호(nIRQ_3)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 3 시간 간격(S3)이 기 설정된 간격(PS)이 되도록 제 4 인터럽트 요청 신호(nIRQ_4)의 출력을 지연시킬 수 있다. 이와 같이, 도 1의 인터럽트 스프레드 방법은 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)을 기 설정된 간격(PS)을 두어 제 1 내지 제 4 프로세서들에 순차적으로 출력할 수 있다.Specifically, the interrupt spread method of FIG. 1 can sequentially receive the first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4. 2A, the first time interval S1 between the first interrupt request signal nIRQ_1 and the second interrupt request signal nIRQ_2 is smaller than the predetermined interval PS and the second interrupt request signal nIRQ_2 is smaller than the predetermined interval PS, the second time interval S2 between the third interrupt request signal nIRQ_2 and the third interrupt request signal nIRQ_3 is also smaller than the predetermined interval PS and the second time interval S2 between the third interrupt request signal nIRQ_3 and the fourth interrupt request signal nIRQ_4 The third time interval S3 is also smaller than the predetermined interval PS. 1, the first interrupt interval S1 between the first interrupt request signal nIRQ_1 and the second interrupt request signal nIRQ_2 is set to a predetermined interval PS, And the second interval S2 between the second interrupt request signal nIRQ_2 and the third interrupt request signal nIRQ_3 delays the output of the second interrupt request signal nIRQ_2 to a predetermined interval PS The output of the third interrupt request signal nIRQ_3 is delayed so that the third time interval S3 between the third interrupt request signal nIRQ_3 and the fourth interrupt request signal nIRQ_4 becomes a predetermined interval PS It is possible to delay the output of the fourth interrupt request signal nIRQ_4. 1, the first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4 may be sequentially output to the first to fourth processors with a predetermined interval PS have.

도 3a 및 도 3b는 도 1의 인터럽트 스프레드 방법이 수행되는 다른 예를 나타내는 도면들이다.FIGS. 3A and 3B are diagrams showing another example in which the interrupt spread method of FIG. 1 is performed. FIG.

도 3a 및 도 3b를 참조하면, 도 3a는 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 순차적으로 입력되는 것을 보여주고 있고, 도 3b는 도 1의 인터럽트 스프레드 방법에 의하여 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 제 1 내지 제 4 프로세서들에 순차적으로 출력되는 것을 보여주고 있다.3A and 3B, FIG. 3A shows that first through fourth interrupt request signals nIRQ_1 through nIRQ_4 are sequentially input. FIG. 3B illustrates an interrupt spreading method of FIG. The first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4 are sequentially output to the first to fourth processors.

구체적으로, 도 1의 인터럽트 스프레드 방법은 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)을 순차적으로 수신할 수 있다. 도 3a에 도시된 바와 같이, 제 1 인터럽트 요청 신호(nIRQ_1)와 제 2 인터럽트 요청 신호(nIRQ_2) 사이의 제 1 시간 간격(S1)은 기 설정된 간격(PS)보다 크고, 제 2 인터럽트 요청 신호(nIRQ_2)와 제 3 인터럽트 요청 신호(nIRQ_3) 사이의 제 2 시간 간격(S2)은 기 설정된 간격(PS)보다 작으며, 제 3 인터럽트 요청 신호(nIRQ_3)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 3 시간 간격(S3)은 기 설정된 간격(PS)보다 작다. 이에, 도 3b에 도시된 바와 같이, 도 1의 인터럽트 스프레드 방법은 제 1 인터럽트 요청 신호(nIRQ_1)와 제 2 인터럽트 요청 신호(nIRQ_2) 사이의 제 1 시간 간격(S1)은 그대로 유지시키고, 제 2 인터럽트 요청 신호(nIRQ_2)와 제 3 인터럽트 요청 신호(nIRQ_3) 사이의 제 2 시간 간격(S2)이 기 설정된 간격(PS)이 되도록 제 3 인터럽트 요청 신호(nIRQ_3)의 출력을 지연시키며, 제 3 인터럽트 요청 신호(nIRQ_3)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 3 시간 간격(S3)이 기 설정된 간격(PS)이 되도록 제 4 인터럽트 요청 신호(nIRQ_4)의 출력을 지연시킬 수 있다. 이와 같이, 도 1의 인터럽트 스프레드 방법은 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)을 기 설정된 간격(PS) 이상을 두어 제 1 내지 제 4 프로세서들에 순차적으로 출력할 수 있다.Specifically, the interrupt spread method of FIG. 1 can sequentially receive the first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4. 3A, a first time interval S1 between the first interrupt request signal nIRQ_1 and the second interrupt request signal nIRQ_2 is greater than a predetermined interval PS, and a second interrupt request signal the second time interval S2 between the third interrupt request signal nIRQ_2 and the third interrupt request signal nIRQ_3 is smaller than the predetermined interval PS and the third interrupt request signal nIRQ_2 is between the third interrupt request signal nIRQ_3 and the fourth interrupt request signal nIRQ_4. The third time interval S3 is less than the predetermined interval PS. As shown in FIG. 3B, the interrupt spread method of FIG. 1 maintains the first time interval S1 between the first interrupt request signal nIRQ_1 and the second interrupt request signal nIRQ_2 as it is, The output of the third interrupt request signal nIRQ_3 is delayed so that the second time interval S2 between the interrupt request signal nIRQ_2 and the third interrupt request signal nIRQ_3 becomes the predetermined interval PS, The output of the fourth interrupt request signal nIRQ_4 may be delayed such that the third time interval S3 between the request signal nIRQ_3 and the fourth interrupt request signal nIRQ_4 becomes the predetermined interval PS. In this way, the interrupt spread method of FIG. 1 sequentially outputs the first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4 to the first to fourth processors with a predetermined interval (PS) or more .

도 4a 및 도 4b는 도 1의 인터럽트 스프레드 방법이 수행되는 또 다른 예를 나타내는 도면들이다.4A and 4B are diagrams showing still another example in which the interrupt spread method of FIG. 1 is performed.

도 4a 및 도 4b를 참조하면, 도 4a는 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 순차적으로 입력되는 것을 보여주고 있고, 도 4b는 도 1의 인터럽트 스프레드 방법에 의하여 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 제 1 내지 제 4 프로세서들에 순차적으로 출력되는 것을 보여주고 있다.Referring to FIGS. 4A and 4B, FIG. 4A shows sequentially inputting first through fourth interrupt request signals nIRQ_1,..., NIRQ_4, FIG. 4B illustrates an interrupt spread method The first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4 are sequentially output to the first to fourth processors.

구체적으로, 도 1의 인터럽트 스프레드 방법은 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)을 순차적으로 수신할 수 있다. 도 4a에 도시된 바와 같이, 제 1 인터럽트 요청 신호(nIRQ_1)와 제 2 인터럽트 요청 신호(nIRQ_2) 사이의 제 1 시간 간격(S1)은 기 설정된 간격(PS)보다 작고, 제 2 인터럽트 요청 신호(nIRQ_2)와 제 3 인터럽트 요청 신호(nIRQ_3) 사이의 제 2 시간 간격(S2)은 기 설정된 간격(PS)보다 작으며, 제 3 인터럽트 요청 신호(nIRQ_3)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 3 시간 간격(S3)도 기 설정된 간격(PS)보다 작다. 그러나, 시스템 온-칩의 성능에 따라, 2개의 프로세서들이 짧은 시간 내에 연속적으로 웨이크-업을 하더라도, 2개의 프로세서들 내부에 인러쉬 전류가 생성되지 않을 수 있고, 3개의 프로세서들이 짧은 시간 내에 연속적으로 웨이크-업을 하더라도, 3개의 프로세서들 내부에 인러쉬 전류가 생성되지 않을 수 있다. 이하, 도 4a 및 도 4b에서는 2개의 프로세서들이 짧은 시간 내에 연속적으로 웨이크-업하는 것을 허용하나, 3개의 프로세서들이 짧은 시간 내에 연속적으로 웨이크-업하는 것은 허용하지 않는 것으로 가정하고 설명하기로 한다. 예를 들어, 도 4b에 도시된 바와 같이, 도 1의 인터럽트 스프레드 방법은 기 설정된 개수(즉, 2개)의 프로세서들이 짧은 시간 내에 연속적으로 웨이크-업을 하는 것을 허용하고 있으므로, 제 1 인터럽트 요청 신호(nIRQ_1)와 제 2 인터럽트 요청 신호(nIRQ_2) 사이의 제 1 시간 간격(S1)이 기 설정된 간격(PS)보다 작더라도, 제 1 인터럽트 요청 신호(nIRQ_1)와 제 2 인터럽트 요청 신호(nIRQ_2) 사이의 제 1 시간 간격(S1)을 그대로 유지시킬 수 있다. 그러나, 도 1의 인터럽트 스프레드 방법은 3개의 프로세서들이 짧은 시간 내에 연속적으로 웨이크-업을 하는 것을 허용하지 않으므로, 제 2 인터럽트 요청 신호(nIRQ_2)와 제 3 인터럽트 요청 신호(nIRQ_3) 사이의 제 2 시간 간격(S2)이 기 설정된 간격(PS)보다 작기 때문에, 상기 제 2 시간 간격(S2)이 기 설정된 간격(PS)이 되도록 제 3 인터럽트 요청 신호(nIRQ_3)의 출력을 지연시킬 수 있다. 이후, 도 1의 인터럽트 스프레드 방법은 2개의 프로세서들이 짧은 시간 내에 연속적으로 웨이크-업을 하는 것을 허용하고 있으므로, 제 3 인터럽트 요청 신호(nIRQ_3)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 3 시간 간격(S3)이 기 설정된 간격(PS)보다 작더라도, 제 3 인터럽트 요청 신호(nIRQ_3)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 3 시간 간격(S3)을 그대로 유지시킬 수 있다.Specifically, the interrupt spread method of FIG. 1 can sequentially receive the first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4. 4A, the first time interval S1 between the first interrupt request signal nIRQ_1 and the second interrupt request signal nIRQ_2 is smaller than the predetermined interval PS and the second interrupt request signal nIRQ_2 is smaller than the predetermined interval PS, the second time interval S2 between the third interrupt request signal nIRQ_2 and the third interrupt request signal nIRQ_3 is smaller than the predetermined interval PS and the third interrupt request signal nIRQ_2 is between the third interrupt request signal nIRQ_3 and the fourth interrupt request signal nIRQ_4. The third time interval S3 is also smaller than the predetermined interval PS. However, depending on the performance of the system on-chip, even if two processors continuously wake up in a short time, an inrush current may not be generated within the two processors, and three processors may be continuously The inrush current may not be generated in the three processors. 4A and 4B, it is assumed that the two processors allow continuous wake-up in a short time, but do not allow the three processors to successively wake up in a short time. For example, as shown in FIG. 4B, the interrupt spread method of FIG. 1 allows a predetermined number (i.e., two) of processors to continuously wake up in a short time, The first interrupt request signal nIRQ_1 and the second interrupt request signal nIRQ_2 are set to the same value even if the first time interval S1 between the signal nIRQ_1 and the second interrupt request signal nIRQ_2 is smaller than the predetermined interval PS, The first time interval S1 can be maintained as it is. However, since the interrupt spread method of FIG. 1 does not allow the three processors to continuously wake up in a short time, a second time between the second interrupt request signal nIRQ_2 and the third interrupt request signal nIRQ_3 The output of the third interrupt request signal nIRQ_3 may be delayed so that the second time interval S2 becomes the predetermined interval PS since the interval S2 is smaller than the predetermined interval PS. Since the interrupt spread method of Fig. 1 allows the two processors to continuously wake up in a short time, a third time between the third interrupt request signal nIRQ_3 and the fourth interrupt request signal nIRQ_4 The third time interval S3 between the third interrupt request signal nIRQ_3 and the fourth interrupt request signal nIRQ_4 can be maintained as it is even if the interval S3 is smaller than the predetermined interval PS.

도 5는 본 발명의 다른 실시예에 따른 인터럽트 스프레드 방법을 나타내는 순서도이다.5 is a flowchart illustrating an interrupt spread method according to another embodiment of the present invention.

도 5를 참조하면, 도 5의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호를 수신(Step S210)하고, 제 k+1 인터럽트 요청 신호를 수신(Step S220)한 후, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 0보다 큰지 여부를 판단(Step S230)할 수 있다. 이 때, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 0보다 큰 경우, 상기 시간 간격이 기 설정된 간격으로 될 때까지 제 k 인터럽트 요청 신호의 출력을 지연(Step S240)시키고, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 0인 경우, 기 설정된 우선순위에 따라 제 k 인터럽트 요청 신호 또는 제 k+1 인터럽트 요청 신호의 출력을 기 설정된 간격만큼 지연(Step S250)시킬 수 있다. 다만, 도 5에서는 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 기 설정된 간격보다 작은 것으로 가정되어 있다.5, the interrupt spread method receives a k-th interrupt request signal (Step S210), receives a (k + 1) -th interrupt request signal (Step S220) It can be determined whether the time interval between the +1 interrupt request signals is greater than 0 (Step S230). At this time, if the time interval between the k-th interrupt request signal and the k + 1-th interrupt request signal is greater than 0, the output of the k-th interrupt request signal is delayed (Step S240) K interrupt request signal and the (k + 1) -th interrupt request signal at a predetermined interval according to a predetermined priority when the time interval between the k-th interrupt request signal and the k + (Step S250). In FIG. 5, it is assumed that the time interval between the k-th interrupt request signal and the (k + 1) -th interrupt request signal is smaller than a predetermined interval.

도 5의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호를 순차적으로 수신하고, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 기 설정된 간격보다 작은지 여부를 판단함에 있어서, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 0보다 큰지 여부까지 판단한다. 즉, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호가 순차적으로 입력된다고 보면, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격은 0보다 큰 것이 일반적이나, 실시예에 따라 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호가 실질적으로 동시에 입력될 수도 있으므로, 도 5의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 0보다 큰지 여부까지 판단하는 것이다. 이 때, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 0보다 큰 경우, 도 5의 인터럽트 스프레드 방법은 상기 시간 간격이 기 설정된 간격으로 될 때까지 제 k 인터럽트 요청 신호의 출력을 지연시킬 수 있고, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 0인 경우, 도 5의 인터럽트 스프레드 방법은 기 설정된 우선순위에 따라 제 k 인터럽트 요청 신호 또는 제 k+1 인터럽트 요청 신호의 출력을 기 설정된 간격만큼 지연시킬 수 있다. 그 결과, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호가 동시에 입력되는 경우에도 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호가 기 설정된 간격을 두어 각각 제 k 프로세서와 제 k+1 프로세서에 출력되기 때문에, 도 5의 인터럽트 스프레드 방법은 시스템 온-칩에서 짧은 시간 내에 복수의 프로세서들이 인액티브 상태에서 액티브 상태로 변경(즉, 급작스러운 웨이크-업)되는 것을 방지할 수 있다.The interrupt spread method of FIG. 5 sequentially receives the k-th interrupt request signal and the (k + 1) -th interrupt request signal, and determines whether the time interval between the k-th interrupt request signal and the (k + 1) -th interrupt request signal is less than It is determined whether the time interval between the k-th interrupt request signal and the (k + 1) -th interrupt request signal is greater than zero. In other words, when the k-th interrupt request signal and the (k + 1) -th interrupt request signal are sequentially input, the time interval between the k-th interrupt request signal and the (k + Therefore, the time interval between the k-th interrupt request signal and the (k + 1) -th interrupt request signal is greater than 0 because the k-th interrupt request signal and the k + 1-th interrupt request signal may be input substantially simultaneously. It is judged whether it is big or not. If the time interval between the k < th > interrupt request signal and the (k + 1) -th interrupt request signal is greater than 0, the interrupt spread method of FIG. And if the time interval between the k < th > interrupt request signal and the (k + 1) -th interrupt request signal is 0, the interrupt spread method of FIG. 5 may delay the output of the k & The output of the +1 interrupt request signal may be delayed by a predetermined interval. As a result, even if the k-th interrupt request signal and the (k + 1) -th interrupt request signal are inputted at the same time, the k-th interrupt request signal and the (k + 1) The interrupt spread method of FIG. 5 can prevent a plurality of processors from changing from an inactive state to an active state (i. E., Sudden wake-up) in a short time on a system on-chip.

도 6a 및 도 6b는 도 5의 인터럽트 스프레드 방법이 수행되는 일 예를 나타내는 도면들이다.6A and 6B are diagrams illustrating an example in which the interrupt spread method of FIG. 5 is performed.

도 6a 및 도 6b를 참조하면, 도 6a는 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 순차적으로 입력되는 것을 보여주고 있고, 도 6b는 도 5의 인터럽트 스프레드 방법에 의하여 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 제 1 내지 제 4 프로세서들에 순차적으로 출력되는 것을 보여주고 있다.Referring to FIGS. 6A and 6B, FIG. 6A shows that the first to fourth interrupt request signals nIRQ_1,..., NIRQ_4 are sequentially input. FIG. 6B shows an interrupt spread method The first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4 are sequentially output to the first to fourth processors.

구체적으로, 도 5의 인터럽트 스프레드 방법은 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)을 순차적으로 수신할 수 있는데, 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4) 중에서 인접하는 인터럽트 요청 신호들이 실질적으로 동시에 입력될 수 있다. 예를 들어, 도 6a에 도시된 바와 같이, 제 1 인터럽트 요청 신호(nIRQ_1)와 제 2 인터럽트 요청 신호(nIRQ_2) 사이의 제 1 시간 간격(S1)은 기 설정된 간격(PS)보다 작고, 제 2 인터럽트 요청 신호(nIRQ_2)와 제 3 인터럽트 요청 신호(nIRQ_3) 사이의 제 2 시간 간격(S2)도 기 설정된 간격(PS)보다 작으며, 제 3 인터럽트 요청 신호(nIRQ_3)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 3 시간 간격(S3)은 0에 상응한다. 따라서, 제 4 인터럽트 요청 신호(nIRQ_4)의 우선순위가 제 3 인터럽트 요청 신호(nIRQ_3)의 우선순위보다 높다고 가정하면, 도 6b에 도시된 바와 같이, 도 5의 인터럽트 스프레드 방법은 제 1 인터럽트 요청 신호(nIRQ_1)와 제 2 인터럽트 요청 신호(nIRQ_2) 사이의 제 1 시간 간격(S1)이 기 설정된 간격(PS)이 되도록 제 2 인터럽트 요청 신호(nIRQ_2)의 출력을 지연시키고, 제 2 인터럽트 요청 신호(nIRQ_2)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 2 시간 간격(S2)이 기 설정된 간격(PS)이 되도록 제 4 인터럽트 요청 신호(nIRQ_4)의 출력을 지연시키며, 제 3 인터럽트 요청 신호(nIRQ_3)와 제 4 인터럽트 요청 신호(nIRQ_4) 사이의 제 3 시간 간격(S3)은 기 설정된 간격(PS)이 되도록 제 3 인터럽트 요청 신호(nIRQ_3)의 출력을 지연시킬 수 있다. 이 때, 제 4 인터럽트 요청 신호(nIRQ_4)의 우선순위가 제 3 인터럽트 요청 신호(nIRQ_3)의 우선순위보다 높기 때문에, 제 3 인터럽트 요청 신호(nIRQ_3)보다 제 4 인터럽트 요청 신호(nIRQ_4)가 먼저 출력된 것이다. 이와 같이, 도 5의 인터럽트 스프레드 방법은 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_I1, ..., nIRQ_I4) 중에서 인접하는 인터럽트 요청 신호들이 실질적으로 동시에 입력되더라도, 기 설정된 우선순위에 따라 기 설정된 간격(PS)을 두어, 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)을 제 1 내지 제 4 프로세서들에 순차적으로 출력할 수 있다.5 may sequentially receive the first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4. The first to fourth interrupt request signals nIRQ_1, ..., nIRQ_4 may be sequentially received. ., nIRQ_4) can be input at substantially the same time. 6A, the first time interval S1 between the first interrupt request signal nIRQ_1 and the second interrupt request signal nIRQ_2 is smaller than the predetermined interval PS, The second time interval S2 between the interrupt request signal nIRQ_2 and the third interrupt request signal nIRQ_3 is also smaller than the predetermined interval PS and the third interrupt request signal nIRQ_3 and the fourth interrupt request signal nIRQ_3, lt; RTI ID = 0.0 > nIRQ_4 < / RTI > Accordingly, assuming that the priority of the fourth interrupt request signal nIRQ_4 is higher than that of the third interrupt request signal nIRQ_3, as shown in FIG. 6B, the interrupt spread method of FIG. the output of the second interrupt request signal nIRQ_2 is delayed so that the first time interval S1 between the first interrupt request signal nIRQ_1 and the second interrupt request signal nIRQ_2 becomes the predetermined interval PS, the output of the fourth interrupt request signal nIRQ_4 is delayed so that the second time interval S2 between the fourth interrupt request signal nIRQ_2 and the fourth interrupt request signal nIRQ_4 becomes the predetermined interval PS, And the fourth interrupt request signal nIRQ_4 may delay the output of the third interrupt request signal nIRQ_3 to a predetermined interval PS. At this time, since the priority of the fourth interrupt request signal nIRQ_4 is higher than that of the third interrupt request signal nIRQ_3, the fourth interrupt request signal nIRQ_4 is outputted first than the third interrupt request signal nIRQ_3 . 5, even if adjacent interrupt request signals among the first to fourth interrupt request signals nIRQ_I1, ..., nIRQ_I4 are input substantially simultaneously, the interrupt spread method of FIG. (NIRQ_1, ..., nIRQ_4) sequentially to the first to fourth processors by placing the first to fourth interrupt request signals (PS).

도 7은 본 발명의 또 다른 실시예에 따른 인터럽트 스프레드 방법을 나타내는 순서도이다.7 is a flowchart showing an interrupt spread method according to another embodiment of the present invention.

도 7을 참조하면, 도 7의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호를 수신(Step S310)하고, 제 k+1 인터럽트 요청 신호를 수신(Step S320)한 후, 제 k 인터럽트 요청 신호가 제 k+1 인터럽트 요청 신호보다 우선순위가 높은지 여부를 판단(Step S330)할 수 있다. 이 때, 도 7의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호의 우선순위가 제 k+1 인터럽트 요청 신호의 우선순위보다 높으면, 제 k+1 인터럽트 요청 신호를 지연(Step S340)시킬 수 있고, 제 k 인터럽트 요청 신호의 우선순위가 제 k+1 인터럽트 요청 신호의 우선순위보다 낮으면, 제 k 인터럽트 요청 신호를 지연(Step S345)시킬 수 있다. 다만, 도 7에서는 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 기 설정된 간격보다 작은 것으로 가정되어 있다.Referring to FIG. 7, the interrupt spread method of FIG. 7 receives a kth interrupt request signal (Step S310), receives a k + 1 interrupt request signal (Step S320) It can be determined whether the priority is higher than that of the +1 interrupt request signal (Step S330). In this case, if the priority of the k-th interrupt request signal is higher than that of the (k + 1) -th interrupt request signal, the interrupt spread method of FIG. 7 can delay the k + If the priority of the k-th interrupt request signal is lower than the priority of the (k + 1) -th interrupt request signal, the k-th interrupt request signal may be delayed (Step S345). However, it is assumed in FIG. 7 that the time interval between the k-th interrupt request signal and the (k + 1) -th interrupt request signal is smaller than a predetermined interval.

도 7의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호를 순차적으로 수신하고, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호 사이의 시간 간격이 기 설정된 간격보다 작은지 여부를 판단함에 있어서, 제 k 인터럽트 요청 신호가 제 k+1 인터럽트 요청 신호보다 우선순위가 높은지 여부까지 판단할 수 있다. 이에, 도 7의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호의 입력 순서와는 별개로, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호의 출력 순서를 결정할 수 있다. 구체적으로, 도 7의 인터럽트 스프레드 방법은 제 k 인터럽트 요청 신호의 우선순위가 제 k+1 인터럽트 요청 신호의 우선순위보다 높으면, 제 k+1 인터럽트 요청 신호를 지연시킬 수 있고, 제 k 인터럽트 요청 신호의 우선순위가 제 k+1 인터럽트 요청 신호의 우선순위보다 낮으면, 제 k 인터럽트 요청 신호를 지연시킬 수 있다. 그 결과, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호가 순차적으로 입력되는 경우에도, 제 k 인터럽트 요청 신호와 제 k+1 인터럽트 요청 신호가 기 설정된 우선순위에 따라 비순차적으로 출력되고, 그 때에도 제 k+1 인터럽트 요청 신호와 제 k 인터럽트 요청 신호가 기 설정된 간격을 두어 각각 제 k 프로세서와 제 k+1 프로세서에 출력되기 때문에, 도 7의 인터럽트 스프레드 방법은 시스템 온-칩에서 짧은 시간 내에 복수의 프로세서들이 인액티브 상태에서 액티브 상태로 변경(즉, 급작스러운 웨이크-업)되는 것을 방지할 수 있다.The interrupt spread method of FIG. 7 sequentially receives the k-th interrupt request signal and the (k + 1) -th interrupt request signal and determines whether the time interval between the k-th interrupt request signal and the (k + 1) -th interrupt request signal is less than It is possible to determine whether the k < th > interrupt request signal has a higher priority than the (k + 1) -th interrupt request signal. 7, the output order of the k-th interrupt request signal and the k + 1-th interrupt request signal can be determined independently of the input order of the k-th interrupt request signal and the (k + 1) -th interrupt request signal . 7 can delay the (k + 1) -th interrupt request signal if the priority of the k-th interrupt request signal is higher than that of the (k + 1) -th interrupt request signal, K interrupt request signal if the priority of the (k + 1) -th interrupt request signal is lower than the priority of the (k + 1) -th interrupt request signal. As a result, even when the k-th interrupt request signal and the (k + 1) -th interrupt request signal are sequentially input, the k-th interrupt request signal and the (k + 1) -th interrupt request signal are output in a non- Since the (k + 1) -th interrupt request signal and the k-th interrupt request signal are output to the k-th processor and (k + 1) -th processor at predetermined intervals, respectively, the interrupt spread method of FIG. It is possible to prevent a plurality of processors from changing from an inactive state to an active state (i.e., sudden wake-up).

도 8a 및 도 8b는 도 7의 인터럽트 스프레드 방법이 수행되는 일 예를 나타내는 도면들이다.8A and 8B are diagrams illustrating an example in which the interrupt spread method of FIG. 7 is performed.

도 8a 및 도 8b를 참조하면, 도 8a는 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 순차적으로 입력되는 것을 보여주고 있고, 도 8b는 도 7의 인터럽트 스프레드 방법에 의하여 제 1 내지 제 4 인터럽트 요청 신호들(nIRQ_1, ..., nIRQ_4)이 기 설정된 우선순위에 따라 제 1 내지 제 4 프로세서들에 각각 출력되는 것을 보여주고 있다.8A and 8B show that the first through fourth interrupt request signals nIRQ_1 through nIRQ_4 are sequentially input. FIG. 8B illustrates an interrupt spreading method of FIG. The first through fourth interrupt request signals nIRQ_1 through nIRQ_4 are output to the first through fourth processors, respectively, according to a predetermined priority.