KR101226435B1 - 감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및표시장치 - Google Patents

감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및표시장치 Download PDFInfo

- Publication number

- KR101226435B1 KR101226435B1 KR1020060013928A KR20060013928A KR101226435B1 KR 101226435 B1 KR101226435 B1 KR 101226435B1 KR 1020060013928 A KR1020060013928 A KR 1020060013928A KR 20060013928 A KR20060013928 A KR 20060013928A KR 101226435 B1 KR101226435 B1 KR 101226435B1

- Authority

- KR

- South Korea

- Prior art keywords

- power supply

- resistor

- gamma

- supply voltage

- gamma reference

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3696—Generation of voltages supplied to electrode drivers

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0267—Details of drivers for scan electrodes, other than drivers for liquid crystal, plasma or OLED displays

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/027—Details of drivers for data electrodes, the drivers handling digital grey scale data, e.g. use of D/A converters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0275—Details of drivers for data electrodes, other than drivers for liquid crystal, plasma or OLED displays, not related to handling digital grey scale data or to communication of data to the pixels by means of a current

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0247—Flicker reduction other than flicker reduction circuits used for single beam cathode-ray tubes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0285—Improving the quality of display appearance using tables for spatial correction of display data

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/041—Temperature compensation

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0673—Adjustment of display parameters for control of gamma adjustment, e.g. selecting another gamma curve

Abstract

온도 보상 기능을 갖는 감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및 표시장치가 개시된다. 제1 메인 온도 보상부는 제1 전원전압에 연결되고, 복수의 제1 극성 감마기준전압들을 출력하는 제1 저항 스트링에 연결되며, 온도 증가에 따라 증가하는 저항치를 갖는다. 제2 메인 온도 보상부는 제1 전원전압보다는 낮은 제2 전원전압에 연결되고, 복수의 제2 극성 감마기준전압들을 출력하는 제2 저항 스트링에 연결되며, 온도 증가에 따라 감소하는 저항치를 갖는다. 이에 따라, 온도 증가에 따라 화이트 계조측의 감마기준전압은 상대적으로 레벨 다운되고, 블랙 계조측의 감마기준전압을 유지되어 화이트 계조측의 킥백 전압의 편차는 줄어들어 표시 특성의 악화가 방지된다.

액정, 감마기준전압, 킥백, 온도, 써미스터

Description

도 1은 일반적인 액정 표시 장치의 단위 화소를 설명하는 등가 회로도이다.

도 2는 도 1의 화소에 인가되는 게이트 전압과 액정 캐패시터에 인가되는 전압을 비교하여 나타낸 파형도이다.

도 3a 및 도 3b는 온도에 따른 액정의 유전률 변화를 설명하는 그래프들이다.

도 4는 본 발명의 일실시예에 따른 감마기준전압 생성회로를 설명하는 회로도이다.

도 5는 본 발명의 다른 실시예에 따른 감마기준전압 생성회로를 설명하는 회로도이다.

도 6은 본 발명의 또 다른 실시예에 따른 감마전압 생성부를 설명하는 블록도이다.

도 7은 본 발명의 또 다른 실시예에 따른 액정 표시 장치를 설명하기 위한 블록도이다.

도 8은 도 7에 도시된 액정 표시 장치의 동작을 설명하기 위한 블록도이다.

도 9는 본 발명의 또 다른 실시예에 따른 액정 표시 장치를 설명하기 위한 블록도이다.

도 10은 도 9에 도시된 감마기준전압 저장부를 설명하는 블록도이다.

<도면의 주요부분에 대한 부호의 설명>

110, 312 : 제1 저항 스트링 120, 314 : 제2 저항 스트링

130 : 제1 온도 보상부 140 : 제2 온도 보상부

200 : 감마기준전압 생성회로 210, 316 : 제1 메인 온도 보상부

220 : 제1 서브 온도 보상부 230 : 제2 서브 온도 보상부

240, 318 : 제2 메인 온도 보상부 310 : 감마기준전압 생성부

320 : 감마전압 출력부 410 : 타이밍 제어부

420 : 감마전압 생성부 430 : 데이터 구동부

440 : 게이트 구동부 450 : 액정 표시 패널

510 : 온도 센서 520 : 감마기준전압 저장부

530 : 감마전압 생성부

본 발명은 감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및 표시장치에 관한 것으로, 보다 상세하게는 온도 보상 기능을 갖는 감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및 표시장치에 관한 것이다.

일반적으로 액정 표시 장치(liquid crystal display; LCD)는 박막 트랜지스터(thin film transistor; TFT)를 사용하여 아날로그 계조 전압을 픽셀(pixel)에 인가함으로써 영상을 표시한다. 상기 계조 전압은 액정 표시 장치의 데이터 라인에 공급되어 데이터 전압이다.

상기 데이터 전압은 게이트 전압이 하이 상태로 되어 상기 박막 트랜지스터가 턴-온될 때, 픽셀을 이루는 액정 캐패시터와 스토리지 캐패시터에 충전됨으로써 픽셀 전압으로 나타난다. 상기 픽셀에 충전된 전압의 크기에 따라 공통 전압사이의 액정 캐패시터의 작용으로 빛의 투과 정도가 달라져 계조가 표시된다.

상기 픽셀의 박막 트랜지스터의 게이트 전압이 하이 상태일 때, 픽셀에 충전되는 전압은 데이터 전압까지 충전되게 된다. 그러나 상기 픽셀의 박막 트랜지스터의 게이트 전압이 로우 상태로 변하는 순간에 픽셀 전압은 충전된 데이터 전압을 유지하는 것이 아니라, 상기 픽셀 박막 트랜지스터의 기생 커패시터에 의하여 킥백 전압만큼 왜곡되어 나타난다.

상기 킥백 전압은 픽셀 전압뿐만 아니라 픽셀 전압과 공통 전극 전압의 차이 즉 액정 캐패시터에 충전되는 전압에 따라 달라진다. 이는 액정의 유전율 이방성(dielectric anisotropic)에서 기인된다. 그러므로 화이트 계조 표시시와 블랙 계조 표시시에 따라 액정 캐패시턴스가 달라지므로 각 계조별로 킥백 전압이 달라진다.

상기 계조별 킥백 전압의 차이로 인해 액정 표시 장치의 특정 화면이 장시간 방치된 후 새로운 패턴의 화면으로 전환될 때, 기존의 화면이 잔상의 형태로 남아 있는 이미지 스티킹(image sticking)이 유발된다.

상기 이미지 스티킹을 개선하기 위하여 일례로, 계조별 킥백 전압을 계산하여 감마를 보정하므로써, 잔류 DC 전압을 줄이는 방법이 이용된다.

다른 일례로, 킥백 전압의 절대치를 줄여 계조별 킥백 전압의 차이를 줄이는 방법이 이용된다.

이에 본 발명의 기술적 과제는 이러한 점에 착안한 것으로, 본 발명의 목적은 온도 변화에 따라 화이트 계조측에서는 킥백 전압의 변화가 상대적으로 크고, 블랙 계조측에서는 킥백 전압의 변화가 상대적으로 작은 상태에서 온도 보상 동작을 수행하는 감마기준전압 생성회로를 제공하는 것이다.

본 발명의 다른 목적은 상기한 감마기준전압 생성회로를 갖는 감마전압 생성장치를 제공하는 것이다.

본 발명의 또 다른 목적은 상기한 감마전압 생성장치를 갖는 표시장치를 제공하는 것이다.

상기한 본 발명의 목적을 실현하기 위하여 일실시예에 따른 감마기준전압 생성회로는 제1 저항 스트링, 제2 저항 스트링, 제1 메인 온도 보상부 및 제2 메인 온도 보상부를 포함한다. 상기 제1 저항 스트링은 복수의 제1 극성 감마기준전압들을 출력한다. 상기 제2 저항 스트링은 복수의 제2 극성 감마기준전압들을 출력한다. 상기 제1 메인 온도 보상부는 일단이 제1 전원전압에 전기적으로 연결되고, 타 단이 상기 제1 저항 스트링에 전기적으로 연결되며, 온도 증가에 따라 증가하는 저항치를 갖는다. 상기 제2 메인 온도 보상부는 일단이 상기 제1 전원전압보다는 낮은 제2 전원전압에 전기적으로 연결되고, 타단이 상기 제2 저항 스트링에 전기적으로 연결되며, 온도 증가에 따라 감소하는 저항치를 갖는다.

상기한 본 발명의 다른 목적을 실현하기 위하여 일실시예에 따른 감마전압 생성장치는 감마기준전압 생성회로 및 감마전압 출력부를 포함한다. 상기 감기기준전압 생성회로는 복수의 감마기준전압들을 출력하는 저항 스트링과, 전원전압이 공급되는 전원전압단과 고계조에 대응하는 감마기준전압을 출력하는 저항 스트링에 전기적으로 연결되고, 온도에 따라 가변하는 저항치를 갖는 메인 온도 보상부를 포함한다. 상기 감마전압 출력부는 상기 감마기준전압 생성회로에서 복수의 감마기준전압들을 입력됨에 따라 복수의 감마전압들을 출력한다.

상기 본 발명의 또 다른 목적을 실현하기 위하여 일실시예에 따른 표시장치는 표시패널, 타이밍 제어부, 데이터 구동부, 게이트 구동부 및 감마전압 생성부를 포함한다. 상기 타이밍 제어부는 외부에서 공급되는 제1 영상신호 및 제1 동기신호를 근거로 제2 영상신호, 제2 동기신호 및 제3 동기신호를 출력한다. 상기 데이터 구동부는 상기 제2 영상 신호 및 제2 동기 신호를 근거로 상기 표시패널에 데이터 신호를 출력한다. 상기 게이트 구동부는 상기 제3 동기 신호를 근거로 상기 표시패널에 게이트 신호를 출력한다. 상기 감마전압 생성부는 복수의 감마전압들을 생성하고, 상기 감마전압들을 상기 데이터 구동부에 제공한다. 상기 감마전압 생성부는 저항 스트링과 온도 보상부를 포함한다. 상기 저항 스트링은 복수의 감마기준전압 들을 출력한다. 상기 온도 보상부는 전원전압이 공급되는 전원전압단과 고계조에 대응하는 감마기준전압을 출력하는 저항 스트링에 전기적으로 연결되고, 온도에 따라 가변하는 저항치를 갖는다.

이러한 감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및 표시장치에 의하면, 온도 증가에 따라 화이트 계조측의 감마기준전압은 상대적으로 레벨 다운되고, 블랙 계조측의 감마기준전압을 유지되어 화이트 계조측의 킥백 전압의 편차는 줄어들어 표시 특성의 악화가 방지된다.

이하, 첨부한 도면들을 참조하여, 본 발명을 보다 상세하게 설명하고자 한다.

액정 표시 장치의 화소부는 서로 교차하도록 배치된 복수의 게이트 라인들 및 복수의 데이터 라인들과, 서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 구획되는 영역에 형성된 화소를 포함한다.

도 1은 일반적인 액정 표시 장치의 단위 화소를 설명하는 등가 회로도이다.

도 1을 참조하면, 일반적인 액정 표시 장치의 단위 화소는 박막 트랜지스터(TFT), 액정 캐패시터(Clc) 및 스토리지 캐패시터(Cst)를 포함한다. 상기 박막 트랜지스터(TFT)의 게이트 전극에는 게이트 라인(GL)이 전기적으로 연결되고, 상기 게이트 라인(GL)을 통해 게이트 전압(Vg)이 인가된다.

상기 박막 트랜지스터(TFT)의 드레인 전극에는 데이터 라인(DL)이 전기적으로 연결되고, 상기 데이터 라인(DL)을 통해 데이터 전압(Vs)이 인가된다. 상기 게이트 전압(Vg)이 턴-온 레벨일 경우에는 상기 박막 트랜지스터(TFT)는 턴-온되어 상기 데이터 전압(Vs)이 상기 액정 캐패시터(Clc) 및 스토리지 캐패시터(Cst)에 충전되어 영상 정보가 표시된다.

상기 액정 캐패시터(Clc)의 다른 단자에는 공통 전압(Vcom)이 인가되고, 상기 데이터 전압(Vs)과 상기 공통 전압(Vcom)의 전위차에 해당하는 전계에 의해 상기 액정 캐패시터(Clc)가 충전되어 영상 정보가 표시된다.

이러한 액정 표시 장치에서, 동일한 극성의 전계가 지속적으로 상기 액정 캐패시터에 인가되면, 상기 액정 캐패시터(Clc)에 대응하는 액정층이 열화되므로 프레임 단위로 상기 데이터 전압의 극성을 상기 공통 전압(Vcom)에 대해 반전시켜서 인가한다.

이상적인 경우, 극성이 반전되는 데이터 전압에 의해 상기 액정 캐패시터(Clc)에 충전되는 양극성과 음극성의 전하량이 서로 동일해야 한다. 하지만, 상기 박막 트랜지스터(TFT)의 기생 캐패시턴스(Cgs)에 의해 상기 액정 캐패시터(Clc)에 유지되는 전압이 킥백 전압만큼 다운되므로 상기 양극성과 음극성의 전하량이 상이하다.

도 2는 도 1의 화소에 인가되는 게이트 전압과 액정 캐패시터에 인가되는 전압을 비교하여 나타낸 파형도이다.

도 2에 도시된 2개의 파형은 임의의 한 화소에 인가되는 게이트 전압과 액정 캐패시터(Clc)에 실제로 인가되는 전압의 파형이다. 도 2의 아래 파형에서 점선 표시된 부분은 데이터 라인(DL)에 인가되는 데이터 전압의 파형이고, 실선 표시된 부분이 액정 캐패시터(Clc)에서 나타나는 전압의 파형이다.

도 1 및 도 2를 참조하면, 게이트 전압(Vg)이 턴-온 레벨에서 턴-오프레벨로 다운되면, 상기 액정 캐패시터(Clc)에서 유지되는 전압은 킥백 전압(Vkb)만큼 다운된다.

따라서, 양극성과 음극성의 전하량을 일치시키는 평균 전압과 공통 전압 사이에는 오프셋 전압(Voffset) 만큼의 차이가 발생한다. 상기 오프셋 전압(Voffset)은 보상되어야 한다. 상기한 오프셋 전압(Voffset)을 정확하게 보상하는 것은 불가능하므로 화면의 화소 라인이 깜빡거리는 플리커가 나타난다.

한편, 액정 표시 장치의 잔상은 상기 액정 표시 장치의 장시간 사용에 따라 발생된다. 상기한 잔상의 발생은 액정층내의 이온성 불순물과 상기 액정층에 인가되는 장기적인 DC 전압에 의해 설명된다. 예를들어, DC 전압은 온도에 따라 발생된다.

통상적으로 액정 표시 장치의 구동 조건은 상온, 예를들어, 25℃에서 설정된다. 그러나, 상기 액정 표시 장치가 실제 사용되는 조건은 각종 샤시류나 케이스들이 체결된 상태에서 이용된다. 특히 TV 세트에 채용되는 액정 표시 장치의 경우, 온도가 대략 10℃~15℃ 가량 상승된다.

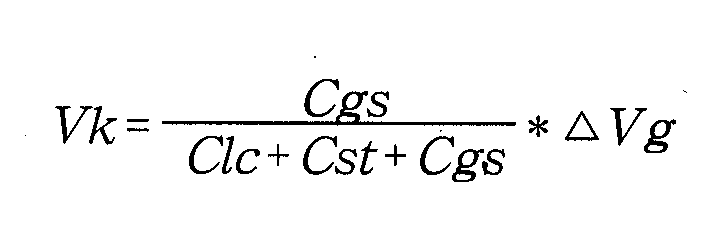

따라서, 최근에는 잔상에 대한 신뢰성 평가도 50℃ 챔버내에서 이루어진다. 온도가 상승되면 액정의 유전율은 변하고, 상기 액정의 유전율 변화에 따라 하기와 같은 수학식 1과 같이 킥백 전압의 변화가 유발된다.

여기서, Vk는 킥백 전압, Clc는 액정 캐패시턴스, Cst는 스토리지 캐패시턴스, Cgs는 게이트-소스간 기생 캐패시턴스, △Vg는 게이트 온 전압(Von)과 게이트 오프 전압(Voff)간의 차전압이다. 또한, 액정 캐패시턴스(Clc)는 에 의해 정의된다. ε은 액정의 유전율, A는 픽셀 전극의 면적, d는 액정층의 셀갭이다.

특히, ε은 하기하는 도 3a 및 도 3b에 나타낸 바와 같이, 20℃에서 50℃ 로 변할 때 30% 이상의 변화를 보인다.

도 3a 및 도 3b는 온도에 따른 액정의 유전률 변화를 설명하는 그래프들이다. 특히, 도 3a는 온도에 따른 액정의 유전율 곡선을 나타내고, 도 3b는 온도에 따른 액정의 유전율 변화율 곡선을 나타낸다. 도 3a 및 도 3b에서 LC1, LC2 및 LC3은 서로 다른 액정을 나타낸다.

도 3a 및 도 3b를 참조하면, 액정의 유전율 변화율은 액정 캐패시턴스(Clc)의 변화율로 반영된다. 통상 Clc ≒ Cst이며, Cgs는 상대적으로 작아 무시된다. 따라서, 액정 캐패시턴스(Clc)는 킥백 전압에 반비례한다.

화이트 패턴을 구현하기 위해 액정층에 풀 전압(full voltage)이 인가되면, 온도 증가에 따라 액정의 유전율은 감소한다. 즉, 도 3a에서, 액정의 온도가 0℃일 때, 액정의 유전율은 대략 8~8.5이나, 액정의 온도가 60℃일 때, 액정의 유전율은 대략 6이다.

한편, 블랙 패턴을 구현하기 위해 액정층에 전압이 거의 인가되지 않는다면, 온도 증가에 따라 액정의 유전율 변화는 거의 없다. 즉, 도 3a에서, 액정의 온도가 0℃일 때, 액정의 유전율은 대략 3.5이나, 액정의 온도가 60℃일 때, 액정의 유전율은 대략 3.7이다.

도 4는 본 발명의 일실시예에 따른 감마기준전압 생성회로를 설명하는 회로도이다.

도 4를 참조하면, 감마기준전압 생성회로(100)는 제1 저항 스트링(110), 제2 저항 스트링(120), 제1 온도 보상부(130) 및 제2 온도 보상부(140)를 포함하고, 복수의 감마기준전압들을 출력한다.

상기 제1 저항 스트링(110)은 상기 제1 온도 보상부(130) 및 제3 전원전압(Vx)이 인가되는 단자간에 전기적으로 연결되어, 상기 제1 온도 보상부(130)를 경유하는 제1 전원전압(AVDD)과 상기 제3 전원전압(Vx)을 저항 분배하여 복수의 제1 극성의 감마기준전압들을 출력한다. 일례로, 상기 제1 저항 스트링(110)은 제1 내지 제8 저항들(R1, R2, R3, R4, R5, R6, R7, R8)을 포함한다. 따라서, 상기 제1 저항 스트링(110)은 제1 극성의 제1 내지 제8 감마기준전압들(VGMA1, VGMA2, VGMA3, VGMA4, VGMA5, VGMA6, VGMA7, VGMA8, VGMA9)을 출력한다.

상기 제2 저항 스트링(120)은 상기 제3 전원전압단(Vx) 및 제2 전원전압(VGS)이 인가되는 제2 온도 보상부(140)간에 전기적으로 연결되어, 제3 전원전압(Vx)과 제2 전원전압(VGS)간을 저항 분배하여 복수의 제2 극성의 감마기준전압들을 출력한다. 일례로, 상기 제2 저항 스트링(120)은 제9 내지 제16 저항들(R10, R11, R12, R13, R14, R15, R16)을 포함한다. 따라서, 상기 제2 저항 스트링(120)은 제2 극성의 제9 내지 제19 감마기준전압들(VGMA10, VGMA11, VGMA12, VGMA13, VGMA14, VGMA15, VGMA16, VGMA17, VGMA18)을 출력한다.

상기 제1 온도 보상부(130)는 제1 전원전압(AVDD)이 인가되는 제1 전원전압단에 전기적으로 연결되고, 온도 증가에 따라 증가하는 저항치를 갖는다. 상기 제1 온도 보상부(130)는 포지티브 써미스터(Rp), 상기 포지티브 써미스터(Rp)에 병렬 연결된 제17 저항(R17)을 포함한다.

상기 제2 온도 보상부(140)는 제2 전원전압(VGS)이 인가되는 제2 전원전압단에 전기적으로 연결되고, 온도 증가에 따라 감소하는 저항치를 갖는다. 상기 제2 온도 보상부(140)는 네거티브 써미스터(Rn), 상기 네거티브 써미스터(Rn)에 병렬 연결된 제18 저항(R18)을 포함한다.

도 4에서, 온도 보상을 위해 써미스터가 사용된다. 특히, PVA 모드의 액정 표시 장치에서, 화이트 계조측의 킥백 전압 변화가 상대적으로 크다. 따라서, 상대적으로 높은 제1 전원전압(AVDD)이 인가되는 단자측과 상대적으로 낮은 제2 전원전압(VGS)이 인가되는 단자측에 포지티브 써미스터(Rp)가 사용된다.

즉, 온도가 상승할수록 화이트 조건에서의 킥백 전압이 커지므로 외부에서 인가하는 화이트 계조에 대응하는 감마기준전압들은 낮아지도록 구현되어야 한다.

상기한 감마기준전압들이 낮아지도록 설계하기 위해, 포지티브 써미스터(Rp)는 상대적으로 높은 제1 전원전압(AVDD)측에, 네거티브 써미스터(Rn)는 상대적으로 낮은 제2 전원전압(VGS)측에 배치한다. 상기 포지티브 써미스터(Rp)는 온도 증가에 따라, 증가하는 저항치를 갖는다. 상기 네거티브 써미스터(Rn)는 온도 증가에 따라, 감소하는 저항치를 갖는다.

그러면, 네거티브 써미스터(Rn)를 제2 전원전압(VGS)측에 배치하는 경우를 일례로 설명한다.

온도가 상승되면, 네거티브 써미스터(Rn)의 저항치는 감소된다. 이에 따라, 제10 내지 제18 감마기준전압들(VGMA10~VGMA18)은 모두 낮아진다. 특히, 화이트 계조측인 제18 감마기준전압(VGMA18)의 감소차가 가장 크고, 제10 감마기준전압(VGMA10)으로 갈수록 감소차가 작아진다.

제3 전원전압(Vx)은 10V이고, 제9 내지 제16 저항(R9 ~R16)이 10Ω이며, 네거티브 써미스터(Rn)는 25℃ 및 50℃일 때, 각각 20Ω 및 10Ω으로 가정한다.

먼저, 25℃에서 50℃로 온도 조건이 변경됨에 따라, 제18 감마기준전압(VGMA18)의 전압 감소차는 하기하는 수학식 2와 같다.

반면, 25℃에서 50℃로 온도 조건이 변경됨에 따라, 제10 감마기준전압(VGMA10)의 전압 감소차는 하기하는 수학식 3과 같다.

상기한 수학식 2 및 3으로부터 온도가 25℃에서 50℃로 변경됨에 따라, 제18 감마기준전압(VGMA18)의 전압 감소차는 제10 감마기준전압(VGMA10)의 전압 감소차보다 9배이다.

한편, 수학식 3으로부터 제10 감마기준전압(VGMA10) 역시 낮아지는 것이 확인된다. 왜냐하면, 블랙 계조의 경우, 도 3a 및 도 3b에서 설명된 바와 같이, 유전율이 오히려 증가하여 킥백 전압이 상온 대비 작아지는 결과에 대해 설정이 옳지 않다.

따라서, 올바른 보정을 하기 위해 블랙 감마측에도 제9 저항(R9)에 병렬로 네거티브 써미스터를 배치하는 것이 바람직하다.

도 4에서는 제1 및 제2 온도 보상부들(130, 140)이 써미스터와 병렬 연결된 저항을 포함하는 것을 설명하였으나, 상기 제1 및 제2 온도 보상부들(130, 140)이 써미스터, 상기 써미스터에 병렬 연결된 저항 및 상기 써미스터와 직렬 연결된 저항을 포함할 수도 있다.

왜냐하면, 써미스터가 단독으로 사용되면, 네거티브 써멀 계수(Negative Thermal Coefficient)의 변화율과 원하는 계수간에 차이가 발생될 수 있다.

따라서, 상기한 네거티브 써멀 계수간의 차이를 줄이기 위한 일례로, 써미스터와 상기 써미스터에 병렬 연결되는 저항을 배치한다(도 4에 도시).

상기한 네거티브 써멀 계수간의 차이를 줄이기 위한 다른 일례로, 써미스터와 상기 써미스터에 병렬 연결되는 저항과, 상기 써미스터 또는 병렬 연결된 저항과 직렬 연결된 저항을 배치한다.

이상에서 설명한 바와 같이, 감마기준전압 생성회로에 구비되어 공통 전압 대비 높은 레벨의 감마기준전압을 출력하는 제1 저항 스트링과 상대적으로 높은 레벨의 전압 입력단간에 온도 증가에 따라 증가하는 저항치를 갖는 써미스터(포지티브 써미스터)를 배치한다.

또한, 상기 감마기준전압 생성회로에 구비되어 공통 전압 대비 낮은 레벨의 감마기준전압들을 출력하는 제2 저항 스트링과 상대적으로 낮은 레벨의 전압 입력 단자간에 온도 증가에 따라 감소하는 저항치를 갖는 써미스터(네거티브 써미스터)를 배치한다.

이에 따라, 온도 증가에 따라 화이트 계조측의 감마기준전압은 상대적으로 레벨 다운되고, 블랙 계조측의 감마기준전압을 유지된다. 따라서, 온도가 증가하더라도 화이트 계조측의 킥백 전압의 편차는 줄어들어 표시 특성의 악화가 방지된다.

도 5는 본 발명의 다른 실시예에 따른 감마기준전압 생성회로를 설명하는 회로도이다.

도 5를 참조하면, 본 발명의 다른 실시예에 따른 감마기준전압 생성회로(200)는 제1 저항 스트링(110), 제2 저항 스트링(120), 제1 메인 온도 보상부(210), 제1 서브 온도 보상부(220), 제2 서브 온도 보상부(230) 및 제2 메인 온도 보상부(240)를 포함한다. 도 4와 비교할 때 동일한 구성 요소에 대해서는 동일한 도면 번호를 부여하고 그 상세한 설명은 생략한다.

상기 제1 메인 온도 보상부(210)는 일단이 제1 전원전압(AVDD)에 전기적으로 연결되고, 타단이 상기 제1 저항 스트링(110)에 전기적으로 연결되며, 온도 증가에 따라 증가하는 저항치를 갖는다. 상기 제1 메인 온도 보상부(210)는 포지티브 써미스터(Rp1), 상기 포지티브 써미스터에 병렬 연결된 저항(R17) 및 상기 저항(R17)에 직렬 연결된 제18 저항(R18)을 포함한다. 상기 제18 저항(R18)의 일단은 상기 제1 전원전압(AVDD)에 전기적으로 연결된다.

상기 제1 서브 온도 보상부(220)는 상기 제1 저항 스트링(110)과 상기 전원전압(AVDD)에 개재되고, 온도 증가에 따라 증가하는 저항치를 갖는다. 상기 제1 서브 온도 보상부(220)는 포지티브 써미스터(Rp2), 상기 포지티브 써미스터(Rp2)에 병렬 연결된 제19 저항(R19) 및 상기 제19 저항(R19)에 직렬 연결된 제20 저항(R20)을 포함한다. 상기 제20 저항(R20)의 일단은 상기 제3 전원전압(Vx)에 전기적으로 연결된다.

상기 제2 서브 온도 보상부(230)는 상기 제2 저항 스트링(120)과 상기 제3 전원전압단(Vx)에 개재되고, 온도 증가에 따라 감소하는 저항치를 갖는다. 상기 제2 서브 온도 보상부(230)는 네거티브 써미스터(Rn1) 및 상기 네거티브 써미스터(Rn1)에 병렬 연결된 제21 저항(R21)을 포함한다. 상기 제21 저항(R21)의 일단은 상기 제3 전원전압(Vx)에 전기적으로 연결된다.

상기 제2 메인 온도 보상부(240)는 일단이 상기 제1 전원전압(AVDD)보다는 낮은 제2 전원전압(VGS)에 전기적으로 연결되고, 타단이 상기 제2 저항 스트링 (120)에 전기적으로 연결되며, 온도 증가에 따라 감소하는 저항치를 갖는다. 상기 제2 메인 온도 보상부(240)는 네거티브 써미스터(Rn2), 상기 네거티브 써미스터(Rn2)에 병렬 연결된 제22 저항(R22) 및 상기 제22 저항(R22)에 직렬 연결된 제23 저항(R23)을 포함한다. 상기 제23 저항(R23)의 일단은 상기 제2 전원전압(VGS)에 전기적으로 연결된다.

도 6은 본 발명의 또 다른 실시예에 따른 감마전압 생성부를 설명하는 블록도이다.

도 6을 참조하면, 본 발명의 또 다른 실시예에 따른 감마전압 생성부(300)는 감마기준전압 생성부(310) 및 감마전압 출력부(320)를 포함한다.

상기 감마기준전압 생성부(310)는 제1 저항 스트링(312), 제2 저항 스트링(314), 제1 메인 온도 보상부(316) 및 제2 메인 온도 보상부(318)를 포함한다.

상기 제1 저항 스트링(312)은 복수의 제1 극성 감마기준전압들(VGMA1~VGMA8)을 상기 감마전압 출력부(320)에 출력한다. 상기 제1 저항 스트링(312)이 직렬 연결된 8개의 저항들로 구성될 때, 상기 제1 극성 감마기준전압들은 제1 내지 제9 감마기준전압들(VGMA1~VGMA9)을 포함한다.

상기 제2 저항 스트링(314)은 복수의 제2 극성 감마기준전압들(VGMA9~VGMA18)을 상기 감마전압 출력부(320)에 출력한다. 상기 제2 저항 스트링(314)이 직렬 연결된 8개의 저항들로 구성될 때, 상기 제2 극성 감마기준전압들은 제10 내지 제18 감마기준전압들(VGMA10~VGMA18)을 포함한다.

상기 제1 메인 온도 보상부(316)는 일단이 제1 전원전압(AVDD)에 전기적으로 연결되고, 타단이 상기 제1 저항 스트링(312)에 전기적으로 연결되며, 온도 증가에 따라 증가하는 저항치를 갖는다.

상기 제2 메인 온도 보상부(318)는 일단이 상기 제1 전원전압(AVDD)보다는 낮은 제2 전원전압(VGS)에 전기적으로 연결되고, 타단이 상기 제2 저항 스트링(314)에 전기적으로 연결되며, 온도 증가에 따라 감소하는 저항치를 갖는다.

상기 제2 저항 스트링(314)과 상기 제1 저항 스트링(312)은 공통 연결되어 제3 전원전압(Vx)을 공급받는다.

동작시, 상기 제1 메인 온도 보상부(316)는 온도가 증가함에 따라, 점차적으로 증가하는 저항치를 이용하여 점차적으로 레벨 다운된 제1 전원전압(AVDD)을 상기 제1 저항 스트링(312)에 제공한다. 이에 따라, 상기 제1 저항 스트링(312)은 온도 증가에 따라 레벨 다운된 제1 전원전압(AVDD)과 상기 제3 전원전압(Vx)을 전압 분배하여 제1 내지 제9 감마기준전압들(VGMA1~VGMA9)을 상기 감마전압 출력부(320)에 출력한다.

또한, 상기 제2 메인 온도 보상부(318)는 온도가 증가함에 따라, 점차적으로 감소하는 저항치를 이용하여 점차적으로 상기 제2 전원전압(VGS)에 근접하는 전원전압을 상기 제2 저항 스트링(314)에 제공한다. 이에 따라, 상기 제2 저항 스트링(314)은 상기 제3 전원전압(Vx)과 온도 증가에 따라 감소되는 제2 전원전압(VGS)을 전압 분배하여 제10 내지 제18 감마기준전압들(VGMA10~VGMA18)을 상기 감마전압출력부(320)에 출력한다.

상기 감마전압 출력부(320)는 상기 감마기준전압 생성부(310)에서 제공되는 제1 내지 제18 감마기준전압들(VGMA1~VGMA18)을 고려하여 복수의 감마전압들(V0, V1, V2, ..., V62, V63)을 출력한다.

예를들어, 상기 감마전압 출력부(320)는 제3 내지 제10 저항 스트링들을 포함한다. 제3 저항 스트링의 일단에는 제1 감마기준전압(VGMA1)이 인가되고, 타단에는 제2 감마기준전압(VGMA2)이 인가된다. 따라서, 상기 제3 저항 스트링은 상기 제1 및 제2 감마기준전압들(VGMA1, VGMA2)을 이용하는 전압분배 방식을 통해 제1 내지 제8 감마전압들(V0~V7)을 출력한다.

또한, 제4 저항 스트링의 일단에는 제2 감마기준전압(VGMA2)이 인가되고, 타단에는 제3 감마기준전압(VGMA3)이 인가된다. 따라서, 상기 제4 저항 스트링은 상기 제2 및 제3 감마기준전압들(VGMA2,VGMA3)을 이용하는 전압분배 방식을 통해 제9 내지 제16 감마전압들(V8~V15)을 출력한다.

이러한 방식으로, 제10 저항 스트링의 일단에는 제18 감마기준전압(VGMA18)이 인가되고, 타단에는 제2 전원전압(VGS)이 인가된다. 따라서, 상기 제10 저항 스트링은 상기 제19 감마기준전압(VGMA18) 및 제2 전원전압(VGS)을 이용하여 전압분배 방식을 통해 제56 내지 제64 감마전압들(V54~V63)을 출력한다.

도 7은 본 발명의 또 다른 실시예에 따른 액정 표시 장치를 설명하기 위한 블록도이다.

도 7을 참조하면, 본 발명의 또 다른 실시예에 따른 액정 표시 장치(400)는 타이밍 제어부(410), 감마전압 생성부(420), 데이터 구동부(430), 게이트 구동부(440) 및 액정 표시 패널(450)을 포함한다.

상기 타이밍 제어부(410)는 그래픽 콘트롤러와 같은 외부의 호스트 시스템으로부터 제1 데이터 신호(DATA1)와 동기신호(SYNC)를 제공받는다. 상기 타이밍 제어부(410)는 제2 데이터 신호(DATA2) 및 제1 제어 신호(TS1)를 상기 데이터 구동부(430)에 출력하고, 제2 제어 신호(TS2)를 상기 게이트 구동부(440)에 출력한다.

상기 감마전압 생성부(420)는 복수의 감마전압을 생성하고, 생성된 감마전압을 상기 데이터 구동부(430)에 제공한다. 도 8에서는 64개의 감마전압들(V0, V1, ..., V62, V63)을 출력한다.

상기 데이터 구동부(430)는 상기 제2 데이터 신호(DATA2), 상기 제1 제어 신호(TS1) 및 상기 감마전압들(V0, V1, ..., V62, V63)을 근거로 복수의 데이터 전압들을 상기 액정 표시 패널(450)에 공급한다.

일례로 상기 데이터 구동부(430)는 인쇄회로기판(PCB)과, 상기 인쇄회로기판(PCB)에 전기적으로 연결된 연성인쇄회로기판(FPCB)과, 상기 연성인쇄회로기판(FPCB)에 탑재된 하나 또는 복수의 데이터 구동칩들을 포함한다. 다른 일례로, 상기 데이터 구동부(430)는 상기 액정 표시 패널(450)의 주변 영역에 집적될 수도 있다.

상기 게이트 구동부(440)는 복수의 게이트 전압들을 상기 액정 표시 패널(450)에 순차적으로 공급한다. 상기 게이트 구동부(440)는 일례로, 인쇄회로기판(PCB)과, 상기 인쇄회로기판(PCB)에 전기적으로 연결된 연성인쇄회로기판(FPCB)과, 상기 연성인쇄회로기판(FPCB)에 탑재된 하나 또는 복수의 게이트 구동칩들을 포함한다.

다른 예로, 상기 게이트 구동부(440)는 연성인쇄회로기판(FPCB)과, 상기 연성인쇄회로기판(FPCB)에 탑재된 하나 또는 복수의 게이트 구동칩들을 포함한다. 또 다른 예로, 상기 게이트 구동부(440)는 상기 액정 표시 패널(450)의 주변 영역에 집적될 수도 있다.

상기 액정 표시 패널(450)은 복수의 게이트 라인들과, 복수의 데이터 라인들과, 서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 둘러싸인 영역에 형성된 스위칭 소자(TFT)와, 상기 스위칭 소자(TFT)에 전기적으로 연결된 액정 캐패시터(Clc)와, 상기 스위칭 소자(TFT)에 전기적으로 연결된 스토리지 캐패시터(Cst)를 포함한다.

동작시, 상기 게이트 라인(GL)은 상기 게이트 전압을 상기 스위칭 소자(TFT)에 전달한다. 상기 데이터 라인(DL)은 상기 데이터 전압을 상기 스위칭 소자(TFT)에 전달한다. 상기 액정 캐패시터(Clc)는 상기 게이트 전압을 근거로 턴-온 또는 턴-오프되어, 상기 데이터 전압을 충전한다. 상기 스토리지 캐패시터(Cst)는 턴-온된 스위칭 소자(TFT)를 경유하여 제공되는 데이터 전압을 저장하고, 상기 스위칭 소자(TFT)의 턴-오프 구간 동안 충전된 데이터 전압을 상기 액정 캐패시터(Clc)에 제공한다.

도 8은 도 7에 도시된 액정 표시 장치의 동작을 설명하기 위한 블록도이다.

도 7 및 도 8을 참조하면, 상기 타이밍 제어부(410)에 구비되는 그래픽 램(412)은 6비츠의 R 영상 데이터와, 6비츠의 G 영상 데이터와, 6 비츠의 B 영상 데이터를 상기 데이터 구동부(430)에 제공한다.

상기 감마전압 생성부(420)는 64개의 감마전압들(V0, V1, ..., V62, V63)을 상기 데이터 구동부(430)에 제공한다.

상기 데이터 구동부(430)는 RGB 각각의 영상 데이터를 RGB 각각의 영상 신호로 변환하기 위해 복수의 64-계조 제어부들과 복수의 소스 드라이버들을 포함하고, 상기 64개의 감마전압(V0, V1, ..., V62, V63)들을 근거로 상기 RGB 영상 데이터를 RGB 영상 신호로 변환하여 액정 표시 패널(450)에 구비되는 RGB 각각의 화소에 제공한다.

도 8에 도시한 바와 같이, 감마전압들의 수가 64개이고, R 영상 데이터가 6비츠이고, G 영상 데이터가 6 비츠이며, B 영상 데이터가 6 비츠이므로 액정 표시 패널(450)을 통해서는 총 262,144(64×64×64)의 컬러를 표시할 수 있다.

이상에서는 감마 기준을 저항 분배방식을 통해 형성할 때 사용할 수 있는 방식이다. 디지털 감마 IC를 사용하더라도 동일하게 적용될 수 있다. 다만, 상기 디지털 감마 IC를 사용할 경우, 온도 범위에 따라 감마 테이블을 달리 사용하여 온도에 따라 보상하는 방식을 사용한다.

도 9는 본 발명의 또 다른 실시예에 따른 액정 표시 장치를 설명하기 위한 블록도이다. 도 10은 도 9에 도시된 감마기준전압 저장부를 설명하는 블록도이다.

도 9 및 도 10을 참조하면, 본 발명의 또 다른 실시예에 따른 액정 표시 장치는 온도 센서(510), 타이밍 제어부(410), 감마기준전압 저장부(520), 감마전압 생성부(530), 데이터 구동부(430), 게이트 구동부(440) 및 액정 표시 패널(450)을 포함한다. 도 7과 비교할 때 동일한 구성 요소에 대해서는 동일한 도면 번호를 부 여하고 그 상세한 설명은 생략한다.

상기 온도 센서(510)는 액정 표시 장치의 온도를 감지하고, 감지된 온도 데이터를 상기 타이밍 제어부(410)에 제공한다.

상기 감마기준전압 저장부(520)는 온도 구간별로 감마기준전압들이 저장된 룩업 테이블들(522, 524, 526,..., 52n)을 포함한다. 예를들어, 상기 룩업 테이블들은 21℃ 내지 30℃의 온도 구간에 대응하여 룩업 테이블, 31℃ 내지 40℃의 온도 구간에 대응하는 룩업 테이블, 41℃ 내지 50℃의 온도 구간에 대응하는 룩업 테이블을 포함한다. 상기 각각의 룩업 테이블들에는 온도 증가에 따라 가변되는 저항치를 이용하여 설정된 감마기준전압들이 저장된다.

상기 감마전압 생성부(530)는 상기 타이밍 제어부(410)에서 온도 데이터(TD)가 제공됨에 따라, 해당 온도 구간에 대응하는 감마기준전압들이 저장된 룩업 테이블을 상기 감마 전압 저장부(520)에서 추출한다. 상기 감마전압 생성부(530)는 상기 감마기준전압 저장부(520)에서 제공되는 해당 온도 구간에 대응하는 제1 내지 제18 감마기준전압들(VGMA1~VGMA18)을 고려하여 복수의 감마전압들(V0, V1, V2, ..., V62, V63)을 출력한다.

예를들어, 상기 감마전압 생성부(530)는 제1 내지 제8 저항 스트링들을 포함한다. 제1 저항 스트링의 일단에는 제1 감마기준전압(VGMA1)이 인가되고, 타단에는 제2 감마기준전압(VGMA2)이 인가된다. 따라서, 상기 제1 저항 스트링은 상기 제1 및 제2 감마기준전압들(VGMA1, VGMA2)을 이용하는 전압분배 방식을 통해 제1 내지 제8 감마전압들(V0~V7)을 출력한다.

또한, 제2 저항 스트링의 일단에는 제2 감마기준전압(VGMA2)이 인가되고, 타단에는 제3 감마기준전압(VGMA3)이 인가된다. 따라서, 상기 제2 저항 스트링은 상기 제2 및 제3 감마기준전압들(VGMA2,VGMA3)을 이용하는 전압분배 방식을 통해 제9 내지 제16 감마전압들(V8~V15)을 출력한다.

이상에서 설명한 바와 같이, 본 발명에 따르면 상대적으로 높은 레벨의 전압 입력단과 공통 전압 대비 높은 레벨의 감마기준전압들을 출력하는 제1 저항 스트링간에 온도 증가에 따라 증가하는 저항치를 갖는 온도 보상부를 배치한다.

또한, 공통 전압 대비 낮은 레벨의 감마기준전압들을 출력하는 제2 저항 스트링과 상대적으로 낮은 레벨의 전압 입력 단자간에 온도 증가에 따라 감소하는 저항치를 갖는 온도 보상부를 배치한다.

이에 따라, 온도 증가에 따라 화이트 계조측의 감마기준전압은 상대적으로 레벨 다운되고, 블랙 계조측의 감마기준전압을 유지된다. 따라서, 온도가 증가하더라도 화이트 계조측의 킥백 전압의 편차는 줄어들어 표시 특성의 악화가 방지된다.

이상에서는 실시예들을 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

Claims (23)

- 복수의 제1 극성 감마기준전압들을 출력하는 제1 저항 스트링;복수의 제2 극성 감마기준전압들을 출력하는 제2 저항 스트링;일단이 제1 전원전압에 전기적으로 연결되고, 타단이 상기 제1 저항 스트링에 전기적으로 연결되며, 온도 증가에 따라 증가하는 저항치를 갖는 제1 메인 온도 보상부; 및일단이 상기 제1 전원전압보다는 낮은 제2 전원전압에 전기적으로 연결되고, 타단이 상기 제2 저항 스트링에 전기적으로 연결되며, 온도 증가에 따라 감소하는 저항치를 갖는 제2 메인 온도 보상부를 포함하고,상기 제1 메인 온도 보상부는,포지티브 써미스터;상기 포지티브 써미스터에 병렬 연결된 제1 저항; 및상기 제1 저항에 직렬 연결된 제2 저항을 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 복수의 제1 극성 감마기준전압들을 출력하는 제1 저항 스트링;복수의 제2 극성 감마기준전압들을 출력하는 제2 저항 스트링;일단이 제1 전원전압에 전기적으로 연결되고, 타단이 상기 제1 저항 스트링에 전기적으로 연결되며, 온도 증가에 따라 증가하는 저항치를 갖는 제1 메인 온도 보상부; 및일단이 상기 제1 전원전압보다는 낮은 제2 전원전압에 전기적으로 연결되고, 타단이 상기 제2 저항 스트링에 전기적으로 연결되며, 온도 증가에 따라 감소하는 저항치를 갖는 제2 메인 온도 보상부를 포함하고,상기 제2 메인 온도 보상부는,네거티브 써미스터;상기 네거티브 써미스터에 병렬 연결된 제3 저항; 및상기 제3 저항에 직렬 연결된 제4 저항을 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 복수의 제1 극성 감마기준전압들을 출력하는 제1 저항 스트링;복수의 제2 극성 감마기준전압들을 출력하는 제2 저항 스트링;일단이 제1 전원전압에 전기적으로 연결되고, 타단이 상기 제1 저항 스트링에 전기적으로 연결되며, 온도 증가에 따라 증가하는 저항치를 갖는 제1 메인 온도 보상부; 및일단이 상기 제1 전원전압보다는 낮은 제2 전원전압에 전기적으로 연결되고, 타단이 상기 제2 저항 스트링에 전기적으로 연결되며, 온도 증가에 따라 감소하는 저항치를 갖는 제2 메인 온도 보상부를 포함하고,상기 제1 저항 스트링과 제2 저항 스트링의 공통단에 제3 전원전압을 공급하는 제3 전원전압단을 더 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 제8항에 있어서, 상기 제1 저항 스트링과 상기 제3 전원전압단에 개재되고, 온도 증가에 따라 증가하는 저항치를 갖는 제1 서브 온도 보상부를 더 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 제9항에 있어서, 상기 제1 서브 온도 보상부는,포지티브 써미스터를 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 제9항에 있어서, 상기 제1 서브 온도 보상부는,포지티브 써미스터; 및상기 포지티브 써미스터에 병렬 연결된 제5 저항을 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 제11항에 있어서, 상기 제1 서브 온도 보상부는,상기 제5 저항에 직렬 연결된 제6 저항을 더 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 제8항에 있어서, 상기 제2 저항 스트링과 상기 제3 전원전압단에 개재되고, 온도 증가에 따라 감소하는 저항치를 갖는 제2 서브 온도 보상부를 더 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 제13항에 있어서, 상기 제2 서브 온도 보상부는,네거티브 써미스터를 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 제14항에 있어서, 상기 제2 서브 온도 보상부는,네거티브 써미스터와, 상기 네거티브 써미스터에 병렬 연결된 제7 저항을 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 제15항에 있어서, 상기 제2 서브 온도 보상부는,상기 제7 저항에 직렬 연결된 제8 저항을 더 포함하는 것을 특징으로 하는 감마기준전압 생성회로.

- 복수의 감마기준전압들을 출력하는 저항 스트링과, 전원전압이 공급되는 전원전압단과 고계조에 대응하는 감마기준전압을 출력하는 저항 스트링에 전기적으로 연결되고, 온도에 따라 가변하는 저항치를 갖는 메인 온도 보상부를 포함하는 감마기준전압 생성회로;상기 감마기준전압 생성회로에서 복수의 감마기준전압들을 입력됨에 따라 복수의 감마전압들을 출력하는 감마전압 출력부; 및저계조에 대응하는 감마기준전압을 출력하는 저항 스트링과 전원전압단에 전기적으로 연결되고, 온도에 따라 가변하는 저항치를 갖는 서브 온도 보상부를 포함하는 것을 특징으로 하는 감마전압 생성장치.

- 제17항에 있어서, 상기 메인 온도 보상부는,써미스터를 포함하는 것을 특징으로 하는 감마전압 생성장치.

- 삭제

- 복수의 감마기준전압들을 출력하는 저항 스트링과, 전원전압이 공급되는 전원전압단과 고계조에 대응하는 감마기준전압을 출력하는 저항 스트링에 전기적으로 연결되고, 온도에 따라 가변하는 저항치를 갖는 메인 온도 보상부를 포함하는 감마기준전압 생성회로; 및상기 감마기준전압 생성회로에서 복수의 감마기준전압들을 입력됨에 따라 복수의 감마전압들을 출력하는 감마전압 출력부를 포함하고,상기 저항 스트링은,제1 전원전압이 공급되는 제1 전원전압단에 일단이 전기적으로 연결되고, 복수의 제1 극성 감마기준전압들을 출력하는 제1 저항부; 및제2 전원전압이 공급되는 제2 전원전압단에 일단이 전기적으로 연결되고, 복수의 제2 극성 감마기준전압들을 출력하는 제2 저항부를 포함하는 것을 특징으로 하는 감마전압 생성장치.

- 제20항에 있어서, 상기 제1 저항부와 제2 저항부의 공통단에 제3 전원전압을 공급하는 제3 전원전압단을 더 포함하는 것을 특징으로 하는 감마전압 생성장치.

- 표시패널;외부에서 공급되는 제1 영상신호 및 제1 동기신호를 근거로 제2 영상신호, 제2 동기신호 및 제3 동기신호를 출력하는 타이밍 제어부;상기 제2 영상 신호 및 제2 동기 신호를 근거로 상기 표시패널에 데이터 신호를 출력하는 데이터 구동부;상기 제3 동기 신호를 근거로 상기 표시패널에 게이트 신호를 출력하는 게이트 구동부; 및복수의 감마전압들을 생성하고, 상기 감마전압들을 상기 데이터 구동부에 제공하는 감마전압 생성부를 포함하고,상기 감마전압 생성부는,복수의 감마기준전압들을 출력하는 저항 스트링과, 전원전압이 공급되는 전원전압단과 고계조에 대응하는 감마기준전압을 출력하는 저항 스트링에 전기적으로 연결되고, 온도에 따라 가변하는 저항치를 갖는 온도 보상부와, 저계조에 대응하는 감마기준전압을 출력하는 저항 스트링과 전원전압단에 전기적으로 연결되고, 온도에 따라 가변하는 저항치를 갖는 서브 온도 보상부를 포함하는 것을 특징으로 하는 표시장치.

- 표시패널;외부에서 공급되는 제1 영상신호 및 제1 동기신호를 근거로 제2 영상신호, 제2 동기신호 및 제3 동기신호를 출력하는 타이밍 제어부;상기 제2 영상 신호 및 제2 동기 신호를 근거로 상기 표시패널에 데이터 신호를 출력하는 데이터 구동부;상기 제3 동기 신호를 근거로 상기 표시패널에 게이트 신호를 출력하는 게이트 구동부; 및복수의 감마전압들을 생성하고, 상기 감마전압들을 상기 데이터 구동부에 제공하는 감마전압 생성부를 포함하고,상기 감마전압 생성부는,복수의 감마기준전압들을 출력하는 저항 스트링과, 전원전압이 공급되는 전원전압단과 고계조에 대응하는 감마기준전압을 출력하는 저항 스트링에 전기적으로 연결되고, 온도에 따라 가변하는 저항치를 갖는 온도 보상부를 포함하고,상기 저항 스트링은,제1 전원전압이 공급되는 제1 전원전압단에 일단이 전기적으로 연결되고, 복수의 제1 극성 감마기준전압들을 출력하는 제1 저항부; 및제2 전원전압이 공급되는 제2 전원전압단에 일단이 전기적으로 연결되고, 복수의 제2 극성 감마기준전압들을 출력하는 제2 저항부를 포함하는 것을 특징으로 하는 표시장치.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060013928A KR101226435B1 (ko) | 2006-02-14 | 2006-02-14 | 감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및표시장치 |

| US11/706,045 US8068086B2 (en) | 2006-02-14 | 2007-02-12 | Gamma-reference-voltage generating circuit and apparatus for generating gamma-voltages and display device having the circuit |

| CN2007100053742A CN101022005B (zh) | 2006-02-14 | 2007-02-14 | 生成伽马电压的伽马参考电压生成电路和装置及显示设备 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060013928A KR101226435B1 (ko) | 2006-02-14 | 2006-02-14 | 감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및표시장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20070081806A KR20070081806A (ko) | 2007-08-20 |

| KR101226435B1 true KR101226435B1 (ko) | 2013-01-25 |

Family

ID=38367842

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020060013928A KR101226435B1 (ko) | 2006-02-14 | 2006-02-14 | 감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및표시장치 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8068086B2 (ko) |

| KR (1) | KR101226435B1 (ko) |

| CN (1) | CN101022005B (ko) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20140116716A (ko) * | 2013-03-25 | 2014-10-06 | 엘지디스플레이 주식회사 | 청색광 보상 회로를 포함하는 액정표시장치 |

| KR20160094542A (ko) * | 2015-01-30 | 2016-08-10 | 엘지디스플레이 주식회사 | 계조 전압 생성 장치와 이를 포함하는 디스플레이용 데이터 구동 장치 및 디스플레이 장치 |

| US11847972B2 (en) | 2022-04-15 | 2023-12-19 | Samsung Display Co., Ltd. | Electronic device |

Families Citing this family (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20070103412A1 (en) * | 2005-11-09 | 2007-05-10 | Pao-Yun Tang | Liquid crystal display having a voltage divider with a thermistor |

| US7973748B2 (en) * | 2007-10-03 | 2011-07-05 | Himax Technologies Limited | Datadriver and method for conducting driving current for an OLED display |

| KR101457694B1 (ko) * | 2008-05-09 | 2014-11-04 | 엘지디스플레이 주식회사 | 액정표시장치와 그 구동방법 |

| US20100321361A1 (en) | 2009-06-19 | 2010-12-23 | Himax Technologies Limited | Source driver |

| KR20110007529A (ko) * | 2009-07-16 | 2011-01-24 | 삼성전자주식회사 | 소스 드라이버 및 이를 구비하는 디스플레이 장치 |

| TW201108190A (en) * | 2009-08-24 | 2011-03-01 | Novatek Microelectronics Corp | Device for driving a LCD panel and related display device |

| KR101163219B1 (ko) | 2010-07-08 | 2012-07-11 | 에스케이하이닉스 주식회사 | 기준전압 레벨 설정 방법을 사용하는 집적회로 |

| KR101324552B1 (ko) * | 2010-10-26 | 2013-11-01 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 구동방법 |

| KR20120109890A (ko) * | 2011-03-28 | 2012-10-09 | 삼성디스플레이 주식회사 | 액정 표시 장치의 구동 장치 및 방법 |

| KR101941984B1 (ko) * | 2011-09-27 | 2019-04-12 | 삼성디스플레이 주식회사 | 액정표시장치 |

| TWI450262B (zh) * | 2011-12-28 | 2014-08-21 | Chunghwa Picture Tubes Ltd | 顯示面板的閘極驅動電路 |

| CN105427827B (zh) * | 2012-05-31 | 2017-11-14 | 京东方科技集团股份有限公司 | 伽马参考电压的设定方法、装置、驱动电路及显示装置 |

| JP2015031906A (ja) * | 2013-08-06 | 2015-02-16 | シナプティクス・ディスプレイ・デバイス株式会社 | 表示駆動装置及び表示装置 |

| CN103745695B (zh) * | 2013-12-02 | 2016-03-30 | 深圳市华星光电技术有限公司 | Gamma电压驱动电路、源极驱动模块以及液晶面板 |

| CN103794187B (zh) | 2014-01-27 | 2016-06-01 | 北京京东方光电科技有限公司 | 伽马参考电压产生装置及显示器 |

| KR102185786B1 (ko) * | 2014-02-27 | 2020-12-03 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 및 액정 표시 장치의 구동 방법 |

| CN104978936A (zh) * | 2014-04-03 | 2015-10-14 | 奇景光电股份有限公司 | 显示装置的伽玛参考电压与伽玛电压产生电路 |

| KR102214032B1 (ko) * | 2014-07-02 | 2021-02-10 | 삼성디스플레이 주식회사 | 표시장치 |

| KR20160012309A (ko) * | 2014-07-23 | 2016-02-03 | 삼성디스플레이 주식회사 | 표시 장치 및 그것의 구동 방법 |

| KR20160050166A (ko) | 2014-10-28 | 2016-05-11 | 삼성디스플레이 주식회사 | 감마 전압 발생기 및 이를 포함하는 디스플레이 장치 |

| KR102331176B1 (ko) * | 2015-06-11 | 2021-11-26 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102416343B1 (ko) * | 2015-09-24 | 2022-07-05 | 삼성디스플레이 주식회사 | 표시 장치 및 이의 구동 방법 |

| CN105632437A (zh) | 2016-01-08 | 2016-06-01 | 京东方科技集团股份有限公司 | 一种显示驱动方法、显示面板及显示装置 |

| CN106601202B (zh) * | 2016-12-14 | 2019-04-09 | 昆山龙腾光电有限公司 | 液晶显示装置、伽马电压调节装置及其调节方法 |

| CN107274850B (zh) | 2017-08-11 | 2019-06-07 | 京东方科技集团股份有限公司 | 一种显示驱动电路及其驱动方法、显示装置 |

| US10872550B2 (en) * | 2019-03-27 | 2020-12-22 | Novatek Microelectronics Corp. | Display driver and displaying method for cascade application |

| CN112669786A (zh) * | 2021-01-11 | 2021-04-16 | 北京京东方技术开发有限公司 | 伽马电路及其驱动方法、显示面板 |

| CN113672023A (zh) * | 2021-08-17 | 2021-11-19 | 晟合微电子(肇庆)有限公司 | 伽马电压生成电路及显示设备 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5250937A (en) * | 1990-03-08 | 1993-10-05 | Hitachi, Ltd. | Half tone liquid crystal display circuit with an A.C. voltage divider for drivers |

| KR19980025704A (ko) * | 1996-10-04 | 1998-07-15 | 김광호 | 온도 보상 계조 전압 발생 회로 |

| KR20040100559A (ko) * | 2003-05-23 | 2004-12-02 | 엘지.필립스 엘시디 주식회사 | 액정표시장치의 감마 기준전압회로 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4045791A (en) * | 1972-04-06 | 1977-08-30 | Matsushita Electric Industrial Co., Ltd. | Apparatus for driving liquid crystal display device wherein the signal applied thereto is varied in accordance with the temperature of the device |

| KR100634827B1 (ko) | 1999-09-07 | 2006-10-17 | 엘지.필립스 엘시디 주식회사 | 액정표시장치의 감마전압 보상 장치 및 방법 |

| CN1243337C (zh) * | 2002-01-17 | 2006-02-22 | 奇景光电股份有限公司 | 用于液晶显示器的伽马校正装置及方法 |

| US20070103412A1 (en) * | 2005-11-09 | 2007-05-10 | Pao-Yun Tang | Liquid crystal display having a voltage divider with a thermistor |

-

2006

- 2006-02-14 KR KR1020060013928A patent/KR101226435B1/ko active IP Right Grant

-

2007

- 2007-02-12 US US11/706,045 patent/US8068086B2/en active Active

- 2007-02-14 CN CN2007100053742A patent/CN101022005B/zh active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5250937A (en) * | 1990-03-08 | 1993-10-05 | Hitachi, Ltd. | Half tone liquid crystal display circuit with an A.C. voltage divider for drivers |

| KR19980025704A (ko) * | 1996-10-04 | 1998-07-15 | 김광호 | 온도 보상 계조 전압 발생 회로 |

| KR20040100559A (ko) * | 2003-05-23 | 2004-12-02 | 엘지.필립스 엘시디 주식회사 | 액정표시장치의 감마 기준전압회로 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20140116716A (ko) * | 2013-03-25 | 2014-10-06 | 엘지디스플레이 주식회사 | 청색광 보상 회로를 포함하는 액정표시장치 |

| KR102059784B1 (ko) * | 2013-03-25 | 2019-12-27 | 엘지디스플레이 주식회사 | 청색광 보상 회로를 포함하는 액정표시장치 |

| KR20160094542A (ko) * | 2015-01-30 | 2016-08-10 | 엘지디스플레이 주식회사 | 계조 전압 생성 장치와 이를 포함하는 디스플레이용 데이터 구동 장치 및 디스플레이 장치 |

| KR102307725B1 (ko) * | 2015-01-30 | 2021-10-01 | 엘지디스플레이 주식회사 | 계조 전압 생성 장치와 이를 포함하는 디스플레이용 데이터 구동 장치 및 디스플레이 장치 |

| US11847972B2 (en) | 2022-04-15 | 2023-12-19 | Samsung Display Co., Ltd. | Electronic device |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101022005A (zh) | 2007-08-22 |

| CN101022005B (zh) | 2013-04-17 |

| US20070188430A1 (en) | 2007-08-16 |

| US8068086B2 (en) | 2011-11-29 |

| KR20070081806A (ko) | 2007-08-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101226435B1 (ko) | 감마기준전압 생성회로, 이를 갖는 감마전압 생성장치 및표시장치 | |

| US9218791B2 (en) | Liquid crystal display device and method for driving a liquid crystal display device | |

| KR20080076387A (ko) | 표시장치 및 이의 구동방법 | |

| JP2004530171A (ja) | 液晶表示装置 | |

| KR20160055368A (ko) | 표시 장치 및 이의 구동 방법 | |

| KR20080107855A (ko) | 표시 장치 및 이의 구동 방법 | |

| KR20080010796A (ko) | 유기 발광 표시 장치 및 그의 구동 방법 | |

| KR20150079259A (ko) | 표시 장치 및 그 구동 방법 | |

| KR20160066577A (ko) | 전압 공급부와 이를 포함한 표시장치 | |

| KR101991384B1 (ko) | 액정표시장치 | |

| KR101310738B1 (ko) | 액정 표시 장치 및 이의 구동 방법 | |

| KR101556778B1 (ko) | 액정 표시 장치 및 그것의 구동 방법 | |

| KR100840331B1 (ko) | 공통 전압 발생 장치 및 이를 이용한 액정 표시 장치 | |

| KR20090072779A (ko) | 포토센서와 그 구동방법 | |

| KR101507152B1 (ko) | 액정 표시 장치 및 이의 구동 방법 | |

| KR101356164B1 (ko) | 오버드라이빙 회로를 포함하는 액정표시장치 | |

| KR20080070221A (ko) | 액정 표시 장치 및 그 구동 방법 | |

| KR20150071360A (ko) | 액정표시장치 | |

| KR100964566B1 (ko) | 액정 표시 장치와 이의 구동 장치 및 방법 | |

| KR20070082232A (ko) | 액정 표시 장치 | |

| KR101123075B1 (ko) | 킥백전압 보상방법과 이를 이용한 액정표시장치 | |

| KR20170072423A (ko) | 표시 장치 및 이의 구동 방법 | |

| KR20090129558A (ko) | 액정표시패널 | |

| TWI436341B (zh) | 電壓補償電路、顯示模組、顯示裝置及其控制方法 | |

| KR20080048199A (ko) | 표시 장치 및 그 구동 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| N231 | Notification of change of applicant | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20151230 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20170102 Year of fee payment: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20180102 Year of fee payment: 6 |

|

| FPAY | Annual fee payment |

Payment date: 20190102 Year of fee payment: 7 |

|

| FPAY | Annual fee payment |

Payment date: 20191223 Year of fee payment: 8 |