JP7562529B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP7562529B2 JP7562529B2 JP2021529962A JP2021529962A JP7562529B2 JP 7562529 B2 JP7562529 B2 JP 7562529B2 JP 2021529962 A JP2021529962 A JP 2021529962A JP 2021529962 A JP2021529962 A JP 2021529962A JP 7562529 B2 JP7562529 B2 JP 7562529B2

- Authority

- JP

- Japan

- Prior art keywords

- lead

- semiconductor device

- resin

- back surface

- main surface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/482—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes for individual devices provided for in groups H10D8/00 - H10D48/00, e.g. for power transistors

- H10W20/484—Interconnections having extended contours, e.g. pads having mesh shape or interconnections comprising connected parallel stripes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/40—Leadframes

- H10W70/481—Leadframes for devices being provided for in groups H10D8/00 - H10D48/00

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/111—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/40—Encapsulations, e.g. protective coatings characterised by their materials

- H10W74/47—Encapsulations, e.g. protective coatings characterised by their materials comprising organic materials, e.g. plastics or resins

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/40—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels

- H10D30/47—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels having two-dimensional [2D] charge carrier gas channels, e.g. nanoribbon FETs or high electron mobility transistors [HEMT]

- H10D30/471—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT]

- H10D30/475—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT] having wider bandgap layer formed on top of lower bandgap active layer, e.g. undoped barrier HEMTs such as i-AlGaN/GaN HEMTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/343—Gate regions of field-effect devices having PN junction gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/85—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group III-V materials, e.g. GaAs

- H10D62/8503—Nitride Group III-V materials, e.g. AlN or GaN

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/111—Field plates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/254—Source or drain electrodes for field-effect devices for lateral devices wherein the source or drain electrodes extend entirely through the semiconductor bodies, e.g. via-holes for back side contacts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/257—Source or drain electrodes for field-effect devices for lateral devices wherein the source or drain electrodes are characterised by top-view geometrical layouts, e.g. interdigitated, semi-circular, annular or L-shaped electrodes

Landscapes

- Electrodes Of Semiconductors (AREA)

- Junction Field-Effect Transistors (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Lead Frames For Integrated Circuits (AREA)

Description

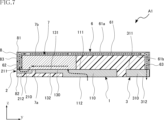

窒化物半導体からなる電子走行層と、厚さ方向において互いに反対側を向く素子主面および素子裏面と、前記素子主面に配置されたゲート電極、ソース電極、およびドレイン電極と、を有する半導体素子と、

前記ドレイン電極が接合されている第1リードと、

前記ソース電極が接合されている第2リードと、

前記第2リードに接続し、かつ、前記素子裏面側に、前記厚さ方向視において前記半導体素子に重なるように配置されている接続リードと、

を備え、

前記接続リードにはスイッチングの対象である主電流が流れる、

半導体装置。

〔付記2〕

前記接続リードは、前記素子裏面に接触している、付記1に記載の半導体装置。

〔付記3〕

前記半導体素子は、前記素子裏面に配置され、かつ、前記ソース電極と電気的に接続された裏面電極をさらに備え、

前記接続リードには、前記裏面電極が接合されている、付記2に記載の半導体装置。

〔付記4〕

前記半導体素子を覆う封止樹脂をさらに備え、

前記接続リードの一部は、前記封止樹脂から露出している、付記1ないし3のいずれかに記載の半導体装置。

〔付記5〕

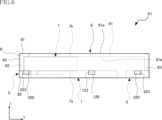

前記封止樹脂は、前記厚さ方向において互いに反対側を向く樹脂主面および樹脂裏面と、前記樹脂主面および前記樹脂裏面に繋がる樹脂側面とを有する、付記4に記載の半導体装置。

〔付記6〕

前記第2リードは、前記樹脂主面および前記樹脂裏面から露出していない、付記5に記載の半導体装置。

〔付記7〕

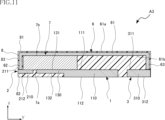

前記接続リードは、金属板である、付記5または6に記載の半導体装置。

〔付記8〕

前記接続リードは、前記厚さ方向視において前記半導体素子に重なる第1板状部と、

前記第2リードと前記第1板状部とに接続する第2板状部と、

を備えている、付記7に記載の半導体装置。

〔付記9〕

前記第1リードに対して、前記第2リードとは反対側に配置されている第3リードをさらに備え、

前記接続リードは、前記第3リードと前記第1板状部とに接続する第3板状部をさらに備えている、付記8に記載の半導体装置。

〔付記10〕

前記第2板状部および前記第3板状部は、前記厚さ方向に平行である、付記9に記載の半導体装置。

〔付記11〕

前記第1リードおよび前記第3リードの一部は、前記樹脂裏面から露出している、付記9または10に記載の半導体装置。

〔付記12〕

前記第3リードは、前記第1リードとは反対側を向き、かつ、前記樹脂側面から露出する第3端面を備え、

前記第3端面と前記樹脂側面とは、互いに面一である、付記9ないし11のいずれかに記載の半導体装置。

〔付記13〕

前記第1リードに対して、前記第2リードと同じ側に配置され、かつ、前記ゲート電極が接合されている第4リードをさらに備えている、付記5ないし12のいずれかに記載の半導体装置。

〔付記14〕

前記第4リードは、前記第1リードとは反対側を向き、かつ、前記樹脂側面から露出する第4端面を備え、

前記第4端面と前記樹脂側面とは、互いに面一である、付記13に記載の半導体装置。

〔付記15〕

前記第1リードは、前記厚さ方向視において前記第2リード側に向かって延びる複数の第1延出部を備え、

前記第2リードは、前記厚さ方向視において前記第1リード側に向かって延び、かつ、前記複数の第1延出部の間に配置される第2延出部を備え、

前記半導体素子は、前記第1延出部および前記第2延出部によって支持されている、付記4ないし14のいずれかに記載の半導体装置。

〔付記16〕

前記第2リードは、前記厚さ方向視において前記第1リード側に向かって延びる複数の第2延出部を備え、

前記第1リードは、前記厚さ方向視において前記第2リード側に向かって延び、かつ、前記複数の第2延出部の間に配置される第1延出部を備え、

前記半導体素子は、前記第1延出部および前記第2延出部によって支持されている、付記4ないし14のいずれかに記載の半導体装置。

〔付記17〕

前記第1リードは、前記第1延出部を2個以上備えており、

前記第2リードは、前記第2延出部を2個以上備えており、

前記第1延出部と前記第2延出部とは、前記第1延出部が延びる方向と前記厚さ方向とに直交する方向において、交互に配置されている、付記15または16に記載の半導体装置。

〔付記18〕

前記第1延出部および前記第2延出部は、前記封止樹脂に覆われている、付記15ないし17のいずれかに記載の半導体装置。

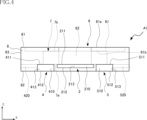

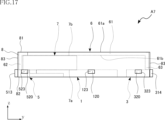

1 :第1リード

110 :端子部

111 :端子部主面

112 :端子部裏面

120 :連結部

121 :連結部主面

122 :連結部裏面

123 :連結部端面

130 :延出部

131 :延出部主面

132 :延出部裏面

2 :第2リード

210 :支持部

211 :支持部主面

212 :支持部裏面

213 :支持部端面

230 :延出部

231 :延出部主面

232 :延出部裏面

3 :第3リード

310 :端子部

311 :端子部主面

312 :端子部裏面

313 :端子部端面

314 :突出部

320 :連結部

321 :連結部主面

322 :連結部裏面

323 :連結部端面

4 :第4リード

410 :端子部

411 :端子部主面

412 :端子部裏面

413 :端子部端面

420 :連結部

421 :連結部主面

422 :連結部裏面

423 :連結部端面

5 :第5リード

510 :端子部

511 :端子部主面

512 :端子部裏面

513 :端子部端面

520 :連結部

521 :連結部主面

522 :連結部裏面

523 :連結部端面

6 :接続リード

61 :第1板部

61a :第1板部主面

61b :第1板部裏面

61c :突出面

62 :第2板部

63 :第3板部

65 :柱状部

7 :半導体素子

71 :ドレイン電極

711 :帯状部

712 :延出部

72 :ソース電極

721 :帯状部

722 :延出部

73,74:ゲート電極

75 :裏面電極

70 :素子本体

7a :素子主面

7b :素子裏面

701 :基板

702 :バッファ層

703 :第1窒化物半導体層

704 :第2窒化物半導体層

705 :第3窒化物半導体層

706 :保護膜

707 :導電部

709,709a~709c:配線

8 :封止樹脂

81 :樹脂主面

82 :樹脂裏面

83 :樹脂側面

Claims (15)

- 窒化物半導体からなる電子走行層と、厚さ方向において互いに反対側を向く素子主面および素子裏面と、前記素子主面に配置されたゲート電極、ソース電極、およびドレイン電極と、を有する半導体素子と、

前記ドレイン電極が接合されている第1リードと、

前記ソース電極が接合されている第2リードと、

前記第1リードに対して、前記第2リードとは反対側に配置されている第3リードと、

前記第2リードに接続し、かつ、前記素子裏面側に、前記厚さ方向視において前記半導体素子に重なるように配置されている接続リードと、

を備え、

前記接続リードは、

金属板であり、スイッチングの対象である主電流が流れ、

前記厚さ方向視において前記半導体素子に重なる第1板状部と、

前記第2リードと前記第1板状部とに接続する第2板状部と、

前記第3リードと前記第1板状部とに接続する第3板状部と、

を備えている、

半導体装置。 - 前記第2板状部および前記第3板状部は、前記厚さ方向に平行である、請求項1に記載の半導体装置。

- 前記接続リードは、前記素子裏面に接触している、請求項1または2に記載の半導体装置。

- 前記半導体素子は、前記素子裏面に配置され、かつ、前記ソース電極と電気的に接続された裏面電極をさらに備え、

前記接続リードには、前記裏面電極が接合されている、請求項3に記載の半導体装置。 - 前記半導体素子を覆う封止樹脂をさらに備え、

前記接続リードの一部は、前記封止樹脂から露出している、請求項1ないし4のいずれかに記載の半導体装置。 - 前記封止樹脂は、前記厚さ方向において互いに反対側を向く樹脂主面および樹脂裏面と、前記樹脂主面および前記樹脂裏面に繋がる樹脂側面とを有する、請求項5に記載の半導体装置。

- 前記第2リードは、前記樹脂主面および前記樹脂裏面から露出していない、請求項6に記載の半導体装置。

- 前記第1リードおよび前記第3リードの一部は、前記樹脂裏面から露出している、請求項6または7に記載の半導体装置。

- 前記第3リードは、前記第1リードとは反対側を向き、かつ、前記樹脂側面から露出する第3端面を備え、

前記第3端面と前記樹脂側面とは、互いに面一である、請求項6ないし8のいずれかに記載の半導体装置。 - 前記第1リードに対して、前記第2リードと同じ側に配置され、かつ、前記ゲート電極が接合されている第4リードをさらに備えている、請求項6ないし9のいずれかに記載の半導体装置。

- 前記第4リードは、前記第1リードとは反対側を向き、かつ、前記樹脂側面から露出する第4端面を備え、

前記第4端面と前記樹脂側面とは、互いに面一である、請求項10に記載の半導体装置。 - 前記第1リードは、前記厚さ方向視において前記第2リード側に向かって延びる複数の第1延出部を備え、

前記第2リードは、前記厚さ方向視において前記第1リード側に向かって延び、かつ、前記複数の第1延出部の間に配置される第2延出部を備え、

前記半導体素子は、前記第1延出部および前記第2延出部によって支持されている、請求項5ないし11のいずれかに記載の半導体装置。 - 前記第2リードは、前記厚さ方向視において前記第1リード側に向かって延びる複数の第2延出部を備え、

前記第1リードは、前記厚さ方向視において前記第2リード側に向かって延び、かつ、前記複数の第2延出部の間に配置される第1延出部を備え、

前記半導体素子は、前記第1延出部および前記第2延出部によって支持されている、請求項5ないし11のいずれかに記載の半導体装置。 - 前記第1リードは、前記第1延出部を2個以上備えており、

前記第2リードは、前記第2延出部を2個以上備えており、

前記第1延出部と前記第2延出部とは、前記第1延出部が延びる方向と前記厚さ方向とに直交する方向において、交互に配置されている、請求項12または13に記載の半導体装置。 - 前記第1延出部および前記第2延出部は、前記封止樹脂に覆われている、請求項12ないし14のいずれかに記載の半導体装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019122873 | 2019-07-01 | ||

| JP2019122873 | 2019-07-01 | ||

| PCT/JP2020/024238 WO2021002225A1 (ja) | 2019-07-01 | 2020-06-19 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2021002225A1 JPWO2021002225A1 (ja) | 2021-01-07 |

| JP7562529B2 true JP7562529B2 (ja) | 2024-10-07 |

Family

ID=74100598

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021529962A Active JP7562529B2 (ja) | 2019-07-01 | 2020-06-19 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US12165957B2 (ja) |

| JP (1) | JP7562529B2 (ja) |

| WO (1) | WO2021002225A1 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7636219B2 (ja) * | 2021-03-19 | 2025-02-26 | ローム株式会社 | 半導体装置 |

| WO2024181293A1 (ja) * | 2023-03-01 | 2024-09-06 | ローム株式会社 | 半導体装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013222781A (ja) | 2012-04-16 | 2013-10-28 | Sharp Corp | 半導体装置のデバイス実装構造 |

| JP2015216346A (ja) | 2014-05-07 | 2015-12-03 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | タンタルキャパシタ及びその製造方法 |

| JP2018056538A (ja) | 2016-09-26 | 2018-04-05 | 株式会社パウデック | 半導体パッケージ、モジュールおよび電気機器 |

| JP2018082011A (ja) | 2016-11-15 | 2018-05-24 | ローム株式会社 | 半導体デバイス |

| JP2018113429A (ja) | 2016-12-28 | 2018-07-19 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2941523B2 (ja) | 1991-10-25 | 1999-08-25 | ローム株式会社 | 半導体装置 |

| JPH07201914A (ja) * | 1993-12-29 | 1995-08-04 | Nippon Steel Corp | 半導体装置及びその製造方法 |

| JP2005175512A (ja) * | 2005-02-16 | 2005-06-30 | Nec Electronics Corp | 半導体装置 |

| JP6211829B2 (ja) | 2013-06-25 | 2017-10-11 | 株式会社東芝 | 半導体装置 |

-

2020

- 2020-06-19 JP JP2021529962A patent/JP7562529B2/ja active Active

- 2020-06-19 US US17/596,926 patent/US12165957B2/en active Active

- 2020-06-19 WO PCT/JP2020/024238 patent/WO2021002225A1/ja not_active Ceased

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013222781A (ja) | 2012-04-16 | 2013-10-28 | Sharp Corp | 半導体装置のデバイス実装構造 |

| JP2015216346A (ja) | 2014-05-07 | 2015-12-03 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | タンタルキャパシタ及びその製造方法 |

| JP2018056538A (ja) | 2016-09-26 | 2018-04-05 | 株式会社パウデック | 半導体パッケージ、モジュールおよび電気機器 |

| JP2018082011A (ja) | 2016-11-15 | 2018-05-24 | ローム株式会社 | 半導体デバイス |

| JP2018113429A (ja) | 2016-12-28 | 2018-07-19 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JPWO2021002225A1 (ja) | 2021-01-07 |

| US20220319964A1 (en) | 2022-10-06 |

| WO2021002225A1 (ja) | 2021-01-07 |

| US12165957B2 (en) | 2024-12-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7520177B2 (ja) | 半導体装置 | |

| US12347752B2 (en) | Semiconductor device | |

| JP6744610B2 (ja) | 半導体パッケージ、モジュールおよび電気機器 | |

| CN102074538A (zh) | 半导体装置及其引线框 | |

| JP7562529B2 (ja) | 半導体装置 | |

| JP7649127B2 (ja) | 半導体装置 | |

| CN115777142A (zh) | 半导体装置及半导体模组 | |

| US20230230904A1 (en) | Semiconductor device | |

| JP7582301B2 (ja) | 半導体装置 | |

| US20230361006A1 (en) | Semiconductor device | |

| JP2021190556A (ja) | 半導体装置の実装構造 | |

| JP7385414B2 (ja) | 半導体装置 | |

| US12463119B2 (en) | Semiconductor device and semiconductor device manufacturing method | |

| US20250226295A1 (en) | Multi-die semiconductor package | |

| US20250226351A1 (en) | Semiconductor package with heat flow restricting connector | |

| JP7835681B2 (ja) | 半導体装置 | |

| JP7535077B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| CN117913087A (zh) | 氮化物半导体元件及氮化物半导体装置 | |

| KR20260041001A (ko) | 컴팩트한 직접 본딩된 금속 기판 패키지 및 이를 조립하는 방법 | |

| WO2023140046A1 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240430 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240531 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240827 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240925 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7562529 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |