JP7561663B2 - ゲート駆動装置 - Google Patents

ゲート駆動装置 Download PDFInfo

- Publication number

- JP7561663B2 JP7561663B2 JP2021041380A JP2021041380A JP7561663B2 JP 7561663 B2 JP7561663 B2 JP 7561663B2 JP 2021041380 A JP2021041380 A JP 2021041380A JP 2021041380 A JP2021041380 A JP 2021041380A JP 7561663 B2 JP7561663 B2 JP 7561663B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- semiconductor switching

- reference voltage

- timing

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Landscapes

- Electronic Switches (AREA)

- Power Conversion In General (AREA)

Description

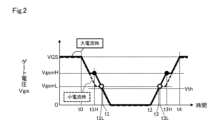

以下、本発明の第1実施形態について、図1~図3を参照して説明する。

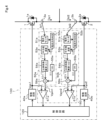

電気的構成を示す図1において、上下アームを構成する2つの半導体スイッチング素子であるNチャンネル型のMOSトランジスタ1、2は、直列接続された状態として電源端子間に接続されている。MOSトランジスタ1および2の共通接続点は負荷への出力端子となっている。また、MOSトランジスタ1はボディダイオード1aを有し、MOSトランジスタ2はボディダイオード2aを有する。

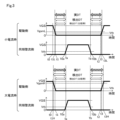

図4は第2実施形態を示すもので、以下、第1実施形態と異なる部分について説明する。この実施形態では、ゲート駆動装置100は、デッドタイム設定回路30a、30bの機能を制御回路120において実行する構成とされ、また、これによって、ゲート変動検出回路160はコンパレータ61a、61bを設ける構成としている。

したがって、このような第3実施形態においても第1実施形態と同様の作用効果を得ることができる。

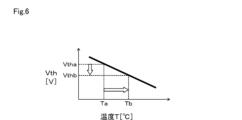

図5および図6は第3実施形態を示すもので、以下、第1実施形態と異なる部分について説明する。この実施形態では、ゲート駆動装置110は、参照電圧調整回路150a、150bとして、それぞれのMOSトランジスタ1、2の温度をモニタする機能を備えた構成としている。温度モニタの構成としては、例えば、検出部位にダイオードを配置し、これに一定電流を流す構成が設けられる。ダイオードに一定電流が流れたときの順方向電圧を検出することで温度を算出することができる。

なお、本発明は、上述した実施形態のみに限定されるものではなく、その要旨を逸脱しない範囲で種々の実施形態に適用可能であり、例えば、以下のように変形または拡張することができる。

Claims (5)

- 上アームおよび下アームにそれぞれ配置され整流素子を備えたゲート駆動型の半導体スイッチング素子のゲート駆動を行うゲート駆動装置であって、

前記上下アームのそれぞれの半導体スイッチング素子を交互に駆動するための駆動信号を送信する制御回路(20)と、

前記制御回路からの駆動信号に応じて前記上下アームのそれぞれの半導体スイッチング素子のゲートを駆動する駆動回路(40a、40b)と、

前記上下アームのそれぞれの半導体スイッチング素子についてゲート電圧が参照電圧と一致するタイミングを検出するゲート変動検出回路(60)と、

前記半導体スイッチング素子の電流値に応じて前記ゲート変動検出回路の前記参照電圧を調整する参照電圧調整回路(50a、50b)とを備え、

前記制御回路は、前記ゲート変動検出回路により検出される前記上下アームの前記半導体スイッチング素子のゲート電圧変動のタイミングからデッドタイムを算出し、次に駆動する側の駆動タイミングを調整するタイミング調整機能を備えるゲート駆動装置。 - 前記参照電圧調整回路は、前記参照電圧を、対応する前記半導体スイッチング素子の電流値の平方根に比例して変動させて設定する請求項1に記載のゲート駆動装置。

- 前記参照電圧は、前記半導体スイッチング素子のしきい値電圧に相当する定数項と、前記半導体スイッチング素子の電流値の平方根に比例して変動させて設定する変動項とを加算した電圧値に設定される請求項2に記載のゲート駆動装置。

- 前記参照電圧は、前記半導体スイッチング素子が同期整流時に対応し電流値が負である場合には前記変動項をゼロとして設定する請求項3に記載のゲート駆動装置。

- 前記参照電圧は、前記半導体スイッチング素子のしきい値電圧に相当する定数項についても、前記半導体スイッチング素子の素子温度に応じて変更設定される請求項3または4に記載のゲート駆動装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021041380A JP7561663B2 (ja) | 2021-03-15 | 2021-03-15 | ゲート駆動装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021041380A JP7561663B2 (ja) | 2021-03-15 | 2021-03-15 | ゲート駆動装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2022141181A JP2022141181A (ja) | 2022-09-29 |

| JP7561663B2 true JP7561663B2 (ja) | 2024-10-04 |

Family

ID=83403173

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021041380A Active JP7561663B2 (ja) | 2021-03-15 | 2021-03-15 | ゲート駆動装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7561663B2 (ja) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002272131A (ja) | 2001-03-07 | 2002-09-20 | Fuji Electric Co Ltd | 電力用半導体素子のゲート駆動回路 |

| JP2010016937A (ja) | 2008-07-02 | 2010-01-21 | Yaskawa Electric Corp | 電力変換装置とデッドタイム補償方法 |

| JP2015216818A (ja) | 2014-05-13 | 2015-12-03 | 株式会社デンソー | スイッチング素子の駆動回路 |

-

2021

- 2021-03-15 JP JP2021041380A patent/JP7561663B2/ja active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002272131A (ja) | 2001-03-07 | 2002-09-20 | Fuji Electric Co Ltd | 電力用半導体素子のゲート駆動回路 |

| JP2010016937A (ja) | 2008-07-02 | 2010-01-21 | Yaskawa Electric Corp | 電力変換装置とデッドタイム補償方法 |

| JP2015216818A (ja) | 2014-05-13 | 2015-12-03 | 株式会社デンソー | スイッチング素子の駆動回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2022141181A (ja) | 2022-09-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9829387B2 (en) | System and method for temperature sensing | |

| JP5862434B2 (ja) | パワートランジスタの駆動回路 | |

| US7969227B2 (en) | Temperature detection circuit | |

| US6838914B2 (en) | Semiconductor device | |

| US9929073B2 (en) | Semiconductor device | |

| WO2017186609A1 (en) | Junction temperature and current sensing | |

| CN112823469A (zh) | 栅极驱动装置 | |

| JP6286899B2 (ja) | 絶縁ゲート型半導体素子の駆動装置および電力変換装置 | |

| US10050031B2 (en) | Power conventer and semiconductor device | |

| CN115211009B (zh) | 栅极驱动装置 | |

| CN111512528B (zh) | 电力转换装置 | |

| US20240291402A1 (en) | Semiconductor device and power conversion device | |

| US20180175849A1 (en) | Driving device for semiconductor elements | |

| US10715136B2 (en) | Current sense devices and associated methods | |

| CN100422751C (zh) | 欠电流感应设备和方法 | |

| US11211924B2 (en) | Electronic circuit | |

| WO1997033370A1 (en) | Temperature-compensated driver circuit | |

| JP7041887B2 (ja) | 負荷駆動装置 | |

| JP7561663B2 (ja) | ゲート駆動装置 | |

| CN111880068A (zh) | 用于控制功率半导体开关的电路装置和方法 | |

| JP6906390B2 (ja) | スイッチング回路 | |

| US20240146179A1 (en) | Driving device for semiconductor element, and power conversion device | |

| WO2018096828A1 (ja) | ゲート駆動装置 | |

| RU2754501C1 (ru) | Управления металл-оксид-полупроводниковым полевым транзистором | |

| CN117728653A (zh) | 电子电路、电力变换装置及逆变器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20231211 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20240820 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240827 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240924 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7561663 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |