JP7221221B2 - Chip-embedded power converter - Google Patents

Chip-embedded power converter Download PDFInfo

- Publication number

- JP7221221B2 JP7221221B2 JP2019565153A JP2019565153A JP7221221B2 JP 7221221 B2 JP7221221 B2 JP 7221221B2 JP 2019565153 A JP2019565153 A JP 2019565153A JP 2019565153 A JP2019565153 A JP 2019565153A JP 7221221 B2 JP7221221 B2 JP 7221221B2

- Authority

- JP

- Japan

- Prior art keywords

- inductor

- switch

- converter

- power converter

- power

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/10—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/156—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators

- H02M3/158—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators including plural semiconductor devices as final control devices for a single load

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is dc

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/003—Constructional details, e.g. physical layout, assembly, wiring or busbar connections

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/10—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/156—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators

- H02M3/158—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators including plural semiconductor devices as final control devices for a single load

- H02M3/1584—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators including plural semiconductor devices as final control devices for a single load with a plurality of power processing stages connected in parallel

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Description

[関連出願の相互参照]

この出願は、2017年2月8日に出願された米国特許出願番号第15/428、019号(米国特許第9、729、059号として発行)の一部継続である、2017年8月4日に出願された米国特許出願番号第15/669、838の継続である。これらの出願の全内容を全ての目的のために本願に参照により援用する。

[Cross reference to related applications]

This application is a continuation-in-part of U.S. patent application Ser. This is a continuation of US patent application Ser. No. 15/669,838, filed on Jan. The entire contents of these applications are incorporated herein by reference for all purposes.

[技術分野]

本開示は、電子システム、直流-直流(DC-DC)変換器、電子デバイス設計、および電子デバイス製造技術に関する。

[Technical field]

The present disclosure relates to electronic systems, direct current-to-direct current (DC-DC) converters, electronic device design, and electronic device manufacturing techniques.

種々のDC-DC変換器が知られているが、これらのDC-DC変換器は、寄生損失および非効率性の影響を受ける非理想的な構成要素および/または構造からなる。改善された電力変換器に対する必要性がある。 Various DC-DC converters are known, but these DC-DC converters consist of non-ideal components and/or structures subject to parasitic losses and inefficiencies. There is a need for improved power converters.

いくつかの実施形態は、直流-直流(DC-DC)電力変換器について開示されており、この直流-直流電力変換器は、下面および上面を有する下部プリント基板(PCB)部分と、下面および上面を有する上部プリント基板(PCB)部分と、前記下部PCB部分の前記上面と前記上部PCB部分の前記下面との間の埋め込み型回路とを備え、前記埋め込み型回路は、パルス幅変調器と、少なくとも1つのスイッチとを備え、前記上部PCB部分を通って延びる1つまたは複数のビアと、前記上部PCB部分の前記上面に位置決めされたインダクタとを備え、前記1つまたは複数のビアは、前記インダクタおよび前記埋め込み型回路と電気的に連結されている。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記埋め込み型回路は集積回路(IC)を備える。

・前記インダクタのフットプリントは前記集積回路のフットプリントに少なくとも部分的に重なる。

・ワイヤボンドが前記インダクタと前記埋め込み型回路とを電気的に相互接続しない、

・前記回路は少なくとも1MHzの切替速度を有する。

・前記回路は少なくとも3MHzの切替速度を有する。

・前記回路は少なくとも5MHzの切替速度を有する。

・前記回路は最大7MHzの切替速度を有する。

・前記少なくとも1つのスイッチはエンハンスト窒化ガリウム電界効果トランジスタ(enhanced gallium nitride fieldeffect transistor、eGaNFET)を備える。

・前記上部PCB部分の前記上面に設けられた1つまたは複数のキャパシタをさらに備える。

・前記下部PCB部分の前記上面と前記上部PCB部分の前記下面との間に設けられたコアをさらに備え、前記コアはその内部に形成された1つまたは複数のポケットを備え、前記埋め込み型回路は前記1つまたは複数のポケットに設けられている。

・前記DC-DC電力変換器は25mm2未満のフットプリントを有する。

・前記DC-DC電力変換器は10mm2未満のフットプリントを有し、

・前記DC-DC電力変換器は5mm2未満のフットプリントを有し、

・前記DC-DC電力変換器が2mm2のように小さいフットプリントを有する。

・前記DC-DC電力変換器は電流のアンペア数当たり0.5mm2~10mm2であるフットプリント領域を有する。

Some embodiments are disclosed for a direct current-to-direct current (DC-DC) power converter comprising a lower printed circuit board (PCB) portion having a bottom surface and a top surface, and a bottom surface and a top surface. and embedded circuitry between the top surface of the bottom PCB section and the bottom surface of the top PCB section, the embedded circuitry comprising a pulse width modulator and at least a switch; one or more vias extending through the upper PCB portion; and an inductor positioned on the top surface of the upper PCB portion, wherein the one or more vias are connected to the inductor. and electrically coupled to the embedded circuit. This embodiment may feature any combination of the following. i.e.

- said embedded circuit comprises an integrated circuit (IC);

- the footprint of the inductor at least partially overlaps the footprint of the integrated circuit;

- wire bonds do not electrically interconnect the inductor and the embedded circuit;

- the circuit has a switching speed of at least 1 MHz;

- the circuit has a switching speed of at least 3 MHz;

• The circuit has a switching speed of at least 5 MHz.

• The circuit has a switching speed of up to 7 MHz.

- said at least one switch comprises an enhanced gallium nitride field effect transistor (eGaNFET);

• further comprising one or more capacitors provided on said top surface of said upper PCB portion;

- further comprising a core provided between said upper surface of said lower PCB portion and said lower surface of said upper PCB portion, said core comprising one or more pockets formed therein, said embedded circuit; are provided in said one or more pockets.

- Said DC-DC power converter has a footprint of less than 25mm2 .

- said DC-DC power converter has a footprint of less than 10mm2 ;

- said DC-DC power converter has a footprint of less than 5 mm2 ;

- The DC-DC power converter has a footprint as small as 2mm2 .

• Said DC-DC power converter has a footprint area that is between 0.5 mm 2 and 10 mm 2 per amperage of current.

いくつかの実施形態は、直流-直流(DC-DC)電力変換器パッケージについて開示されており、この直流-直流電力変換器パッケージは、少なくとも1つのプリント基板(PCB)に埋め込まれた集積回路(IC)チップであって、ドライバを備えるICチップと、と、前記チップ埋め込みパッケージの外部に位置決めされ、前記チップ埋め込みパッケージの表面に連結されたインダクタと、前記インダクタを前記ICチップに電気的に連結するビアとを備え、前記インダクタのフットプリントは、前記ICチップのフットプリントに少なくとも部分的に重なる。本実施形態は、以下のいずれかを特徴とし得る。すなわち、トランジスタは前記少なくとも1つのPCBに埋め込みされる、前記インダクタは前記トランジスタと電気的に連結される、前記ICチップは、前記ドライバに連結されたパルス幅変調器(PWM)コントローラと、前記ドライバの出力部と連結されたスイッチングトランジスタとを備える、エンハンスト窒化ガリウム(eGaN)を含むスイッチをさらに備える、前記スイッチは4MHz以上で切り替わるように構成されている、前記スイッチは5MHz以上で切り替わるように構成されている、シリコンまたはヒ化ガリウムの少なくとも1つを含むスイッチをさらに備える。 Some embodiments are disclosed for a direct current to direct current (DC-DC) power converter package, which includes an integrated circuit ( an IC chip, the IC chip comprising a driver; an inductor positioned outside the chip-embedded package and coupled to a surface of the chip-embedded package; and electrically coupling the inductor to the IC chip. and a via, wherein the footprint of the inductor at least partially overlaps the footprint of the IC chip. This embodiment may be characterized by any of the following. a transistor is embedded in the at least one PCB; the inductor is electrically coupled to the transistor; the IC chip comprises a pulse width modulator (PWM) controller coupled to the driver; further comprising a switch comprising enhanced gallium nitride (eGaN) comprising a switching transistor coupled to an output of and a switch comprising at least one of silicon or gallium arsenide.

いくつかの実施形態は、単一のパッケージにおける直流-直流(DC-DC)電力変換器について開示されており、この直流-直流電力変換器は、実装基板の内側に、少なくとも部分的に、埋め込まれたエンハンスト窒化ガリウム(eGaN)構成要素と、前記実装基板の外側に搭載されたインダクタと、前記eGaN構成要素に前記インダクタを連結するビアとを備え、前記インダクタのフットプリントは、前記eGaN構成要素のフットプリントに少なくとも部分的に重なる。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記実装基板は多層PCBである。

・前記eGaN構成要素はeGaNを含むスイッチであり、前記DC-DC電力変換器は前記スイッチを駆動するドライバ回路をさらに備える。

・前記ドライバおよび前記スイッチは、ICチップの一部である。

・前記ICチップは、パルス幅変調器(PWM)コントローラをさらに備える。

Some embodiments are disclosed for a direct current to direct current (DC-DC) power converter in a single package, the direct current to direct current power converter being embedded, at least partially, inside a mounting substrate. an enhanced gallium nitride (eGaN) component mounted on the substrate; an inductor mounted on the outside of the mounting substrate; and a via coupling the inductor to the eGaN component, the footprint of the inductor at least partially overlap the footprint of This embodiment may feature any combination of the following. i.e.

- The mounting substrate is a multi-layer PCB.

- the eGaN component is a switch comprising eGaN, and the DC-DC power converter further comprises a driver circuit for driving the switch;

• the driver and the switch are part of an IC chip;

- the IC chip further comprises a pulse width modulator (PWM) controller;

いくつかの実施形態は、チップ埋め込みパッケージを利用する直流-直流(DC-DC)電力変換器について開示されており、このDC-DC変換器は、プリント基板(PCB)の内側におけるエンハンスト窒化ガリウム(eGaN)スイッチと、パルス幅変調器(PWM)コントローラと、前記PCBの内部に埋め込まれたドライバとを備え、前記PWMコントローラおよび前記ドライバは、1MHz以上の周波数で前記eGaNスイッチを駆動するように構成され、そして、このDC-DC変換器は、前記チップ埋め込みパッケージの外部に配置され、前記PCBの表面に連結されたインダクタと、前記インダクタを前記eGaNスイッチに電気的に連結するビアとを備える。これらの実施形態は、前記ドライバが前記eGaNスイッチを5MHz以上の周波数で駆動するように構成されていることを特徴とし得る。 Some embodiments are disclosed for direct-current-to-direct-current (DC-DC) power converters that utilize chip-embedded packages, which include enhanced gallium nitride ( a pulse width modulator (PWM) controller; and a driver embedded within said PCB, said PWM controller and said driver configured to drive said eGaN switch at a frequency of 1 MHz or higher. and the DC-DC converter comprises an inductor located outside the chip-embedded package and coupled to the surface of the PCB, and a via electrically coupling the inductor to the eGaN switch. These embodiments can be characterized in that the driver is configured to drive the eGaN switch at a frequency of 5 MHz or greater.

いくつかの実施形態は、直流-直流(DC-DC)電力変換器について開示されており、この直流-直流電力変換器は、プリント基板と、前記プリント基板の内側の集積回路とを備え、前記集積回路はドライバを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記プリント基板を通って延びる1つまたは複数のビアにより前記集積回路と電気的に連結されたインダクタをさらに備える。

・前記インダクタは、前記集積回路のフットプリントに少なくとも部分的に重なるフットプリントを有する。

Some embodiments are disclosed for a direct current to direct current (DC-DC) power converter comprising a printed circuit board and an integrated circuit inside said printed circuit board, said The integrated circuit has a driver. This embodiment may feature any combination of the following. i.e.

• further comprising an inductor electrically coupled to said integrated circuit by one or more vias extending through said printed circuit board;

- the inductor has a footprint that at least partially overlaps the footprint of the integrated circuit;

いくつかの実施形態は、直流-直流(DC-DC)電力変換器について開示されており、この直流-直流電力変換器は、ドライバを備える集積回路と、前記インダクタのフットプリントが前記集積回路のフットプリントに少なくとも部分的に重なるように、前記集積回路に垂直に積層されたインダクタとを備え、前記インダクタは、前記集積回路と電気的に連結されている。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・第1面と前記第1面とは反対側の第2面とを有するプリント基板(PCB)をさらに備え、前記集積回路は、前記PCBの前記第1面に実装され、前記インダクタは、前記PCBの前記第2側に実装される。

・前記インダクタは、前記プリント基板を通って延びる1つまたは複数のビアにより前記集積回路と電気的に連結されている。

Some embodiments are disclosed for a direct current to direct current (DC-DC) power converter comprising an integrated circuit comprising a driver and a footprint of the inductor an inductor vertically stacked on the integrated circuit to at least partially overlap the footprint, the inductor electrically coupled to the integrated circuit. This embodiment may feature any combination of the following. i.e.

- further comprising a printed circuit board (PCB) having a first side and a second side opposite said first side, said integrated circuit being mounted on said first side of said PCB; Mounted on the second side of the PCB.

- the inductor is electrically coupled to the integrated circuit by one or more vias extending through the printed circuit board;

いくつかの実施形態は、直流-直流(DC-DC)バックコンバータについて開示されており、この直流-直流電力変換器は、1つまたは複数のスイッチと、前記1つまたは複数のスイッチを駆動するドライバと、前記スイッチと電気的に連結されたインダクタとを備え、前記DC-DCバックコンバータの前記フットプリントは、65mm2未満であり、前記DC-DCバックコンバータは、少なくとも20アンペアの電流を受信するように構成され、前記DC-DCバックコンバータは、少なくとも20アンペアの電流を出力するように構成されている。 Some embodiments are disclosed for a direct current to direct current (DC-DC) buck converter, the direct current to direct current power converter driving one or more switches and the one or more switches a driver and an inductor electrically coupled to the switch, wherein the footprint of the DC-DC buck converter is less than 65 mm 2 and the DC-DC buck converter receives a current of at least 20 amps; and the DC-DC buck converter is configured to output a current of at least 20 amps.

いくつかの実施形態は、直流-直流(DC-DC)電力変換器について開示されており、この直流-直流電力変換器は、1つまたは複数のスイッチと、前記1つまたは複数のスイッチを1MHz以上5MHz以下の周波数で駆動するように構成されたドライバと、前記1つまたは複数のスイッチと電気的に連結されたインダクタとを備え、前記DC-DC変換器の前記フットプリントは、10mm2以下であり、前記DC-DC変換器は少なくとも5アンペアの電流を受信するように構成されており、前記DC-DC変換器は少なくとも5アンペアの電流を出力するように構成されている。 Some embodiments are disclosed for a direct current to direct current (DC-DC) power converter comprising one or more switches and switching the one or more switches to 1 MHz a driver configured to drive at a frequency greater than or equal to 5 MHz and less than or equal to 5 MHz; and an inductor electrically coupled to the one or more switches, wherein the footprint of the DC-DC converter is less than or equal to 10 mm 2 . and wherein the DC-DC converter is configured to receive a current of at least 5 Amps and the DC-DC converter is configured to output a current of at least 5 Amps.

いくつかの実施形態は、直流-直流(DC-DC)電力変換器について開示されており、この直流-直流電力変換器は、第1インダクタと連結された第1スイッチと、第2インダクタと連結された第2スイッチと、プリント基板に埋め込まれた集積回路チップとを備え、前記第1スイッチおよび前記第2スイッチは、変調器と連結され、前記第1インダクタおよび前記第2インダクタは、電圧出力ノードと連結されている。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記変調器は、前記集積回路チップに含まれる。

・前記変調器は、前記第1スイッチおよび前記第2スイッチに同期期間で位相を出力するように動作させるように構成されている。

・前記出力ノードにおける出力信号は、第1インダクタを介した第1信号および第2インダクタを介した第2信号に重畳される。

Some embodiments are disclosed for a direct current to direct current (DC-DC) power converter, the direct current to direct current power converter having a first switch coupled with a first inductor and a second inductor. and an integrated circuit chip embedded in a printed circuit board, wherein the first switch and the second switch are coupled with a modulator, and the first inductor and the second inductor are voltage output connected to the node. This embodiment may feature any combination of the following. i.e.

- the modulator is included in the integrated circuit chip;

- the modulator is arranged to operate the first switch and the second switch to output a phase in a synchronous period;

- the output signal at the output node is superimposed on a first signal via a first inductor and a second signal via a second inductor;

いくつかの実施形態は、直流-直流(DC-DC)電力変換器について開示されており、この直流-直流電力変換器は、プリント基板に埋め込まれた集積回路チップであって、ドライバを備える集積回路チップと、前記ドライバと連結された第1スイッチと、前記第1スイッチと連結されたインダクタと、出力ノードから変調回路へのフィードバック経路とを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記変調回路は、電圧モード変調回路である。

・前記変調回路は、常時オン時間または常時オフ時間変調回路である。

・前記変調回路は、前記集積回路チップに含まれる。

・前記変調回路および前記インダクタは、前記集積回路チップと共にパッケージに含まれている。

Some embodiments are disclosed for a direct current-to-direct current (DC-DC) power converter, which is an integrated circuit chip embedded in a printed circuit board and comprising a driver. A circuit chip, a first switch coupled to the driver, an inductor coupled to the first switch, and a feedback path from an output node to a modulation circuit. This embodiment may feature any combination of the following. i.e.

- said modulation circuit is a voltage mode modulation circuit;

- the modulation circuit is an always-on-time or always-off-time modulation circuit;

- the modulation circuit is included in the integrated circuit chip;

- the modulation circuit and the inductor are included in a package with the integrated circuit chip;

いくつかの実施形態は、直流-直流(DC-DC)電力変換器について開示されており、この直流-直流電力変換器は、プリント基板に埋め込まれた集積回路チップであって、ドライバを備える集積回路チップと、前記ドライバと連結された第1スイッチと、前記第1スイッチと連結されたインダクタと、出力ノードから変調回路へのフィードバック経路と、ランプ波発生器とを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記フィードバック経路と、前記ランプ波発生器からの出力とが比較器に連結される。

・前記比較器と連結された基準電圧源をさらに備える。

・前記ランプ波発生器は、前記インダクタを通るリップル電流をエミュレートするように構成される。

・前記ランプ波発生器は、第1電流源と、第2電流源と、キャパシタとを備える。

・前記第1電流源および前記第2電流源は、少なくとも一部が前記インダクタのインダクタンスに基づいてトリムされるように構成される。

・前記ランプ波発生器および前記インダクタは、同じDC-DC電力変換器パッケージに含まれる。

・前記ランプ波発生器は、前記インダクタに連結された出力キャパシタにより影響を受けない出力信号を生成するように構成されている。

・前記ランプ波発生器は、前記インダクタに連結された出力キャパシタの等価直列抵抗(ESR)から独立した出力信号を生成するように構成されている。

・前記出力キャパシタのリップル電圧が小さすぎて変調回路へ確実に提供されないように、十分に低いESRを有する出力キャパシタをさらに備える。

Some embodiments are disclosed for a direct current-to-direct current (DC-DC) power converter, which is an integrated circuit chip embedded in a printed circuit board and comprising a driver. A circuit chip, a first switch coupled with the driver, an inductor coupled with the first switch, a feedback path from an output node to a modulation circuit, and a ramp generator. This embodiment may feature any combination of the following. i.e.

• the feedback path and the output from the ramp generator are coupled to a comparator;

• further comprising a reference voltage source connected to the comparator;

- the ramp generator is configured to emulate a ripple current through the inductor;

- the ramp generator comprises a first current source, a second current source and a capacitor;

- the first current source and the second current source are configured to be trimmed at least in part based on the inductance of the inductor;

- The ramp generator and the inductor are included in the same DC-DC power converter package.

- the ramp generator is configured to generate an output signal that is unaffected by an output capacitor coupled to the inductor;

- the ramp generator is configured to generate an output signal independent of the equivalent series resistance (ESR) of an output capacitor coupled to the inductor;

• further comprising an output capacitor with a sufficiently low ESR to ensure that the ripple voltage of said output capacitor is not too small to be provided to the modulation circuit;

いくつかの実施形態は、以下を備えるランプ波発生器について開示されている。すなわち、供給電圧に連結された第1電流源と、アースに連結された第2電流源と、前記第1電流源と前記第2電流源との間に連結されたキャパシタとを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記ランプ波発生器は、DC-DC変換器においてインダクタを通るリップル電流をエミュレートするように構成される。

・前記第1電流源の前記出力は、DC-DC変換器に対する入力電圧少なくとも一部が基づいている。

・前記第1電流源の前記出力は、DC-DC変換器におけるインダクタのインダクタンスに少なくとも一部が基づいている。

・前記第2電流源の前記出力は、DC-DC変換器におけるインダクタのインダクタンスに少なくとも一部が基づいている。

・前記第2電流源の前記出力は、DC-DC変換器におけるインダクタのインダクタンスに少なくとも一部が基づいている。

・前記第1電流源は、DC-DC変換器に置けるインダクタのインダクタンスに少なくとも一部が基づいてトリムされるように構成されている。

・前記第2電流源は、DC-DC変換器におけるインダクタのインダクタンスに少なくとも一部が基づいてトリムされるように構成されている。

Some embodiments are disclosed for a ramp generator comprising: a. That is, it comprises a first current source connected to a supply voltage, a second current source connected to ground, and a capacitor connected between the first current source and the second current source. This embodiment may feature any combination of the following. i.e.

- the ramp generator is configured to emulate a ripple current through an inductor in a DC-DC converter;

- said output of said first current source is based at least in part on an input voltage to a DC-DC converter;

- the output of the first current source is based at least in part on the inductance of an inductor in a DC-DC converter;

- the output of the second current source is based at least in part on the inductance of an inductor in a DC-DC converter;

• the output of the second current source is based at least in part on the inductance of an inductor in a DC-DC converter;

• the first current source is configured to be trimmed based at least in part on the inductance of an inductor in the DC-DC converter;

• the second current source is configured to be trimmed based at least in part on the inductance of an inductor in the DC-DC converter;

いくつかの実施形態は、チップ埋め込み型直流-直流変換器の作成のための、以下を含む方法について開示されている。すなわち、プリント基板に集積回路チップを埋め込み、前記プリント基板に第1インダクタを連結し、前記プリント基板に第2インダクタを連結し、前記第1インダクタおよび前記第2インダクタの双方は出力ノードに連結されていることを含む。 Some embodiments are disclosed for methods for making chip-embedded DC-DC converters, including: An integrated circuit chip is embedded in a printed circuit board, a first inductor is connected to the printed circuit board, a second inductor is connected to the printed circuit board, and both the first inductor and the second inductor are connected to an output node. including being

いくつかの実施形態は、第1直流電圧を第2直流電圧に変換する、以下を含む方法について開示されている。すなわち、第1インダクタと連結された第1スイッチを駆動し、第2インダクタと連結された第2スイッチを駆動し、前記第1スイッチおよび前記第2スイッチは、出力ノードに連結され、前記第1スイッチおよび前記第2スイッチを位相をずらして変調し、ドライバまたは変調器の少なくとも1つのがプリント基板に埋め込まれたチップに含まれる。 Some embodiments are disclosed for methods of converting a first DC voltage to a second DC voltage, including: a. That is, a first switch connected to a first inductor is driven, a second switch connected to a second inductor is driven, the first switch and the second switch are connected to an output node, and the first switch is connected to the output node. Modulating the switch and said second switch out of phase, at least one of the driver or modulator being included in a chip embedded in a printed circuit board.

いくつかの実施形態は、チップ埋め込み型直流-直流変換器の作成のための、以下を含む方法について開示されている。すなわち、プリント基板に集積回路チップを埋め込み、前記集積回路チップと出力ノードとの間にインダクタを連結し、前記出力ノードから変調回路へのフィードバック経路を提供し、前記変調回路がランプ波発生器を含む。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記変調回路は、前記プリント基板に含まれる。

・前記変調回路は、常時オン時間または常時オフ時間変調回路である。

・前記ランプ波発生器は、前記集積回路に含まれる。

・前記ランプ波発生器を少なくとも一部は前記インダクタの特性に基づいてトリムすることをさらに備える。

・前記ランプ波発生器は、いずれかの上記実施形態のランプ波発生器である。

Some embodiments are disclosed for methods for making chip-embedded DC-DC converters, including: An integrated circuit chip is embedded in a printed circuit board, an inductor is coupled between the integrated circuit chip and an output node to provide a feedback path from the output node to a modulation circuit, the modulation circuit driving a ramp generator. include. This embodiment may feature any combination of the following. i.e.

- The modulation circuit is included in the printed circuit board.

- the modulation circuit is an always-on-time or always-off-time modulation circuit;

- the ramp generator is included in the integrated circuit;

• further comprising trimming the ramp generator based at least in part on the characteristics of the inductor;

- the ramp generator is the ramp generator of any of the above embodiments;

いくつかの実施形態は、直流-直流変換器の使用のための、以下を含む方法について開示されている。すなわち、入力ノードにおいて入力電力を受信し、インダクタへスイッチを通して電力を提供し、出力電圧が出力キャパシタ両端に生じるように出力キャパシタにエネルギーを格納し、前記出力電圧で出力電力を出力ノードへ提供し、前記出力電圧を変調回路へ提供し、出力キャパシタとは独立したリップル電圧を生成し、前記リップル電圧を前記変調回路へ提供し、前記スイッチを、前記変調回路の出力に少なくとも一部は基づいて変調する。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記リップル電圧、基準電圧、および前記出力電圧のうち少なくとも2つを比較することをさらに含む。

・電流源を、少なくとも一部は、前記インダクタのインダクタンスに基づいてトリムすることをさらに備える。

・前記リップル電圧は、前記インダクタを通る電流をエミュレートするように構成されたランプ波発生器により生成される。

Some embodiments are disclosed for methods for use of DC-to-DC converters, including: That is, receiving input power at an input node, providing power through a switch to an inductor, storing energy in the output capacitor such that an output voltage appears across the output capacitor, and providing output power to the output node at said output voltage. providing said output voltage to a modulation circuit; generating a ripple voltage independent of an output capacitor; providing said ripple voltage to said modulation circuit; and configuring said switch based at least in part on the output of said modulation circuit. modulate. This embodiment may feature any combination of the following. i.e.

- further comprising comparing at least two of said ripple voltage, a reference voltage and said output voltage;

- further comprising trimming a current source based at least in part on the inductance of said inductor;

- the ripple voltage is generated by a ramp generator configured to emulate the current through the inductor;

いくつかの実施形態は、直流-直流(DC-DC)電力変換器パッケージについて開示されており、この直流-直流電力変換器パッケージは、少なくとも1つのプリント基板(PCB)に埋め込まれた集積回路(IC)チップであって、ドライバを備えるICチップと、前記チップ埋め込みパッケージの外部に位置決めされ、前記チップ埋め込みパッケージの表面に連結されたインダクタと、前記インダクタへ提供される電流が限界を超えた場合を検出するように構成された過電流保護回路とを備える。本実施形態は、以下の任意の組み合わせを特徴とし得る。すなわち、

・前記過電流保護回路は、少なくとも一部が集積回路間または電源管理バスコマンドに基づいて調整またはトリムされるように構成された電流源を備える。

・前記インダクタの飽和インダクタンスが前記限界を超え、かつ、前記限界を50%未満超える。

・前記限界は、最大規定DC電流仕様プラス最大交流電流リップル仕様を50%未満超過する。

Some embodiments are disclosed for a direct current to direct current (DC-DC) power converter package, the direct current to direct current power converter package comprising an integrated circuit ( IC) chip, the IC chip comprising a driver, an inductor positioned outside the chip-embedded package and coupled to the surface of the chip-embedded package, and when the current provided to the inductor exceeds a limit. an overcurrent protection circuit configured to detect This embodiment may feature any combination of the following. i.e.

- the overcurrent protection circuit comprises a current source configured at least in part to be regulated or trimmed based on inter-integrated circuit or power management bus commands;

• the saturated inductance of the inductor exceeds the limit and exceeds the limit by less than 50%;

• Said limit exceeds the maximum specified DC current specification plus maximum AC current ripple specification by less than 50%.

ここに開示されたいくつかの実施形態は、直流-直流(DC-DC)電力変換器パッケージに関し、この直流-直流電力変換器パッケージは、少なくとも1つのプリント基板(PCB)に埋め込まれた集積回路(IC)チップであって、ドライバを備える前記ICチップと、前記チップ埋め込みパッケージの外部に位置決めされ、前記チップ埋め込みパッケージの表面に連結されたインダクタと、集積回路間または電源管理バスとを備える。本実施形態は、以下の任意の組み合わせを有し得る。すなわち、

・前記集積回路間または電源管理バスは少なくとも1つの電流源に連結され、プロトコルコマンドを提供して前記電流源を調節またはトリムするように構成されている。

・前記集積回路間または電源管理バスは少なくとも1つの電流源に連結され、プロトコルコマンドを提供して比較器へ提供される基準値を設定または調節するように構成されている。

・前記集積回路間または電源管理バスは、前記DC-DC電力変換器パッケージのオンまたはオフ、前記DC-DC電力変換器パッケージの低電力またはスリープモードの変更、前記DC-DC電力変換器パッケージの電流設定についての情報の読み出し、前記DC-DC電力変換器パッケージについて診断および/または技術情報の読み出し、前記DC-DC電力変換器パッケージにより提供される出力電圧の設定または変更、の少なくとも1つを実施するための指示を含むプロトコルを通信するように構成されている。

・集積回路間実装品の上に配線層として電源管理プロトコルを実施する。

Some embodiments disclosed herein relate to a direct current-to-direct current (DC-DC) power converter package, which includes an integrated circuit embedded in at least one printed circuit board (PCB). An (IC) chip comprising: said IC chip with drivers; an inductor positioned outside said chip-embedded package and coupled to a surface of said chip-embedded package; and an inter-integrated circuit or power management bus. This embodiment may have any combination of the following. i.e.

- the inter-integrated circuit or power management bus is coupled to at least one current source and is configured to provide protocol commands to adjust or trim the current source;

- the inter-integrated circuit or power management bus is coupled to at least one current source and configured to provide protocol commands to set or adjust the reference value provided to the comparator;

the inter-integrated circuit or power management bus can turn on or off the DC-DC power converter package, change the low power or sleep mode of the DC-DC power converter package, at least one of reading information about current settings, reading diagnostic and/or technical information about the DC-DC power converter package, and setting or changing the output voltage provided by the DC-DC power converter package. It is configured to communicate a protocol including instructions to implement.

• Implement the power management protocol as a wiring layer above the inter-integrated circuit implementation.

ここに開示されたいくつかの実施形態は、以下を備える電力変換器を特徴とする。すなわち、プリント基板(PCB)(前記プリント基板は、下面および上面を有する下部プリント基板(PCB)部分と、下面および上面を有する上部プリント基板(PCB)部分とを備える)と、前記下部PCB部分の前記上面と前記上部PCB部分の前記下面との間の埋め込み型回路(1つまたは複数のドライバ信号を生成するように構成されたドライバと、前記1つまたは複数のドライバ信号により駆動されるように構成された1つまたは複数のスイッチとを備える前記埋め込み型回路)と、前記上部PCB部分を通って延びる1つまたは複数のビアと、前記上部PCB部分の前記上面に位置決めされたインダクタとを備え、前記1つまたは複数のビアは、前記インダクタおよび前記埋め込み型回路と電気的に連結され、前記インダクタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なる。本実施形態は、以下の任意の組み合わせを有し得る。すなわち、

・前記電力変換器は、前記電力変換器の入力部と出力部との間の直接的な電気的接続を絶縁するように構成された絶縁トポロジで構成される。

・前記絶縁トポロジは、フライバックトポロジ、順方向変換器トポロジ、2トランジスタ順方向、LLC共振変換器、プッシュプルトポロジ、フルブリッジ、ハイブリッド、PWM共振変換器、およびハーフブリッジトポロジの少なくとも1つを備える。

・前記第1インダクタを通る変更電流が前記第2インダクタにおける変更電流を誘発するように構成された前記第1インダクタおよび前記第2インダクタを含む変圧器をさらに備える。

・前記埋め込み型回路と同じパッケージにおける無線通信システムをさらに備える。

・前記電力変換器の出力は、前記無線信号システムにより受信される無線信号に応じて調整されるように構成される。前記インダクタを通る電流リップルをエミュレートする信号を生成するように構成されたランプ波発生器を有するフィードバックシステムをさらに備え、前記フィードバックシステムは、前記無線通信システムにより受信される無線信号に応じてトリムまたは調整されるように構成された電流源を備える。

・前記埋め込み型回路は前記無線通信システムを備える。

・前記電力変換器の出力を調整するための制御信号を受信するように構成された通信インターフェースをさらに備える。

・前記通信インターフェースは電源管理バス(PMBUS)を備える。

・前記通信インターフェースは、集積回路間(I2C)プロトコルを実施するように構成されている。

・前記インダクタを通る電流リップルをエミュレートする信号を生成するように構成されたランプ波発生器を有するフィードバックシステムをさらに備え、前記フィードバックシステムは、前記通信インターフェースを介して受信されるコマンドに応じて前記ランプ波発生器をトリムするように構成されている。

・前記埋め込み型回路は、1つまたは複数のPWM信号を生成するように構成されたパルス幅変調器(PWM)コントローラを備え、前記PWMコントローラは、前記ドライバと連結され、前記ドライバは、少なくとも一部は前記PWM信号に基づいて1つまたは複数のドライバ信号を生成するように構成される。

・前記インダクタは、定格電流を有し、前記インダクタは、飽和定格を有し、前記飽和定格は、前記定格電流よりも50%未満高い。

・前記インダクタは、定格電流を有し、前記インダクタは、飽和定格を有し、前記飽和定格は、前記定格電流よりも20%未満高い。

・前記インダクタを通る電流が前記飽和定格を上回るのを防止するように構成された過電流保護回路をさらに備える。

・過電流条件の検出に応じて前記1つまたは複数のスイッチの少なくとも1つを開くように構成された過電流保護回路さらに備える。

・前記電力変換器は、直流-直流(DC-DC)電力変換器である。

・前記電力変換器は、交流-直流(AC-DC)電力変換器である。

・電流源を有するフィードバックシステムをさらに備え、前記電流源は、前記無線通信システムにより受信される無線信号に少なくとも一部が基づいてトリムまたは調整されるように構成されている。

・前記インダクタを通る電流の指標を提供するように構成された過電流保護システムをさらに備え、前記過電流システムは電流源を備え、前記電流源は、前記無線通信システムにより受信される無線信号に少なくとも一部が基づいてトリムまたは調整されるように構成されている。

Some embodiments disclosed herein feature power converters comprising: a printed circuit board (PCB), said printed circuit board comprising a lower printed circuit board (PCB) portion having a bottom surface and a top surface, and an upper printed circuit board (PCB) portion having a bottom surface and a top surface; Embedded circuitry between the top surface and the bottom surface of the upper PCB portion (drivers configured to generate one or more driver signals and to be driven by the one or more driver signals) one or more vias extending through the upper PCB portion; and an inductor positioned on the top surface of the upper PCB portion. , the one or more vias are electrically coupled to the inductor and the embedded circuit, and the footprint of the inductor at least partially overlaps the footprint of the embedded circuit. This embodiment may have any combination of the following. i.e.

- the power converter is configured with an isolation topology configured to isolate a direct electrical connection between an input and an output of the power converter;

- said isolation topology comprises at least one of a flyback topology, a forward converter topology, a two-transistor forward, an LLC resonant converter, a push-pull topology, a full-bridge, a hybrid, a PWM resonant converter, and a half-bridge topology; .

• further comprising a transformer comprising said first inductor and said second inductor configured such that a modified current through said first inductor induces a modified current in said second inductor;

• further comprising a wireless communication system in the same package as the embedded circuit;

- the output of said power converter is arranged to be adjusted in response to a radio signal received by said radio signal system; Further comprising a feedback system having a ramp generator configured to generate a signal emulating current ripple through the inductor, the feedback system being trimmed in response to a radio signal received by the radio communication system. or with a current source configured to be regulated.

- the embedded circuit comprises the wireless communication system;

• further comprising a communication interface configured to receive a control signal for regulating the output of said power converter;

- The communication interface comprises a power management bus (PMBUS).

- the communication interface is configured to implement an inter-integrated circuit (I2C) protocol;

- further comprising a feedback system having a ramp generator configured to generate a signal emulating a current ripple through the inductor, the feedback system being responsive to commands received via the communication interface; configured to trim the ramp generator;

- the embedded circuit comprises a pulse width modulator (PWM) controller configured to generate one or more PWM signals, the PWM controller coupled to the driver, the driver comprising at least one A unit is configured to generate one or more driver signals based on said PWM signal.

- said inductor has a rated current, said inductor has a saturation rating, said saturation rating being less than 50% higher than said rated current;

- said inductor has a rated current, said inductor has a saturation rating, said saturation rating being less than 20% higher than said rated current;

• further comprising an overcurrent protection circuit configured to prevent current through said inductor from exceeding said saturation rating;

• further comprising an overcurrent protection circuit configured to open at least one of said one or more switches in response to detection of an overcurrent condition;

- said power converter is a direct current to direct current (DC-DC) power converter;

- said power converter is an alternating current to direct current (AC-DC) power converter;

• further comprising a feedback system comprising a current source, said current source being configured to be trimmed or adjusted based at least in part on radio signals received by said wireless communication system;

- further comprising an overcurrent protection system configured to provide an indication of the current through the inductor, the overcurrent system comprising a current source, the current source responsive to a radio signal received by the wireless communication system; configured to be trimmed or adjusted based at least in part.

ここに開示されたいくつかの実施形態は、以下を備える品目を特徴とし、すなわち、前記パラグラフの前記電力変換器と、電力を用いる物理作用を実施するように構成された第1システムと、前記第1システムを制御するように構成された電気システムとを備え、前記電力変換器は、前記第1システムおよび前記電気システムの一方または双方に電力を提供するように構成され、前記電気システムは、前記電力変換器の前記埋め込み型回路と同じパッケージにある前記無線通信システムにより受信される無線信号に少なくとも一部は基づいて前記第1システムを制御するように構成されている。いくつかの実施形態において、前記品目はインターネット・オブ・シングス装置である。いくつかの実施形態は、以下を備える電力供給システムを特徴とする。すなわち、複数の電力変換器であって、前記パラグラフの電力変換器にそれぞれ応じた電力変換器と、複数のPWM信号を生成するように構成された共用パルス幅変調器(PWM)コントローラとを備え、前記PWMコントローラは、前記複数の電力変換器の前記ドライバと連結されて、前記複数のPWM信号を前記電力変換器の前記対応するドライバへ送り、前記ドライバは、少なくとも一部は前記PWM信号に基づいて前記1つまたは複数のドライバ信号を生成するように構成されている。いくつかの実施形態は、電力供給システムを特徴とし、この電力供給システムは、請求項1の電力変換器に係る第1電力変換器と、前記第1電力変換器と並列に連結された第2電力変換器とを備える。前記電力供給システムは、電流平衡のために前記第1電力変換器の出力と前記第2電力変換器の出力とを調節するように構成された制御システムを特徴とし得る。

Some embodiments disclosed herein feature items comprising: the power converter of the previous paragraph; a first system configured to perform a physical action using power; an electrical system configured to control a first system, the power converter configured to provide power to one or both of the first system and the electrical system, the electrical system comprising: configured to control the first system based at least in part on radio signals received by the wireless communication system co-packaged with the embedded circuitry of the power converter. In some embodiments, the item is an Internet of Things device. Some embodiments feature a power delivery system comprising: That is, a plurality of power converters, each power converter responsive to the power converters of the previous paragraph, and a shared pulse width modulator (PWM) controller configured to generate a plurality of PWM signals. , the PWM controller is coupled to the drivers of the plurality of power converters to deliver the plurality of PWM signals to the corresponding drivers of the power converters, the drivers at least in part to the PWM signals; and generating the one or more driver signals based on. Some embodiments feature a power supply system comprising a first power converter according to the power converter of

ここに開示されたいくつかの実施形態は、以下を備える電力変換器を特徴とする。すなわち、下面および上面を有する下部プリント基板(PCB)部分と、下面および上面を有する上部プリント基板(PCB)部分とを有するプリント基板(PCB)と、入力電圧を受信するように構成された入力ポートと、前記入力電圧とは異なる出力電圧を提供するように構成された出力ポートと、前記下部PCB部分の前記上面と前記上部PCB部分の前記下面との間の埋め込み型回路であって、前記入力ポートに連結され、前記入力電圧を変化させるように構成された埋め込み型回路と、前記上部PCB部分を通って延びるビアと、前記上部PCB部分の前記上面に位置決めされたインダクタまたはキャパシタとを備え、前記1つまたは複数のビアは、前記インダクタまたはキャパシタおよび前記埋め込み型回路と電気的に連結され、前記インダクタまたはキャパシタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なる。本実施形態は、以下の任意の組み合わせを有し得る。すなわち、

・前記インダクタは、前記上部PCB部分の前記上面に位置決めされ、前記1つまたは複数のビアは、前記インダクタおよび前記埋め込み型回路と電気的に連結され、発生器前記インダクタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なり、前記埋め込み型回路は、1つまたは複数のドライバ信号を生成するように構成されたドライバと、前記1つまたは複数のドライバ信号により駆動されるように構成された1つまたは複数のスイッチとを備える。

・前記電力変換器は、直流-直流(DC-DC)変換装置である。

・前記電力変換器は、交流-直流(AC-DC)変換装置である。

・前記第1インダクタを通る変更電流が前記第2インダクタにおける変更電流を誘発するように構成された前記第1インダクタおよび前記第2インダクタを含む変圧器をさらに備える。

・前記埋め込み型回路は、交流電流(AC)入力電圧をパルスDC電圧に変更するように構成された整流回路を備える。

・前記パルスDC電圧をより安定したDC電圧に平滑化するように構成された平滑回路を備え、前記平滑回路は、前記上部PCB部分の上側の上部に位置決めされたキャパシタまたは前記インダクタを備える。

・前記整流回路は、1つまたは複数のスイッチを備える。

・前記整流回路は、ダイオードブリッジを備える。

Some embodiments disclosed herein feature power converters comprising: a printed circuit board (PCB) having a lower printed circuit board (PCB) portion having a bottom surface and a top surface and an upper printed circuit board (PCB) portion having a bottom surface and a top surface; and an input port configured to receive an input voltage. and an output port configured to provide an output voltage different from the input voltage, and embedded circuitry between the top surface of the lower PCB portion and the bottom surface of the upper PCB portion, wherein the input an embedded circuit coupled to a port and configured to vary the input voltage; a via extending through the upper PCB portion; an inductor or capacitor positioned on the top surface of the upper PCB portion; The one or more vias are electrically coupled to the inductor or capacitor and the embedded circuit, and the footprint of the inductor or capacitor at least partially overlaps the footprint of the embedded circuit. This embodiment may have any combination of the following. i.e.

- the inductor is positioned on the top surface of the upper PCB portion, the one or more vias are electrically coupled to the inductor and the embedded circuit, and the generator footprint of the inductor is embedded in the embedded circuit; a driver configured to generate one or more driver signals, the embedded circuit being configured to be driven by the one or more driver signals; and one or more switches.

- said power converter is a direct current to direct current (DC-DC) converter;

- said power converter is an alternating current to direct current (AC-DC) converter;

• further comprising a transformer comprising said first inductor and said second inductor configured such that a modified current through said first inductor induces a modified current in said second inductor;

- said implantable circuit comprises a rectifying circuit configured to change an alternating current (AC) input voltage into a pulsed DC voltage;

- a smoothing circuit configured to smooth the pulsed DC voltage to a more stable DC voltage, the smoothing circuit comprising the capacitor or the inductor positioned on top of the upper side of the upper PCB portion;

- the rectifier circuit comprises one or more switches;

- the rectifier circuit comprises a diode bridge;

ここに開示されたいくつかの実施形態は、直流-直流(DC-DC)電力変換器を特徴とし、この直流-直流電力変換器は、下面および上面を有する下部プリント基板(PCB)部分と、下面および上面を有する上部プリント基板(PCB)部分と、前記下部PCB部分の前記上面と前記上部PCB部分の前記下面との間の埋め込み型回路とを備え、前記埋め込み型回路は、PWM信号を生成するように構成されたパルス幅変調器(PWM)コントローラと、前記PWM信号を受信するように構成され、1つまたは複数のドライバ信号を生成するように構成されたドライバと、前記1つまたは複数のドライバ信号の少なくとも1つにより駆動されるように構成された第1スイッチと、前記1つまたは複数のドライバ信号の少なくとも1つにより駆動されるように構成された第2スイッチと、前記上部PCB部分を通って延びる1つまたは複数のビアと、前記上部PCB部分の前記上面に位置決めされたインダクタとを備え、前記1つまたは複数のビアは、前記インダクタおよび前記埋め込み型回路と電気的に連結され、発生器前記インダクタのフットプリントが前記埋め込み型回路のフットプリントに少なくとも部分的に重なり、前記埋め込み型回路と同じパッケージにおける無線通信システムと、前記無線通信は、前記PWMコントローラ、または、前記第1スイッチの少なくとも1つへ信号を提供して前記DC-DC変換器の出力に影響を及ぼすように構成されている。 Some embodiments disclosed herein feature a direct current-to-direct current (DC-DC) power converter comprising a lower printed circuit board (PCB) portion having a bottom surface and a top surface; an upper printed circuit board (PCB) portion having a bottom surface and a top surface; and embedded circuitry between the top surface of the bottom PCB portion and the bottom surface of the top PCB portion, the embedded circuitry generating a PWM signal. a pulse width modulator (PWM) controller configured to: a driver configured to receive the PWM signal and configured to generate one or more driver signals; and the one or more a first switch configured to be driven by at least one of the driver signals of the upper PCB; a second switch configured to be driven by at least one of the one or more driver signals; and an inductor positioned on the top surface of the upper PCB portion, the one or more vias electrically coupling the inductor and the embedded circuitry. a generator with a footprint of the inductor at least partially overlapping a footprint of the embedded circuit, and a wireless communication system in the same package as the embedded circuit; A switch is configured to provide a signal to at least one of the switches to affect the output of the DC-DC converter.

ここに開示されたいくつかの実施形態は、直流-直流(DC-DC)電力を特徴とし、この直流-直流電力は、プリント基板(PCB)の内側に位置決めされた集積回路を備え、前記集積回路は、ドライバからの第1信号により駆動されるように構成された第1窒化ガリウム(GaN)スイッチと、前記ドライバからの第2信号により駆動されるように構成された第2GaNスイッチと、前記集積回路のフットプリントと少なくとも部分的に重なるフットプリントを有するように前記集積回路に位置決めされたインダクタと、前記インダクタを前記GaNスイッチに電気的に連結するビアとを備える。いくつかの実施形態は以下を含んでいてもよく、すなわち、前記第1GaNスイッチが第1エンハンスト窒化ガリウム(eGaN)スイッチであり、前記第2GaNスイッチが第2eGaNスイッチである。 Some embodiments disclosed herein feature direct current to direct current (DC-DC) power comprising an integrated circuit positioned inside a printed circuit board (PCB), said integrated The circuit includes a first gallium nitride (GaN) switch configured to be driven by a first signal from a driver, a second GaN switch configured to be driven by a second signal from the driver, and the An inductor positioned on the integrated circuit to have a footprint that at least partially overlaps a footprint of the integrated circuit, and a via electrically coupling the inductor to the GaN switch. Some embodiments may include: the first GaN switch is a first enhanced gallium nitride (eGaN) switch and the second GaN switch is a second eGaN switch.

序論

直流(DC)-直流(DC-DC)変換器は、電子回路の一種である。DC-DC変換器は、第1電圧の入力電力を受信することができ、かつ、第2電圧の出力電力を提供することができる。DC-DC変換器としては、例えば、ブーストコンバータ(入力電圧よりも高い出力電圧を有することができる)、バックコンバータ(入力電圧よりも低い出力電圧を有することができる)、バック-ブーストコンバータ、および種々のその他のトポロジが挙げられる。

Introduction A direct current (DC) to direct current (DC-DC) converter is a type of electronic circuit. A DC-DC converter can receive input power at a first voltage and can provide output power at a second voltage. DC-DC converters include, for example, boost converters (which can have an output voltage higher than the input voltage), buck converters (which can have an output voltage lower than the input voltage), buck-boost converters, and Various other topologies are included.

DC-DC変換器は、非理想的な構成要素特性により影響を受けるものものある。これらは、ワイヤボンドおよびクワッド・フラット・リード端子なし(QFN)パッケージ、パワークワッド・フラット・リード端子なし(PQFN)パッケージ、デュアルフラット・リードなし(DFN)パッケージ、マイクロリードフレーム(MLF)パッケージなどのリードフレームパッケージなどの構成要素により引き起こされる寄生インダクタンス、寄生容量、および/または寄生抵抗を含み得る。さらに、DC-DC変換器の内部構成要素間の、例えば、ドライバからスイッチへの相互接続も寄生効果に寄与し得る。これらの寄生効果は、DC-DC変換器の効率および/または切替速度を制限し得る。パッケージは、DC-DC変換器レベルパッケージのことであってもよい。パッケージは、DC-DC変換器に含まれる1つまたは複数のICを封止してもよい。パッケージは、DC-DC変換器における構成要素のための支持および保護を提供してもよく、パッケージは、DC-DC変換器に接続するための電気接触部を提供してもよい。種々の実施形態において、パッケージは、パッケージ内に備えられた、および/または、外部からパッケージと連結された1つまたは複数のインダクタおよび/またはキャパシタを備えていてもよい。 Some DC-DC converters suffer from non-ideal component characteristics. These include wirebond and quad flat leadless (QFN) packages, power quad flat leadless (PQFN) packages, dual flat leadless (DFN) packages, and micro leadframe (MLF) packages. It may include parasitic inductance, parasitic capacitance, and/or parasitic resistance caused by components such as leadframe packages. Additionally, interconnections between internal components of the DC-DC converter, eg drivers to switches, can also contribute to parasitic effects. These parasitic effects can limit the efficiency and/or switching speed of DC-DC converters. A package may refer to a DC-DC converter level package. A package may encapsulate one or more ICs included in the DC-DC converter. The package may provide support and protection for the components in the DC-DC converter, and the package may provide electrical contacts for connecting to the DC-DC converter. In various embodiments, the package may include one or more inductors and/or capacitors provided within the package and/or externally coupled to the package.

この開示は、高集積ソリューションの例を含み、高集積ソリューションでは、DC-DC変換器は、より効率的に切替可能であり、比較的高い周波数で切替可能であり、および/または低減されたパッケージフットプリントを有する向上した性能を提供する。パルス幅変調器コントローラ、ドライバ、および/または1つまたは複数のエンハンストヒ化ガリウムスイッチ(エンハンスメントモードヒ化ガリウムスイッチおよびeGaN(登録商標)FETとしても知られている)などの多くのDC-DC構成要素を集積する集積回路チップがパッケージに含まれていてもよい。集積回路は、プリント基板に埋め込みされていてもよく、または、プリント基板間に埋め込みされていてもよい。パッケージは、パッケージフットプリントを低減するために垂直設計のインダクタおよび/またはキャパシタを含んでいてもよい。ある種の特徴は、比較的高い切替速度および/または比較的高い効率を達成することを阻止してしまう寄生効果を低減することができる。比較的高い切替速度を効率的に達成することにより、インダクタサイズは低減され得る。DC-DC変換器は、比較的高い周波数で動作することができ、より良好な過渡性能を提供することができ、比較的低いリップルを有すことができ、より少数のキャパシタを使用することができ、および/または全体のフットプリントを低減することができる。 This disclosure includes examples of highly integrated solutions, in which DC-DC converters can switch more efficiently, switch at relatively high frequencies, and/or have reduced packaging. Provides improved performance with a footprint. Many DC-DC configurations such as pulse width modulator controllers, drivers, and/or one or more enhanced gallium arsenide switches (also known as enhancement mode gallium arsenide switches and eGaN FETs) An integrated circuit chip that integrates the components may be included in the package. Integrated circuits may be embedded in or between printed circuit boards. The package may include inductors and/or capacitors in a vertical design to reduce the package footprint. Certain features can reduce parasitic effects that prevent achieving higher switching speeds and/or higher efficiencies. By efficiently achieving relatively high switching speeds, inductor size can be reduced. DC-DC converters can operate at relatively high frequencies, can provide better transient performance, can have relatively low ripple, and can use fewer capacitors. and/or the overall footprint can be reduced.

序論を提供するために、ある種の態様、利点、および新規の特徴を紹介した。必ずしも序論のこのような態様、利点、および新規の特徴の全てが任意の特定の実施形態に基づいて達成されるわけではないことが理解される。したがって、1つまたは複数の態様、利点、および新規の特徴は、ここに記載のその他の態様、利点、新規の特徴を必ずしも達成せずに達成されてもよい。全ての態様、利点、および新規の特徴が序論において開示されているわけではないことが分かる。 Certain aspects, advantages, and novel features have been introduced to provide an introduction. It is understood that not necessarily all such aspects, advantages and novel features of the introduction will be achieved in accordance with any particular embodiment. Accordingly, one or more aspects, advantages and novel features may be achieved without necessarily achieving other aspects, advantages and novel features described herein. It is understood that not all aspects, advantages and novel features are disclosed in the introduction.

例示的な概略図

図1は、チップ埋め込み型DC-DC変換器パッケージ100の例示的回路レベルの回路図を示す。回路図は、電力入力ポート101と、電源103と、入力キャパシタ105と、アースポート106と、アース107と、電圧出力ポート109と、出力キャパシタ111と、集積回路(IC)チップ113Aと、代替IC113Bと、ドライバ117と、パルス幅変調器(PWM)コントローラ119と、第1電気経路121と、第1スイッチ(例えば、第1エンハンスト窒化ガリウム(eGaN)スイッチ)123と、第2電気経路125と、第2スイッチ(例えば、第2eGaNスイッチ)127と、第3電気経路129と、インダクタ131と、ACバイパスキャパシタ133とを示す。破線135は、スイッチ123、127の代替の別個のパッケージングを示す。スイッチ123、127は、電力スイッチ、スイッチングFET、および/またはスイッチングトランジスタとも称される。この回路図は、電流源137、比較器139、故障論理および/または過電流保護回路141も示す。

Exemplary Schematic FIG. 1 shows an exemplary circuit-level schematic of a chip-embedded DC-

チップ埋め込み型DC-DC変換器パッケージ100は、電力入力ポート101を介して電源103と連結されてもよく、かつ、入力キャパシタ105を介してアース107とも連結されていてもよい。チップ埋め込み型DC-DC変換器パッケージ100は、入力キャパシタ111を介してアース107と連結されていてもよい電力入力ポート109も備えていてもよい。チップ埋め込み型DC-DC変換器パッケージ100は、アース107と連結されたアース基準ポート106も備えていてもよい。

Chip embedded DC-

チップ埋め込み型DC-DC変換器パッケージ100は、埋め込み型集積回路(IC)チップ113Aまたは113Bを含むプリント基板(PCB)を備えていてもよい。ICは、ドライバ117および/またはパルス幅変調器(PWM)コントローラ119を備えていてもよい。例えば、第1電気経路121は、ICを第1eGaNスイッチ123のゲートに連結する。第2電気経路125は、ICを第2eGaNスイッチ127のゲートに連結する。第3電気経路129は、ICを第1eGaNスイッチ123のソース、第2eGaNスイッチ127のドレイン、およびインダクタ131に連結する。インダクタ131は、電圧出力ポート109と連結されていてもよい。ACバイパスキャパシタ133は、第1eGaNスイッチ123のドレインから第2eGaNスイッチ127のソースへ連結されてAC信号をアース107に短絡してもよい。

Chip embedded DC-

図1は、ドライバ117およびPWMコントローラ119を、IC113Aの一部として示すが、種々の実施形態において、ICは、PWMコントローラ119またはドライバ117の一方を含んでいてもよく、一方、PWMコントローラ119およびドライバ117の他方は、個別にIC113Aに連結されている。いくつかの実施形態において、eGaNスイッチ123、127または一対のeGaNスイッチ123、127の1つは、各電気経路121、125、および/または129と共にIC113Aに集積されてもよい。IC113Aは、半導体であってもよい。IC113Aは、シリコン、ヒ化ガリウム、窒化ガリウム、eGaN、または他のIII-V族半導体であってもよい。したがって、任意の集積された構成要素も、IC113Aと同じまたは同様の材料で形成されていてもよい。スイッチ123、127、電気経路121、129、125、ドライバ、117、およびPWMコントローラ119も、IC113Aと同じまたは同様の材料で形成されていてもよい。

Although FIG. 1 shows

一対のスイッチ123、127は、モノリシックのeGaN電界効果トランジスタ(FET)であってもよい。いくつかの実施形態において、一対のスイッチ123、127は、個別の装置であってもよく、2つの独立型eGaNFETを含む。いくつかの実施形態において、スイッチ123、127は、金属酸化物電界効果トランジスタ(MOSFET)である。種々の他の複数のまたは種類のスイッチは、種々の他の実施形態において使用されてもよい。複数の実施形態はスイッチ123、127をeGaNスイッチとして説明しているが、他の適切な材料を、eGaNの代替としてまたはeGaNに加えて使用してもよい。

The pair of

いくつかの実施形態において、電気経路121、129、125は、銅ピラーなどのビア、配線、および/または低い寄生効果(例えば、低い寄生インダクタンス、低い寄生抵抗、および/または低い寄生容量)を有する他の電気経路によって実施されてもよい。ワイヤボンドは、比較的高い寄生効果(例えば、比較的高い寄生インダクタンス、比較的高い寄生抵抗、および/または比較的高い寄生容量)を有していてもよい。

In some embodiments, the

電力入力ポート101、アースポート106、および電圧出力ポート109を含むポートは、低い寄生効果(例えば、低い寄生インダクタンス、低い寄生抵抗、および/または低い寄生容量)を有するパッド、ピン、または他の電気導体として実施されていてもよい。ポートは、マザーボード、PCB、などの別の装置における配線と連結されるように設計されていてもよい。

Ports, including

多くの変形例が可能である。いくつかの実施形態において、バイパスキャパシタ133は省略されていてもよい。いくつかの実施形態は、異なるインダクタ、キャパシタ、磁石、および/または共振構造を特徴としてもよい。図1の例示的な回路図に示す種々の構成要素は、DC-DC変換器を形成するが、DC-DC変換器は、他の変形例を有していてもよい。ここに開示される教示は、他の変形例のDC-DC変換器に拡大し得ることが分かる。

Many variations are possible. In some embodiments,

例えば、DC-DC変換器110は、電力信号を電力入力ポート101を介して電源103から受信し得る。電力信号は、ノイズの在る交流電流(AC)信号構成要素をフィルタするために減結合キャパシタとして作用し得るシャント入力キャパシタ105を通してフィルタリングされ得る。電力信号は、一対のスイッチ123、127の第1スイッチ123のドレインに提供される。

For example, DC-DC converter 110 may receive a power signal from

ドライバ117は、電気経路121を介して第1制御信号を第1スイッチ(例えば、eGaNスイッチ)123のゲートへ提供する。また、ドライバは、電気経路125を介して第2制御信号を第2スイッチ(例えば、eGaNスイッチ)127のゲートへ提供する。制御信号を用いて、ドライバは、スイッチ123、127を交互にオンおよびオフすることができる。ドライバは、第1スイッチ123のオン/オフ状態は第2スイッチ127のオン/オフ状態の逆であるように信号を制御してもよい。制御信号のオン/オフデューティサイクルは、PWMコントローラ119によって設定されてもよい。PWMコントローラ119は、ドライバに提供されるPWM信号を介してパルス幅または周期を制御してもよい。

スイッチ123、127、IC113A(例えば、PWMコントローラ119および/またはドライバ117を含む)、および、インダクタ131は、非絶縁同期電力変換器または電力段の一部を形成するように配置されてもよい。ドライバ117が第1スイッチ123を駆動してオンにし、第2スイッチ127を駆動してオフにする場合、電力は、電源103からインダクタ131および/またはキャパシタ111などのエネルギー蓄積回路に提供されてもよく、電圧出力ポート109におけるDC出力電圧を上昇させる。ドライバ117が第1スイッチ123を駆動してオフし、第2スイッチ127を駆動してオンする一方で、エネルギー蓄積回路からの電力は、第2スイッチ127を通ってアース107へ流れてもよく、電圧出力ポート109におけるDC出力電圧を低減させる。したがって、スイッチ123、127のペア123は、迅速に切り替えされて電圧出力ポート109におけるDC出力電圧を制御する。インダクタ131およびキャパシタ111も、DC電圧を制御することを補助する共振フィルタとして作用する。

比較器139は、第2スイッチ127のドレインに連結された第1入力部を有する。比較器139は、第2スイッチ127のソースに連結された第2入力部を有する。したがって、比較器139は、第2スイッチ127の両端に連結されてもよい。いくつかの実施形態において、比較器139は、第1入力部としての反転端子を有していてもよい。比較器139の第1入力部は、電流源137とも連結されていてもよい。I2Cおよび/またはPMBUS(図2に関連してさらに説明される)は、電流源137の出力電流をトリムおよび/または調節するために使用されてもよい。したがって、過電流限度は、設定および/または調節され得る。比較器139の出力は、故障論理および過電流保護(OCP)回路141に提供されてもよい。

故障論理およびОCP回路141と共に比較器139は、スイッチ127がオンである場合にドレインソース抵抗Rdsを検知するように構成されている。Rdsにより引き起こされるスイッチ127の両端の電圧降下は、電流源137をトリムまたは調節することにより調節され得る基準値と比較される。比較器139の出力は、過電流条件が生じるとトリップする可能性がある。過電流保護回路141は、過電流条件が検出され故障モードになると、スイッチ123、127および/またはドライバをオフしてもよい。種々の実施形態において、ОCP回路は、スイッチ123、127のゲートに直接連結されて、スイッチをオフしてもよく、1つまたは複数の代替のエネルギー経路(図示せず)を短絡してエネルギーを放出してもよく、過電流条件に応答してPWMコントローラ119の出力に影響を及ぼし、および/または、過電流条件に応答してドライバ117の出力に影響を及ぼしてもよい。故障モードにおいて、システムは、スイッチ123、127および/またはドライバを短期間オンにすることにより回復を周期的に試みてもよく、過電流条件の検出を試みてもよく、過電流条件が依然として継続するならば、スイッチ123、127および/またはドライバ117をオフし、回復を再び試みる前に一定の期間待機する。

過電流条件は、インダクタ飽和の結果として起こり得る場合もある。インダクタ131などのインダクタは、長すぎる期間に多すぎる電流がインダクタへ提供されると、飽和し、その磁気特性を失う可能性がある。このような場合、インダクタのインダクタンスは、10%、30%、またはそれ以上低下する。完全に飽和したインダクタは、配線として効果的に作用することができ、回路において潜在的な短絡を作成する。飽和中にインダクタの実行抵抗は、降下する可能性があり、出力電流を仕様を上回って潜在的に危険なレベルまで上昇させる。回路のLC共振は、インダクタがエネルギーを効果的に格納しなくなる場合も影響される可能性があり、そのため、過電圧および/または電圧条件が起こり得る。

An overcurrent condition may also occur as a result of inductor saturation. An inductor, such as

インダクタ131は、ACリップルと同様に負荷電流(DC出力電流)を許容するように選択されてもよい。したがって、インダクタ131の飽和電流限度は、特定のDC出力電流プラス最大ACリップルを超過するように選択されてもよい。例えば、チップ埋め込み型DC-DC変換器が10AのDC電流と+/-5Aのリップルとを生成する場合、最大合計電流は15Aであり、インダクタ飽和限度は、15Aを上回ることになる.比較的高いインダクタンスを有するインダクタは、比較的高い飽和限度を有していてもよく、サイズが比較的大きくてもよい。

いくつかの設計では、過電流保護限度の決定およびインダクタサイズの決定が互いに独立して行われることがあり、一方または他方がオーバースペックになっている可能性がある。これは、例えば、製造者により作成されたDC-DC変換器に対して、第2者がインダクタを選択し連結する場合に起こり得る。いくつかの場合には、第2者は、十分な注意の範囲外でインダクタをオーバースペックにしてしまうことがあり、例えば、5AのAC電流、10AのDC電流、および100%のDC過電流を許容することで、このようなインダクタは、25A以上の飽和限度を有するように選択される。いくつかの場合には、第2者は、OCP限度を知ら無いことがあり、そのため、インダクタが飽和しないように、インダクタンスおよびサイズを比較的大きくするためにインダクタをオーバースペックにすることに頼る場合がある。または、いくつかの場合には、第2ユーザーは、高すぎる過電流保護限度に比較的小さいインダクタを使用することがあり、そのため、最小サイズと必要以上に大きいインダクタンスとを有するインダクタを使用する。いくつかの場合には、製造者は高すぎるまたは低すぎる過電流限度を設定することがある。ここに開示されたDC-DC変換器のいくつかの実施形態は、調整可能な過電流限度を有していてもよい。ここに開示されたDC-DC変換器のいくつかの実施形態は、過電流保護回路とインダクタとの双方を含んでいてもよく、過電流限度は、インダクタの少なくともサイズに基づいて決定され、過電流限度は、インダクタの飽和限度と等しい、および/または、飽和限度よりも低いように設定されてもよい。ここに開示されたDC-DC変換器のいくつかの実施形態は、過電流保護回路とインダクタとの双方を含んでいてもよく、インダクタのサイズは、少なくとも一部は過電流限度に基づいて、インダクタの飽和限度が過電流限度に等しいか、または、過電流限度を、50%以下、40%以下、30%以下、20%以下、10%以下、またはそれらの間の任意の値または、これらの値のいずれかにより規定される範囲等の狭い幅だけ上回るように選択される。ここに開示されたDC-DC変換器のいくつかの実施形態は、90%以下のDC過電流、75%以下のDC過電流、50%以下のDC過電流、50%以下のDC過電流、40%以下のDC過電流、30%以下のDC過電流、20%以下のDC過電流、10%以下のDC過電流、またはこれらの間の任意の値、または、これらの値の何れかにより規定される範囲など、予測される最大AC電流プラス予測されるDC電流の2倍よりも少ないように設定された過電流限度を有していてもよい。いくつかの実施形態において、単独の設計者が、構成要素を提供でき、インダクタおよびその飽和限度と同様に、OCP回路および限度の双方のために値を選択してもよい。したがって、いくつかの実施形態において、DC-DC変換器は、比較的低いフットプリント、比較的低いインダクタ直流抵抗、および上昇された効率を有しつつ、インダクタが飽和に達することなく動作し得る。 In some designs, overcurrent protection limit determination and inductor sizing may occur independently of each other, and one or the other may be overspecified. This can occur, for example, when a second party selects and connects an inductor to a DC-DC converter made by the manufacturer. In some cases, a second party may overspec the inductor outside of due diligence, e.g., 5A AC current, 10A DC current, and 100% DC overcurrent. By allowance, such inductors are selected to have a saturation limit of 25A or higher. In some cases, the second party may be unaware of the OCP limit and so resort to overspecifying the inductor to make it relatively large inductance and size so that the inductor does not saturate. There is Or, in some cases, a second user may use a relatively small inductor for overcurrent protection limits that are too high, and thus use an inductor with a minimum size and a larger inductance than necessary. In some cases, the manufacturer may set the overcurrent limit too high or too low. Some embodiments of the DC-DC converters disclosed herein may have adjustable overcurrent limits. Some embodiments of the DC-DC converter disclosed herein may include both an overcurrent protection circuit and an inductor, wherein the overcurrent limit is determined based at least on the size of the inductor and The current limit may be set equal to and/or lower than the saturation limit of the inductor. Some embodiments of the DC-DC converters disclosed herein may include both an overcurrent protection circuit and an inductor, the size of the inductor being based at least in part on the overcurrent limit: The saturation limit of the inductor is equal to the overcurrent limit, or the overcurrent limit is less than or equal to 50%, less than or equal to 40%, less than or equal to 30%, less than or equal to 20%, less than or equal to 10%, or any value in between, or is selected to be over a narrow band, such as the range defined by any of the values of . Some embodiments of the DC-DC converters disclosed herein have a DC overcurrent of 90% or less, a DC overcurrent of 75% or less, a DC overcurrent of 50% or less, a DC overcurrent of 50% or less, DC overcurrent of 40% or less, DC overcurrent of 30% or less, DC overcurrent of 20% or less, DC overcurrent of 10% or less, or any value in between, or any of these values It may have an overcurrent limit set at less than twice the expected maximum AC current plus the expected DC current, such as a specified range. In some embodiments, a single designer may provide the components and select values for both the OCP circuit and limits as well as the inductor and its saturation limit. Thus, in some embodiments, the DC-DC converter can operate without the inductor reaching saturation while having a relatively low footprint, relatively low inductor DC resistance, and increased efficiency.

パッケージング

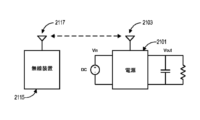

図2は、チップ埋め込み型DC-DC変換器パッケージ100の実施形態のパッケージレベルの回路図を示す。チップ埋め込み型DC-DC変換器パッケージは、入力ポート101、アースポート106、および出力ポート109を備えていてもよい。図1に関連して説明したように、電力入力ポート101は、電源103と、アースに連結された入力キャパシタ105などにより連結されていてもよい。電圧出力ポート109は、DC出力電圧をノード201に連結された負荷へ、アース107と連結された出力キャパシタ111などによって供給してもよい。イネーブルポート205は、信号を受信してDC-DC変換器をイネーブルするように構成されていてもよい。テストポート203は、装置の状態を確認するために使用されてもよい。いくつかの実施形態において、集積回路間(I2C)および/または電源管理バス(PMBUS)は、チップ埋め込み型DC-DC変換器パッケージ100へ/からの通信経路を提供する。

Packaging FIG. 2 shows a package level schematic diagram of an embodiment of an embedded chip DC-

パッケージ100のフットプリントは、DC-DC変換器の全ての構成要素を含んでいてもよい。いくつかの実施形態において、パッケージ100のフットプリントは、IC113Aまたは113Bおよびインダクタ131を、例えば、外部インダクタを追加せずにパッケージがDC-DC変換器として動作し得るように備える。いくつかの実施形態において、例えば、外部キャパシタを追加せずにこのようなパッケージがDC-DC変換器として動作し得るように、キャパシタ105、111、および/または133の少なくとも1つまたは複数もパッケージフットプリント内に含まれていてもよい。

The footprint of

いくつかの実施形態において、I2Cおよび/またはPMBUSは、I2Cおよび/またはPMBUSプロトコル通信を受信するために使用されて、チップ埋め込み型DC-DC変換器パッケージ100のオンまたはオフし、前記DC-DC電力変換器パッケージ100の低電力またはスリープモードの変更、前記DC-DC変換装置パッケージ100の電流設定についての情報の読み出し、前記DC-DC変換装置パッケージ100について診断および/または技術情報の読み出し、DC-DC変換器パッケージ100により提供される出力電圧の(例えば、図16および図17に関連して説明されるデジタル-アナログコントローラ「DAC」へ提供されるデジタル信号を変更することによる)変更または設定、ランプ波発生器(例えば、図17のランプ波発生器)の振幅または周波数などの特性のトリム、1つまたは複数の電流源(例えば、図18の電流源)のトリム、その他の機能、の1つまたは複数を行ってもよい。いくつかの実施形態において、PMBUSプロトコルは、I2C実装品の上に配線層として実施されている。

In some embodiments, I2C and/or PMBUS is used to receive I2C and/or PMBUS protocol communications to turn on or off the chip embedded DC-

集積およびチップ埋め込み型設計

DC-DC変換器は、比較的高く集積されていてもよく、比較的高い周波数で切り替わってもよく、他のDC-DC変換器と比べて改善された性能を提供することができる。いくつかの設計では、寄生効果防止は、仮にあったとしても、DC-DC変換器が比較的高い周波数(比較的高い切替速度)で効率的に動作することを防止することができる。DC-DC変換器の複数の設計は、寄生効果が低下された追加の設計と共にここで開示されている。

Integrated and On-Chip Design DC-DC converters may be relatively highly integrated and switched at relatively high frequencies, providing improved performance compared to other DC-DC converters. be able to. In some designs, parasitic effect prevention can prevent, if at all, a DC-DC converter from operating efficiently at relatively high frequencies (relatively high switching speeds). Multiple designs of DC-DC converters are disclosed herein along with additional designs with reduced parasitic effects.

いくつかのDC-DC変換器パッケージは、ワイヤボンドおよび/またはリードフレームパッケージを備える。一例1mil、1mmの長さのボンドワイヤは、0.7nHの寄生インダクタンス、0.08pFの寄生容量、および140mΩの寄生抵抗を有していてもよい。同様のまたはより高い寄生抵抗は、ワイヤボンドおよびクワッド・フラット・リード端子なし(QFN)パッケージ、パワークワッド・フラット・リード端子なし(PQFN)パッケージ、デュアルフラット・リードなし(DFN)パッケージ、マイクロリードフレーム(MLF)パッケージなどのリードフレームパッケージから生じ得る。ここに開示されるDC-DC変換器のいくつかの実施形態は、寄生効果を低減するために、ワイヤボンドおよび/またはリードフレームの使用をまとめて制限または回避することができる。ビア、配線、バンプ、および/またはバンプパッドは、代替として、パッケージの内側に使用されてもよい。 Some DC-DC converter packages include wirebond and/or leadframe packages. An example 1 mil, 1 mm long bond wire may have a parasitic inductance of 0.7 nH, a parasitic capacitance of 0.08 pF, and a parasitic resistance of 140 mΩ. Similar or higher parasitic resistances are wirebond and quad flat leadless (QFN) packages, power quad flat leadless (PQFN) packages, dual flat leadless (DFN) packages, micro leadframes (MLF) packages, such as leadframe packages. Some embodiments of the DC-DC converters disclosed herein may collectively limit or avoid the use of wirebonds and/or leadframes to reduce parasitic effects. Vias, traces, bumps and/or bump pads may alternatively be used inside the package.

いくつかのDC-DC変換器パッケージは、インダクタもキャパシタも備えていない。このようなパッケージは、ユーザーにキャパシタおよびインダクタのための特定値の選択の柔軟性を提供し、これらの構成要素の品質を制御する。DC-DC変換器パッケージ、インダクタ、およびキャパシタは、マザーボードまたは別個のPCBに表面実装されていてもよく、マザーボードまたは別個のPCBに亘るワイヤボンドまたは長い配線と一緒に(例えば、図7Aに示すように)連結されている。しかしながら、DC-DC変換器パッケージを外部インダクタまたはキャパシタと連結することは寄生効果を導入し得る。寄生効果は、インダクタと負荷との間に同様に導入される可能性がある。ここに開示されるDC-DC変換器のいくつかの実施形態は、インダクタまたはキャパシタをDC-DC変換器の他の構成要素と同じパッケージに集積することにより、インダクタまたはキャパシタに対する連結の寄生効果を低減することができる。ここに開示されたいくつかの実施形態において、インダクタまたはキャパシタを連結する電気経路は、ワイヤボンドの代わりにビアおよび/または配線と共に実施されてもよい。ここに開示されたいくつかの実施形態において、1つまたは複数のインダクタまたはキャパシタを連結する電気経路は、マザーボードまたは別個のPCB(例えば、図3および図7Bに示すように)における配線を含む代わりに、DC-DC変換器のPCBに位置するビアおよび/または配線を含んでいてもよい。ここに開示されたいくつかの実施形態において、PWMコントローラ、ドライバ、1つまたは複数ののインダクタ、1つまたは複数のキャパシタ、および/または1つまたは複数のスイッチの任意の組み合わせは、同じパッケージに含まれていてもよい。 Some DC-DC converter packages do not have inductors or capacitors. Such packages offer the user the flexibility of selecting specific values for the capacitors and inductors to control the quality of these components. The DC-DC converter package, inductors, and capacitors may be surface mounted to the motherboard or separate PCB, with wire bonds or long traces across the motherboard or separate PCB (e.g., as shown in FIG. 7A). to). However, coupling a DC-DC converter package with an external inductor or capacitor can introduce parasitic effects. Parasitic effects can similarly be introduced between the inductor and the load. Some embodiments of the DC-DC converter disclosed herein eliminate the parasitic effects of coupling to the inductor or capacitor by integrating the inductor or capacitor in the same package as other components of the DC-DC converter. can be reduced. In some embodiments disclosed herein, electrical paths connecting inductors or capacitors may be implemented with vias and/or traces instead of wire bonds. In some embodiments disclosed herein, electrical paths connecting one or more inductors or capacitors instead include traces on the motherboard or a separate PCB (eg, as shown in FIGS. 3 and 7B). may include vias and/or traces located on the PCB of the DC-DC converter. In some embodiments disclosed herein, any combination of the PWM controller, driver, one or more inductors, one or more capacitors, and/or one or more switches are in the same package. may be included.

いくつかの設計では、寄生効果は、構成要素の相互接続の結果として生じ得る。例えば、図1に関して、1つの集積回路113Aにおけるドライバ117は、スイッチ123、127を含む別個の構成要素電子135と連結し得る。集積回路113Aおよび別個の構成要素電子135は、PCBに含まれていてもよい。ドライバとスイッチ123、127との間の電気経路121、129、125は、PCB上の配線を用いて実施されてもよいが、PCB上の配線は、集積回路内の電気経路よりも高い寄生効果を有し得る。ここに開示されるDC-DC変換器のいくつかの実施形態は、スイッチ123、127、およびドライバ117をそれらの相互接続と共に同じIC113Bに集積することによって、ドライバとスイッチとの間の相互接続の寄生効果を低減し得る。ここに開示されたいくつかの実施形態において、PWMコントローラ、ドライバ、およびスイッチは、同じIC113Bに全て含まれている。いくつかの実施形態において、1つまたは複数のキャパシタも、同じIC113Bに含まれていてもよい。

In some designs, parasitic effects can result from component interconnections. For example, with respect to FIG. 1,

いくつかの設計では、MOSFETスイッチを使用することができる。しかしながら、MOSFETスイッチは、比較的高い切替速度ではあまり効率的でないこともある。ここに開示されたいくつかの実施形態において、スイッチ123、127は、eGaNスイッチであってもよい。eGaNスイッチは、MOSFETスイッチと比べてより効率的かつより高い速度で切替可能である。 In some designs, MOSFET switches may be used. However, MOSFET switches may not be very efficient at relatively high switching speeds. In some embodiments disclosed herein, switches 123, 127 may be eGaN switches. eGaN switches can switch more efficiently and at higher speeds than MOSFET switches.

ここに記載の技術の相乗効果が考えられる。寄生容量および/またはインダクタンス効果は、DC-DC変換器における最大切替速度を制限し得る。その理由は、寄生効果は、格納されることになる不都合なエネルギーを引き起こす可能性があり、エネルギーの充電および放電に影響し、それにより、DC電圧規制に影響するためである。寄生効果は、スイッチをゆっくりとオンまたはオフにすることもあり得る。いくつかの実施形態において、ここに記載の技術の組み合わせは、DC-DC変換器性能における十分な程度の改善により低減されることになる寄生効果を引き起こし得る。DC-DC変換器の構造、サイズ、性能に関連する追加の相乗効果は、詳細な開示の後の部分においても検討される。 Synergistic effects of the techniques described herein are possible. Parasitic capacitance and/or inductance effects can limit the maximum switching speed in DC-DC converters. The reason is that parasitic effects can cause unwanted energy to be stored, affecting energy charging and discharging and thereby affecting DC voltage regulation. Parasitic effects can also turn the switch on or off slowly. In some embodiments, the combination of techniques described herein can cause parasitic effects that will be reduced by a sufficient degree of improvement in DC-DC converter performance. Additional synergies related to DC-DC converter structure, size, and performance are also discussed later in the detailed disclosure.

いくつかの他のDC-DC変換器と比べ、ここに開示されたいくつかの実施形態は、約40本のボンドワイヤを除去し、このことは、約20mΩ分の寄生効果を低減することができ、10nH以上分のパッケージ漏れインダクタンス(寄生インダクタンス)も低減することができる。これらの寄生効果の除去は、高速切替(例えば、eGaNスイッチ)の利益を実現することを補助し得る。 Compared to some other DC-DC converters, some embodiments disclosed herein eliminate about 40 bond wires, which can reduce parasitic effects by about 20 mΩ. It is possible to reduce package leakage inductance (parasitic inductance) by 10 nH or more. Elimination of these parasitic effects can help realize the benefits of fast switching (eg, eGaN switches).

電力スイッチについての性能指数は、数式1に基づいて決定され得る。

ただし、FOMは性能指数、RDS(ON)は、スイッチのオン抵抗、およびQGはスイッチのゲート電荷である。ゲート電荷QGは、寄生インダクタンスによって影響され得る。寄生インダクタンスを低減することは、比較的低いFOM、通常は達成することが困難な設計改善という結果になり得る。

A figure of merit for the power switch may be determined based on

where FOM is the figure of merit, RDS (ON) is the on-resistance of the switch, and QG is the gate charge of the switch. Gate charge QG can be affected by parasitic inductance. Reducing parasitic inductance can result in a relatively low FOM, a design improvement that is typically difficult to achieve.

全体の利点の全てではないがいくつかは、十分な寄生効果低減と構成要素選択の同時の組み合わせによってのみ実現され得ることがさらに分かる。例えば、寄生効果を低減することのいくつかの利点は、MOSFETを使用する場合、いくつかの条件下では実現されない場合もある。これは、切替速度をより高くできるように十分なレベルまで寄生効果を低減できるかもしれないが、MOSFET設計がより高い速度での効率的な切替を許容しない場合もあるためである。同様に、DC-DC変換器におけるeGaNスイッチ(または他のより高速かつ典型的にはより高コストのスイッチ)の完全な切替性能が寄生効果によって制限される可能性がある。完全な切替性能は、1MHz以上、3MHz以上、4MHz以上、5MHz以上、7MHz以上、10MHz以上などのメガヘルツ範囲における比較的高い周波数でより効率的に切り替えることを含んでいてもよい。いくつかの例では、15MHzまでの切替速度を達成でき、これらの特定された範囲外の切替速度は、いくつかの実施において使用され得る。 It is further seen that some, but not all, of the overall benefits can only be realized through the simultaneous combination of sufficient parasitic effect reduction and component selection. For example, some benefits of reducing parasitic effects may not be realized under some conditions when using MOSFETs. This is because although the parasitic effects may be reduced to a sufficient level to allow higher switching speeds, the MOSFET design may not allow for efficient switching at higher speeds. Similarly, parasitic effects can limit the perfect switching performance of eGaN switches (or other faster and typically more costly switches) in DC-DC converters. Perfect switching performance may include more efficient switching at relatively high frequencies in the megahertz range, such as 1 MHz or higher, 3 MHz or higher, 4 MHz or higher, 5 MHz or higher, 7 MHz or higher, 10 MHz or higher. In some examples, switching speeds up to 15 MHz can be achieved, and switching speeds outside these specified ranges may be used in some implementations.

したがって、寄生効果を低減するために限定された技術をテストするエンジニアは、インパクトのあるレベルへ寄生効果を低下させない可能性がある。寄生低減技術の組み合わせをテストするエンジニアは、切替速度がMOSFETにより限定される場合、より顕著なゲインを達成しない場合がある。DC-DC変換器における寄生効果に最初に気付かず、対処せずにeGaNスイッチをテストするエンジニアは、eGaNスイッチを使用する切替速度利点に気付かない場合があり、特に、eGaNスイッチはMOSFETスイッチよりもコストがかかるからである。さらに、切替速度を、他の変数に応じて、特に、1、2、3、5、7または10MHz以上に上昇することは、効率がより高い切替速度で低減する傾向があるという従来の知識に反する。 Therefore, engineers testing limited techniques to reduce parasitic effects may not reduce parasitic effects to impactful levels. Engineers testing combinations of parasitic reduction techniques may not achieve more significant gains when switching speed is limited by the MOSFET. Engineers who test eGaN switches without first noticing and addressing parasitic effects in DC-DC converters may be unaware of the switching speed advantage of using eGaN switches, especially eGaN switches over MOSFET switches. This is because it is costly. Moreover, as the switching speed is increased above 1, 2, 3, 5, 7 or 10 MHz, depending on other variables, the conventional wisdom is that efficiency tends to decrease at higher switching speeds. oppose.

詳細な開示の集積およびチップ埋め込み型設計の項目は、寄生効果を低減および/または比較的高速の切替速度の達成のための種々の実施形態を検討する。いくつかの実施形態は、特徴の組み合わせを含むが、全ての特徴よりも少ない特徴を有する実施形態は、それ自体の権利において理解される。 The Integrated and Chip Embedded Design section of the detailed disclosure discusses various embodiments for reducing parasitic effects and/or achieving relatively fast switching speeds. Some embodiments include combinations of features, but embodiments with less than all features are understood in their own right.

物理的構造図

図3は、例示的チップ埋め込み型DC-DC変換器の断面図300を示す。図300は、絶縁体301、コンダクタ(例えば、金属)303、バンプまたはパッド304、コンダクタマイクロビア305、第1PCB層307、導電性メッキ309、PCBコア311、配線313、埋め込み型ICチップ315、第2PCB層317、インダクタ321、およびキャパシタ323を備える。

Physical Structural Diagram FIG. 3 shows a

埋め込み型ICチップ315は、PCBコア311に埋め込みされていてもよい。種々の実施形態において、ICチップ315はPCBの一層、または、PCBの2以上の層の間、または、下部PCBと上部PCBとの間に埋め込みされていてもよい。埋め込み型ICチップ315は、例えば図1に関連してここで検討したように、PWMコントローラ、ドライバ、および/または1つまたは複数のスイッチ(例えば、eGaNスイッチ)を備えていてもよい。埋め込み型ICチップ315は、DC-DC変換器構造において、複数のビア305および/または配線313を介してインダクタ321およびキャパシタ323と連結されていてもよい。

Embedded

絶縁体301は、例えば、半田マスク、モールド、アンダーフィルなどを備えていてもよい。PCBの層307、317は、PCB基板、積層、樹脂、エポキシ、絶縁体などであってもよい。図3に示す図300において、PCBコア311はフィラー、積層、絶縁モールド化合物、または基板などであってもよい。導体(例えば、金属)303、ビア305、および配線313は、銅、アルミニウム、金などの様々な種類の金属または導電性材料であってもよい。ビアは、メッキされたビアとして示されているが、いくつかの実施形態は、ピラーまたは他のピラーを使用してもよい。種々の実施形態は、金属の種類および層を増減して使用し得る。

いくつかの実施形態において、ICチップ315は、フリップチップ実装されていてもよい。種々の実施形態において、ICチップ315は、ICチップ315上の接続がインダクタ321および/またはキャパシタ323に対向し得るように、または、インダクタ321および/またはキャパシタ323の反対側を向くように、フェイスアップまたはフェイスダウンであってもよい。ICチップ315上の接続が、インダクタ321および/またはキャパシタ323の反対側を向く場合、インダクタ321および/またはキャパシタ323は、ビア305および/または配線313によってICチップ315の遠位端と連結されてもよい。

In some embodiments,

図3は、ドライバおよびスイッチを含み得る単一のICチップ315を示すが、いくつかの実施形態において、スイッチ(例えば、モノリシックのeGaNスイッチ)はICチップ315とは別個のPCBにチップ埋め込まれたチップであってもよく、チップ埋め込み型ICチップ315におけるドライバによって相互接続されていてもよい。ビア、パッド、および/または配線は、DC-DC変換器の種々の構成要素を連結することができ、2つのダイはフェイスダウンまたはフェイスアップであってもよい。インダクタまたは他の磁気は、最上層内または最上層上に配置されてもよく、バックコンバータにおける完全なハーフブリッジ組み合わせ、または、ハーフブリッジ回路図を用いる任意の他の構成を作成してもよい。

Although FIG. 3 shows a

ICチップ315は、ビア305および配線313の双方によってインダクタ321と連結されたものを示したが、いくつかの実施形態において、ICチップ315は、ビア305または配線313のどちらかでインダクタ321および/またはキャパシタ323と連結されていてもよい。種々の実施形態において、PCB組立品は、図3に示すよりも多くの、または、よりも少ないPCB層を有していてもよく、ICチップ315は、単一層に、または、複数層のPCB間に埋め込みされていてもよい。種々の実施形態において、層307、317は、1つのPCBまたは別個の複数のPCBの複数の層であってもよい。PCBの底に露出した金属303は、入力電源、アース、および/または負荷と連結するための入力/出力パッドを提供し得る。

Although

インダクタ321および/またはキャパシタ323の一部は、ICチップ315に積層されていてもよい。いくつかの実施形態において、インダクタ321および/またはキャパシタ323は、ICチップ315に全体的に積層されていてもよい。インダクタ321およびICチップ315は、DC-DC変換器パッケージにおいて大きい方の構成要素になる傾向がある。いくつかの実施形態において、インダクタ321またはICチップ315の小さい方は、インダクタ321またはICチップ315の大きい方のフットプリント範囲内に積層されてもよい。スイッチおよびドライバの双方を含む単一のICチップ315が図3に示されているが、種々の実施形態において、インダクタ321および/またはキャパシタ323は、単一のICチップ315とは別個の構成要素に少なくとも部分的に重なってもよい。例えば、インダクタ321は、1つまたは複数のスイッチ、PWMコントローラ、および/またはドライバなどに重なっていてもよい。

A portion of

インダクタ321の位置は、DC-DC変換器のより良好な熱性能に寄与し得る。インダクタ321を最上部に設けることにより、インダクタ321は、周囲空気により冷却され得る。最上部に実装されたインダクタ321により、インダクタ321について種々のサイズまたは形状も(例えば、インダクタ321がPCBの寸法により制約されないように)使用できるようになる。

The position of

図4Aは、積層型インダクタ321を有する例示的チップ埋め込み型DC-DC変換器の斜視図400を示す。インダクタ321は、PCBの層317、307間のコア311に埋め込まれたICチップ(不可視)上に積層されてもよい。インダクタ321は、少なくとも部分的に、金属接点401を介してPCBと連結されてもよい。いくつかの実施形態において、1つまたは複数のキャパシタ323(不可視)は、PBC層317と連結されていてもよい。

FIG. 4A shows a

図4Bは、積層型インダクタ321を有する例示的なレンダリングされたチップ埋め込み型DC-DC変換器の逆斜視図425を示す。インダクタ321は、PCBの層317、307間に埋め込まれたICチップ(不可視)上に積層されてもよい。インダクタ321は、少なくとも部分的に、金属配線313を介してPCBと連結されてもよい。1つまたは複数のキャパシタ323A、323Bは、PBC層317と連結されていてもよい。1つまたは複数のキャパシタ323A、323Bは、配線313によってインダクタ321とも連結されていてもよい。

FIG. 4B shows a

いくつかの実施形態において、切替周波数が上昇するにつれて、インダクタが小さくなり得る。さらに、いくつかの材料および薄膜技術などの技術は、インダクタのサイズも低減することができる。したがって、いくつかの実施形態において、インダクタは、例えばICの上方に、または、ICに並行してPCBに埋め込みされていてもよい。このような構造はさらなる集積を提供し、入力および出力キャパシタなどの他の周辺の構成要素のために、PCB実装表面上などの利用可能な空間量を増大させる。 In some embodiments, the inductor may become smaller as the switching frequency increases. Additionally, some materials and techniques such as thin film technology can also reduce the size of the inductor. Thus, in some embodiments, the inductor may be embedded in the PCB, for example above or parallel to the IC. Such structures provide additional integration and increase the amount of available space, such as on the PCB mounting surface, for other peripheral components such as input and output capacitors.