JP7206589B2 - Manufacturing method of glass circuit board with built-in capacitor - Google Patents

Manufacturing method of glass circuit board with built-in capacitor Download PDFInfo

- Publication number

- JP7206589B2 JP7206589B2 JP2017246227A JP2017246227A JP7206589B2 JP 7206589 B2 JP7206589 B2 JP 7206589B2 JP 2017246227 A JP2017246227 A JP 2017246227A JP 2017246227 A JP2017246227 A JP 2017246227A JP 7206589 B2 JP7206589 B2 JP 7206589B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- capacitor

- forming

- glass

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Parts Printed On Printed Circuit Boards (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Description

本発明は、キャパシタ内蔵ガラス回路基板及びキャパシタ内蔵ガラス回路基板の製造方法に係り、特にキャパシタの高信頼性及び容量の安定化を実現できるものに関する。 The present invention relates to a glass circuit board with built-in capacitors and a method of manufacturing a glass circuit board with built-in capacitors, and more particularly to a method capable of realizing high reliability and stable capacitance of capacitors.

電子機器の高機能化及び小型化に伴って、半導体装置を構成する配線基板の高密度化の要求が高まっている。その中で、回路配線の微細化に合わせて、抵抗、キャパシタ、インダクタ等の受動部品についても小型化が求められている。しかしながら、これら受動部品の小型化と基板表面への高密度実装のみではさらなる小型化には限界がある。そこで、実装基板に受動素子を内蔵化する技術が提案されている(例えば、特許文献1参照。)。この技術では、受動素子を印刷や真空成膜法等で形成することで多層基板内に内蔵することで小型化が可能となる。さらに多層基板内に形成することで、配線長を短くすることが可能となり、高周波ノイズを軽減することも可能である。 2. Description of the Related Art As electronic devices become more sophisticated and smaller, there is an increasing demand for high-density wiring substrates that constitute semiconductor devices. Among them, passive components such as resistors, capacitors, and inductors are also required to be miniaturized in accordance with the miniaturization of circuit wiring. However, there is a limit to further miniaturization only with miniaturization of these passive components and high-density mounting on the substrate surface. Therefore, a technology has been proposed for embedding a passive element in a mounting substrate (see, for example, Patent Document 1). In this technology, miniaturization is possible by embedding passive elements in a multi-layer substrate by forming them by printing, vacuum deposition, or the like. Furthermore, by forming it in a multilayer substrate, it becomes possible to shorten the wiring length, and it is also possible to reduce high-frequency noise.

一方、配線基板の材料としては、一般的にガラスエポキシ樹脂に代表される有機材料が用いられている。近年、ガラス材料への穴あけ技術の進歩により、例えば、300μm厚のガラス基板に対して100μm以下の小径スルーホールを150μmピッチ以下で形成することが可能である。このことからガラス材料を用いた電子回路基板が注目されている。ガラス材料をコアに用いた回路基板(以下、「ガラス回路基板」と称する)は、ガラスの線熱膨張係数(CTE)が2ppm~8ppmと小さく、シリコンチップと整合するため実装信頼性が高く、さらに平坦性に優れるため高精度な実装が可能になる。また、平坦性に優れるために微細配線形成性、高速伝送性にも優れている。 On the other hand, as the material of the wiring board, an organic material, typically glass epoxy resin, is generally used. In recent years, advances in drilling technology for glass materials have made it possible, for example, to form small-diameter through holes of 100 μm or less in a 300 μm-thick glass substrate at a pitch of 150 μm or less. For this reason, an electronic circuit board using a glass material has attracted attention. A circuit board using a glass material for the core (hereinafter referred to as a "glass circuit board") has a small linear thermal expansion coefficient (CTE) of 2 ppm to 8 ppm and is matched with a silicon chip, so mounting reliability is high. Furthermore, since the flatness is excellent, highly accurate mounting becomes possible. In addition, due to its excellent flatness, it is also excellent in fine wiring formability and high-speed transmission.

さらにガラスの透明性、化学的安定性、高弾性、かつ、安価である特徴を生かした電子回路基板への応用が研究されており、半導体装置用インターポーザ、撮像素子用回路基板、通信機器用のLC分波器(デュプレクサ)等の製品化が期待されている(例えば、特許文献2参照。)。これらガラス基板をコアとする電子回路にはデカップリングコンデンサやLC回路等を形成する必要性があることから、キャパシタを内蔵する要求が高まっている。キャパシタを内蔵させるためには、誘電体を下部電極層と上部電極層で挟持するMIM構造(Metal insulator Metal)を有する薄膜キャパシタを形成することが考えられる。 Furthermore, application to electronic circuit substrates that take advantage of the transparency, chemical stability, high elasticity, and low cost of glass is being researched. Commercialization of an LC branching filter (duplexer) and the like is expected (see, for example, Patent Document 2). Since it is necessary to form decoupling capacitors, LC circuits, and the like in electronic circuits having glass substrates as cores, there is an increasing demand for built-in capacitors. In order to incorporate a capacitor, it is conceivable to form a thin film capacitor having an MIM structure (Metal Insulator Metal) in which a dielectric is sandwiched between a lower electrode layer and an upper electrode layer.

上述したガラス回路基板にキャパシタを内蔵しようとすると、次のような問題があった。すなわち、キャパシタ部の下部電極層表面の粗さに応じてキャパシタの容量が変化するという問題があった。特に下部電極層の表面が粗い場合は、その凹凸の影響を受けてキャパシタのショート誘発や、キャパシタ容量の大きな変化を引き起こす。また、基板面内での下部電極層表面の粗さのバラつきは、キャパシタ容量のバラつきに直結するため、基板面内で均一な下部電極層表面が必要であり、製造工程において高い精度で加工制御する必要がある。 When trying to incorporate a capacitor into the glass circuit board described above, there are the following problems. That is, there is a problem that the capacitance of the capacitor changes depending on the roughness of the surface of the lower electrode layer of the capacitor portion. In particular, if the surface of the lower electrode layer is rough, the unevenness of the surface may induce a short circuit of the capacitor or cause a large change in the capacitance of the capacitor. In addition, variations in the surface roughness of the lower electrode layer within the substrate surface are directly linked to variations in the capacitance of the capacitor. There is a need to.

そこで本発明は、上述した問題を解決するためになされたものであり、電子回路、電子機器の小型化薄型化の際に必要となる、高信頼性及び容量の安定化を実現できるキャパシタ内蔵ガラス回路基板及びこのキャパシタ内蔵ガラス基板を歩留まり良く製造できるキャパシタ内蔵ガラス基板製造方法と提供することを課題とする。 Therefore, the present invention has been made to solve the above-mentioned problems, and is a capacitor-embedded glass that can realize high reliability and stable capacitance, which are necessary for miniaturization and thinning of electronic circuits and electronic devices. It is an object of the present invention to provide a capacitor-embedded glass substrate manufacturing method capable of manufacturing a circuit board and the capacitor-embedded glass substrate with a high yield.

本発明の請求項1に記載の発明は、ガラス基板の上に、下部電極を有する導体回路層を形成する工程と、前記導体回路層の上に、前記導体回路層の上面が部分的に露出するように保護層を形成する工程と、前記保護層をマスクとして用いたエッチングにより、前記導体回路層の上面に、第1上面領域と、前記第1上面領域から突き出た凸部の上面としての第2上面領域とを形成する工程であって、前記第2上面領域は前記下部電極の上面である工程と、前記保護層を剥離する工程と、前記下部電極上に誘電体層を形成する工程と、前記誘電体層上に上部電極を形成する工程と、を含む。

本発明の請求項2に記載の発明は、前記導体回路層を形成する前に、前記ガラス基板上に下部金属層を形成する工程をさらに含む。

本発明の請求項3に記載の発明は、前記導体回路層は、銅、ニッケル、クロム、パラジウム、金、ロジウム、及びイリジウムからなる群より選択される何れかの材料からなる。

The invention according to claim 1 of the present invention comprises a step of forming a conductor circuit layer having a lower electrode on a glass substrate; and etching using the protective layer as a mask to form, on the upper surface of the conductor circuit layer, a first upper surface region and a projection as an upper surface protruding from the first upper surface region. forming a second top surface region, wherein the second top surface region is the top surface of the bottom electrode; stripping the protective layer; and forming a dielectric layer on the bottom electrode. and forming a top electrode on the dielectric layer.

The invention according to claim 2 of the present invention further includes the step of forming a lower metal layer on the glass substrate before forming the conductor circuit layer.

According to a third aspect of the present invention, the conductor circuit layer is made of any material selected from the group consisting of copper, nickel, chromium, palladium, gold, rhodium and iridium.

本発明の請求項4に記載の発明は、前記保護層は、前記ガラス基板と前記導体回路層との積層方向の平面視において前記誘電体層及び前記上部電極の形成領域の外側まで形成される。 According to a fourth aspect of the present invention, the protective layer extends to the outside of the regions where the dielectric layer and the upper electrode are formed in a plan view in the lamination direction of the glass substrate and the conductor circuit layer. .

本発明の請求項5に記載の発明は、前記上部電極を、前記ガラス基板と前記導体回路層との積層方向の平面視において前記第2上面領域の内側に形成する。 According to the fifth aspect of the present invention, the upper electrode is formed inside the second upper surface region when viewed from above in the lamination direction of the glass substrate and the conductor circuit layer.

本発明の請求項6に記載の発明は、前記上部電極を形成する前に、前記誘電体層の上に、前記第2上面領域と前記第1上面領域との高さの差と比較してより大きい厚さを有する上部金属層を形成する工程を更に含む。 According to the sixth aspect of the present invention, before forming the upper electrode, on the dielectric layer, the height difference between the second top surface region and the first top surface region is compared with Further comprising forming a top metal layer having a greater thickness.

本発明の請求項7に記載の発明は、前記導体回路層を形成する前に、前記ガラス基板に表裏面を貫通する貫通孔を形成する工程を更に含む。 The invention according to claim 7 of the present invention further includes the step of forming a through-hole penetrating through the front and rear surfaces of the glass substrate before forming the conductor circuit layer.

本発明によれば、下部電極の表面粗さの均一化を行うことで、ショート誘発や、キャパシタ容量の大きな変化を防止し、高信頼性及び容量の安定化を実現することができると共に、上述した表面粗さの均一化を容易な加工制御によって行うことが可能となる。 According to the present invention, by uniformizing the surface roughness of the lower electrode, it is possible to prevent the induction of a short circuit and a large change in the capacitance of the capacitor, thereby realizing high reliability and stabilization of the capacitance. It becomes possible to make the surface roughness uniform by easy processing control.

以下、図に基づいて、本発明の実施形態について説明する。 An embodiment of the present invention will be described below with reference to the drawings.

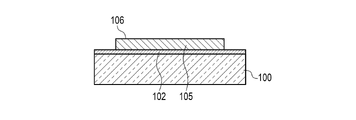

図1は本発明の第1の実施の形態に係るキャパシタ内蔵ガラス回路基板10の要部を示す縦断面図である。なお、図3F中Pはキャパシタ形成部を示している。

FIG. 1 is a vertical cross-sectional view showing a main part of a capacitor built-in

図1に示すようにキャパシタ内蔵ガラス回路基板10は、ガラス基板100を有している。

As shown in FIG. 1, the capacitor built-in

ガラス基板100には表裏面を貫通する貫通孔101が形成されており、この貫通孔101内壁面及びガラス基板100の両面にわたってシード金属層102が形成されている。シード金属層102には、導体回路層104が形成されている。導体回路層104の一部はキャパシタ109を構成する下部電極105となる。

A through-

キャパシタ109の導体回路層104の上面(表面)106は、導体回路層の上面106a領域と、下部電極105の上面(凸部の表面)106b領域とが形成されている(図4D参照)。

An upper surface (surface) 106 of the

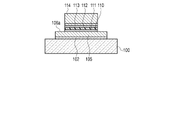

キャパシタ109は、図1に示すように基本的に下部電極と誘電体層と上部電極とから構成されるが、さらに密着層、またはシード層を設けてもよい。従って、一つの形態としては、図4Iに示すように、下部電極105上に下部密着層110、誘電体層111、上部密着層112、シード金属層113を順次設けられている。シード金属層113の上部には上部電極114が形成されている。

The

また、ガラス基板の両面に絶縁樹脂層131を設ける。絶縁樹脂層131には、ビアホール132、積層導体回路層133が形成される。さらに必要に応じて第2の絶縁樹脂層と第2の導体回路層が形成され積層される。最外部に外部接続端子134が形成されている。外部接続端子134の所定部位にははんだボール135が形成されている。

Insulating

次に、各要素の材質、形状等について詳細に説明する。ガラス基板100は、光透過性を有する透明のガラス材料である。ガラスの成分またはガラスに含有される各成分の配合比率、更にガラスの製造方法は特に限定されない。例えば、ガラスとしては、無アルカリガラス、アルカリガラス、ホウ珪酸ガラス、石英ガラス、サファイアガラス、感光性ガラス等が挙げられるが、ケイ酸塩を主成分とするいずれのガラス材料を用いてもよい。さらに、その他のいわゆるガラス材料を用いても良い。ただし、本実施形態にかかる半導体用途では、無アルカリガラスを用いるのが望ましい。また、ガラス基板100の厚さは1mm以下が好ましいが、ガラスの貫通孔形成プロセスの容易性や製造時のハンドリング性を考慮して、より好ましくは0.1mm以上0.8mm以下である。

Next, the material, shape, etc. of each element will be described in detail. The

ガラス基板100の製造方法としては、フロート法、ダウンドロー法、フュージョン法、アップドロー法、ロールアウト法等が挙げられるが、いずれの方法によって作製されたガラス材料を用いてもよく、本実施形態のものに限定されない。ガラスの線膨張係数は-1ppm/K以上15.0ppm/K以下であることが望ましい。その理由として、-1ppm/K以下である場合、ガラス材料自体を選定することが困難となり安価に作成できない。一方、15.0ppm/K以上である場合、他層との熱膨張係数の差異が大きく信頼性が低下する。また、本実施形態の基板にシリコンチップを実装する場合は、シリコンチップとの接続信頼性が低下する。なお、ガラスの線膨張係数は、より好ましくは0.5ppm/K以上8.0ppm/K以下、更に好ましくは1.0ppm/K以上4.0ppm/K以下であることが望ましい。

Examples of the method for manufacturing the

また、ガラス基板100には予め反射防止膜またはIRカットフィルタ等の機能膜が形成されていてもよい。また、強度付与、帯電防止付与、着色、テクスチャー制御等の機能が付与されても良い。これら機能膜の例として、強度付与にはハードコート膜、帯電防止付与については、帯電防止膜、着色については、光学フィルタ膜、テクスチャー制御においては、アンチグレア、光散乱膜等が挙げられるが、この限りではない。これら機能膜の形成方法としては、蒸着、スパッタリング法、ウエット方式等の成膜技術が用いられる。

Further, a functional film such as an antireflection film or an IR cut filter may be formed in advance on the

シード金属層102はセミアディティブ工法における配線形成用において、電解めっきの給電層として作用する。ガラス基板100直上及び貫通孔101内壁に設けられるシード金属層102は、例えば、スパッタ法、またはCVD法によって形成され、例えば、Cu、Ni、Al、Ti、Cr、Mo、W、Ta、Au、Ir、Ru、Pd、Pt、AlSi、AlSiCu、AlCu、NiFe、ITO、IZO、AZO、ZnO、PZT、TiN、Cu3N4、Cu合金単体もしくは複数組み合わせたものが用いられている。さらにその上に無電解めっき層(無電解銅めっき、無電解ニッケルめっき等)が形成されている。

The

本実施形態では、電気特性、製造の容易性の観点及びコスト面を考慮して、ガラスと密着が良好なチタン層、続いて銅層を順次スパッタリング法で形成する。ガラス基板上の回路形成用のチタンと銅層の合計の膜厚は、セミアディティブ法による微細な配線形成に有利なことから1μm以下とするのが望ましい。1μmより厚い場合ピッチ30μm以下の微細配線形成が困難である。 In the present embodiment, a titanium layer, which has good adhesion to glass, and then a copper layer are sequentially formed by a sputtering method in consideration of electrical properties, ease of manufacture, and cost. The total film thickness of the circuit-forming titanium and copper layers on the glass substrate is preferably 1 μm or less because it is advantageous for fine wiring formation by the semi-additive method. If the thickness is more than 1 μm, it is difficult to form fine wiring with a pitch of 30 μm or less.

導体回路層104は、電解銅めっきであることが簡便で安価で、電気伝導性が良好であることから望ましいが、電解銅めっきの他、電解ニッケルめっき、電解クロムめっき、電解Pdめっき、電解金めっき、電解ロジウムめっき、電解イリジウムめっき等であっても良い。

The

キャパシタ109において、下部密着層110は、下部電極105と誘電体層111との密着性を向上させる機能を有し、上部密着層112は、誘電体層111とシード金属層113との密着性を向上させる機能を有している。下部密着層110及び上部密着層112の材質は、例えばTiである。この他、例えばCu、Ni、Al、Cr、Mo、W、Ta、Au、Ir、Ru、Pd、Pt、AlSi、AlSiCu、AlCu、NiFe、Cu合金単体もしくは複数組み合わせたものを用いてもよい。Tiは、密着性、電気伝導性、製造の容易性の観点及びコスト面から優れている。

In the

下部密着層110及び上部密着層112の厚さは例えば、10nm以上1μm以下であることが望ましい。10nm未満である場合、密着強度が不十分となる虞がある。1μmを超える場合、後述する製造工程において、成膜時間がかかりすぎて量産性に欠けるばかりでなく、不要部分を除去する工程でさらに時間がかかる虞がある。下部密着層110及び上部密着層112の厚さは、より好ましくは10nm以上、500nm以下であることが望ましい。下部密着層110及び上部密着層112はそれぞれ厚さが異なってもよいが、構造上単純になるため同厚であることが望ましい。また、下部電極105と誘電体層111との密着が十分である場合は、下部密着層110はなくてもかまわない。誘電体層111とシード金属層113との密着が十分である場合は、上部密着層112はなくてもかまわない。

It is desirable that the thickness of the

誘電体層111は、絶縁性、比誘電率の観点からアルミナ、シリカ、シリコンナイトライド、タンタルオキサイド、酸化チタン、チタン酸カルシウム、チタン酸バリウム、チタン酸ストロンチウムから選択することができる。誘電体層111の厚さは、10nm以上5μm以下であることが望ましい。誘電体層111の厚さが、10nm以下である場合、絶縁性を保つことができずにキャパシタとしての機能が発現しない。誘電体層111の厚さが、5μm以上の場合、成膜時間がかかりすぎて量産性に欠けるばかりでなく、不要部分を除去する工程でさらに時間がかかってしまう。より好ましくは50nm以上、1μm以下であることが望ましい。

The

シード金属層113はキャパシタ109の上部電極114をセミアディティブ法で形成するための給電層である。シード金属層113は例えばCu、Ni、Al、Ti、Cr、Mo、W、Ta、Au、Ir、Ru、Pd、Pt、AlSi、AlSiCu、AlCu、NiFe、Cu合金単体もしくは複数組み合わせたものを適用することができる。より好ましくは銅であることが後のエッチング除去が簡便となるため銅であることが望ましい。シード金属層113の厚さは、10nm以上5μm以下であることが望ましい。シード金属層113の厚さが、100nm未満である場合、続く電解めっき工程において通電不良が発生する可能性がある。シード金属層113の厚さが、5μmを超えると、エッチング除去に時間がかかってしまう。シード金属層113の厚さが、より好ましくは100nm以上500nm以下が望ましい。

The

上部電極114は、電解めっき層である。電解銅めっきであることが簡便で安価で、電気伝導性が良好であることから望ましいが、電解銅めっきの他、電解ニッケルめっき、電解クロムめっき、電解Pdめっき、電解金めっき、電解ロジウムめっき、電解イリジウムめっき等であっても良い。

The

上部電極114の厚さ(電解銅めっきの厚さ)は3μm以上30μm以下であることが望ましい。3μm未満の場合、上部電極114を形成した後のエッチング処理によっては回路が消失してしまう虞がある。さらに回路の接続信頼性、電気伝導性が低下する危険性がある。電解銅めっき厚が30μmを超えると、30μm厚以上のレジスト層を形成する必要があり、製造コストがかかる。さらにはレジスト解像性が低下することから、ピッチ30μm以下の微細な配線形成が困難となってしまう。より好ましくは5μm以上、25μm以下であることが望ましい。さらに望ましくは10μm以上、20μm以下であることが望ましい。

The thickness of the upper electrode 114 (thickness of electrolytic copper plating) is desirably 3 μm or more and 30 μm or less. If the thickness is less than 3 μm, the circuit may disappear depending on the etching process after the

その後、図1に示すように、ガラス直上の導体回路層104の一部を下部電極としてキャパシタ109を形成した後に絶縁樹脂層131、ビアホール132を形成する。その後、積層導体回路層133と絶縁樹脂層131を繰り返して形成することによって多層配線が形成される。なお、導体回路層104と積層導体回路層133は公知のセミアディティブ法あるいはサブトラクティブ法を用いて形成することができる。さらに積層導体回路層133を形成した後に外部接続端子134を形成する。さらに、外部接続端子134にはんだボール135を形成する。

After that, as shown in FIG. 1, after forming a

本実施形態による回路基板は図1に示すように、片面に積層導体回路層133、外部接続端子134、はんだボール135があってもよく、両面にあっても良い。

As shown in FIG. 1, the circuit board according to the present embodiment may have laminated conductor circuit layers 133,

なお、絶縁樹脂層131は最外層であれば、ソルダーレジストを用いても良く、本実施形態により限定されない。また、外部接続端子134に表面処理を行ってもよい。表面処理を行うことではんだボール135との接合性が向上する。

Note that the insulating

表面処理は、スズやスズの合金めっき皮膜、無電解Ni-P/無電解Pd-P/Auめっき皮膜、もしくは無電解Ni-P/Auめっき皮膜等を成膜することができる。または、プレソルダー処理、または、OSP(Organic Solderability PReservative)等の有機皮膜処理が施されてもよい。はんだボール135はスクリーン印刷法、はんだボール振込み搭載法、電解めっき法等によって形成することができる。はんだボールの組成はスズ、銀、銅、ビスマス、鉛、亜鉛、インジウム、アンチモン等一種、もしくは複数種を混合したものを用いることができ、これら金属材料の混合比は問わない。はんだの代わりにワイヤーボンディング用のパッドを設けてもよい。

The surface treatment may be tin or tin alloy plating film, electroless Ni--P/electroless Pd--P/Au plating film, electroless Ni--P/Au plating film, or the like. Alternatively, pre-solder treatment or organic film treatment such as OSP (Organic Solderability Preservative) may be applied. The

図2はキャパシタ内蔵ガラス回路基板のキャパシタ周辺部を積層方向に見た平面図である。この図は、導体回路層104のうち、キャパシタ109を構成する領域近傍の下部電極105を示している。後述するが、図2のA-A線で切断した断面図でキャパシタ形成工程を説明する(図4参照)。

FIG. 2 is a plan view of the capacitor-embedded glass circuit substrate, viewed in the stacking direction, around the capacitors. This figure shows the

次に、キャパシタ内蔵ガラス回路基板10の製造方法について説明する。図3A~図3Fは、キャパシタ内蔵ガラス回路基板10を構成するキャパシタ内蔵ガラス回路基板の製造工程を示す縦断面図である。

Next, a method for manufacturing the capacitor built-in

図3Aに示すように、ガラス基板100を準備する。続いて図3Bに記載するようにガラス基板100に貫通孔101を形成する。貫通孔101の断面形状や径は本実施形態により限定されない。例えば貫通孔のトップ径とボトム径よりも中央部の径が狭くなるような形状でもよく、また、トップ径に対しボトム径が小さい形状等でもよい。更に、貫通孔のトップ径とボトム径よりも中央部の径が広くなるような形状でもよい。貫通孔の公知形成方法としては、レーザ加工、放電加工、感光性レジスト材料を用いる場合ではサンドブラスト加工、ドライエッチング、フッ化水素酸等によるケミカルエッチング加工が挙げられる。さらに感光性ガラスを用いてもガラスコアを作成することが可能である。好ましくはレーザ加工、放電加工が簡便でスループットが良いことから望ましい。用いることができるレーザは、CO2レーザ、UVレーザ、ピコ秒レーザ、フェムト秒レーザ等から選択することができる。

As shown in FIG. 3A, a

続いて図3Cに記載するように貫通孔101が形成されたガラス基板100の表面及び貫通孔内にシード金属層102を形成する。シード金属層102はセミアディティブ工法における配線形成用において、電解めっきの給電層として作用する。

Subsequently, as shown in FIG. 3C, a

シード金属層102の形成工程は、ガラス基板100上にチタン、銅層を形成した後に、無電解めっき層を形成する。チタン、銅層のみである場合、貫通孔101内部すべてに金属皮膜を形成することができずに、貫通孔101の接続信頼性低下が生じる。本実施形態によれば、無電解めっき法によって貫通孔101内に金属層を増強することで貫通孔101の接続信頼性を向上させることができる。無電解めっき層は無電解銅めっき、無電解ニッケルめっきが挙げられるが、ガラスあるいはチタン、銅層との密着性がよいことから無電解ニッケルめっきを行う。ニッケルめっき層が厚い場合微細は配線形成が困難となってしまうばかりでなく、膜応力増加による密着性低下する。そのため、無電解ニッケルめっき厚は1μm以下が望ましい。また、より好ましくは、0.5μm以下であり、さらに好ましくは0.3μm以下である。また、無電解ニッケルめっき皮膜には還元剤に由来する共析物であるリンや、無電解ニッケルめっき液中に含まれる硫黄や鉛やビスマス等が含まれていてもよい。以上の工程を経て、貫通孔101が形成されたガラス基板上にシード金属層102が形成された基板(図3C)が得られる。

In the step of forming the

続いて、図3Dに記載するように、フォトレジストパターンPRを形成する。フォトレジストパターンPRの形成方法について記載する。まず、シード金属層102上全面にフォトレジスト層を形成する。形成するフォトレジスト層はネガ型ドライフィルムレジスト、ネガ型液状レジスト、ポジ型液状レジストが挙げられるが、レジスト層の形成が簡便でかつ安価であるためネガ型フォトレジストであることが望ましい。レジスト層形成方法は、例えばネガ型ドライフィルムレジストであればロールラミネート法、真空ラミネート法が挙げられる。液状ネガ型、あるいはポジ型レジストである場合はスリットコート、カーテンコート、ダイコート、スプレーコート、静電塗装、インクジェットコート、グラビアコート、スクリーン印刷、グラビアオフセット印刷、スピンコート、ドクターコートより選定できる。これらレジスト層の形成方法は本実施形態により限定されない。

Subsequently, as shown in FIG. 3D, a photoresist pattern PR is formed. A method of forming the photoresist pattern PR will be described. First, a photoresist layer is formed on the entire surface of the

続いて、フォトレジスト層に所望の導体回路層104を形成するためのパターンを公知のフォトリソグラフィー法によって形成する。すなわち、レジストパターンは後の導体回路層104が形成される部分が露出するように位置あわせの上、露光、現像処理することによってパターニングする。レジスト層の厚みは、導体回路層の厚みにも依存するが、好ましくは5μm以上、25μm以下であることが望ましい。5μmより薄い場合、導体回路層となる電解めっき層を5μm以上に増膜できなくなり、回路の接続信頼性が低下する可能性がある。25μmより厚くなる場合、ピッチ30μm以下の微細配線を形成することが困難となる。こうして図3Dに示すように、フォトレジストパターンPRが形成されたガラス基板を得る。

Subsequently, a pattern for forming a desired

続いて、図3Eに示すように、導体回路層104の元となる電解めっき層103を電解めっき法により形成する。電解めっき法は電解ニッケルめっき、電解銅めっき電解、電解クロムめっき、電解Pdめっき、電解金めっき、電解ロジウムめっき、電解イリジウムめっき等が挙げられるが、電解銅めっきであることが簡便で安価で、電気伝導性が良好であることから望ましい。電解銅めっきの厚さは3μm以上30μm以下であることが望ましい。この理由として、3μm以下の場合、後のエッチング処理によっては回路が消失してしまう危険性があり、さらに回路の接続信頼性、電気伝導性が低下する危険性があるためである。一方、電解銅めっき厚が30μm以上である場合、30μm厚以上のレジスト層を形成する必要があり、製造コストがかかることになる。さらにはレジスト解像性が低下することから、ピッチ30μm以下の微細な配線形成が困難となってしまう。より好ましくは5μm以上、25μm以下であり、さらに好ましくは10μm以上、20μm以下であることが望ましい。

Subsequently, as shown in FIG. 3E, an electrolytic plated

続いて、図3Fに示すように、電解めっきにより配線形成した後に不要となったフォトレジストパターンPRを除去し、導体回路層104のみをガラス基板100に配置すると共に、シード金属層102を露出させる。本実施形態にレジスト除去方法は限定されず、例えば、アルカリ水溶液によって剥離除去することができる。

Subsequently, as shown in FIG. 3F, the photoresist pattern PR that is no longer necessary after the wiring is formed by electrolytic plating is removed, and only the

図4A~図4Iは、図3F中二点鎖線Pの部分を拡大して示す縦断面図である。なお、これらの図において、ガラス基板100上に形成された導体回路層104上へのキャパシタ形成の一例を記載してあるが、導体回路層104の直上にキャパシタ109を作成することに限定されない。

4A to 4I are vertical cross-sectional views showing enlarged portions of the chain double-dashed line P in FIG. 3F. Although these figures show an example of capacitor formation on the

図4Aは、導体回路層104の一部であるキャパシタ109を構成する下部電極105を示している。続いて、図4Bに記載するように下部電極105の上部に導体回路層の上面(表面)106を保護するため、保護層Hを形成する。保護層Hとしては前述のフォトレジストパターンPRを適用することができ、前記と同じ方法で形成することができる。保護層の形成領域はその後のキャパシタ形成領域よりやや大きいことが好ましい。

FIG. 4A shows a

続いて、先ほど図3Fに示したシード金属層102の露出した部分を除去し、回路を電気的に分断することによって、導体回路層104が形成される。露出したシード層を除去する工程では、導体回路層104も同時にエッチングされる。この際、図4Cに記載するように、保護層Hで保護された導体回路層の部分は、エッチングされず、凸状段差部が形成される。なお、シード層除去方法は本実施形態によって限定されることはないが、無電解Ni層、銅層、チタン層を順次化学エッチングにより除去する方法を用いることができる。エッチング液の種類は除去する金属種により適宜選択され、本実施形態によって限定されない。

A

続いて、図4Dに示すように、不要になった保護層Hを除去する。保護層Hの除去は前述のフォトレジストパターンPRと同様に公知方法のアルカリ水溶液で除去剥離処理を行うことができる。この場合、保護層Hが形成されていた領域は導体回路層104がエッチング液から保護されていたため、エッチングされず、一方、非保護部の導体回路層のみがエッチングされ、導体回路層104上に凸状段差部が形成される。この凸状部は下部電極105としてキャパシタ109が形成される領域となる。

Subsequently, as shown in FIG. 4D, the unnecessary protective layer H is removed. The removal of the protective layer H can be carried out using a known alkaline aqueous solution in the same manner as the photoresist pattern PR described above. In this case, since the

続いて、図4Eに示すように、下部電極105上の全面に渡り、下部密着層110、誘電体層111、上部密着層112、及び、シード金属層113を順次堆積形成する。上記層の成膜方法としては、真空蒸着法、スパッタリング法、イオンプレーティング法、MBE法、レーザブレーション法、CVD法が挙げられるが、本実施形態により限定されない。

Subsequently, as shown in FIG. 4E, a

誘電体層111の下層にある下部密着層110は、誘電体層111と導体回路層104の密着性を向上させる機能を有する。また、誘電体層111と導体回路層104との密着が十分である場合は、下部密着層110は無くても構わない。シード金属層113はキャパシタ109の上部電極114をセミアディティブ法で形成するための給電層として機能する。

The

続いて、図4Fに記載するようにフォトレジストパターンPSを形成する。フォトレジストパターンPSの形成は、前述したフォトレジストパターンPRと同じ方法で行うことができる。この場合、フォトレジストパターンPSの開口領域は導体回路層の凸部上面106bの内側となるように形成し、積層方向における平面視においても内側になるように形成する(図2参照)。

Subsequently, a photoresist pattern PS is formed as shown in FIG. 4F. The photoresist pattern PS can be formed by the same method as the photoresist pattern PR described above. In this case, the opening region of the photoresist pattern PS is formed so as to be inside the convex

続いて、図4Gに示すように、シード金属層113を用いて電解めっき法によって上部電極114を形成する。

Subsequently, as shown in FIG. 4G, the

上述したように、フォトレジストパターンPSは導体回路層の凸部上面106bの内側に開口部が形成されているため、上部電極114は導体回路層の凸部上面106bの内側にのみ形成される。

As described above, the photoresist pattern PS has an opening formed inside the

続いて、図4Hに示すように、フォトレジストパターンPSを除去する。フォトレジストパターンPSの除去は公知方法のアルカリ水溶液で除去剥離処理を行うことができる。 Subsequently, as shown in FIG. 4H, the photoresist pattern PS is removed. The removal of the photoresist pattern PS can be carried out using a known method of alkaline aqueous solution.

続いて、図4Iに示すように、上部電極114をマスクとして、シード金属層113、上部密着層112、誘電体層111、及び、下部密着層110の不要部分を除去する。シード金属層113、上部密着層112、誘電体層111、及び、下部密着層110の除去方法は化学エッチング法、ドライエッチング法、いずれも公知方法を用いることができ、各層毎で異なった方法でも、また、全ての層で同じ方法でもよく、本実施形態により限定されない。上述したように、上部電極114は導体回路層の凸部上面106bの内側に形成にされているため、上部電極114をマスクとして不要部分を除去すると誘電体層111は導体回路層の凸部上面106bの内側にのみ形成される。以上の工程によりキャパシタ109が形成される。

Subsequently, as shown in FIG. 4I, unnecessary portions of the

その後、図1に示すように、ガラス直上の配線回路上にキャパシタ109を形成した後に絶縁樹脂層131、ビアホール132を形成する。その後、積層導体回路層133と絶縁樹脂層131を繰り返して形成することによって多層配線が形成される。なお、導体回路層104と積層導体回路層133は公知のセミアディティブ法あるいはサブトラクティブ法を用いて形成することができる。さらに積層導体回路層133を形成した後に外部接続端子134を形成する。さらに、外部接続端子134にはんだボール135を形成する。

After that, as shown in FIG. 1, after forming a

本実施形態による回路基板は図1に記載のように片面に積層導体回路層133、外部接続端子134、はんだボール135があってもよく、変形例として図6に示したように両面にあっても良い。さらに半導体チップ136、チップ部品137を搭載してもよい。

The circuit board according to this embodiment may have laminated conductor circuit layers 133,

以下に多層配線の形成方法について説明する。多層配線の形成方法は公知方法を用いることができる。すなわち、多層配線層の絶縁樹脂層131として使用できる例としてはエポキシ樹脂、ポリイミド、マレイミド樹脂、ポリエチレンテレフタラート、ポリフェニレンオキシド、液晶ポリマー及びこれらの複合材料、あるいは感光性ポリイミド樹脂、感光性ポリベンゾオキサゾール、感光性アクリル-エポキシ樹脂を用いても良い。絶縁樹脂の形成方法は本実施形態により限定されないが、シート状のものであれば真空ラミネート、真空プレス、ロールラミネート法を用いることができる。液状のものであれば、スリットコート、カーテンコート、ダイコート、スプレーコート、静電塗装、インクジェットコート、グラビアコート、スクリーン印刷、グラビアオフセット印刷、スピンコート、ドクターコートより選定できる。

A method for forming a multilayer wiring will be described below. A known method can be used as a method for forming the multilayer wiring. That is, examples that can be used as the insulating

絶縁樹脂層131の厚さであるが、好ましくは5μm以上50μm以下であることが望ましい。50μm以上である場合、絶縁樹脂層131に形成できるビアホール132の小径化が難しくなるため、配線の高密度化が不利となってしまう、5μm以下である場合、層間絶縁性を確保することが困難となる。

The thickness of the insulating

多層配線中のビアホール132の形成は、非感光性絶縁樹脂であればレーザ加工を用いることができる。レーザは、CO2レーザ、UVレーザ、ピコ秒レーザ、フェムト秒レーザ等が挙げられるが、好ましくはUVレーザ、CO2レーザであることが簡便で望ましい。感光性絶縁樹脂であればフォトリソグラフィー法によって形成することができる。ビアホール形成後に適宜過マンガン酸溶液によるデスミアを行うことで樹脂表面の粗化とビアホール内をクリーニングして導体回路層104との密着性向上を行うことが望ましい。あるいはプラズマ処理によって樹脂表面及びビア内部をクリーニングする方法を行っても良い。

Laser processing can be used to form the via holes 132 in the multi-layer wiring if the non-photosensitive insulating resin is used. Examples of lasers include CO2 lasers, UV lasers, picosecond lasers, femtosecond lasers, etc., but UV lasers and CO2 lasers are preferred because they are simple and easy to use. If it is a photosensitive insulating resin, it can be formed by a photolithographic method. After forming the via hole, desmearing with a permanganic acid solution is preferably performed to roughen the surface of the resin and clean the inside of the via hole to improve the adhesion to the

このように構成されたキャパシタ内蔵ガラス回路基板と、このキャパシタ内蔵ガラス回路基板の製造方法によれば、次のような効果が得られる。すなわち、図4Bに示すように、導体回路層の上面106を保護層Hで保護することによって、図4Dに示すように、キャパシタの下部電極層側となる導体回路層の上面106に、シード金属層102のエッチング液に侵されない導体回路層の凸部上面(表面)106bの領域を形成可能である。導体回路層の凸部上面106bは、非保護部導体回路の上面106aと比較して、シード金属層102のエッチング液に侵されていないため滑らかな表面を得ることが可能である。この場合、より滑らかな面上にキャパシタを形成できるため、表面荒れに起因するキャパシタのショート低減や、電極表面積のバラつきに起因する容量のバラつきを低減できるため、歩留まりを向上することが可能である。

According to the glass circuit board with a built-in capacitor and the method for manufacturing the glass circuit board with a built-in capacitor thus configured, the following effects can be obtained. That is, as shown in FIG. 4B, by protecting the

また、図4Bに示すように、保護層Hをキャパシタ形成領域Qより積層方向における平面視において外側になるように形成することによって、導体回路層の凸部上面106b領域Qをキャパシタ形成領域より大きい。すなわち、キャパシタは凸状段差部の内側に形成される。この場合、キャパシタ109の下部電極層の全面がより滑らかな面である導体回路層の凸部上面106bであるため、より歩留まりを向上することができる。

Further, as shown in FIG. 4B, by forming the protective layer H so as to be outside the capacitor formation region Q in plan view in the stacking direction, the region Q of the upper surface of the

また、図4Eに示すように、シード金属層113の厚さを、凸状段差部の段差よりも大きくすることによって、キャパシタの上部電極114をセミアディティブ法で形成するための給電を安定して行うことが可能である。この場合、絶縁体である誘電体層111表面の段差を導電性の高いシード金属層113で乗り越えるため、凸状段差部の段差による誘電体層111表面の段差で断線する可能性がなくなり歩留まり良く上部電極114を形成可能となる。

Further, as shown in FIG. 4E, by making the thickness of the

また、図4F~図4Hに示すように、上部電極114は、導体回路層の凸部上面106bに対して、平面視において内側に形成することによって、キャパシタを導体回路層の凸部上面106bの内側に形成できる。この場合、キャパシタの下部電極層の全面がより滑らかな面である導体回路層の凸部上面106bであるため、より歩留まりを向上することができる。

In addition, as shown in FIGS. 4F and 4H, the

図5A~図5Cは、比較例に係るキャパシタを形成する製造工程を説明する説明図である。図5A~図5Cに示す製造工程においては、導体回路層の上面106を保護層Hで保護しない製造方法である。なお、これらの図において、同一要素又は同一機能を有する各部分には、同一符号を用いて、重複する説明は省略する。

5A to 5C are explanatory diagrams explaining manufacturing steps for forming a capacitor according to a comparative example. 5A to 5C is a manufacturing method in which the

図5Aは、導体回路層104の一部であるキャパシタ109を構成する下部電極105を示しており、図4Aと同じ状態である。続いて、図5Bに示すように、シード金属層102を除去する。この場合、導体回路層の上面106の全面がシード金属層102のエッチング液に侵されるため、導体回路層の上面106の全てが、上述の実施形態における非保護部導体回路の上面106aと同じ状態となる。

FIG. 5A shows a

次いで、前述した図4E~図4Hと同じ製造方法を経て、図5Cのようにキャパシタが形成される。この場合、キャパシタの下部電極層側はエッチング液で侵された非保護部導体回路の上面106aとなるため、荒れた面の上にキャパシタを形成することとなる。表面荒れに起因するキャパシタのショートや、電極表面積のバラつきに起因する容量のバラつきが生じるため歩留まり低下を引き起こす。

Then, a capacitor is formed as shown in FIG. 5C through the same manufacturing method as in FIGS. 4E to 4H. In this case, since the lower electrode layer side of the capacitor becomes the

このように、本実施形態におけるキャパシタ内蔵ガラス回路基板においては、導体回路層の上面106を保護層Hで保護しない製造方法に比べて、信頼性を向上させることができると共に、電極表面積のバラつきに起因する容量のバラつきが生じるため歩留まり低下を防止できる。また、本実施形態に係るキャパシタ内蔵ガラス回路基板10においても、電気的信頼性を高めることができると共に、電子回路、電子機器の小型化・薄型化を実現することが可能となる。

As described above, in the glass circuit substrate with a built-in capacitor according to the present embodiment, the reliability can be improved compared to the manufacturing method in which the

なお、本発明は、上記実施形態に限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で種々に変形することが可能である。また、各実施形態は適宜組み合わせて実施してもよく、その場合組み合わせた効果が得られる。更に、上記実施形態には種々の発明が含まれており、開示される複数の構成要件から選択された組み合わせにより種々の発明が抽出され得る。例えば、実施形態に示される全構成要件からいくつかの構成要件が削除されても、課題が解決でき、効果が得られる場合には、この構成要件が削除された構成が発明として抽出され得る。 It should be noted that the present invention is not limited to the above-described embodiments, and various modifications can be made in the implementation stage without departing from the scope of the invention. Further, each embodiment may be implemented in combination as appropriate, in which case the combined effect can be obtained. Furthermore, various inventions are included in the above embodiments, and various inventions can be extracted by combinations selected from a plurality of disclosed constituent elements. For example, even if some constituent elements are deleted from all the constituent elements shown in the embodiments, if the problem can be solved and effects can be obtained, the configuration with the constituent elements deleted can be extracted as an invention.

本発明によれば、ガラス基板を有するキャパシタ内蔵回路基板を高い信頼性で製造することが可能となる。なお、キャパシタ内蔵ガラス回路基板は、半導体パッケージ基板、インターポーザ、光学素子用基板の製造、あるいは電子部品の製造に利用することができる。

以下に、本願出願の当初の特許請求の範囲に記載された発明と同等の記載を付記する。

[1]

ガラス基板と、

このガラス基板に積層され、内部に導体回路層が形成された絶縁樹脂層と、

前記導体回路層の一部を下部電極とし、この下部電極上に積層形成される誘電体層と、前記誘電体層上に積層形成される上部電極層とを有するキャパシタとを備え、

前記下部電極は、前記ガラス基板と前記絶縁樹脂層の積層方向を含む平面における断面視において前記誘電体層側に凸状段差部を有し、前記凸状段差部の表面は凸状段差部以外の表面より、表面粗さが小さく形成されたキャパシタ内蔵ガラス回路基板。

[2]

前記キャパシタは、前記積層方向の平面視において前記導体回路層の前記凸状段差部の内側に備えられている[1]に記載のキャパシタ内蔵ガラス回路基板。

[3]

前記キャパシタの前記上部電極層の下地にはシード金属層が形成され、

前記シード金属層の厚さが、前記下部電極の前記凸状段差部の段差より厚く形成されている[1]に記載のキャパシタ内蔵ガラス回路基板。

[4]

前記ガラス基板には、表裏面を貫通する貫通孔が形成されている[1]に記載のキャパシタ内蔵ガラス回路基板。

[5]

ガラス基板表面に導体回路層を形成する工程と、前記ガラス基板に絶縁樹脂層を積層形成する工程と、前記絶縁樹脂層にビアを形成する工程を複数回繰り返す第1工程と、

前記第1工程は、前記導体回路層の一部に、誘電体層と、上部電極層とを有するキャパシタを形成する工程を含み、

前記キャパシタを形成する工程は、前記導体回路層の上に保護層を形成する工程と、前記保護層をマスクとして前記導体回路層のシード金属層を除去する工程と、前記保護層を剥離する工程と、前記導体回路層の上に下部電極、若しくは、前記誘電体層を形成する工程を含むキャパシタ内蔵ガラス回路基板の製造方法。

[6]

前記保護層を形成する工程は、前記ガラス基板と前記絶縁樹脂層との積層方向の平面視において前記キャパシタの形成領域位の外側まで形成する[5]に記載のキャパシタ内蔵ガラス回路基板の製造方法。

[7]

前記キャパシタを形成する工程は、前記上部電極層を、前記ガラス基板と前記絶縁樹脂層との積層方向の平面視において前記保護層によって保護された導体回路層部の内側に形成する[5]に記載のキャパシタ内蔵ガラス回路基板の製造方法。

[8]

前記キャパシタを形成する工程は、前記誘電体層の上部にシード金属層を形成する工程を備え、

前記シード金属層を形成する工程は、シード層の厚さが、前記保護層によって保護された導体回路層部と、保護されていない導体回路層部の段差より厚くなるように実施する[5]に記載のキャパシタ内蔵ガラス回路基板の製造方法。

[9]

前記第1工程の前に、前記ガラス基板に表裏面を貫通する貫通孔を形成する工程を有する[5]に記載のキャパシタ内蔵ガラス回路基板の製造方法。

According to the present invention, it is possible to manufacture a capacitor built-in circuit board having a glass substrate with high reliability. The capacitor-embedded glass circuit substrate can be used for manufacturing semiconductor package substrates, interposers, substrates for optical elements, or for manufacturing electronic components.

The description equivalent to the invention described in the original claims of the present application is added below.

[1]

a glass substrate;

an insulating resin layer laminated on the glass substrate and having a conductive circuit layer formed therein;

a capacitor having a dielectric layer formed by laminating a part of the conductor circuit layer as a lower electrode, a dielectric layer laminated on the lower electrode, and an upper electrode layer laminated on the dielectric layer;

The lower electrode has a convex stepped portion on the dielectric layer side in a cross-sectional view in a plane including the stacking direction of the glass substrate and the insulating resin layer, and the surface of the convex stepped portion is other than the convex stepped portion. A capacitor-embedded glass circuit substrate having a surface roughness smaller than that of the surface of the capacitor.

[2]

The capacitor-embedded glass circuit board according to [1], wherein the capacitor is provided inside the convex stepped portion of the conductor circuit layer when viewed from above in the stacking direction.

[3]

a seed metal layer is formed under the upper electrode layer of the capacitor;

The capacitor-embedded glass circuit board according to [1], wherein the seed metal layer is thicker than the step of the convex step portion of the lower electrode.

[4]

The capacitor-embedded glass circuit board according to [1], wherein the glass substrate is formed with a through hole penetrating through the front and back surfaces.

[5]

a first step of repeating a step of forming a conductive circuit layer on the surface of a glass substrate, a step of laminating an insulating resin layer on the glass substrate, and a step of forming vias in the insulating resin layer a plurality of times;

The first step includes forming a capacitor having a dielectric layer and an upper electrode layer on a portion of the conductor circuit layer,

The step of forming the capacitor includes forming a protective layer on the conductive circuit layer, removing a seed metal layer of the conductive circuit layer using the protective layer as a mask, and peeling off the protective layer. and a method of manufacturing a glass circuit substrate with a built-in capacitor, comprising a step of forming a lower electrode or the dielectric layer on the conductive circuit layer.

[6]

The method for manufacturing a capacitor-embedded glass circuit board according to [5], wherein the step of forming the protective layer includes forming the protective layer up to the outside of the capacitor forming region in a plan view in the lamination direction of the glass substrate and the insulating resin layer. .

[7]

The step of forming the capacitor includes forming the upper electrode layer inside the conductive circuit layer portion protected by the protective layer in plan view in a lamination direction of the glass substrate and the insulating resin layer [5]. A method for manufacturing the glass circuit board with a built-in capacitor as described above.

[8]

forming the capacitor comprises forming a seed metal layer on top of the dielectric layer;

The step of forming the seed metal layer is performed so that the thickness of the seed layer is thicker than the step between the conductor circuit layer portion protected by the protective layer and the unprotected conductor circuit layer portion [5]. 3. A method for manufacturing the capacitor-embedded glass circuit board according to 1.

[9]

The method for manufacturing a glass circuit board with a built-in capacitor according to [5], further comprising, prior to the first step, forming a through hole penetrating through the front and back surfaces of the glass substrate.

10,10A…キャパシタ内蔵ガラス回路基板、100…ガラス基板、101…貫通孔、102…シード金属層、103…電解めっき層、104…導体回路層、105…下部電極、106…導体回路の上面(表面)、106a…非保護部導体回路の上面(表面)、106b…凸部上面(表面)、109…キャパシタ、110…下部密着層、111…誘電体層、112…上部密着層、113…シード金属層、114…上部電極、131…絶縁樹脂層、132…ビアホール、133…積層導体回路層、134…外部接続端子、135…はんだボール、136…半導体チップ、137…チップ部品。

10, 10A... glass circuit substrate with built-in capacitor, 100... glass substrate, 101... through hole, 102... seed metal layer, 103... electroplating layer, 104... conductor circuit layer, 105... lower electrode, 106... upper surface of conductor circuit ( Surface), 106a... Upper surface (surface) of non-protected portion conductor circuit, 106b... Upper surface of convex portion (surface), 109... Capacitor, 110... Lower adhesive layer, 111... Dielectric layer, 112... Upper adhesive layer, 113...

Claims (7)

前記導体回路層の上に、前記導体回路層の上面が部分的に露出するように保護層を形成する工程と、

前記保護層をマスクとして用いたエッチングにより、前記導体回路層の上面に、第1上面領域と、前記第1上面領域から突き出た凸部の上面としての第2上面領域とを形成する工程であって、前記第2上面領域は前記下部電極の上面である工程と、

前記保護層を剥離する工程と、

前記下部電極上に誘電体層を形成する工程と、

前記誘電体層上に上部電極を形成する工程と、

を含むキャパシタ内蔵ガラス回路基板の製造方法。 forming a conductive circuit layer having a lower electrode on a glass substrate;

forming a protective layer on the conductor circuit layer so that the upper surface of the conductor circuit layer is partially exposed;

A step of forming, on the upper surface of the conductive circuit layer, a first upper surface region and a second upper surface region as an upper surface of a projection protruding from the first upper surface region by etching using the protective layer as a mask. wherein the second top surface region is the top surface of the bottom electrode;

peeling off the protective layer;

forming a dielectric layer on the bottom electrode;

forming a top electrode on the dielectric layer;

A method for manufacturing a glass circuit board with a built-in capacitor.

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017246227A JP7206589B2 (en) | 2017-12-22 | 2017-12-22 | Manufacturing method of glass circuit board with built-in capacitor |

| JP2022130129A JP7444210B2 (en) | 2017-12-22 | 2022-08-17 | Glass circuit board with built-in capacitor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017246227A JP7206589B2 (en) | 2017-12-22 | 2017-12-22 | Manufacturing method of glass circuit board with built-in capacitor |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022130129A Division JP7444210B2 (en) | 2017-12-22 | 2022-08-17 | Glass circuit board with built-in capacitor |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019114635A JP2019114635A (en) | 2019-07-11 |

| JP2019114635A5 JP2019114635A5 (en) | 2021-01-28 |

| JP7206589B2 true JP7206589B2 (en) | 2023-01-18 |

Family

ID=67222835

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017246227A Active JP7206589B2 (en) | 2017-12-22 | 2017-12-22 | Manufacturing method of glass circuit board with built-in capacitor |

| JP2022130129A Active JP7444210B2 (en) | 2017-12-22 | 2022-08-17 | Glass circuit board with built-in capacitor |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022130129A Active JP7444210B2 (en) | 2017-12-22 | 2022-08-17 | Glass circuit board with built-in capacitor |

Country Status (1)

| Country | Link |

|---|---|

| JP (2) | JP7206589B2 (en) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019244382A1 (en) | 2018-06-21 | 2019-12-26 | 大日本印刷株式会社 | Wiring substrate and semiconductor device |

| JP7443734B2 (en) * | 2019-11-29 | 2024-03-06 | Tdk株式会社 | electronic components |

| JP7512594B2 (en) * | 2020-01-10 | 2024-07-09 | Toppanホールディングス株式会社 | Circuit Board |

| TWI800153B (en) * | 2020-12-24 | 2023-04-21 | 南韓商東友精細化工有限公司 | Circuit board |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007123690A (en) | 2005-10-31 | 2007-05-17 | Tdk Corp | Thin film device and manufacturing method thereof |

| JP2007180093A (en) | 2005-12-27 | 2007-07-12 | Tdk Corp | Thin film device and manufacturing method thereof |

| JP2008084933A (en) | 2006-09-26 | 2008-04-10 | Fujitsu Ltd | Interposer and manufacturing method thereof |

| JP2009188401A (en) | 2008-02-07 | 2009-08-20 | Ibiden Co Ltd | Printed circuit board with built-in capacitor |

| JP2011054979A (en) | 2005-10-18 | 2011-03-17 | Murata Mfg Co Ltd | Thin-film capacitor |

| JP2011129665A (en) | 2009-12-17 | 2011-06-30 | Sony Corp | Method of manufacturing laminated wiring board |

| JP2014241356A (en) | 2013-06-12 | 2014-12-25 | 日本電気株式会社 | Electrode structure and process of manufacturing the same |

| JP2016195161A (en) | 2015-03-31 | 2016-11-17 | Tdk株式会社 | Thin film capacitor |

| JP2017139326A (en) | 2016-02-03 | 2017-08-10 | 富士ゼロックス株式会社 | Circuit board and method for manufacturing circuit board |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4997757B2 (en) * | 2005-12-20 | 2012-08-08 | 富士通株式会社 | Thin film capacitor and method for manufacturing the same, electronic device and circuit board |

-

2017

- 2017-12-22 JP JP2017246227A patent/JP7206589B2/en active Active

-

2022

- 2022-08-17 JP JP2022130129A patent/JP7444210B2/en active Active

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011054979A (en) | 2005-10-18 | 2011-03-17 | Murata Mfg Co Ltd | Thin-film capacitor |

| JP2007123690A (en) | 2005-10-31 | 2007-05-17 | Tdk Corp | Thin film device and manufacturing method thereof |

| JP2007180093A (en) | 2005-12-27 | 2007-07-12 | Tdk Corp | Thin film device and manufacturing method thereof |

| JP2008084933A (en) | 2006-09-26 | 2008-04-10 | Fujitsu Ltd | Interposer and manufacturing method thereof |

| JP2009188401A (en) | 2008-02-07 | 2009-08-20 | Ibiden Co Ltd | Printed circuit board with built-in capacitor |

| JP2011129665A (en) | 2009-12-17 | 2011-06-30 | Sony Corp | Method of manufacturing laminated wiring board |

| JP2014241356A (en) | 2013-06-12 | 2014-12-25 | 日本電気株式会社 | Electrode structure and process of manufacturing the same |

| JP2016195161A (en) | 2015-03-31 | 2016-11-17 | Tdk株式会社 | Thin film capacitor |

| JP2017139326A (en) | 2016-02-03 | 2017-08-10 | 富士ゼロックス株式会社 | Circuit board and method for manufacturing circuit board |

Also Published As

| Publication number | Publication date |

|---|---|

| JP7444210B2 (en) | 2024-03-06 |

| JP2022159478A (en) | 2022-10-17 |

| JP2019114635A (en) | 2019-07-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7083600B2 (en) | Glass circuit board with built-in capacitor and its manufacturing method | |

| US11412615B2 (en) | Electronic component and method of producing electronic component | |

| JP7444210B2 (en) | Glass circuit board with built-in capacitor | |

| US10923439B2 (en) | Core substrate, multi-layer wiring substrate, semiconductor package, semiconductor module, copper-clad substrate, and method for manufacturing core substrate | |

| US11516911B2 (en) | Glass circuit board and stress relief layer | |

| EP3220417B1 (en) | Wiring circuit board, semiconductor device, wiring circuit board manufacturing method, and semiconductor device manufacturing method | |

| JP4708407B2 (en) | Capacitor-embedded printed circuit board and manufacturing method thereof | |

| US11756846B2 (en) | Glass core, multilayer circuit board, and method of manufacturing glass core | |

| JP2018107256A (en) | Glass wiring board, semiconductor package substrate, semiconductor device, and method for manufacturing semiconductor device | |

| JP7009958B2 (en) | Manufacturing method of glass substrate with built-in capacitor | |

| JP6946745B2 (en) | Glass circuit board and its manufacturing method | |

| JP2019114723A (en) | Capacitor built-in glass circuit board and method for manufacturing capacitor built-in glass circuit board | |

| JP2019197791A (en) | Capacitor built-in glass substrate and capacitor built-in circuit substrate | |

| WO2023090197A1 (en) | Wiring board and method for manufacturing same | |

| TW202448236A (en) | Wiring board and manufacturing method therefor | |

| WO2024004566A1 (en) | Glass core laminate structure and production method for glass core laminate structure | |

| JP2024006905A (en) | Multilayer wiring board, method for manufacturing multilayer wiring board, and base material substrate | |

| JP2024134681A (en) | Wiring board and method for manufacturing the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201208 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20201208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210916 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20211019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20211220 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20220517 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220817 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20220817 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20220819 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20220907 |

|

| C21 | Notice of transfer of a case for reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C21 Effective date: 20220913 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20221206 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20221219 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7206589 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |