JP6719693B1 - 電力変換器の試験装置および試験方法 - Google Patents

電力変換器の試験装置および試験方法 Download PDFInfo

- Publication number

- JP6719693B1 JP6719693B1 JP2020517616A JP2020517616A JP6719693B1 JP 6719693 B1 JP6719693 B1 JP 6719693B1 JP 2020517616 A JP2020517616 A JP 2020517616A JP 2020517616 A JP2020517616 A JP 2020517616A JP 6719693 B1 JP6719693 B1 JP 6719693B1

- Authority

- JP

- Japan

- Prior art keywords

- command value

- voltage

- converter

- switching elements

- current

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000012360 testing method Methods 0.000 title claims abstract description 130

- 238000010998 test method Methods 0.000 title claims description 8

- 238000000034 method Methods 0.000 claims description 22

- 230000007423 decrease Effects 0.000 claims description 9

- 238000001514 detection method Methods 0.000 claims description 6

- 238000010992 reflux Methods 0.000 claims description 6

- 239000003990 capacitor Substances 0.000 description 39

- 238000010586 diagram Methods 0.000 description 28

- 230000008569 process Effects 0.000 description 14

- 230000004048 modification Effects 0.000 description 7

- 238000012986 modification Methods 0.000 description 7

- 102220012974 rs139794370 Human genes 0.000 description 6

- 102220012970 rs199742269 Human genes 0.000 description 6

- 238000012545 processing Methods 0.000 description 5

- 230000006870 function Effects 0.000 description 4

- 230000004044 response Effects 0.000 description 4

- 230000007704 transition Effects 0.000 description 3

- 230000008859 change Effects 0.000 description 2

- 239000000470 constituent Substances 0.000 description 2

- 230000008034 disappearance Effects 0.000 description 2

- 102220227728 rs1064795458 Human genes 0.000 description 2

- 102220056701 rs730880971 Human genes 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- UXUFTKZYJYGMGO-CMCWBKRRSA-N (2s,3s,4r,5r)-5-[6-amino-2-[2-[4-[3-(2-aminoethylamino)-3-oxopropyl]phenyl]ethylamino]purin-9-yl]-n-ethyl-3,4-dihydroxyoxolane-2-carboxamide Chemical compound O[C@@H]1[C@H](O)[C@@H](C(=O)NCC)O[C@H]1N1C2=NC(NCCC=3C=CC(CCC(=O)NCCN)=CC=3)=NC(N)=C2N=C1 UXUFTKZYJYGMGO-CMCWBKRRSA-N 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 239000013307 optical fiber Substances 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/36—Means for starting or stopping converters

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/50—Testing of electric apparatus, lines, cables or components for short-circuits, continuity, leakage current or incorrect line connections

- G01R31/56—Testing of electric apparatus

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

- H02M1/0016—Control circuits providing compensation of output voltage deviations using feedforward of disturbance parameters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of DC power input into DC power output

- H02M3/22—Conversion of DC power input into DC power output with intermediate conversion into AC

- H02M3/24—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters

- H02M3/28—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC

- H02M3/325—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC using devices of a triode or a transistor type requiring continuous application of a control signal

- H02M3/335—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC using devices of a triode or a transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/33569—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC using devices of a triode or a transistor type requiring continuous application of a control signal using semiconductor devices only having several active switching elements

- H02M3/33573—Full-bridge at primary side of an isolation transformer

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of DC power input into DC power output

- H02M3/22—Conversion of DC power input into DC power output with intermediate conversion into AC

- H02M3/24—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters

- H02M3/28—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC

- H02M3/325—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC using devices of a triode or a transistor type requiring continuous application of a control signal

- H02M3/335—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC using devices of a triode or a transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/33569—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC using devices of a triode or a transistor type requiring continuous application of a control signal using semiconductor devices only having several active switching elements

- H02M3/33576—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC using devices of a triode or a transistor type requiring continuous application of a control signal using semiconductor devices only having several active switching elements having at least one active switching element at the secondary side of an isolation transformer

- H02M3/33592—Conversion of DC power input into DC power output with intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate AC using devices of a triode or a transistor type requiring continuous application of a control signal using semiconductor devices only having several active switching elements having at least one active switching element at the secondary side of an isolation transformer having a synchronous rectifier circuit or a synchronous freewheeling circuit at the secondary side of an isolation transformer

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/42—Conversion of DC power input into AC power output without possibility of reversal

- H02M7/44—Conversion of DC power input into AC power output without possibility of reversal by static converters

- H02M7/48—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/483—Converters with outputs that each can have more than two voltages levels

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/42—Conversion of DC power input into AC power output without possibility of reversal

- H02M7/44—Conversion of DC power input into AC power output without possibility of reversal by static converters

- H02M7/48—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/483—Converters with outputs that each can have more than two voltages levels

- H02M7/4833—Capacitor voltage balancing

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/42—Conversion of DC power input into AC power output without possibility of reversal

- H02M7/44—Conversion of DC power input into AC power output without possibility of reversal by static converters

- H02M7/48—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/483—Converters with outputs that each can have more than two voltages levels

- H02M7/4835—Converters with outputs that each can have more than two voltages levels comprising two or more cells, each including a switchable capacitor, the capacitors having a nominal charge voltage which corresponds to a given fraction of the input voltage, and the capacitors being selectively connected in series to determine the instantaneous output voltage

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/42—Conversion of DC power input into AC power output without possibility of reversal

- H02M7/44—Conversion of DC power input into AC power output without possibility of reversal by static converters

- H02M7/48—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/53—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M7/537—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters

- H02M7/5387—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters in a bridge configuration

- H02M7/53871—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters in a bridge configuration with automatic control of output voltage or current

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Inverter Devices (AREA)

Abstract

Description

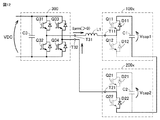

図1は、本実施の形態に係る試験装置を含む試験システムの第1の構成例を説明する回路図である。

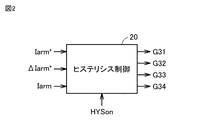

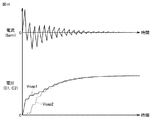

図2を参照して、図1に示された制御回路2は、ヒステリシス制御部20を含む。ヒステリシス制御部20は、ヒステリシスコンバータ300から出力されるアーム電流Iarmを、基準電流指令値Iarm*に従って制御する。具体的には、アーム電流Iarmは、基準電流指令値Iarm*を中心とした、ヒステリシス幅指令値ΔIarm*によって規定される一定範囲内に制御される。上述のように、アーム電流Iarmは、リアクトルL1、電力変換器100x、及び、補助変換器200xを通過し、センサCT1によって検出される。

式(1)において、時間tに対して、ω及びθは、交流成分の角周波数及び位相を示す。基準電流指令値Iarm*を直流電流指令値(Idc*)及び交流電流指令値(Iac*・sin(ωt+θ))の重畳によって与えることにより、MMCの各変換器セルの実際の運転時における通過電流を模擬することが可能となる。尚、直流成分(直流電流指令値)Idc*は負値(電力変換器100xからヒステリシスコンバータ300へ電流が流入する方向)に設定されてもよいが、以下では、Idc*>0のケースを説明する。

Vcell*=Vdc*+Vac*・sin(ωt+φ) …(2)

式(2)において、時間tに対して、ωは、交流成分の角周波数であり、式(1)と共通である。φは、交流成分の位相であり、式(1)のθとは個別に設定されるが、φ≠θ及びφ=θのいずれであってもよい。基準出力電圧指令値Vcell*についても、直流電圧指令値(Vdc*)及び交流電圧指令値(Vac*・sin(ωt+φ))が重畳するように与えることにより、MMCの各変換器セルの実際の運転時における出力電圧を模擬することが可能となる。

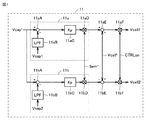

図6を参照して、出力電圧指令値生成部11は、電力変換器100xの電圧制御指令値Vc1を生成する第1演算部11aと、補助変換器200xの電圧制御指令値Vc2を算出する第2演算部11bとを含む。

図7を参照して、第1演算部11a及び第2演算部11bは、図6の構成例と比較して、ローパスフィルタ11aB及び11bBの配置が異なる。具体的には、ローパスフィルタ11aB及び11bBには、キャパシタ電圧Vcap1及びVcap2(センサVT1及びVT2による検出値)が入力されて、偏差演算部11aA及び11bAは、ローパスフィルタを通過したキャパシタ電圧Vcap1及びVcap2を、蓄電素子電圧指令値Vcap*(図5)から減算することによって、比例制御部11aC及び11bCに入力される電圧偏差を算出する。このような構成としても、図6と同様に、電力変換器100xの出力電圧指令値Vcell1(第1の出力電圧指令値)、及び、補助変換器200xの出力電圧指令値Vcell2(第2の出力電圧指令値)を算出することができる。

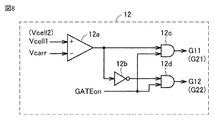

図8を参照して、PWM制御部12は、電圧比較器12aと、NOT回路12bと、AND回路12c,12dとを有する。電圧比較器12aは、出力電圧指令値Vcell1及びキャリア電圧Vcarrの比較結果を出力する。例えば、Vcell1>Vcarrのときには、電圧比較器12aは「1」を出力し、Vcell1<Vcarrのときには、電圧比較器12aは「0」を出力する。NOT回路12bは、電圧比較器12aの出力値を反転する。

+Vac*×Iac*×cos(φ−θ)/2 …(3)

式(3)は、式(1)のIarm*と、式(2)のVcell*との積で示される瞬時電力を、基本波1周期分、即ち、ωt=0〜2πの期間で積分することによって得られる。

−Vac*×Iac*×cos(φ−θ)/2 …(4)

ここで、電力変換器100xに含まれる蓄電素子C1は、電力変換器100xに流入する瞬時電力によって充放電される。同様に、補助変換器200xに含まれる蓄電素子C2は、補助変換器200xに流入する瞬時電力によって充放電される。一方で、式(3)及び式(4)から理解されるように、電力変換器100xに流入する平均電力Pcell*と、補助変換器200xに流入する平均電力Paux*との間には、Paux*=−Pcell*の関係がある。

定常状態においては、式(5)が成り立つように、基準出力電圧指令値Vcell*及び基準電流指令値Iarm*を与える。通常、実際のMMCにおける1個の変換器セルが出力する電圧と、当該変換器セルに流れる電流とに相当するように、基準出力電圧指令値Vcell*(Vdc*,Vac*,φ)及び基準電流指令値Iarm*(Idc*,Iac*,θ)が設定される。即ち、図5に示された、定常状態における直流電流指令値Idc*=Idcsは、上記式(5)が成立するように設定される。

実施の形態2では、還流ステップS1の前に、蓄電素子C1及びC2をプリチャージする充電ステップS3が実行される制御処理を説明する。

図10を参照して、充電ステップS3は、電力変換器100xのスイッチング素子Q11,Q12及び補助変換器200xのスイッチング素子Q21,Q22をオフするステップS3Aを含む。例えば、図8においてGATEon=「0」に固定することで、ステップS3Aの処理を実行することができる。

図11を参照して、上限電流指令値Iarmh*及び基準電流指令値Iarm*(=0)の差(絶対値)と、下限電流指令値Iarml*及び基準電流指令値Iarm*(=0)の差(絶対値)とは等しい。従って、上限電流指令値Iarmh*及び下限電流指令値Iarml*が0を基準に正負対称であるので、アーム電流Iarmは、Iarm>0の期間と、Iarm<0との期間とが周期的に現れる、0を基準に正負対称な交流電流(平均値=0)に制御される。

実施の形態3では、実施の形態2で説明した充電ステップS3の変形例を説明する。

図14を参照して、実施の形態3においても、制御回路2は、図9で説明した還流ステップS1に先立って、充電ステップS3を実行する。充電ステップS3は、図10と同様のステップS3Aと、ヒステリシスコンバータ300を一定デューティで動作させるステップS3Cとを含む。即ち、実施の形態3に係る充電ステップS3では、基準電流指令値Iarm*=0としてヒステリシスコンバータ300を動作するステップS3Bに代えて、ステップS3Cが実行される。

図17は、本実施の形態に係る試験装置を含む試験システムの構成の第1の変形例を説明する回路図である。

Claims (17)

- 第1の端子を介して直列接続された第1及び第2の主スイッチング素子の直列接続体と、前記直列接続体と並列接続される第1の蓄電素子とを有する電力変換器の試験装置であって、

第2の端子を介して直列接続された第1及び第2の補助スイッチング素子の直列接続体と、前記直列接続体と並列接続される第2の蓄電素子とを有する補助変換器と、

前記電力変換器と前記補助変換器との間を電気的に接続する配線と、

前記第1及び第2の端子と接続されて、交流電流指令値と直流電流指令値とが重畳された基準電流指令値に従う、前記電力変換器の試験用電流を出力する電流出力回路と、

前記電流出力回路、前記電力変換器、及び、前記補助変換器を制御する制御回路とを備え、

前記制御回路は、

前記電流出力回路からの前記基準電流指令値に従う前記試験用電流の出力開始後に、前記試験用電流の直流成分が予め定められたレベルに達するまでの間、前記第1及び第2の蓄電素子を迂回した電流経路が前記第1及び第2の端子間に形成されるように前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子のオンオフを固定する還流動作を実行し、

前記直流成分が前記予め定められたレベルに達した後は、蓄電素子電圧指令値に従った前記第1及び第2の蓄電素子の電圧の制御を少なくとも含む電圧制御のための前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子のオンオフ制御を開始する、電力変換器の試験装置。 - 前記制御回路は、前記還流動作の前に、前記電流出力回路から直流成分を含まない交流電流が供給される状態の下で、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子をオフに固定して、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子の各々と逆並列に接続されたダイオードを経由する電流経路によって、前記第1及び第2の蓄電素子を充電する充電動作を実行する、請求項1記載の電力変換器の試験装置。

- 前記電流出力回路は、

前記第1及び第2の端子のそれぞれと電気的に接続される第1及び第2のテスト端子と、

複数のスイッチング素子を有し、当該複数のスイッチング素子のオンオフ制御によって、直流電圧を正のパルス電圧又は負のパルス電圧に変換して前記第1及び第2のテスト端子間に出力するヒステリシスコンバータと、

前記第1の端子及び前記第1のテスト端子の間、並びに、前記第2の端子及び前記第2のテスト端子の間との間の少なくとも一方に、前記試験用電流が通過するように接続されたリアクトルとを含み、

前記制御回路は、

前記正のパルス電圧の出力時に、前記試験用電流の検出値が、前記基準電流指令値よりも高く設定された上限電流指令値まで上昇すると前記負のパルス電圧の出力に切り替える一方で、前記負のパルス電圧の出力時には、前記試験用電流の検出値が、前記基準電流指令値よりも低く設定された下限電流指令値まで低下すると前記正のパルス電圧の出力に切り替えるように、前記ヒステリシスコンバータの前記複数のスイッチング素子のオンオフを制御する、請求項1記載の電力変換器の試験装置。 - 前記制御回路は、前記還流動作の前に、前記第1及び第2の蓄電素子の充電動作を実行するように、前記ヒステリシスコンバータ、前記電力変換器、及び、前記補助変換器を制御し、

前記基準電流指令値と前記上限電流指令値との差の絶対値と、前記基準電流指令値と前記下限電流指令値との差の絶対値とは同一であるとともに、前記充電動作において、前記基準電流指令値はゼロに設定され、

前記充電動作において、前記電力変換器及び前記補助変換器では、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子がオフに固定されて、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子の各々と逆並列に接続されたダイオードを経由する電流経路によって、前記第1及び第2の蓄電素子が充電される、請求項3記載の電力変換器の試験装置。 - 前記制御回路は、前記還流動作の前に、前記第1及び第2の蓄電素子の充電動作を実行するように、前記ヒステリシスコンバータ、前記電力変換器、及び、前記補助変換器を制御し、

前記充電動作において、前記ヒステリシスコンバータは、前記基準電流指令値とは無関係に、前記正のパルス電圧を出力する第1の期間と、前記負のパルス電圧を出力する第2の期間とが、予め定められたそれぞれの期間長の比率に従って交互に出現するように、前記複数のスイッチング素子のオンオフが制御され、

前記充電動作において、前記電力変換器及び前記補助変換器では、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子がオフに固定されて、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子の各々と逆並列に接続されたダイオードを経由する電流経路によって、前記第1及び第2の蓄電素子が充電される、請求項3記載の電力変換器の試験装置。 - 前記電圧制御において、前記電力変換器では、前記第1の端子の出力電圧が、第1の出力電圧指令値に追従するように前記第1及び第2の主スイッチング素子のオンオフが制御されるとともに、前記補助変換器では、前記第2の端子の出力電圧が、第2の出力電圧指令値に追従するように前記第1及び第2の補助スイッチング素子のオンオフが制御され、 前記制御回路は、前記電圧制御において、

前記第1の蓄電素子の電圧と前記蓄電素子電圧指令値との第1の電圧偏差を補償するための第1の電圧制御指令値と、交流電圧指令値と直流電圧指令値とが重畳された基準出力電圧指令値とを加算した値に従って前記第1の出力電圧指令値を算出するとともに、

前記第2の蓄電素子の電圧と前記蓄電素子電圧指令値との第2の電圧偏差を補償するための第2の電圧制御指令値を、前記基準出力電圧指令値から減算した値に従って前記第2の出力電圧指令値を算出し、

前記第1の電圧制御指令値は、前記第1の電圧偏差と、前記基準電流指令値との乗算に従って算出され、

前記第2の電圧制御指令値は、前記第2の電圧偏差と、前記基準電流指令値との乗算に従って算出される、請求項1〜5のいずれか1項に記載の電力変換器の試験装置。 - 前記配線は、前記第1の蓄電素子の負極と、前記第2の蓄電素子の負極との間を接続することによって、前記電力変換器と前記補助変換器との間を電気的に接続する、請求項1〜6のいずれか1項に記載の電力変換器の試験装置。

- 前記配線は、前記第1の蓄電素子の正極と、前記第2の蓄電素子の正極との間を接続することによって、前記電力変換器と前記補助変換器との間を電気的に接続する、請求項1〜6のいずれか1項に記載の電力変換器の試験装置。

- 前記電力変換器は、

直列接続された第3及び第4の主スイッチング素子をさらに有し、

前記第3及び第4の主スイッチング素子の直列接続体は、前記第1の蓄電素子と並列接続され、

前記補助変換器は、

直列接続された第3及び第4の補助スイッチング素子をさらに有し、

前記第3及び第4の補助スイッチング素子の直列接続体は、前記第2の蓄電素子と並列接続され、

前記配線は、前記第3及び第4の主スイッチング素子の接続ノードと、前記第3及び第4の補助スイッチング素子の接続ノードとの間を接続することによって、前記電力変換器と前記補助変換器との間を電気的に接続する、請求項1〜6のいずれか1項に記載の電力変換器の試験装置。 - 第1の端子を介して直列接続された第1及び第2の主スイッチング素子の直列接続体と、前記直列接続体と並列接続される第1の蓄電素子とを有する電力変換器の試験方法であって、

前記電力変換器は、配線を介して、第2の端子を介して直列接続された第1及び第2の補助スイッチング素子の直列接続体と、前記直列接続体と並列接続される第2の蓄電素子とを有する補助変換器と電気的に接続された状態で試験され、

前記第1及び第2の端子と接続された電流出力回路からの、交流電流指令値と直流電流指令値とが重畳された基準電流指令値に従う試験用電流の出力開始後、前記試験用電流の直流成分が予め定められたレベルに達するまでの間、還流動作を実行するステップと、

前記直流成分が前記予め定められたレベルに達した後に、蓄電素子電圧指令値に従った前記第1及び第2の蓄電素子の電圧の制御を少なくとも含む電圧制御のための前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子のオンオフ制御を開始するステップとを備え、

前記還流動作において、前記電力変換器及び前記補助変換器では、前記第1及び第2の蓄電素子を迂回した電流経路が前記第1及び第2の端子間に形成されるように、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子のオンオフが固定される、電力変換器の試験方法。 - 前記還流動作の実行前に、前記電流出力回路から直流成分を含まない交流電流が供給される状態の下で、前記第1及び第2の蓄電素子を充電するステップを更に備え、

前記充電するステップにおいて、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子はオフに固定され、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子の各々と逆並列に接続されたダイオードを経由する電流経路によって、前記第1及び第2の蓄電素子は充電される、請求項10記載の電力変換器の試験方法。 - 前記電流出力回路は、

前記第1及び第2の端子のそれぞれと電気的に接続される第1及び第2のテスト端子と、

複数のスイッチング素子を有し、当該複数のスイッチング素子のオンオフ制御によって、直流電圧を正のパルス電圧又は負のパルス電圧に変換して前記第1及び第2のテスト端子間に出力するヒステリシスコンバータと、

前記第1の端子及び前記第1のテスト端子の間、並びに、前記第2の端子及び前記第2のテスト端子の間との間の少なくとも一方に、前記試験用電流が通過するように接続されたリアクトルとを含み、

前記ヒステリシスコンバータは、前記正のパルス電圧の出力時に、前記試験用電流の検出値が、前記基準電流指令値よりも高く設定された上限電流指令値まで上昇すると前記負のパルス電圧の出力に切り替える一方で、前記負のパルス電圧の出力時には、前記試験用電流の検出値が、前記基準電流指令値よりも低く設定された下限電流指令値まで低下すると前記正のパルス電圧の出力に切り替えるように、前記複数のスイッチング素子のオンオフが制御される、請求項10記載の電力変換器の試験方法。 - 前記還流動作の前に、前記第1及び第2の蓄電素子の充電動作を実行するように、前記ヒステリシスコンバータ、前記電力変換器、及び、前記補助変換器を制御するステップを更に備え、

前記基準電流指令値と前記上限電流指令値との差の絶対値と、前記基準電流指令値と前記下限電流指令値との差の絶対値とは同一であるとともに、前記充電動作において、前記基準電流指令値はゼロに設定され、

前記充電動作において、前記電力変換器及び前記補助変換器では、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子がオフに固定されて、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子の各々と逆並列に接続されたダイオードを経由する電流経路によって、前記第1及び第2の蓄電素子が充電される、請求項12記載の電力変換器の試験方法。 - 前記還流動作の前に、前記第1及び第2の蓄電素子の充電動作を実行するように、前記ヒステリシスコンバータ、前記電力変換器、及び、前記補助変換器を制御するステップを更に備え、

前記充電動作において、前記基準電流指令値は設定されず、前記ヒステリシスコンバータは、前記正のパルス電圧を出力する第1の期間と、前記負のパルス電圧を出力する第2の期間とが、予め定められたそれぞれの期間長の比率に従って交互に出現するように、前記複数のスイッチング素子のオンオフが制御され、

前記充電動作において、前記電力変換器及び前記補助変換器では、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子がオフに固定されて、前記第1及び第2の主スイッチング素子並びに前記第1及び第2の補助スイッチング素子の各々と逆並列に接続されたダイオードを経由する電流経路によって、前記第1及び第2の蓄電素子が充電される、請求項12記載の電力変換器の試験方法。 - 前記電圧制御において、前記電力変換器では、前記第1の端子の出力電圧が、第1の出力電圧指令値に追従するように前記第1及び第2の主スイッチング素子のオンオフが制御されるとともに、前記補助変換器では、前記第2の端子の出力電圧が、第2の出力電圧指令値に追従するように前記第1及び第2の補助スイッチング素子のオンオフが制御され、

前記第1の出力電圧指令値は、前記電圧制御において、前記第1の蓄電素子の電圧と前記蓄電素子電圧指令値との第1の電圧偏差を補償するための第1の電圧制御指令値と、交流電圧指令値と直流電圧指令値とが重畳された基準出力電圧指令値とを加算した値に従って算出され、

前記第2の出力電圧指令値は、前記電圧制御において、前記第2の蓄電素子の電圧と前記蓄電素子電圧指令値との第2の電圧偏差を補償するための第2の電圧制御指令値を、前記基準出力電圧指令値から減算した値に従って算出され、

前記第1の電圧制御指令値は、前記第1の電圧偏差と、前記基準電流指令値との乗算に従って算出され、

前記第2の電圧制御指令値は、前記第2の電圧偏差と、前記基準電流指令値との乗算に従って算出される、請求項10〜14のいずれか1項に記載の電力変換器の試験方法。 - 前記還流動作を実行後における前記電圧制御の実行時において、前記基準電流指令値は、前記第1及び第2の端子の各々の出力電圧の指令値である基準出力電圧指令値と、前記基準電流指令値との積で示される瞬時電力を、前記基準電流指令値の基本波成分の一周期で積分した値が0になるように設定され、

前記基準出力電圧指令値は、交流電圧指令値と直流電圧指令値とが重畳されて設定される、請求項10〜15のいずれか1項に記載の電力変換器の試験方法。 - 前記基準電流指令値の瞬時値は、前記電流出力回路による前記試験用電流の出力開始時において0に設定される、請求項10〜16のいずれか1項に記載の電力変換器の試験方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2019/044417 WO2021095141A1 (ja) | 2019-11-12 | 2019-11-12 | 電力変換器の試験装置および試験方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP6719693B1 true JP6719693B1 (ja) | 2020-07-08 |

| JPWO2021095141A1 JPWO2021095141A1 (ja) | 2021-11-25 |

Family

ID=71402373

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020517616A Active JP6719693B1 (ja) | 2019-11-12 | 2019-11-12 | 電力変換器の試験装置および試験方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20220397616A1 (ja) |

| EP (1) | EP4060883A4 (ja) |

| JP (1) | JP6719693B1 (ja) |

| WO (1) | WO2021095141A1 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP3905504A4 (en) * | 2018-12-25 | 2021-12-15 | Mitsubishi Electric Corporation | POWER CONVERSION DEVICE |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6192114B2 (ja) | 2014-06-26 | 2017-09-06 | 東芝三菱電機産業システム株式会社 | 変換器の試験方法及び試験装置 |

| JP6522141B2 (ja) * | 2015-09-17 | 2019-05-29 | 三菱電機株式会社 | 電力変換装置 |

| CN108051685A (zh) * | 2017-12-28 | 2018-05-18 | 中电普瑞电力工程有限公司 | 一种模块化多电平换流阀的稳态试验电路和方法 |

| JP6950554B2 (ja) * | 2018-02-06 | 2021-10-13 | トヨタ自動車株式会社 | 電力変換器 |

| JP6768993B1 (ja) * | 2019-12-02 | 2020-10-14 | 三菱電機株式会社 | 電力変換装置 |

| WO2021255866A1 (ja) * | 2020-06-17 | 2021-12-23 | 三菱電機株式会社 | 電力変換装置 |

-

2019

- 2019-11-12 JP JP2020517616A patent/JP6719693B1/ja active Active

- 2019-11-12 US US17/762,374 patent/US20220397616A1/en active Pending

- 2019-11-12 EP EP19952838.1A patent/EP4060883A4/en active Pending

- 2019-11-12 WO PCT/JP2019/044417 patent/WO2021095141A1/ja unknown

Also Published As

| Publication number | Publication date |

|---|---|

| US20220397616A1 (en) | 2022-12-15 |

| EP4060883A4 (en) | 2022-11-16 |

| JPWO2021095141A1 (ja) | 2021-11-25 |

| EP4060883A1 (en) | 2022-09-21 |

| WO2021095141A1 (ja) | 2021-05-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6815496B2 (ja) | 電力変換装置 | |

| JP6710810B2 (ja) | 三相コンバータ及び三相コンバータ制御方法 | |

| US10615636B2 (en) | Uninterruptible power supply | |

| JP5985775B1 (ja) | 単独運転検出装置及び単独運転検出方法 | |

| WO2007129456A1 (ja) | 電力変換装置 | |

| CN104935200A (zh) | 电力转换装置、其控制装置及控制方法、发电系统 | |

| Srikanthan et al. | Improved hysteresis current control of three-level inverter for distribution static compensator application | |

| WO2015102049A1 (ja) | 電力変換装置 | |

| US9929676B2 (en) | Method for controlling three phase equivalent voltage of multilevel inverter | |

| KR101929519B1 (ko) | 불평형 커패시터 전압을 가지는 3 레벨 npc 인버터 시스템 및 그 제어 방법 | |

| JP5192258B2 (ja) | クランプ式電力変換装置 | |

| US20190190403A1 (en) | System-connected inverter device and method for operating same | |

| Xie et al. | Adaptive power decoupling control for single-phase converter with unbalanced DC-split-capacitor circuit | |

| JP6538544B2 (ja) | 自励式無効電力補償装置 | |

| Jin et al. | Virtual vector-based FCS-MPC for NPC three-level grid-tied inverter without weighting factor of neutral-point voltage balancing | |

| JP6396135B2 (ja) | 電力変換装置 | |

| JP6719693B1 (ja) | 電力変換器の試験装置および試験方法 | |

| JP4365376B2 (ja) | 電力変換装置 | |

| JP2013230027A (ja) | 交流電源システム | |

| Salim et al. | Three-level (NPC) shunt active power filter performances based on fuzzy controller for harmonic currents compensation under non-ideal voltage conditions | |

| CN115425861A (zh) | 多电平逆变电路的控制方法和并网逆变器 | |

| JP2015107043A (ja) | 電力変換装置及び制御装置 | |

| Changizian et al. | A novel FPGA control scheme to improve power factor and reduce the harmonic distortion in a three phase VIENNA rectifier | |

| Ramos et al. | Complex state-space current controller for grid-connected converters with an LCL filter | |

| TWI578655B (zh) | 電壓平衡控制系統及其方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200326 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200326 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20200326 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20200514 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200519 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200616 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6719693 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |