以下、本発明の一実施形態を図面を参照して説明する。

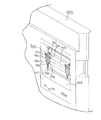

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機を正面からみた正面図、図2は遊技盤の前面を示す正面図である。なお、以下の実施の形態では、パチンコ遊技機を例に説明を行うが、本発明による遊技機はパチンコ遊技機に限られず、スロット機などの他の遊技機に適用することもできる。

Hereinafter, an embodiment of the present invention will be described with reference to the drawings.

First, the entire configuration of a pachinko gaming machine, which is an example of a gaming machine, will be described. FIG. 1 is a front view of the pachinko gaming machine as viewed from the front, and FIG. 2 is a front view showing the front of the game board. In the following embodiments, a pachinko gaming machine is described as an example, but the gaming machine according to the present invention is not limited to a pachinko gaming machine, and can be applied to other gaming machines such as slot machines.

パチンコ遊技機1は、縦長の方形状に形成された外枠(図示せず)と、外枠の内側に開閉可能に取り付けられた遊技枠とで構成される。また、パチンコ遊技機1は、遊技枠に開閉可能に設けられている額縁状に形成されたガラス扉枠2を有する。遊技枠は、外枠に対して開閉自在に設置される前面枠(図示せず)を備え、前面枠には機構部品等が取り付けられる機構板が取り付けられる。また、前面枠にも、種々の部品が取り付けられる。

The pachinko gaming machine 1 is configured of an outer frame (not shown) formed in a vertically-long rectangular shape and a game frame attached to the inside of the outer frame so as to be openable and closable. In addition, the pachinko gaming machine 1 has a glass door frame 2 formed in a frame shape provided so as to be openable and closable in the game frame. The play space has a front frame (not shown) installed so as to be openable and closable with respect to the outer frame, and a mechanical plate to which mechanical parts and the like are attached is attached to the front frame. Also, various parts can be attached to the front frame.

図1に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿(上皿)3がある。打球供給皿3の下部には、打球供給皿3に収容しきれない遊技球を貯留する余剰球受皿4と遊技球を発射する打球操作ハンドル(操作ノブ)5が設けられている。ガラス扉枠2の背面には、遊技盤6が着脱可能に取り付けられている。なお、遊技盤6は、それを構成する板状体と、その板状体に取り付けられた種々の部品とを含む構造体である。また、遊技盤6の前面には遊技領域7が形成されている。

As shown in FIG. 1, the pachinko gaming machine 1 has a glass door frame 2 formed in a frame shape. On the lower surface of the glass door frame 2, there is a hitting ball supply plate (upper plate) 3. At the lower part of the hit ball supply tray 3, there are provided a surplus ball receiver 4 for storing game balls which can not be accommodated in the hit ball supply tray 3 and a hit ball operation handle (operation knob) 5 for firing the game balls. A game board 6 is removably attached to the back of the glass door frame 2. The game board 6 is a structure including a plate-like body that constitutes the game board and various components attached to the plate-like body. In addition, a game area 7 is formed on the front of the game board 6.

遊技領域7の中央付近には、それぞれが演出用の飾り図柄(演出図柄)を可変表示する複数の可変表示部を含む演出表示装置(飾り図柄表示装置)9が設けられている。演出表示装置9には、例えば「左」、「中」、「右」の3つの可変表示部(図柄表示エリア)がある。演出表示装置9は、特別図柄表示器8による特別図柄の可変表示期間中に、装飾用(演出用)の図柄としての演出図柄の可変表示を行う。演出図柄の可変表示を行う演出表示装置9は、演出制御基板に搭載されている演出制御用マイクロコンピュータによって制御される。

In the vicinity of the center of the game area 7, there is provided an effect display device (decorative symbol display device) 9 including a plurality of variable display portions each of which variably displays a decorative symbol (rendering symbol) for effect. The effect display device 9 has, for example, three variable display portions (symbol display areas) of “left”, “middle” and “right”. During the variable display period of the special symbol by the special symbol display 8, the effect display device 9 performs the variable display of the effect symbol as a symbol for decoration (for effect). The effect display device 9 that performs variable display of the effect pattern is controlled by the effect control microcomputer mounted on the effect control board.

演出表示装置9の下部には、始動入賞口14に入った有効入賞球数すなわち保留記憶(始動記憶または始動入賞記憶ともいう。)数を表示する4つの特別図柄保留記憶表示器18が設けられている。特別図柄保留記憶表示器18は、保留記憶数を入賞順に4個まで表示する。特別図柄保留記憶表示器18は、始動入賞口14に始動入賞があるごとに、点灯状態のLEDの数を1増やす。そして、特別図柄保留記憶表示器18は、特別図柄表示器8で可変表示が開始されるごとに、点灯状態のLEDの数を1減らす(すなわち1つのLEDを消灯する)。具体的には、特別図柄保留記憶表示器18は、特別図柄表示器8で可変表示が開始されるごとに、点灯状態をシフトする。なお、この例では、始動入賞口14への入賞による始動記憶数に上限数(4個まで)が設けられているが、上限数を4個以上にしてもよい。

At the lower part of the effect display device 9, four special symbol hold storage indicators 18 are provided to display the number of activated winning balls that have entered the start winning opening 14, that is, the number of retention memories (also referred to as start memories or start prize memories). ing. The special symbol holding storage indicator 18 displays the number of holding storages up to four in the winning order. The special symbol holding memory indicator 18 increases the number of lighted LEDs by one each time the start winning opening 14 has a start winning. And each time the variable display is started by the special symbol display 8, the special symbol hold storage indicator 18 reduces the number of lighted LEDs by one (that is, turns off one LED). Specifically, the special symbol hold storage indicator 18 shifts the lighting state each time variable display is started by the special symbol indicator 8. In this example, although the upper limit number (up to four) is provided in the start memory number by the winning of the start winning opening 14, the upper limit number may be four or more.

演出表示装置9の上部には、識別情報としての特別図柄を可変表示する特別図柄表示器(特別図柄表示装置)8が設けられている。この実施の形態では、特別図柄表示器8は、例えば0〜9の数字を可変表示可能な簡易で小型の表示器(例えば7セグメントLED)で実現されている。特別図柄表示器8は、遊技者に特定の停止図柄を把握しづらくさせるために、0〜99など、より多種類の数字を可変表示するように構成されていてもよい。また、演出表示装置9は、特別図柄表示器8による特別図柄の可変表示期間中に、装飾用(演出用)の図柄としての演出図柄の可変表示を行う。

At the upper part of the effect display device 9, a special symbol display (special symbol display device) 8 for variably displaying a special symbol as identification information is provided. In this embodiment, the special symbol display 8 is realized by a simple and small display (for example, a 7-segment LED) capable of variably displaying the numbers 0 to 9, for example. The special symbol display 8 may be configured to variably display more types of numbers, such as 0 to 99, in order to make it difficult for the player to grasp a specific stop symbol. Further, the effect display device 9 performs variable display of the effect pattern as a symbol for decoration (for effect) during a variable display period of the special symbol by the special symbol display 8.

演出表示装置9の下方には、始動入賞口14を形成する可変入賞球装置15が設けられている。可変入賞球装置15は、羽根を開閉可能に構成され、羽根が開放しているときに遊技球が入賞し易い状態(開状態)となり、羽根が開放していないとき(閉じているとき)に遊技球が入賞し難い状態(閉状態)となる。始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ14a(例えば、近接スイッチ)によって検出されるとともに、入賞確認スイッチ14b(例えば、フォトセンサ)によって検出される。なお、この実施の形態では、後述するように、始動口スイッチ14aによって遊技球が検出されたことにもとづいて、特別図柄の変動表示が開始され、賞球払出が実行される。また、後述するように、始動口スイッチ14aによる検出結果に加えて入賞確認スイッチ14bの検出結果にもとづいて異常入賞の発生の有無が判定され、異常入賞の発生を検出したことにもとづいてセキュリティ信号が外部出力される。また、可変入賞球装置15は、ソレノイド16によって開状態にされる。

Below the effect display device 9, a variable winning ball device 15 that forms the start winning hole 14 is provided. The variable winning ball device 15 is configured to be able to open and close the wings, and when the wings are open, the gaming ball is in a state (open state) where it is easy to win, and when the wings are not open (when closed). It becomes a state (closed state) where it is difficult for the game ball to win. The winning balls that have entered the starting winning opening 14 are guided to the back of the game board 6, detected by the starting opening switch 14a (for example, proximity switch), and detected by the winning confirmation switch 14b (for example, photosensor) . In this embodiment, as described later, based on the fact that the game ball has been detected by the starting opening switch 14a, the variable display of the special symbol is started, and the award ball payout is executed. Further, as described later, in addition to the detection result by the starting opening switch 14a, the presence or absence of the occurrence of the abnormal prize is determined based on the detection result of the prize confirmation switch 14b, and the security signal is Is output to the outside. Also, the variable winning ball device 15 is opened by the solenoid 16.

なお、可変入賞球装置15の真上に第1始動入賞口を設け、可変入賞球装置15を第2始動入賞口としてもよい。この場合、第1始動入賞口および第2始動入賞口のそれぞれについて、始動口スイッチ(例えば、近接スイッチ)を設けるとともに入賞確認スイッチ(例えば、フォトセンサ)を設けるようにしてもよい。そして、第1始動入賞口および第2始動入賞口のそれぞれについて、この実施の形態と同様に、始動口スイッチによって遊技球が検出されたことにもとづいて、特別図柄の変動表示が開始され、賞球払出が実行されるようにしてもよい。また、第1始動入賞口および第2始動入賞口のそれぞれについて、この実施の形態と同様に、始動口スイッチによる検出結果に加えて入賞確認スイッチの検出結果にもとづいて異常入賞の発生の有無が判定され、異常入賞の発生を検出したことにもとづいてセキュリティ信号が外部出力されるようにしてもよい。

The first starting winning opening may be provided immediately above the variable winning ball device 15, and the variable winning ball device 15 may be used as a second starting winning opening. In this case, for each of the first starting winning opening and the second starting winning opening, a starting opening switch (for example, a proximity switch) may be provided and a winning confirmation switch (for example, a photo sensor) may be provided. Then, for each of the first starting winning opening and the second starting winning opening, the variation display of the special symbol is started based on the detection of the gaming ball by the starting opening switch as in this embodiment, and the prize Ball dispensing may be performed. Further, for each of the first starting winning opening and the second starting winning opening, in the same manner as in this embodiment, the presence or absence of occurrence of abnormal winning based on the detection result of the winning confirmation switch in addition to the detection result by the starting opening switch The security signal may be externally output based on the determination and the detection of the occurrence of the abnormal winning.

可変入賞球装置15の下部には、特定遊技状態(大当り状態)においてソレノイド21によって開状態に制御される開閉板を用いた特別可変入賞球装置20が設けられている。特別可変入賞球装置20は大入賞口を開閉する手段である。特別可変入賞球装置20に入賞し遊技盤6の背面に導かれた入賞球は、カウントスイッチ23で検出される。

At the lower part of the variable winning ball device 15, a special variable winning ball device 20 using an open / close plate controlled to an open state by the solenoid 21 in the specific gaming state (big hit state) is provided. The special variable winning prize ball device 20 is means for opening and closing the big prize winning opening. The winning ball that has won the special variable winning ball device 20 and is led to the back of the gaming board 6 is detected by the count switch 23.

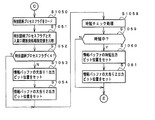

なお、この実施の形態では、始動入賞口14にのみ、始動口スイッチ14aに加えて入賞確認スイッチ14bを設ける場合を示しているが、大入賞口にも、カウントスイッチ23に加えて入賞確認スイッチを備えるようにしてもよい。この場合、例えば、始動入賞口14と同様に、カウントスイッチ13を近接スイッチを用いて構成し、入賞確認スイッチをフォトセンサを用いて構成するようにすればよい(なお、逆に、カウントスイッチ13をフォトセンサを用いて構成し、入賞確認スイッチを近接スイッチを用いて構成してもよいし、近接スイッチやフォトセンサに代えてマイクロスイッチなどの機械式のスイッチを用いてもよい)。また、遊技制御用マイクロコンピュータは、大入賞口への遊技球の入賞にもとづく賞球払出処理については、カウントスイッチ23の検出結果にのみもとづいて賞球の払い出しを行うようにすればよい(ステップS32参照)。一方で、遊技制御用マイクロコンピュータは、大入賞口への異常入賞を行う場合には、カウントスイッチ23の検出結果と入賞確認スイッチの検出結果との両方に基づいて判定を行うようにすればよい。この場合、例えば、遊技制御用マイクロコンピュータは、後述するスイッチ正常/異常チェック処理と同様の処理に従って、カウントスイッチ23の検出数と入賞確認スイッチの検出数との差が所定値(例えば、10)以上となったことにもとづいて、大入賞口への異常入賞が発生したと判定するようにすればよい(ステップS121〜S126参照)。

In this embodiment, only the start winning opening 14 is provided with the winning confirmation switch 14b in addition to the starting opening switch 14a. However, the winning confirmation switch is added to the count switch 23 also in the special winning opening. May be provided. In this case, for example, similarly to the start winning hole 14, the count switch 13 may be configured using a proximity switch, and the winning confirmation switch may be configured using a photo sensor (conversely, the count switch 13). May be configured using a photo sensor, and the winning confirmation switch may be configured using a proximity switch, or a mechanical switch such as a micro switch may be used instead of the proximity switch or the photo sensor). In addition, the game control microcomputer may pay out the winning balls based only on the detection result of the count switch 23 for the winning ball payout processing based on the winning of the gaming ball to the big winning opening (Step See S32). On the other hand, the microcomputer for game control may make a determination based on both of the detection result of the count switch 23 and the detection result of the prize confirmation switch when performing an abnormal prize to the special prize port. . In this case, for example, in the game control microcomputer, the difference between the number of detections of the count switch 23 and the number of detections of the winning confirmation switches is a predetermined value (for example, 10) according to the same processing as the switch normal / abnormality check processing described later Based on the above, it may be determined that an abnormal winning to the special winning opening has occurred (see steps S121 to S126).

遊技球がゲート32を通過しゲートスイッチ32aで検出されると、普通図柄表示器10の表示の可変表示が開始される。この実施の形態では、左右のランプ(点灯時に図柄が視認可能になる)が交互に点灯することによって可変表示が行われ、例えば、可変表示の終了時に左側のランプが点灯すれば当たりになる。そして、普通図柄表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定回数、所定時間だけ開状態になる。普通図柄表示器10の近傍には、ゲート32を通過した入賞球数を表示する4つのLEDによる表示部を有する普通図柄始動記憶表示器41が設けられている。ゲート32への遊技球の通過があるごとに、普通図柄始動記憶表示器41は点灯するLEDを1増やす。そして、普通図柄表示器10の可変表示が開始されるごとに、点灯するLEDを1減らす。

When the game ball passes through the gate 32 and is detected by the gate switch 32a, the variable display of the display of the normal symbol display 10 is started. In this embodiment, the variable display is performed by alternately turning on the left and right lamps (the symbols become visible when lit). For example, if the left lamp is turned on at the end of the variable display, it is a hit. Then, when the stop symbol in the normal symbol display 10 is a predetermined symbol (hit symbol), the variable winning ball device 15 is opened for a predetermined number of times and for a predetermined time. In the vicinity of the normal symbol display 10, a normal symbol start memory indicator 41 having a display unit with four LEDs for displaying the number of winning balls having passed through the gate 32 is provided. Each time there is a passage of the game ball to the gate 32, the normal symbol start memory indicator 41 increases the number of LEDs to be lit by one. Then, every time variable display of the normal symbol display 10 is started, the number of LEDs to be lit is reduced by one.

遊技盤6には、複数の入賞口29,30が設けられ、遊技球の入賞口29,30への入賞は、それぞれ入賞口スイッチ29a,30aによって検出される。各入賞口29,30は、遊技媒体を受け入れて入賞を許容する領域として遊技盤6に設けられる入賞領域を構成している。なお、始動入賞口14や大入賞口も、遊技媒体を受け入れて入賞を許容する入賞領域を構成する。なお、各入賞口29,30に入賞した遊技球を入賞スイッチで検出する構成に代えて、遊技球が所定領域(例えばゲート)を通過したことを検出スイッチで検出する構成としてもよい。遊技領域7の左右周辺には、遊技中に点滅表示される装飾ランプ25が設けられ、下部には、入賞しなかった遊技球を吸収するアウト口26がある。また、遊技領域7の外側の左右上部には、効果音を発する2つのスピーカ27が設けられている。遊技領域7の外周には、天枠ランプ28a、左枠ランプ28bおよび右枠ランプ28cが設けられている。さらに、遊技領域7における各構造物(大入賞口等)の周囲には装飾LEDが設置されている。天枠ランプ28a、左枠ランプ28bおよび右枠ランプ28cおよび装飾用LEDは、遊技機に設けられている装飾発光体の一例である。なお、この実施の形態では、遊技機に設けられている発光体をランプやLEDを用いて構成する場合を示しているが、この実施の形態で示した態様にかぎらず、例えば、遊技機に設けられている発光体を全てLEDを用いて構成するようにしてもよい。

A plurality of winning openings 29, 30 are provided on the game board 6, and the winnings on the winning openings 29, 30 of the gaming balls are detected by the winning opening switches 29a, 30a, respectively. The respective winning openings 29, 30 constitute a winning area provided on the game board 6 as an area for accepting gaming media and allowing winning. The start winning opening 14 and the big winning opening also constitute a winning area for accepting gaming media and allowing winning. It should be noted that instead of the configuration in which the game balls that have won in each of the winning openings 29 and 30 are detected by the prize switch, the detection switch may detect that the game ball has passed a predetermined area (for example, a gate). On the left and right peripheries of the game area 7, a decoration lamp 25 which blinks during the game is provided, and at the lower part, there is an out port 26 for absorbing the game ball which has not won. In addition, two speakers 27 that emit sound effects are provided on the upper left and right of the game area 7. On the outer periphery of the game area 7, a sky lamp 28a, a left frame lamp 28b and a right frame lamp 28c are provided. Furthermore, decoration LED is installed around each structure (big winning opening etc) in the game area 7. The sky lamp 28a, the left frame lamp 28b, the right frame lamp 28c, and the decorative LED are examples of a decorative light-emitting body provided in a game machine. Although this embodiment shows the case where the light-emitting body provided in the gaming machine is configured using a lamp or an LED, the invention is not limited to the mode shown in this embodiment, and, for example, All of the provided light emitters may be configured using LEDs.

なお、図1および図2では、図示を省略しているが、左枠ランプ28bの近傍に、賞球払出中に点灯する賞球ランプが設けられ、天枠ランプ28aの近傍に、補給球が切れたときに点灯する球切れランプが設けられている。なお、賞球ランプおよび球切れランプは、賞球の払出中である場合や球切れが検出された場合に、演出制御基板に搭載された演出制御用マイクロコンピュータによって点灯制御される。さらに、プリペイドカードが挿入されることによって球貸しを可能にするプリペイドカードユニット(以下、「カードユニット」という。)50が、パチンコ遊技機1に隣接して設置されている。

In addition, although illustration is abbreviate | omitted in FIG. 1 and FIG. 2, the prize ball lamp lighted during award ball payout is provided in the vicinity of the left frame lamp 28b, and the replenishment ball is provided in the vicinity of the sky lamp 28a. There is a bulb break lamp that lights up when it runs out. The prize ball lamp and the ball out lamp are controlled to be lighted by the effect control microcomputer mounted on the effect control board when the prize ball is being dispensed or when the ball out is detected. Further, a prepaid card unit (hereinafter referred to as a "card unit") 50 that enables a ball rental by inserting a prepaid card is installed adjacent to the pachinko gaming machine 1.

カードユニット50には、例えば、使用可能状態であるか否かを示す使用可表示ランプ、カードユニットがいずれの側のパチンコ遊技機1に対応しているのかを示す連結台方向表示器、カードユニット内にカードが投入されていることを示すカード投入表示ランプ、記録媒体としてのカードが挿入されるカード挿入口、およびカード挿入口の裏面に設けられているカードリーダライタの機構を点検する場合にカードユニットを解放するためのカードユニット錠が設けられている。

The card unit 50 has, for example, an available display lamp indicating whether or not it is usable, a coupling table direction indicator indicating on which side the pachinko gaming machine 1 corresponds to the card unit, and the card unit When checking the mechanism of the card insertion indicator lamp indicating that the card is inserted inside, the card insertion slot in which the card as the recording medium is inserted, and the back of the card insertion slot A card unit lock is provided to release the card unit.

遊技者の操作により打球発射装置から発射された遊技球は、打球レールを通って遊技領域7に入り、その後、遊技領域7を下りてくる。遊技球が始動入賞口14に入り始動口スイッチ14aで検出されると、図柄の可変表示を開始できる状態であれば、特別図柄表示器8において特別図柄が可変表示(変動)を始める。図柄の可変表示を開始できる状態でなければ、保留記憶数を1増やす。

The game balls fired from the hit ball launcher by the operation of the player enter the game area 7 through the hit rails, and then go down the game area 7. When the game ball enters the start winning opening 14 and is detected by the start opening switch 14a, the special symbol starts variable display (variation) in the special symbol display 8 if it can start variable display of the symbol. If it is not in a state where variable display of symbols can be started, the number of pending storages is increased by one.

特別図柄表示器8における特別図柄の可変表示は、一定時間が経過したときに停止する。停止時の特別図柄(停止図柄)が大当り図柄(特定表示結果)であると、大当り遊技状態に移行する。すなわち、特別可変入賞球装置20が、一定時間経過するまで、または、所定個数(例えば10個)の遊技球が入賞するまで開放する。そして、特別可変入賞球装置20の開放は、決定されたラウンド数の最後のラウンドまで(例えば、15ラウンドまで)許容される。

The variable display of the special symbol in the special symbol display 8 stops when a predetermined time has elapsed. When the special symbol (stop symbol) at the time of stop is the big hit symbol (specific display result), it shifts to the big hit game state. That is, the special variable winning prize ball device 20 is opened until a predetermined time passes or until a predetermined number (for example, 10) of gaming balls win. And, the release of the special variable winning prize ball device 20 is permitted until the last round of the determined number of rounds (for example, up to 15 rounds).

停止時の特別図柄表示器8における特別図柄が確率変動を伴う大当り図柄(確変図柄)である場合には、次に大当りになる確率が高くなる。すなわち、確変状態という遊技者にとってさらに有利な状態になる。

When the special symbol in the special symbol display 8 at the time of stop is the big hit symbol (probable variation symbol) with probability fluctuation, the probability of the next big hit becomes high. That is, it is more advantageous for the player of the probability change state.

遊技球がゲート32を通過すると、普通図柄表示器10において普通図柄が可変表示される状態になる。また、普通図柄表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定時間だけ開状態になる。

When the gaming ball passes through the gate 32, the normal symbol is variably displayed on the normal symbol display 10. Also, when the stop symbol in the normal symbol display 10 is a predetermined symbol (hit symbol), the variable winning ball device 15 is in an open state for a predetermined time.

次に、パチンコ遊技機1の裏面の構造について図3を参照して説明する。図3は、遊技機を裏面から見た背面図である。図3に示すように、パチンコ遊技機1裏面側では、演出表示装置9を制御する演出制御用マイクロコンピュータ100が搭載された演出制御基板80を含む変動表示制御ユニット、遊技制御用マイクロコンピュータ等が搭載された遊技制御基板(主基板)31、音声出力基板70、ランプドライバ基板35、および球払出制御を行なう払出制御用マイクロコンピュータ等が搭載された払出制御基板37等の各種基板が設置されている。なお、遊技制御基板31は基板収納ケース200に収納されている。

Next, the structure of the back surface of the pachinko gaming machine 1 will be described with reference to FIG. FIG. 3 is a rear view of the gaming machine as viewed from the rear. As shown in FIG. 3, on the back side of the pachinko gaming machine 1, a variable display control unit including a presentation control board 80 on which the presentation control microcomputer 100 for controlling the presentation display device 9 is mounted, a game control microcomputer, etc. Various boards such as a game control board (main board) 31 mounted, a voice output board 70, a lamp driver board 35, a payout control board 37 on which a payout control microcomputer for performing ball payout control, etc. are mounted are installed There is. The game control board 31 is stored in the board storage case 200.

さらに、パチンコ遊技機1裏面側には、DC30V、DC21V、DC12VおよびDC5V等の各種電源電圧を作成する電源回路が搭載された電源基板910やタッチセンサ基板91が設けられている。電源基板910には、パチンコ遊技機1における遊技制御基板31および各電気部品制御基板(演出制御基板80および払出制御基板37)やパチンコ遊技機1に設けられている各電気部品(電力が供給されることによって動作する部品)への電力供給を実行あるいは遮断するための電力供給許可手段としての電源スイッチ、遊技制御基板31の遊技制御用マイクロコンピュータ560のRAM55をクリアするためのクリアスイッチが設けられている。さらに、電源スイッチの内側(基板内部側)には、交換可能なヒューズが設けられている。

Further, on the back side of the pachinko gaming machine 1, there are provided a power supply substrate 910 and a touch sensor substrate 91 on which power supply circuits for generating various power supply voltages such as DC30V, DC21V, DC12V and DC5V are mounted. The power supply substrate 910 is supplied with the game control substrate 31 and the respective electric component control substrates (the effect control substrate 80 and the payout control substrate 37) in the pachinko gaming machine 1 and the respective electric components (power) provided in the pachinko gaming machine 1 A power switch as a power supply permission unit for executing or cutting off the power supply to the component (operating by), and a clear switch for clearing the RAM 55 of the game control microcomputer 560 of the game control board 31 ing. Furthermore, a replaceable fuse is provided inside the power switch (inside of the substrate).

なお、この実施の形態では、主基板31は遊技盤側に設けられ、払出制御基板37は遊技枠側に設けられている。このような構成であっても、後述するように、主基板31と払出制御基板37との間の通信をシリアル通信で行うことによって、遊技盤を交換する際の配線の取り回しを容易にしている。

In this embodiment, the main substrate 31 is provided on the game board side, and the payout control board 37 is provided on the game frame side. Even with such a configuration, as will be described later, the communication between the main board 31 and the payout control board 37 is performed by serial communication, thereby facilitating the arrangement of wiring when replacing the game board .

なお、各制御基板には、制御用マイクロコンピュータを含む制御手段が搭載されている。制御手段は、遊技制御手段等からのコマンドとしての指令信号(制御信号)に従って遊技機に設けられている電気部品(遊技用装置:球払出装置97、演出表示装置9、ランプやLEDなどの発光体、スピーカ27等)を制御する。以下、主基板31を制御基板に含めて説明を行うことがある。その場合には、制御基板に搭載される制御手段は、遊技制御手段と、遊技制御手段等からの指令信号に従って遊技機に設けられている電気部品を制御する手段とのそれぞれを指す。また、主基板31以外のマイクロコンピュータが搭載された基板をサブ基板ということがある。なお、球払出装置97は、遊技球を誘導する通路とステッピングモータ等により駆動されるスプロケット等によって誘導された遊技球を上皿や下皿に払い出すための装置であって、払い出された賞球や貸し球をカウントする払出個数カウントスイッチ等もユニットの一部として構成されている。なお、この実施の形態では、払出検出手段は、払出個数カウントスイッチ301によって実現され、球払出装置97から実際に賞球や貸し球が払い出されたことを検出する機能を備える。この場合、払出個数カウントスイッチ301は、賞球や貸し球の払い出しを1球検出するごとに検出信号を出力する。

Control means including a control microcomputer is mounted on each control board. The control means is an electric component provided in the gaming machine according to a command signal (control signal) as a command from the game control means or the like (gaming device: light emitting device such as ball payout device 97, effect display device 9, lamp or LED) Control the body, speaker 27 etc.). Hereinafter, the main substrate 31 may be included in the control substrate to be described. In that case, the control means mounted on the control board refers to each of the game control means and the means for controlling the electric components provided in the game machine according to the command signal from the game control means or the like. Moreover, the board | substrate with which microcomputers other than the main board | substrate 31 were mounted may be called a sub board | substrate. The ball payout device 97 is a device for paying out, to the upper plate or the lower plate, the gaming ball induced by the passage for guiding the gaming ball and the sprocket driven by the stepping motor or the like. A prize ball, a payout number counting switch for counting the lent balls, and the like are also configured as part of the unit. In this embodiment, the payout detecting means is realized by the payout number counting switch 301, and has a function of detecting that the winning balls and the rental balls are actually paid out from the ball payout device 97. In this case, the payout number counting switch 301 outputs a detection signal each time one payout of a winning ball or a rental ball is detected.

パチンコ遊技機1裏面において、上方には、各種情報をパチンコ遊技機1の外部に出力するための各端子を備えたターミナル基板160が設置されている。ターミナル基板160には、例えば、大当り遊技状態の発生を示す大当り情報等の情報出力信号(図60に示す始動口信号、図柄確定回数1信号、大当り1信号、大当り2信号、大当り3信号、時短信号、セキュリティ信号、賞球信号1、遊技機エラー状態信号)を外部出力するための情報出力端子が設けられている。

A terminal board 160 provided with terminals for outputting various information to the outside of the pachinko gaming machine 1 is installed on the upper side of the back of the pachinko gaming machine 1. Terminal board 160, for example, information output signal such as big hit information indicating occurrence of big hit gaming state (start opening signal shown in FIG. 60, symbol determination number 1 signal, big hit 1 signal, big hit 2 signal, big hit 3 signal, hour An information output terminal is provided to externally output a short signal, a security signal, a prize ball signal 1, and a gaming machine error state signal).

貯留タンク38に貯留された遊技球は誘導レール(図示せず)を通り、カーブ樋を経て払出ケース40Aで覆われた球払出装置97に至る。球払出装置97の上方には、遊技媒体切れ検出手段としての球切れスイッチ187が設けられている。球切れスイッチ187が球切れを検出すると、球払出装置97の払出動作が停止する。球切れスイッチ187は遊技球通路内の遊技球の有無を検出するスイッチであるが、貯留タンク38内の補給球の不足を検出する球切れ検出スイッチ167も誘導レールにおける上流部分(貯留タンク38に近接する部分)に設けられている。球切れ検出スイッチ167が遊技球の不足を検知すると、遊技機設置島に設けられている補給機構からパチンコ遊技機1に対して遊技球の補給が行なわれる。

The game balls stored in the storage tank 38 pass through a guiding rail (not shown), pass through a curved weir, and reach the ball dispensing device 97 covered by the dispensing case 40A. Above the ball payout device 97, a ball out switch 187 is provided as a game medium out detection means. When the ball breakage switch 187 detects the ball breakage, the dispensing operation of the ball dispensing device 97 is stopped. The out-of-ball switch 187 is a switch for detecting the presence or absence of a game ball in the game ball passage, but the out-of-ball detection switch 167 for detecting a shortage of supply balls in the storage tank 38 is also an upstream portion of the guide rail It is provided in the adjacent part). When the out-of-ball detection switch 167 detects a shortage of gaming balls, the gaming mechanism is replenished to the pachinko gaming machine 1 from the replenishment mechanism provided on the gaming machine installation island.

入賞にもとづく景品としての遊技球や球貸し要求にもとづく遊技球が多数払出されて打球供給皿3が満杯になると、遊技球は、余剰球誘導通路を経て余剰球受皿4に導かれる。さらに遊技球が払出されると、感知レバー(図示せず)が貯留状態検出手段としての満タンスイッチを押圧して、貯留状態検出手段としての満タンスイッチがオンする。その状態では、球払出装置内の払出モータの回転が停止して球払出装置の動作が停止するとともに打球発射装置の駆動も停止する。

When a large number of gaming balls as prizes based on the prize and a gaming ball based on a ball lending request are paid out and the hitting ball supply tray 3 becomes full, the gaming balls are guided to the surplus ball tray 4 through the surplus ball guiding passage. Further, when the gaming ball is paid out, the sensing lever (not shown) presses the full tank switch as the storage state detection means, and the full tank switch as the storage state detection means is turned on. In that state, the rotation of the dispensing motor in the ball dispensing device is stopped, the operation of the ball dispensing device is stopped, and the driving of the ball striking device is also stopped.

また、図3に示すように、前面枠の上方には、扉体(この例では、ガラス扉枠2)の状態(遊技領域7を覆う閉鎖状態または遊技領域7を外部から接触可能な状態にする開放状態)を検出(具体的には、前面に遊技領域7が形成されている遊技盤6が取り付けられた前面枠に対してガラス扉枠2が開放されたか否かを検出)するためのドア開放センサ155が取り付けられている。

In addition, as shown in FIG. 3, the state of the door (in this example, the glass door frame 2) above the front frame (the closed state covering the game area 7 or the game area 7 can be contacted from the outside) To detect an open state) (specifically, it is detected whether the glass door frame 2 is opened with respect to the front frame to which the game board 6 having the game area 7 formed on the front surface is attached) A door open sensor 155 is attached.

図4は、始動入賞口14内の断面構造の具体例を示す説明図である。図4に示すように、始動入賞口14内には、始動入賞口内に入賞した遊技球を検出可能な2つのスイッチ(始動口スイッチ14aと入賞確認スイッチ14b)が設けられている。この実施の形態では、図4に示すように、始動入賞口14内で、始動口スイッチ14aと入賞確認スイッチ14bとが上下に配置されている(本例では、始動口スイッチ14aが上側に配置され、入賞確認スイッチ14bが下側に配置されている)。従って、この実施の形態では、始動入賞口14内に入賞した遊技球は、遊技盤6の背面に導かれ、まず始動口スイッチ14aで検出され、次いで入賞確認スイッチ14bで検出される。

FIG. 4 is an explanatory view showing a specific example of the sectional structure in the start winning hole 14. As shown in FIG. 4, in the start winning opening 14, two switches (a starting opening switch 14a and a winning confirmation switch 14b) capable of detecting the game ball having won in the start winning opening are provided. In this embodiment, as shown in FIG. 4, the starting opening switch 14a and the winning a prize confirmation switch 14b are arranged vertically in the starting winning opening 14 (in this example, the starting opening switch 14a is arranged on the upper side) And the prize confirmation switch 14b is disposed on the lower side). Therefore, in this embodiment, the gaming ball having won a prize in the start winning opening 14 is guided to the back of the gaming board 6, first detected by the starting opening switch 14a, and then detected by the winning confirmation switch 14b.

また、始動口スイッチ14aと入賞確認スイッチ14bとして、それぞれ異なる検出方式のスイッチが用いられる。この実施の形態では、始動口スイッチ14aとして近接スイッチを用い、入賞確認スイッチ14bとしてフォトセンサを用いる場合を示している。

Further, switches of different detection methods are used as the starting opening switch 14a and the winning a prize confirmation switch 14b. In this embodiment, a proximity switch is used as the starting opening switch 14a, and a photo sensor is used as the winning confirmation switch 14b.

また、この実施の形態では、後述するように、始動口スイッチ14aによって遊技球が検出されたことにもとづいて、特別図柄の変動表示が開始され、賞球払出が実行される。また、後述するように、始動口スイッチ14aによる検出結果に加えて入賞確認スイッチ14bの検出結果にもとづいて異常入賞の発生の有無が判定され、異常入賞の発生を検出したことにもとづいてセキュリティ信号が外部出力される。従って、この実施の形態では、入賞確認スイッチ14bは、異常入賞の判定のみに用いられる。なお、遊技球が始動口スイッチ14aによって検出されても、特別図柄の変動表示が開始されるが、景品払出を生じさせないように構成されていてもよい。その場合には始動口は、景品払出を伴う入賞領域ではなく、遊技球が進入する領域である進入領域(そこを通過しても景品払出を伴わない。)である。また、入賞領域および進入領域を特定領域または通過領域とする。

Further, in this embodiment, as described later, based on the fact that the game ball has been detected by the starting opening switch 14a, the variable display of the special symbol is started, and the award ball payout is executed. Further, as described later, in addition to the detection result by the starting opening switch 14a, the presence or absence of the occurrence of the abnormal prize is determined based on the detection result of the prize confirmation switch 14b, and the security signal is Is output to the outside. Therefore, in this embodiment, the winning a prize confirmation switch 14b is used only for the determination of the abnormal winning. In addition, although the game ball is detected by the starting opening switch 14a, the variable display of the special symbol is started, but it may be configured so as not to generate a prize payout. In that case, the starting opening is not a winning area accompanied by a prize payout but an entry area where the gaming ball enters (even if there is no prize payout even if passing there). In addition, the winning area and the entry area are designated as a specific area or a passing area.

また、始動口スイッチ14aおよび入賞確認スイッチ14bの検出方式は、この実施の形態で示したものにかぎらず、例えば、始動口スイッチ14aと入賞確認スイッチ14bとで異なる検出方式であれば、逆に始動口スイッチ14aとしてフォトセンサを用い、入賞確認スイッチ14bとして近接スイッチを用いてもよい。この場合、フォトセンサである始動口スイッチ14aの検出結果にもとづいて特別図柄の変動表示や賞球払出処理が実行され、近接スイッチである入賞確認スイッチ14bの検出結果は、始動入賞口14の異常入賞の判定のみに用いられることになる。また、例えば、電磁式のスイッチである近接スイッチや光学式のフォトセンサに代えて、始動口スイッチ14aまたは入賞確認スイッチ14bとして、機械式のスイッチ(マイクロスイッチなど)を用いてもよい。

Further, the detection method of the starting opening switch 14a and the winning a prize confirmation switch 14b is not limited to that shown in this embodiment, for example, if it is a detection method different between the starting opening switch 14a and the winning affirmation confirmation switch 14b, reversely. A photosensor may be used as the starting opening switch 14a, and a proximity switch may be used as the winning confirmation switch 14b. In this case, the variation display of the special symbol and the prize ball payout processing are executed based on the detection result of the start opening switch 14a which is a photo sensor, and the detection result of the winning a prize confirmation switch 14b which is a proximity switch is an abnormality of the start winning opening 14 It will be used only for winning determination. For example, instead of the proximity switch or the optical photosensor which is an electromagnetic switch, a mechanical switch (micro switch or the like) may be used as the starting opening switch 14a or the prize confirmation switch 14b.

図5は、遊技球を検出可能な検出手段の方式を説明するための回路図である。図5(A)には、始動口スイッチ14a(近接スイッチ)が示されている。始動口スイッチ14aの一方の端子には、電源基板910から+12V電源電圧が供給されている。始動口スイッチ14aの他方の端子の電圧レベルである検出信号は、主基板31に入力される。主基板31において、検出信号は、入力ドライバ回路から遊技制御用マイクロコンピュータの入力ポートに入力される。また、始動口スイッチ14aの出力側には、一端が接地されている抵抗RとコンデンサCが接続されている。

FIG. 5 is a circuit diagram for explaining a method of detecting means capable of detecting a game ball. The starting opening switch 14a (proximity switch) is shown by FIG. 5 (A). The +12 V power supply voltage is supplied from the power supply substrate 910 to one terminal of the start port switch 14a. A detection signal which is a voltage level of the other terminal of the start port switch 14 a is input to the main substrate 31. In the main board 31, the detection signal is inputted from the input driver circuit to the input port of the game control microcomputer. Further, a resistor R and a capacitor C, one end of which is grounded, are connected to the output side of the start port switch 14a.

近接スイッチである始動口スイッチ14aに設けられている穴を金属の遊技球が通過するとコイルLに逆起電力が生じ、コイルLの等価的な抵抗値が極めて大きくなる。従って、始動口スイッチ14aの出力は、0Vに近いローレベルになる。すなわち、検出信号は、ローレベルである。始動口スイッチ14aに設けられている穴を金属の遊技球が通過していない場合には、始動口スイッチ14aの出力は、+12VがコイルLと抵抗Rの抵抗値で分圧された値であり、ハイレベルであるとみなされるしきい値レベルを越える。すなわち、検出信号は、ハイレベルである。従って、この実施の形態では、遊技制御用マイクロコンピュータは、始動口スイッチ14aからの出力がハイレベルであれば始動口スイッチ14aがオフ状態であると判断することができ、始動口スイッチ14aからの出力がローレベルであれば始動口スイッチ14aがオン状態であると判断することができる(すなわち、始動口スイッチ14aの出力は負論理となっている)。なお、検出信号のレベルを入力ドライバ回路で論理反転してから遊技制御用マイクロコンピュータ560に入力するように構成してもよい。

When a metal game ball passes through a hole provided in the starting opening switch 14a which is a proximity switch, a back electromotive force is generated in the coil L, and the equivalent resistance value of the coil L becomes extremely large. Therefore, the output of the start port switch 14a becomes low level close to 0V. That is, the detection signal is at the low level. When the metal game ball does not pass through the hole provided in the starting opening switch 14a, the output of the starting opening switch 14a is a value obtained by dividing +12 V by the resistance value of the coil L and the resistance R and , A threshold level considered to be high level is exceeded. That is, the detection signal is at high level. Therefore, in this embodiment, the microcomputer for game control can judge that the start opening switch 14a is in the off state if the output from the start opening switch 14a is at high level, and the microcomputer from the start opening switch 14a If the output is low, it can be determined that the start port switch 14a is in the on state (ie, the output of the start port switch 14a has a negative logic). The level of the detection signal may be logically inverted by the input driver circuit and then input to the game control microcomputer 560.

図5(B)には、入賞確認スイッチ14b(フォトセンサ)が示されている。図5(B)に示すフォトセンサは、発光する発光ダイオード(LED)341と、受光して電流を出力するフォトトランジスタ342とで構成されている。発光ダイオード341およびフォトトランジスタ342の近傍を遊技球が通過すると、遊技球が反射した発光ダイオード341からの光をフォトトランジスタ342が受光して出力側に電流を流す。なお、この場合、フォトトランジスタ342のコレクタ端子からエミッタ端子の向きに電流が流れることにより、フォトセンサの検出信号は、近接スイッチと同様に負論理である。フォトセンサの出力側は主基板31に接続され、主基板31において、フォトセンサの検出信号は、入力ドライバ回路から遊技制御用マイクロコンピュータの入力ポートに入力される。フォトセンサの出力側(具体的には、フォトトランジスタ342の出力側)に電流が流れると、入力ドライバ回路は、ハイレベルの検出信号を遊技制御用マイクロコンピュータに出力する。なお、近接スイッチと同様に、検出信号のレベルを入力ドライバ回路で論理反転してから遊技制御用マイクロコンピュータ560に入力するように構成してもよい。

The winning a prize confirmation switch 14b (photo sensor) is shown by FIG. 5 (B). The photosensor illustrated in FIG. 5B includes a light emitting diode (LED) 341 that emits light, and a phototransistor 342 that receives light and outputs a current. When the gaming ball passes near the light emitting diode 341 and the photo transistor 342, the photo transistor 342 receives the light from the light emitting diode 341 reflected by the gaming ball and causes a current to flow on the output side. In this case, the current flows from the collector terminal of the phototransistor 342 in the direction of the emitter terminal, and the detection signal of the photo sensor has a negative logic as in the proximity switch. The output side of the photo sensor is connected to the main board 31, and on the main board 31, the detection signal of the photo sensor is inputted from the input driver circuit to the input port of the game control microcomputer. When a current flows to the output side of the photosensor (specifically, the output side of the phototransistor 342), the input driver circuit outputs a high level detection signal to the game control microcomputer. As in the proximity switch, the level of the detection signal may be logically inverted by the input driver circuit and then input to the game control microcomputer 560.

遊技制御用マイクロコンピュータは、入力ドライバ回路からの検出信号がローレベルである場合に、遊技球がフォトセンサを通過したと判定することができる。

The game control microcomputer can determine that the game ball has passed the photo sensor when the detection signal from the input driver circuit is at a low level.

なお、この実施の形態では、フォトセンサとして反射型のフォトセンサが用いられるが、図5(C)における上段に示すように、発光素子(LED341)と受光素子(フォトトランジスタ342)とを入賞球経路を挟むように対向させて設置し、遊技球が発光素子からの光を遮ることによって受光素子が光を検出しなくなることによって、発光素子と受光素子との間を通過した遊技球を検出する透過型のフォトセンサを用いてもよい。透過型のフォトセンサを用いる場合に、図5(C)における下段に示すように、発光素子の光軸(図5(C)において黒丸で例示されている。)が、遊技球経路(入賞球経路)を通過する遊技球の中央部からずれるように、発光素子および受光素子を設置することが好ましい。光軸が遊技球の中央部に相当するように設置する場合に比べて、連続して通過する2つの遊技球の間隔が相対的に広い部分(図5(C)における「空隙」の部分)において遊技球を検知することができ、2つの遊技球を別個に検出しやすいからである。同様の理由で、図5(B)に例示する反射型のフォトセンサを用いる場合にも、発光素子からの光の反射点が遊技球の中央部からずれるように、発光素子および受光素子を設置することが好ましい。

In this embodiment, a reflection type photosensor is used as the photosensor, but as shown in the upper part of FIG. 5C, the light emitting element (LED 341) and the light receiving element (phototransistor 342) are winning balls. The game balls are placed facing each other so as to sandwich the path, and the game ball intercepts the light from the light emitting element so that the light receiving element does not detect the light, thereby detecting the game ball passed between the light emitting element and the light receiving element A transmissive photosensor may be used. When a transmission type photo sensor is used, as shown in the lower part of FIG. 5C, the optical axis of the light emitting element (exemplified by black circles in FIG. 5C) is a game ball path (winning ball) Preferably, the light emitting element and the light receiving element are provided so as to be offset from the central portion of the gaming ball passing through the path). Compared with the case where the optical axis corresponds to the central portion of the gaming ball, a portion where the distance between two gaming balls passing continuously is relatively wide (portion of “void” in FIG. 5 (C)) The game ball can be detected in and it is easy to detect two game balls separately. For the same reason, even in the case of using the reflection type photo sensor illustrated in FIG. 5B, the light emitting element and the light receiving element are installed such that the reflection point of the light from the light emitting element deviates from the central portion of the game ball It is preferable to do.

図6は、主基板(遊技制御基板)31における回路構成の一例を示すブロック図である。なお、図6には、払出制御基板37および演出制御基板80等も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する遊技制御用マイクロコンピュータ(遊技制御手段に相当)560が搭載されている。遊技制御用マイクロコンピュータ560は、ゲーム制御(遊技進行制御)用のプログラム等を記憶するROM54、ワークメモリとして使用される記憶手段としてのRAM55、プログラムに従って制御動作を行うCPU56およびI/Oポート部57を含む。この実施の形態では、ROM54およびRAM55は遊技制御用マイクロコンピュータ560に内蔵されている。すなわち、遊技制御用マイクロコンピュータ560は、1チップマイクロコンピュータである。1チップマイクロコンピュータには、少なくともRAM55が内蔵されていればよく、ROM54は外付けであっても内蔵されていてもよい。また、I/Oポート部57は、外付けであってもよい。

FIG. 6 is a block diagram showing an example of the circuit configuration of the main board (game control board) 31. As shown in FIG. In FIG. 6, the payout control board 37, the effect control board 80 and the like are also shown. The main substrate 31 is mounted with a game control microcomputer (corresponding to game control means) 560 for controlling the pachinko gaming machine 1 according to a program. The game control microcomputer 560 has a ROM 54 for storing a program for game control (game progression control) and the like, a RAM 55 as storage means used as a work memory, a CPU 56 for performing control operations according to the program, and an I / O port unit 57 including. In this embodiment, the ROM 54 and the RAM 55 are incorporated in the game control microcomputer 560. That is, the game control microcomputer 560 is a one-chip microcomputer. The one-chip microcomputer only needs to have at least the RAM 55 built-in, and the ROM 54 may be external or built-in. Also, the I / O port unit 57 may be externally attached.

なお、遊技制御用マイクロコンピュータ560においてCPU56がROM54に格納されているプログラムに従って制御を実行するので、以下、遊技制御用マイクロコンピュータ560(またはCPU56)が実行する(または、処理を行う)ということは、具体的には、CPU56がプログラムに従って制御を実行することである。このことは、主基板31以外の他の基板に搭載されているマイクロコンピュータについても同様である。

In the game control microcomputer 560, the CPU 56 executes control in accordance with the program stored in the ROM 54, so that the game control microcomputer 560 (or the CPU 56) executes (or performs processing) hereinafter. Specifically, the CPU 56 executes control in accordance with a program. The same applies to a microcomputer mounted on another substrate other than the main substrate 31.

また、遊技制御用マイクロコンピュータ560には、乱数回路503が内蔵されている。乱数回路503は、特別図柄の可変表示の表示結果により大当りとするか否か判定するための判定用の乱数を発生するために用いられるハードウェア回路である。乱数回路503は、初期値(例えば、0)と上限値(例えば、65535)とが設定された数値範囲内で、数値データを、設定された更新規則に従って更新し、ランダムなタイミングで発生する始動入賞時が数値データの読出(抽出)時であることにもとづいて、読出される数値データが乱数値となる乱数発生機能を有する。

Further, the game control microcomputer 560 incorporates a random number circuit 503. The random number circuit 503 is a hardware circuit used to generate a random number for determination to determine whether or not to make a big hit according to the display result of the variable display of the special symbol. The random number circuit 503 updates numerical data in accordance with a set update rule within a numerical range in which an initial value (for example, 0) and an upper limit value (for example, 65535) are set, and start occurs at random timing. Based on the fact that the winning is at the time of reading out (extraction) of numerical data, it has a random number generation function in which the numerical data to be read out is a random number.

乱数回路503は、数値データの更新範囲の選択設定機能(初期値の選択設定機能、および、上限値の選択設定機能)、数値データの更新規則の選択設定機能、および数値データの更新規則の選択切換え機能等の各種の機能を有する。このような機能によって、生成する乱数のランダム性を向上させることができる。

The random number circuit 503 has a selection setting function of updating range of numerical data (setting selection function of initial value and selection setting function of upper limit value), a selection setting function of updating rule of numerical data, and selection of update rule of numerical data It has various functions such as switching function. Such a function can improve the randomness of the generated random number.

また、遊技制御用マイクロコンピュータ560は、乱数回路503が更新する数値データの初期値を設定する機能を有している。例えば、ROM54等の所定の記憶領域に記憶された遊技制御用マイクロコンピュータ560のIDナンバ(遊技制御用マイクロコンピュータ560の各製品ごとに異なる数値で付与されたIDナンバ)を用いて所定の演算を行なって得られた数値データを、乱数回路503が更新する数値データの初期値として設定する。そのような処理を行うことによって、乱数回路503が発生する乱数のランダム性をより向上させることができる。

Further, the game control microcomputer 560 has a function of setting an initial value of numerical data to be updated by the random number circuit 503. For example, using the ID number of the game control microcomputer 560 stored in a predetermined storage area such as the ROM 54 (ID number assigned with a different numerical value for each product of the game control microcomputer 560) The numerical data obtained by the execution is set as the initial value of the numerical data to be updated by the random number circuit 503. By performing such processing, the randomness of the random number generated by the random number circuit 503 can be further improved.

遊技制御用マイクロコンピュータ560は、始動口スイッチ14aへの始動入賞が生じたときに乱数回路503から数値データをランダムRとして読み出し、特別図柄および演出図柄の変動開始時にランダムRにもとづいて特定の表示結果としての大当り表示結果にするか否か、すなわち、大当りとするか否かを決定する。そして、大当りとすると決定したときに、遊技状態を遊技者にとって有利な特定遊技状態としての大当り遊技状態に移行させる。

The game control microcomputer 560 reads out the numerical data from the random number circuit 503 as random R when the start winning on the start opening switch 14a occurs, and a specific display based on the random R at the start of the fluctuation of the special symbol and the effect symbol. It is determined whether or not to make the resulting big hit display result, that is, whether to make it a big hit. Then, when it is determined to be a big hit, the gaming state is shifted to the big hit gaming state as a specific gaming state that is advantageous for the player.

また、遊技制御用マイクロコンピュータ560には、払出制御基板37(の払出制御用マイクロコンピュータ370)や演出制御基板80(の演出制御用マイクロコンピュータ)とシリアル通信で信号を入出力(送受信)するためのシリアル通信回路505が内蔵されている。なお、払出制御用マイクロコンピュータ370や演出制御用マイクロコンピュータにも、遊技制御用マイクロコンピュータ560とシリアル通信で信号を入出力するためのシリアル通信回路が内蔵されている(払出制御用マイクロコンピュータ370に内蔵されたシリアル通信回路については、図7参照)。遊技制御用マイクロコンピュータ560は、2チャネルのシリアル通信回路505を内蔵しており、払出制御用マイクロコンピュータ370とシリアル通信を行うことが可能であるとともに、演出制御用マイクロコンピュータ100ともシリアル通信を行うことが可能である。ただし、この実施の形態では、演出制御用マイクロコンピュータ100との間のシリアル通信に関しては、遊技制御用マイクロコンピュータ560から演出制御用マイクロコンピュータに対してのみ信号が出力され、演出制御用マイクロコンピュータから遊技制御用マイクロコンピュータ560に対しては信号が出力されない。なお、遊技制御用マイクロコンピュータ560と演出制御用マイクロコンピュータとの間の通信については、シリアル通信で行う構成に限られるわけではなく、パラレル通信で行うように構成してもよい。

In addition, in order to input / output (transmit / receive) signals to / from the game control microcomputer 560 by serial communication with the payout control board 37 (the payout control microcomputer 370) or the effect control board 80 (the effect control microcomputer). Serial communication circuit 505 is incorporated. The payout control microcomputer 370 and the effect control microcomputer also include a serial communication circuit for inputting and outputting signals in serial communication with the game control microcomputer 560 (in the payout control microcomputer 370). See Figure 7 for the built-in serial communication circuit. The game control microcomputer 560 incorporates a two-channel serial communication circuit 505 and can perform serial communication with the payout control microcomputer 370 and also performs serial communication with the effect control microcomputer 100. It is possible. However, in this embodiment, regarding serial communication with the effect control microcomputer 100, a signal is outputted only from the game control microcomputer 560 to the effect control microcomputer and from the effect control microcomputer No signal is output to the gaming control microcomputer 560. Communication between the game control microcomputer 560 and the effect control microcomputer is not limited to serial communication, and may be parallel communication.

また、RAM55は、その一部または全部が電源基板において作成されるバックアップ電源によってバックアップされている不揮発性記憶手段としてのバックアップRAMである。すなわち、遊技機に対する電力供給が停止しても、所定期間(バックアップ電源としてのコンデンサが放電してバックアップ電源が電力供給不能になるまで)は、RAM55の一部または全部の内容は保存される。特に、少なくとも、遊技状態すなわち遊技制御手段の制御状態に応じたデータ(特別図柄プロセスフラグや保留記憶数カウンタの値など)と未払出賞球数を示すデータ(具体的には、後述する賞球コマンド出力カウンタの値)は、バックアップRAMに保存される。遊技制御手段の制御状態に応じたデータとは、停電等が生じた後に復旧した場合に、そのデータにもとづいて、制御状態を停電等の発生前に復旧させるために必要なデータである。また、制御状態に応じたデータと未払出賞球数を示すデータとを遊技の進行状態を示すデータと定義する。なお、この実施の形態では、RAM55の全部が、電源バックアップされているとする。

In addition, the RAM 55 is a backup RAM as a non-volatile storage means backed up by a backup power source, part or all of which is created on the power supply substrate. That is, even if the power supply to the gaming machine is stopped, the content of part or all of the RAM 55 is saved for a predetermined period (until the capacitor as the backup power supply is discharged and the power supply of the backup power supply becomes impossible). In particular, data indicating at least the gaming state, that is, the control state of the gaming control means (such as the value of the special symbol process flag or the value of the pending storage number counter) and data indicating the number of unpaid award balls (specifically, the award balls described later) The value of the command output counter) is stored in the backup RAM. The data corresponding to the control state of the game control means is data necessary to restore the control state before the occurrence of a power failure or the like on the basis of the data when the power failure or the like is restored after the occurrence of a power failure or the like. Further, data corresponding to the control state and data indicating the number of unpaid prize balls are defined as data indicating the progress of the game. In this embodiment, it is assumed that all of the RAM 55 is backed up by the power supply.

遊技制御用マイクロコンピュータ560のリセット端子には、電源基板からのリセット信号が入力される。電源基板には、遊技制御用マイクロコンピュータ560等に供給されるリセット信号を生成するリセット回路が搭載されている。なお、リセット信号がハイレベルになると遊技制御用マイクロコンピュータ560等は動作可能状態になり、リセット信号がローレベルになると遊技制御用マイクロコンピュータ560等は動作停止状態になる。従って、リセット信号がハイレベルである期間は、遊技制御用マイクロコンピュータ560等の動作を許容する許容信号が出力されていることになり、リセット信号がローレベルである期間は、遊技制御用マイクロコンピュータ560等の動作を停止させる動作停止信号が出力されていることになる。なお、リセット回路をそれぞれの電気部品制御基板(電気部品を制御するためのマイクロコンピュータが搭載されている基板)に搭載してもよい。

A reset signal from the power supply substrate is input to the reset terminal of the game control microcomputer 560. The power supply substrate is provided with a reset circuit that generates a reset signal supplied to the game control microcomputer 560 or the like. When the reset signal goes high, the gaming control microcomputer 560 becomes operable, and when the resetting signal goes low, the gaming control microcomputer 560 goes into a stopped state. Therefore, while the reset signal is at the high level, an allowance signal for permitting the operation of the gaming control microcomputer 560 or the like is output, and the period when the reset signal is at the low level is the gaming control microcomputer. An operation stop signal for stopping the operation of 560 and the like is output. The reset circuit may be mounted on each of the electric component control boards (a board on which a microcomputer for controlling the electric parts is mounted).

さらに、遊技制御用マイクロコンピュータ560の入力ポートには、電源基板からの電源電圧が所定値以下に低下したことを示す電源断信号が入力される。すなわち、電源基板には、遊技機において使用される所定電圧(例えば、DC30VやDC5Vなど)の電圧値を監視して、電圧値があらかじめ定められた所定値にまで低下すると(電源電圧の低下を検出すると)、その旨を示す電源断信号を出力する電源監視回路が搭載されている。なお、電源監視回路を電源基板に搭載するのではなく、バックアップ電源によって電源バックアップされる基板(例えば、主基板31)に搭載するようにしてもよい。また、遊技制御用マイクロコンピュータ560の入力ポートには、RAMの内容をクリアすることを指示するためのクリアスイッチが操作されたことを示すクリア信号(図示せず)が入力される。

Further, to the input port of the game control microcomputer 560, a power-off signal indicating that the power supply voltage from the power supply board has dropped to a predetermined value or less is input. That is, the power supply substrate monitors the voltage value of a predetermined voltage (for example, DC 30 V, DC 5 V, etc.) used in the game machine, and when the voltage value decreases to a predetermined value determined in advance A power supply monitoring circuit is mounted which outputs a power-off signal indicating that when it detects it). The power supply monitoring circuit may not be mounted on the power supply substrate, but may be mounted on a substrate (for example, the main substrate 31) which is backed up by the backup power supply. A clear signal (not shown) indicating that the clear switch for instructing to clear the contents of the RAM is operated is input to the input port of the game control microcomputer 560.

また、ゲートスイッチ32a、始動口スイッチ14a、入賞確認スイッチ14b、カウントスイッチ23、および各入賞口スイッチ29a,30aからの検出信号を基本回路53に与える入力ドライバ回路58も主基板31に搭載され、可変入賞球装置15を開閉するソレノイド16、および特別可変入賞球装置を開閉するソレノイド21を基本回路53からの指令に従って駆動する出力回路59も主基板31に搭載され、電源投入時に遊技制御用マイクロコンピュータ560をリセットするためのシステムリセット回路(図示せず)や、大当り遊技状態の発生を示す大当り情報等の情報出力信号を、ターミナル基板160を介して、ホールコンピュータ等の外部装置に対して出力する情報出力回路64も主基板31に搭載されている。

Further, an input driver circuit 58 for supplying a detection signal from the gate switch 32a, the start opening switch 14a, the winning confirmation switch 14b, the count switch 23, and each winning opening switch 29a, 30a to the basic circuit 53 is also mounted on the main board 31. A solenoid 16 for opening and closing the variable winning ball device 15 and an output circuit 59 for driving the solenoid 21 for opening and closing the special variable winning ball device in accordance with a command from the basic circuit 53 are also mounted on the main board 31. An information output signal such as a system reset circuit (not shown) for resetting the computer 560 or a big hit information indicating the occurrence of a big hit gaming state is output to an external device such as a hall computer via the terminal board 160. The information output circuit 64 is also mounted on the main board 31.

この実施の形態では、演出制御基板80に搭載されている演出制御手段(演出制御用マイクロコンピュータで構成される。)が、中継基板77を介して遊技制御用マイクロコンピュータ560からの演出制御コマンドを受信し、演出図柄を可変表示する演出表示装置9の表示制御を行う。

In this embodiment, the effect control means (composed of the effect control microcomputer) mounted on the effect control board 80 performs the effect control command from the game control microcomputer 560 via the relay board 77. Display control of the effect display device 9 which receives and displays the effect pattern variably is performed.

図7は、払出制御基板37および球払出装置97などの払出に関連する構成要素を示すブロック図である。図7に示すように、払出制御基板37には、払出制御用CPU371を含む払出制御用マイクロコンピュータ370が搭載されている。この実施の形態では、払出制御用マイクロコンピュータ370は、1チップマイクロコンピュータであり、少なくともRAMが内蔵されている。払出制御用マイクロコンピュータ370、RAM(図示せず)、払出制御用プログラムを格納したROM(図示せず)およびI/Oポート等は、払出制御手段を構成する。すなわち、払出制御手段は、払出制御用CPU371、RAMおよびROMを有する払出制御用マイクロコンピュータ370と、I/Oポートとで実現される。また、I/Oポートは、払出制御用マイクロコンピュータ370に内蔵されていてもよい。なお、遊技制御用マイクロコンピュータ560と異なり、払出制御用マイクロコンピュータ370が内蔵するRAMは、バックアップ電源による電源バックアップを受けていない。そのため、遊技機に対する電力供給が停止してしまうと、払出制御用マイクロコンピュータ370が内蔵するRAMの記憶内容は失われることになる。

FIG. 7 is a block diagram showing the components related to the dispensing, such as the dispensing control board 37 and the ball dispensing device 97. As shown in FIG. As shown in FIG. 7, a payout control microcomputer 370 including a payout control CPU 371 is mounted on the payout control board 37. In this embodiment, the payout control microcomputer 370 is a one-chip microcomputer and incorporates at least a RAM. The payout control microcomputer 370, a RAM (not shown), a ROM (not shown) storing a payout control program, an I / O port and the like constitute a payout control means. That is, the payout control means is realized by a payout control microcomputer 370 having a payout control CPU 371, a RAM and a ROM, and an I / O port. Further, the I / O port may be built in the payout control microcomputer 370. Note that, unlike the gaming control microcomputer 560, the RAM built in the payout control microcomputer 370 has not received power supply backup by the backup power supply. Therefore, when the power supply to the gaming machine is stopped, the stored contents of the RAM built in the payout control microcomputer 370 will be lost.

なお、払出制御用マイクロコンピュータ370は、所定の払出条件が成立したことにもとづいて遊技球を払い出す制御を行う。なお、所定の払出条件は、遊技領域に設けられた入賞領域(普通入賞口29,30、大入賞口、始動入賞口14)に遊技球が入賞したことや、貸し球要求がなされたことによって成立する。また、例えば、パロット機やスロットマシンなどの遊技機に適用する場合には、所定の払出条件は、遊技球やメダルの返却要求がなされたことによっても成立する。さらに、例えば、パロット機やスロットマシンなどの遊技機に適用する場合には、所定の払出条件は、図柄の停止図柄が所定の入賞図柄となったことによっても成立する。

The payout control microcomputer 370 controls the payout of the game balls based on the satisfaction of the predetermined payout condition. In addition, the predetermined payout condition is that the game ball has won in the winning area (normal winning opening 29, 30, big winning opening, starting winning opening 14) provided in the game area, or that the rental ball request is made. To establish. Further, for example, in the case of applying to a gaming machine such as a parrot machine or a slot machine, the predetermined payout condition is also satisfied by the return request of the gaming ball or the medal. Furthermore, for example, when applied to a gaming machine such as a parrot machine or a slot machine, the predetermined payout condition is also satisfied by the fact that the stop symbol of the symbol becomes a predetermined winning symbol.

球切れスイッチ187、満タンスイッチ48および払出個数カウントスイッチ301からの検出信号は、中継基板72を介して払出制御基板37のI/Oポート372fに入力される。なお、この実施の形態では、払出個数カウントスイッチ301からの検出信号は、払出制御用マイクロコンピュータ370に入力されたあと、I/Oポート372aおよび出力回路373Bを介して主基板31に出力される。

Detection signals from the out-of-ball switch 187, the full tank switch 48, and the payout number counting switch 301 are input to the I / O port 372 f of the payout control substrate 37 via the relay substrate 72. In this embodiment, the detection signal from the payout number counting switch 301 is input to the payout control microcomputer 370 and then output to the main substrate 31 via the I / O port 372a and the output circuit 373B. .

また、払出モータ位置センサ295からの検出信号は、中継基板72を介して払出制御基板37のI/Oポート372eに入力される。払出モータ位置センサ295は、払出モータ289の回転位置を検出するための発光素子(LED)と受光素子とによるセンサであり、遊技球が詰まったこと、すなわちいわゆる球噛みを検出するために用いられる。払出制御基板37に搭載されている払出制御用マイクロコンピュータ370は、球切れスイッチ187からの検出信号が球切れ状態を示していたり、満タンスイッチ48からの検出信号が満タン状態を示していると、球払出処理を停止する。

A detection signal from the payout motor position sensor 295 is input to the I / O port 372 e of the payout control substrate 37 via the relay substrate 72. The payout motor position sensor 295 is a sensor based on a light emitting element (LED) and a light receiving element for detecting the rotational position of the payout motor 289, and is used to detect that the gaming ball is clogged, ie . The payout control microcomputer 370 mounted on the payout control board 37 indicates that the detection signal from the out-of-ball switch 187 indicates the out-of-sphere state, and the detection signal from the full-tank switch 48 indicates the full-tank state. And stop the ball payout process.

さらに、満タンスイッチ48からの検出信号が満タン状態を示していると、払出制御用マイクロコンピュータ370は、打球発射装置からの球発射を停止させるために、発射基板90に対してローレベルの満タン信号を出力する。発射基板90のAND回路91が出力する発射モータ94への発射モータ信号は、発射基板90から発射モータ94に伝えられる。払出制御用マイクロコンピュータ370からの満タン信号は、発射基板90に搭載されたAND回路91の入力側の一方に入力され、駆動信号生成回路92からの駆動信号(発射モータ94を駆動するための信号であって、電源基板からの電源を供給する役割を果たす信号である。)は、AND回路91の入力側の他方に入力される。そして、AND回路91の発射モータ信号が発射モータ94に入力される。すなわち、払出制御用マイクロコンピュータ370が満タン信号を出力している間は、発射モータ94への発射モータ信号の出力が停止される。払出制御用マイクロコンピュータ370が満タン信号を出力している間であっても、発射モータ94への発射モータ信号の出力を停止せず、打球発射装置からの球発射を停止させないように構成してもよい。

Furthermore, when the detection signal from the full tank switch 48 indicates the full tank condition, the payout control microcomputer 370 sets the low level to the firing base plate 90 to stop the ball firing from the ball striking launcher. Output a full signal. The launch motor signal to the launch motor 94 output from the AND circuit 91 of the launch substrate 90 is transmitted from the launch substrate 90 to the launch motor 94. The full signal from the payout control microcomputer 370 is input to one of the input sides of the AND circuit 91 mounted on the launch substrate 90, and the drive signal from the drive signal generation circuit 92 (for driving the launch motor 94 The signal, which serves to supply power from the power supply substrate, is input to the other of the input sides of the AND circuit 91. Then, the firing motor signal of the AND circuit 91 is input to the firing motor 94. That is, while the payout control microcomputer 370 outputs the full signal, the output of the firing motor signal to the firing motor 94 is stopped. Even while the dispensing control microcomputer 370 outputs a full signal, the output of the firing motor signal to the firing motor 94 is not stopped, and the ball firing from the ball striking device is not stopped. May be

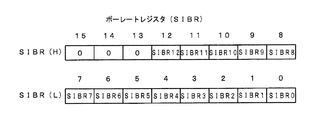

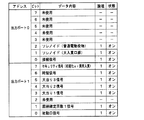

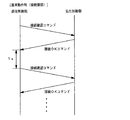

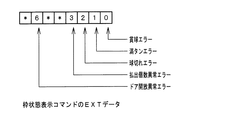

払出制御用マイクロコンピュータ370には、遊技制御用マイクロコンピュータ560とシリアル通信で信号を入出力(送受信)するためのシリアル通信回路380が内蔵されている。この実施の形態では、遊技制御用マイクロコンピュータ560と払出制御用マイクロコンピュータ370とは、シリアル通信回路505,380を介して、遊技制御用マイクロコンピュータ560と払出制御用マイクロコンピュータ370との間の接続確認を行うために、一定の間隔(例えば1秒)で払出制御コマンド(接続確認コマンド、接続OKコマンド)をやり取り(送受信)している。例えば、遊技制御用マイクロコンピュータ560は、シリアル通信回路505を介して、一定の間隔で接続確認を行うための接続確認コマンドを送信し、払出制御用マイクロコンピュータ370は、遊技制御用マイクロコンピュータ560からの接続確認コマンドを受信した場合、その旨を通知する接続OKコマンドを遊技制御用マイクロコンピュータ560に送信する。また、例えば、入賞が発生した場合には、遊技制御用マイクロコンピュータ560は、払い出すべき賞球個数を示すデータを賞球個数コマンドの下位4ビットに設定し、当該設定がなされた賞球個数コマンドを払出制御用マイクロコンピュータ370に送信する。そして、払出制御用マイクロコンピュータ370は、賞球個数を受け付けたことを示す賞球個数受付コマンドを遊技制御用マイクロコンピュータ560に送信する。さらに、払出制御用マイクロコンピュータ370は、賞球払出動作が終了すると、賞球終了を示賞球終了コマンドを遊技制御用マイクロコンピュータ560に送信する。なお、払出制御用マイクロコンピュータ370は、賞球払出動作を終了するまでの間、一定の間隔で賞球準備中コマンドを遊技制御用マイクロコンピュータ560に送信する。また、所定のエラー(球貸し、満タン、球切れなどのエラー)が発生した場合には、エラーの内容を示すデータを、接続OKコマンドや賞球準備中コマンドの下位4ビットを異ならせることにより設定し、当該設定がなされた接続OKコマンドや賞球準備中コマンドを遊技制御用マイクロコンピュータ560に送信する。なお、遊技制御用マイクロコンピュータ560と払出制御用マイクロコンピュータ370におけるシリアル通信による具体的な信号のやり取りについては、図30〜図37において詳述する。

The payout control microcomputer 370 incorporates a serial communication circuit 380 for inputting / outputting (transmitting / receiving) signals in serial communication with the game control microcomputer 560. In this embodiment, the game control microcomputer 560 and the payout control microcomputer 370 are connected between the game control microcomputer 560 and the payout control microcomputer 370 via the serial communication circuits 505 and 380. In order to confirm, a delivery control command (connection confirmation command, connection OK command) is exchanged (transmitted / received) at a fixed interval (for example, one second). For example, the gaming control microcomputer 560 transmits a connection confirmation command for performing connection confirmation at regular intervals via the serial communication circuit 505, and the payout control microcomputer 370 receives the connection from the gaming control microcomputer 560. When the connection confirmation command of is received, a connection OK command notifying that effect is transmitted to the game control microcomputer 560. Also, for example, when a winning occurs, the gaming control microcomputer 560 sets data indicating the number of prize balls to be paid out to the lower 4 bits of the prize ball number command, and the number of prize balls for which the setting is made. The command is sent to the dispensing control microcomputer 370. Then, the payout control microcomputer 370 transmits a winning ball number reception command indicating that the number of winning balls has been received to the game control microcomputer 560. Further, the payout control microcomputer 370 transmits an award ball end command indicating the end of the award ball to the game control microcomputer 560 when the award ball payout operation is completed. The payout control microcomputer 370 transmits a prize ball preparing command to the game control microcomputer 560 at fixed intervals until the prize ball payout operation is completed. In addition, when a predetermined error (error such as ball rental, full tank, ball breakage, etc.) occurs, the data indicating the content of the error should be made different in the lower 4 bits of the connection OK command or the prize ball preparing command. Setting, and the connection OK command and the prize ball preparing command in which the setting has been made are transmitted to the game control microcomputer 560. Specific signal exchange by serial communication in microcomputer 560 for game control and microcomputer 370 for payout control will be described in detail with reference to FIGS.

また、払出制御用マイクロコンピュータ370は、出力ポート372cを介して、7セグメントLEDによるエラー表示用LED374にエラー信号を出力する。なお、払出制御基板37の入力ポート372fには、エラー状態を解除するためのエラー解除スイッチ375からの検出信号が入力される。エラー解除スイッチ375は、ソフトウェアリセットによってエラー状態を解除するために用いられる。

Further, the payout control microcomputer 370 outputs an error signal to the error display LED 374 by the 7-segment LED through the output port 372 c. A detection signal from an error release switch 375 for releasing an error state is input to the input port 372f of the payout control board 37. The error release switch 375 is used to release an error state by software reset.

さらに、払出制御用マイクロコンピュータ370からの払出モータ289への駆動信号は、出力ポート372aおよび中継基板72を介して球払出装置97の払出機構部分における払出モータ289に伝えられる。なお、出力ポート372aの外側に、ドライバ回路(モータ駆動回路)が設置されているが、図7では記載省略されている。

Further, a drive signal to the dispensing motor 289 from the dispensing control microcomputer 370 is transmitted to the dispensing motor 289 in the dispensing mechanism portion of the ball dispensing device 97 through the output port 372 a and the relay board 72. Although a driver circuit (motor drive circuit) is installed outside the output port 372a, it is omitted in FIG.

遊技機に隣接して設置されているカードユニット50には、カードユニット制御用マイクロコンピュータが搭載されている。また、カードユニット50には、使用可表示ランプ、連結台方向表示器、カード投入表示ランプおよびカード挿入口が設けられている。インタフェース基板(中継基板)66には、打球供給皿3の近傍に設けられている度数表示LED60、球貸し可LED61、球貸しスイッチ62および返却スイッチ63が接続される。

A card unit control microcomputer is mounted on the card unit 50 installed adjacent to the gaming machine. In addition, the card unit 50 is provided with an availability indicator lamp, a connecting base direction indicator, a card insertion indicator lamp and a card slot. Connected to the interface board (relay board) 66 are a frequency display LED 60 provided near the ball hitting supply tray 3, a ball lendable LED 61, a ball lend switch 62 and a return switch 63.

インタフェース基板66からカードユニット50には、遊技者の操作に応じて、球貸しスイッチ62が操作されたことを示す球貸しスイッチ信号および返却スイッチ63が操作されたことを示す返却スイッチ信号が与えられる。また、カードユニット50からインタフェース基板66には、プリペイドカードの残高を示すカード残高表示信号および球貸し可表示信号が与えられる。カードユニット50と払出制御基板37の間では、接続信号(VL信号)、ユニット操作信号(BRDY信号)、球貸し要求信号(BRQ信号)、球貸し完了信号(EXS信号)およびパチンコ機動作信号(PRDY信号)が入力ポート372fおよび出力ポート372dを介して送受信される。カードユニット50と払出制御基板37の間には、インタフェース基板66が介在している。よって、接続信号(VL信号)等の信号は、図7に示すように、インタフェース基板66を介してカードユニット50と払出制御基板37の間で送受信されることになる。

From interface board 66 to card unit 50, a ball lending switch signal indicating that ball lending switch 62 is operated and a return switch signal indicating that return switch 63 is operated are given in response to the player's operation. . In addition, a card balance display signal indicating a balance of the prepaid card and a sphere lendable display signal are provided from the card unit 50 to the interface board 66. Between the card unit 50 and the payout control board 37, connection signal (VL signal), unit operation signal (BRDY signal), ball lending request signal (BRQ signal), ball lending completion signal (EXS signal) and pachinko machine operation signal ( The PRDY signal is transmitted and received through the input port 372 f and the output port 372 d. An interface board 66 is interposed between the card unit 50 and the payout control board 37. Therefore, signals such as connection signals (VL signals) are transmitted and received between the card unit 50 and the payout control board 37 through the interface board 66 as shown in FIG.

パチンコ遊技機1の電源が投入されると、払出制御基板37に搭載されている払出制御用マイクロコンピュータ370は、カードユニット50にPRDY信号を出力する。また、カードユニット制御用マイクロコンピュータは、電源が投入されると、VL信号を出力する。払出制御用マイクロコンピュータ370は、VL信号の入力状態によってカードユニット50の接続状態/未接続状態を判定する。カードユニット50においてカードが受け付けられ、球貸しスイッチが操作され球貸しスイッチ信号が入力されると、カードユニット制御用マイクロコンピュータは、払出制御基板37にBRDY信号を出力する。この時点から所定の遅延時間が経過すると、カードユニット制御用マイクロコンピュータは、払出制御基板37にBRQ信号を出力する。

When the pachinko gaming machine 1 is powered on, the payout control microcomputer 370 mounted on the payout control board 37 outputs a PRDY signal to the card unit 50. In addition, the card unit control microcomputer outputs a VL signal when the power is turned on. The payout control microcomputer 370 determines the connection state / non-connection state of the card unit 50 based on the input state of the VL signal. When a card is accepted in the card unit 50, the ball lending switch is operated, and the ball lending switch signal is input, the card unit control microcomputer outputs the BRDY signal to the payout control board 37. When a predetermined delay time has elapsed from this time point, the card unit control microcomputer outputs a BRQ signal to the payout control board 37.

そして、払出制御用マイクロコンピュータ370は、カードユニット50に対するEXS信号を立ち上げ、カードユニット50からのBRQ信号の立ち下がりを検出すると、払出モータ289を駆動し、所定個の貸し球を遊技者に払い出す。そして、払出が完了したら、払出制御用マイクロコンピュータ370は、カードユニット50に対するEXS信号を立ち下げる。その後、カードユニット50からのBRDY信号がオン状態でないことを条件に、遊技制御手段から払出指令信号を受けると賞球払出制御を実行する。

Then, the payout control microcomputer 370 raises the EXS signal to the card unit 50, and when detecting the fall of the BRQ signal from the card unit 50, drives the payout motor 289 to make the predetermined number of rental balls for the player. Pay out. Then, when the payout is completed, the payout control microcomputer 370 lowers the EXS signal to the card unit 50. Thereafter, on the condition that the BRDY signal from the card unit 50 is not in the on state, when the payout command signal is received from the game control means, the prize ball payout control is executed.

カードユニット50で用いられる電源電圧AC24Vは払出制御基板37から供給される。すなわち、カードユニット50に対する電源基板910からの電力供給は、払出制御基板37およびインタフェース基板66を介して行われる。この例では、インタフェース基板66内に配されているカードユニット50に対するAC24Vの電源供給ラインに、カードユニット50を保護するためのヒューズが設けられ、カードユニット50に所定電圧以上の電圧が供給されることが防止される。

The power supply voltage AC 24 V used in the card unit 50 is supplied from the payout control board 37. That is, power supply from the power supply substrate 910 to the card unit 50 is performed via the payout control substrate 37 and the interface substrate 66. In this example, a fuse for protecting the card unit 50 is provided on the AC 24 V power supply line for the card unit 50 disposed in the interface board 66, and a voltage higher than a predetermined voltage is supplied to the card unit 50. Is prevented.

また、この実施の形態では、カードユニット50が遊技機とは別体として遊技機に隣接して設置されている場合を例にするが、カードユニット50は遊技機と一体化されていてもよい。また、コイン投入に応じてその金額に応じた遊技球が貸し出されるような場合でも本発明を適用できる。

Also, in this embodiment, the case where the card unit 50 is installed adjacent to the gaming machine as a separate body from the gaming machine is exemplified, but the card unit 50 may be integrated with the gaming machine . Further, the present invention can be applied to the case where a gaming ball according to the amount is lent out in response to coin insertion.

また、ガラス扉枠2の状態を検出するドア開放センサ155(図3参照)の検出信号が、払出制御基板37に入力される。払出制御基板37において、ドア開放センサ155の検出信号は、払出制御用マイクロコンピュータ370には入力されず、払出制御基板37上を分岐して主基板31に出力される。なお、払出制御基板37上で分岐した後、出力回路373Bを介して主基板31に出力されるようにしてもよい。また、ドア開放センサ155の検出信号を払出制御用マイクロコンピュータ370に入力するようにし、払出制御用マイクロコンピュータ370を介してドア開放信号を主基板31に出力するようにしてもよい。

Further, a detection signal of a door opening sensor 155 (see FIG. 3) for detecting the state of the glass door frame 2 is input to the payout control substrate 37. In the payout control substrate 37, the detection signal of the door opening sensor 155 is not input to the payout control microcomputer 370, but is branched on the payout control substrate 37 and output to the main substrate 31. Alternatively, after being branched on the payout control substrate 37, the signal may be output to the main substrate 31 via the output circuit 373B. Alternatively, the detection signal of the door opening sensor 155 may be input to the payout control microcomputer 370, and the door opening signal may be output to the main substrate 31 via the payout control microcomputer 370.

図8は、中継基板77、演出制御基板80、ランプドライバ基板35および音声出力基板70の回路構成例を示すブロック図である。なお、図8に示す例では、ランプドライバ基板35および音声出力基板70には、マイクロコンピュータは搭載されていないが、マイクロコンピュータを搭載してもよい。また、ランプドライバ基板35および音声出力基板70を設けずに、演出制御に関して演出制御基板80のみを設けてもよい。

FIG. 8 is a block diagram showing an example of the circuit configuration of the relay board 77, the effect control board 80, the lamp driver board 35, and the sound output board 70. As shown in FIG. Although the microcomputer is not mounted on the lamp driver substrate 35 and the audio output substrate 70 in the example shown in FIG. 8, a microcomputer may be mounted. Further, only the effect control substrate 80 may be provided for effect control without providing the lamp driver substrate 35 and the sound output substrate 70.

演出制御基板80は、演出制御用CPU101a、および演出図柄プロセスフラグ等の演出に関する情報を記憶するRAMを含む演出制御用マイクロコンピュータ100を搭載している。なお、RAMは外付けであってもよい。この実施の形態では、演出制御用マイクロコンピュータ100におけるRAMは電源バックアップされていない。演出制御基板80において、演出制御用CPU101aは、内蔵または外付けのROM(図示せず)に格納されたプログラムに従って動作する。また、演出制御用マイクロコンピュータ100は、遊技制御用マイクロコンピュータ560とシリアル通信で信号を入出力(送受信)するシリアル通信回路101bを内蔵している。また、演出制御用CPU101aは、演出制御コマンドにもとづいて、VDP(ビデオディスプレイプロセッサ)109に演出表示装置9の表示制御を行わせる。

The effect control board 80 is mounted with an effect control microcomputer 100 including a effect control CPU 101a and a RAM for storing information on effects such as an effect pattern process flag and the like. The RAM may be externally attached. In this embodiment, the RAM in the effect control microcomputer 100 is not backed up by a power supply. In the effect control board 80, the effect control CPU 101a operates in accordance with a program stored in a built-in or external ROM (not shown). Further, the effect control microcomputer 100 incorporates a serial communication circuit 101b that inputs / outputs (transmits / receives) signals to / from the game control microcomputer 560 in serial communication. Further, the effect control CPU 101a causes the VDP (video display processor) 109 to perform display control of the effect display device 9 based on the effect control command.

この実施の形態では、演出制御用マイクロコンピュータ100と共動して演出表示装置9の表示制御を行うVDP109が演出制御基板80に搭載されている。VDP109は、演出制御用マイクロコンピュータ100とは独立したアドレス空間を有し、そこにVRAMをマッピングする。VRAMは、画像データを展開するためのバッファメモリである。そして、VDP109は、VRAM内の画像データをフレームメモリを介して演出表示装置9に出力する。

In this embodiment, a VDP 109 for controlling display of the effect display device 9 in cooperation with the effect control microcomputer 100 is mounted on the effect control board 80. The VDP 109 has an address space independent of the effect control microcomputer 100, and maps a VRAM there. VRAM is a buffer memory for expanding image data. Then, the VDP 109 outputs the image data in the VRAM to the effect display device 9 via the frame memory.

演出制御用CPU101aは、受信した演出制御コマンドに従ってCGROM(図示せず)から必要なデータを読み出すための指令をVDP109に出力する。CGROMは、演出表示装置9に表示されるキャラクタ画像データや動画像データ、具体的には、人物、文字、図形や記号等(演出図柄を含む)、および背景画像のデータをあらかじめ格納しておくためのROMである。VDP109は、演出制御用CPU101aの指令に応じて、CGROMから画像データを読み出す。そして、VDP109は、読み出した画像データにもとづいて表示制御を実行する。

The effect control CPU 101a outputs, to the VDP 109, an instruction for reading out necessary data from a CGROM (not shown) in accordance with the received effect control command. The CGROM stores in advance character image data and moving image data displayed on the effect display device 9, specifically, data of a person, characters, figures, symbols, etc. (including effect patterns), and background image data. It is a ROM for. The VDP 109 reads image data from the CGROM in accordance with an instruction from the effect control CPU 101a. Then, the VDP 109 executes display control based on the read image data.

さらに、演出制御用CPU101aは、出力ポート105を介してランプドライバ基板35に対してLEDを駆動する信号を出力する。また、演出制御用CPU101aは、出力ポート104を介して音声出力基板70に対して音番号データを出力する。

Further, the effect control CPU 101 a outputs a signal for driving the LED to the lamp driver board 35 via the output port 105. Further, the effect control CPU 101 a outputs sound number data to the audio output board 70 via the output port 104.

ランプドライバ基板35において、LEDを駆動する信号は、入力ドライバ351を介してLEDドライバ352に入力される。LEDドライバ352は、LEDを駆動する信号にもとづいて枠LED28などの枠側に設けられている発光体に電流を供給する。また、遊技盤側に設けられている装飾LED25に電流を供給する。

In the lamp driver substrate 35, a signal for driving the LED is input to the LED driver 352 via the input driver 351. The LED driver 352 supplies current to a light emitter provided on the frame side such as the frame LED 28 based on a signal for driving the LED. In addition, current is supplied to the decoration LED 25 provided on the game board side.

音声出力基板70において、音番号データは、入力ドライバ702を介して音声合成用IC703に入力される。音声合成用IC703は、音番号データに応じた音声や効果音を発生し増幅回路705に出力する。増幅回路705は、音声合成用IC703の出力レベルを、ボリューム706で設定されている音量に応じたレベルに増幅した音声信号をスピーカ27に出力する。音声データROM704には、音番号データに応じた制御データが格納されている。音番号データに応じた制御データは、所定期間(例えば演出図柄の変動期間)における効果音または音声の出力態様を時系列的に示すデータの集まりである。

In the voice output board 70, the sound number data is input to the voice synthesis IC 703 via the input driver 702. The speech synthesis IC 703 generates speech and sound effects according to the sound number data and outputs the speech and the sound effects to the amplification circuit 705. The amplifier circuit 705 outputs to the speaker 27 an audio signal obtained by amplifying the output level of the voice synthesis IC 703 to a level according to the volume set by the volume 706. The voice data ROM 704 stores control data corresponding to the sound number data. The control data corresponding to the sound number data is a collection of data indicating in time series the output mode of the sound effect or the sound in a predetermined period (for example, a fluctuation period of the effect pattern).

図9は、主基板31における回路構成および主基板31から演出制御基板80に送信される演出制御コマンドの信号線を示すブロック図である。図9に示すように、この実施の形態では、主基板31が搭載する遊技制御用マイクロコンピュータ560は、演出制御信号送信用の1本の信号線を用いて、演出制御コマンド(演出制御信号)を演出制御基板80に送信する。

FIG. 9 is a block diagram showing the circuit configuration of the main board 31 and signal lines of the effect control command transmitted from the main board 31 to the effect control board 80. As shown in FIG. As shown in FIG. 9, in this embodiment, the game control microcomputer 560 mounted on the main substrate 31 uses a single signal line for effect control signal transmission to produce an effect control command (effect control signal). Is transmitted to the effect control board 80.

主基板31には、図9に示すように、始動口スイッチ14aや入賞確認スイッチ14bからの配線が接続されている。また、主基板31には、大入賞口である特別可変入賞球装置20や、その他の入賞口への遊技球の入賞等を検出するための各種スイッチ29a,30aからの配線も接続されている。さらに、主基板31には、可変入賞球装置15を開閉するソレノイド16、および特別可変入賞球装置20を開閉するソレノイド21への配線が接続されている。

As shown in FIG. 9, the main board 31 is connected to the wiring from the starting opening switch 14a and the prize confirmation switch 14b. In addition, the main substrate 31 is also connected with wiring from the special variable winning ball device 20 which is a big winning opening, and various switches 29a and 30a for detecting the winning of the game ball to the other winning openings, etc. . Furthermore, the main substrate 31 is connected to the solenoid 16 for opening and closing the variable winning ball device 15 and the wiring for the solenoid 21 for opening and closing the special variable winning ball device 20.