JP6378325B2 - 非対称な記憶容量を有する複数チャネルメモリアーキテクチャにわたってデータを均一にインターリーブするためのシステムおよび方法 - Google Patents

非対称な記憶容量を有する複数チャネルメモリアーキテクチャにわたってデータを均一にインターリーブするためのシステムおよび方法 Download PDFInfo

- Publication number

- JP6378325B2 JP6378325B2 JP2016518727A JP2016518727A JP6378325B2 JP 6378325 B2 JP6378325 B2 JP 6378325B2 JP 2016518727 A JP2016518727 A JP 2016518727A JP 2016518727 A JP2016518727 A JP 2016518727A JP 6378325 B2 JP6378325 B2 JP 6378325B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- channel

- storage capacity

- memory space

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/06—Addressing a physical block of locations, e.g. base addressing, module addressing, memory dedication

- G06F12/0607—Interleaved addressing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

- G06F13/1647—Handling requests for interconnection or transfer for access to memory bus based on arbitration with interleaved bank access

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

- G06F13/1652—Handling requests for interconnection or transfer for access to memory bus based on arbitration in a multiprocessor architecture

- G06F13/1657—Access to multiple memories

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

Description

116 マイクロフォン

120 オンチップシステム

128 ディスプレイコントローラ

130 タッチスクリーンコントローラ

132 ディスプレイ/タッチスクリーン

134 ビデオエンコーダ

136 ビデオ増幅器

138 ビデオポート

140 ユニバーサルシリアルバス(USB)コントローラ

142 USBポート

146 加入者識別モジュール(SIM)カード

148 デジタルカメラ

150 ステレオオーディオコーデック

152 オーディオ増幅器

154 第1のステレオスピーカ

156 第2のステレオスピーカ

158 マイクロフォン増幅器

162 周波数変調(FM)ラジオチューナ

164 FMアンテナ

166 ステレオポート

168 高周波(RF)トランシーバ

170 RFスイッチ

172 RFアンテナ

174 キーパッド

176 モノヘッドセット

178 バイブレータデバイス

180 電源

188 ネットワークカード

200 コンピューティングデバイス

210 マルチコアCPU

211 メモリコントローラ

212 インターリーバロジック

213 オペレーティングシステム(O/S)ロジック

214 キャッシュ

215 コア

215 第0のコア

216 第1のコア

217 第Nのコア

219 接続

220 チャネル

222 チャネル

224 チャネル

226 チャネル

230 システムメモリ

290 メモリ空間

291 メモリモジュール

292 メモリモジュール

293 メモリモジュール

294 メモリモジュール

300 コンピューティングデバイス

302 複数チャネルメモリアクセスアーキテクチャ

390 メモリ空間

391 第1のメモリモジュール

393 メモリモジュール

394 メモリモジュール

411 電気的消去可能プログラマブルリードオンリーメモリ(EEPROM)

418 修正インターリーバロジック

440 メモリ空間

441 第1のメモリモジュール

443 メモリモジュール

444 メモリモジュール

511 EEPROM

518 修正インターリーバロジック

540 メモリ空間

541 第1のメモリモジュール

543 メモリモジュール

544 メモリモジュール

600 システム

611 EEPROM

618 修正インターリーバロジック

640 メモリ空間

641 メモリモジュール

642 メモリモジュール

644 メモリモジュール

645 メモリモジュール

646 メモリモジュール

700 システム

711 EEPROM

718 修正インターリーバロジック

740 メモリ空間

741 メモリモジュール

743 メモリモジュール

744 メモリモジュール

745 メモリモジュール

747 メモリモジュール

748 メモリモジュール

Claims (15)

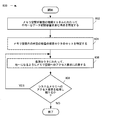

- 不均一な記憶容量を有するメモリ空間へのメモリアクセスを物理チャネルにわたって均一にインターリーブするための方法であって、

複数チャネルメモリアーキテクチャが、異なるデータ転送速度において動作する前記物理チャネルにわたって非対称な記憶容量を与えられる時点を特定するステップと、

前記メモリ空間において等しい記憶容量の複数の仮想セクタを規定するために、前記特定するステップに応答するロジックを使用するステップと、

前記非対称な記憶容量に前記仮想セクタにわたって均一にアクセスするために、前記物理チャネルのうちのメモリ空間アクセス要求を動的に分散させるようにインターリーバを介してインターリーブ機能を適用するステップと

を含む、方法。 - 前記物理チャネルの数は偶数であり、前記等しい容量の仮想セクタの数は奇数である、請求項1に記載の方法。

- 前記物理チャネルの数は奇数であり、前記等しい容量の仮想セクタの数は偶数である、請求項1に記載の方法。

- 前記インターリーブ機能を適用するステップは、拡散機能を適用するステップを含む、請求項1に記載の方法。

- 前記拡散機能は、前記メモリ空間にわたって物理チャネル間の規定された比においてメモリアクセスを動的に分散させる、請求項4に記載の方法。

- 前記等しい容量の仮想セクタの数はプログラム可能である、請求項1に記載の方法。

- 前記等しい容量の仮想セクタの数は前記メモリ空間をサポートするメモリモジュールの数より少ない、請求項1に記載の方法。

- 前記等しい容量の仮想セクタの数は前記メモリ空間をサポートするメモリモジュールの数より多い、請求項1に記載の方法。

- 前記メモリ空間は、同じ記憶容量の奇数のメモリモジュールによってサポートされる、請求項1に記載の方法。

- 前記メモリ空間は、残りのメモリモジュールの前記記憶容量とは異なる記憶容量を有する少なくとも1つのメモリモジュールを有する偶数のメモリモジュールによってサポートされる、請求項1に記載の方法。

- 前記メモリ空間にアクセスする動作は、非インターリーブデータ転送速度を超える、前記物理チャネルそれぞれへのデータ転送速度においてサポートされる、請求項1に記載の方法。

- 第1の物理チャネルを介して前記メモリ空間にアクセスする動作は第1のデータ転送速度においてサポートされ、第2の物理チャネルを介して前記メモリ空間にアクセスする動作は、前記第1のデータ転送速度とは異なる第2のデータ転送速度においてサポートされる、請求項1に記載の方法。

- 前記第1のデータ転送速度は前記第2のデータ転送速度の関数であり、前記第1のデータ転送速度および前記第2のデータ転送速度は、物理チャネルによってサポートされる仮想セクタの数に基づいて決定される、請求項12に記載の方法。

- 不均一な記憶容量を有するメモリ空間へのメモリアクセスを物理チャネルにわたって均一にインターリーブするためのコンピューティングデバイスであって、

複数チャネルメモリアーキテクチャが、異なるデータ転送速度において動作する前記物理チャネルにわたって非対称な記憶容量を与えられる時点を特定するための手段と、

前記メモリ空間において等しい記憶容量の複数の仮想セクタを規定するための手段と、

前記非対称な記憶容量に前記仮想セクタにわたって均一にアクセスするために、前記物理チャネルのうちのメモリ空間アクセス要求を動的に分散させるようにインターリーバを介してインターリーブ機能を適用するための手段と

を備える、コンピューティングデバイス。 - コンピュータ上で実行されるとき、請求項1〜13のいずれか一項に記載の方法を実行するための命令を備える、コンピュータプログラム。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/045,784 | 2013-10-03 | ||

| US14/045,784 US9465735B2 (en) | 2013-10-03 | 2013-10-03 | System and method for uniform interleaving of data across a multiple-channel memory architecture with asymmetric storage capacity |

| PCT/US2014/058946 WO2015051201A1 (en) | 2013-10-03 | 2014-10-03 | System and method for uniform interleaving of data across a multiple-channel memory architecture with asymmetric storage capacity |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016532926A JP2016532926A (ja) | 2016-10-20 |

| JP2016532926A5 JP2016532926A5 (ja) | 2017-10-26 |

| JP6378325B2 true JP6378325B2 (ja) | 2018-08-22 |

Family

ID=51842833

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016518727A Expired - Fee Related JP6378325B2 (ja) | 2013-10-03 | 2014-10-03 | 非対称な記憶容量を有する複数チャネルメモリアーキテクチャにわたってデータを均一にインターリーブするためのシステムおよび方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US9465735B2 (ja) |

| EP (1) | EP3053044B1 (ja) |

| JP (1) | JP6378325B2 (ja) |

| KR (1) | KR20160064223A (ja) |

| CN (1) | CN105612501B (ja) |

| BR (1) | BR112016007344A2 (ja) |

| CA (1) | CA2925131A1 (ja) |

| WO (1) | WO2015051201A1 (ja) |

Families Citing this family (152)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11614893B2 (en) | 2010-09-15 | 2023-03-28 | Pure Storage, Inc. | Optimizing storage device access based on latency |

| US8589640B2 (en) | 2011-10-14 | 2013-11-19 | Pure Storage, Inc. | Method for maintaining multiple fingerprint tables in a deduplicating storage system |

| US20150169445A1 (en) | 2013-12-12 | 2015-06-18 | International Business Machines Corporation | Virtual grouping of memory |

| US11068363B1 (en) | 2014-06-04 | 2021-07-20 | Pure Storage, Inc. | Proactively rebuilding data in a storage cluster |

| US11960371B2 (en) | 2014-06-04 | 2024-04-16 | Pure Storage, Inc. | Message persistence in a zoned system |

| US9367243B1 (en) * | 2014-06-04 | 2016-06-14 | Pure Storage, Inc. | Scalable non-uniform storage sizes |

| US10574754B1 (en) | 2014-06-04 | 2020-02-25 | Pure Storage, Inc. | Multi-chassis array with multi-level load balancing |

| US9836234B2 (en) | 2014-06-04 | 2017-12-05 | Pure Storage, Inc. | Storage cluster |

| US9213485B1 (en) | 2014-06-04 | 2015-12-15 | Pure Storage, Inc. | Storage system architecture |

| US9003144B1 (en) | 2014-06-04 | 2015-04-07 | Pure Storage, Inc. | Mechanism for persisting messages in a storage system |

| US11399063B2 (en) | 2014-06-04 | 2022-07-26 | Pure Storage, Inc. | Network authentication for a storage system |

| US11652884B2 (en) | 2014-06-04 | 2023-05-16 | Pure Storage, Inc. | Customized hash algorithms |

| US8850108B1 (en) | 2014-06-04 | 2014-09-30 | Pure Storage, Inc. | Storage cluster |

| US9218244B1 (en) | 2014-06-04 | 2015-12-22 | Pure Storage, Inc. | Rebuilding data across storage nodes |

| US9836245B2 (en) | 2014-07-02 | 2017-12-05 | Pure Storage, Inc. | Non-volatile RAM and flash memory in a non-volatile solid-state storage |

| US8868825B1 (en) | 2014-07-02 | 2014-10-21 | Pure Storage, Inc. | Nonrepeating identifiers in an address space of a non-volatile solid-state storage |

| US9021297B1 (en) | 2014-07-02 | 2015-04-28 | Pure Storage, Inc. | Redundant, fault-tolerant, distributed remote procedure call cache in a storage system |

| US11604598B2 (en) | 2014-07-02 | 2023-03-14 | Pure Storage, Inc. | Storage cluster with zoned drives |

| US11886308B2 (en) | 2014-07-02 | 2024-01-30 | Pure Storage, Inc. | Dual class of service for unified file and object messaging |

| US10114757B2 (en) | 2014-07-02 | 2018-10-30 | Pure Storage, Inc. | Nonrepeating identifiers in an address space of a non-volatile solid-state storage |

| US8874836B1 (en) | 2014-07-03 | 2014-10-28 | Pure Storage, Inc. | Scheduling policy for queues in a non-volatile solid-state storage |

| US9747229B1 (en) | 2014-07-03 | 2017-08-29 | Pure Storage, Inc. | Self-describing data format for DMA in a non-volatile solid-state storage |

| US10853311B1 (en) | 2014-07-03 | 2020-12-01 | Pure Storage, Inc. | Administration through files in a storage system |

| US9811677B2 (en) | 2014-07-03 | 2017-11-07 | Pure Storage, Inc. | Secure data replication in a storage grid |

| US9766972B2 (en) | 2014-08-07 | 2017-09-19 | Pure Storage, Inc. | Masking defective bits in a storage array |

| US9082512B1 (en) | 2014-08-07 | 2015-07-14 | Pure Storage, Inc. | Die-level monitoring in a storage cluster |

| US10983859B2 (en) | 2014-08-07 | 2021-04-20 | Pure Storage, Inc. | Adjustable error correction based on memory health in a storage unit |

| US9495255B2 (en) | 2014-08-07 | 2016-11-15 | Pure Storage, Inc. | Error recovery in a storage cluster |

| US9483346B2 (en) | 2014-08-07 | 2016-11-01 | Pure Storage, Inc. | Data rebuild on feedback from a queue in a non-volatile solid-state storage |

| US9558069B2 (en) | 2014-08-07 | 2017-01-31 | Pure Storage, Inc. | Failure mapping in a storage array |

| US10079711B1 (en) | 2014-08-20 | 2018-09-18 | Pure Storage, Inc. | Virtual file server with preserved MAC address |

| KR102355573B1 (ko) * | 2014-10-29 | 2022-01-27 | 삼성전자주식회사 | 선형 리맵퍼 및 액세스 윈도우를 포함하는 메모리 시스템 및 시스템 온 칩 |

| US9720825B2 (en) * | 2014-12-19 | 2017-08-01 | Dell Products, Lp | System and method for performance optimal partial rank/bank interleaving for non-symmetrically populated DIMMs across DDR channels |

| US9948615B1 (en) | 2015-03-16 | 2018-04-17 | Pure Storage, Inc. | Increased storage unit encryption based on loss of trust |

| US11294893B2 (en) | 2015-03-20 | 2022-04-05 | Pure Storage, Inc. | Aggregation of queries |

| US9940234B2 (en) | 2015-03-26 | 2018-04-10 | Pure Storage, Inc. | Aggressive data deduplication using lazy garbage collection |

| US10082985B2 (en) | 2015-03-27 | 2018-09-25 | Pure Storage, Inc. | Data striping across storage nodes that are assigned to multiple logical arrays |

| US10178169B2 (en) | 2015-04-09 | 2019-01-08 | Pure Storage, Inc. | Point to point based backend communication layer for storage processing |

| US9672125B2 (en) | 2015-04-10 | 2017-06-06 | Pure Storage, Inc. | Ability to partition an array into two or more logical arrays with independently running software |

| US10140149B1 (en) | 2015-05-19 | 2018-11-27 | Pure Storage, Inc. | Transactional commits with hardware assists in remote memory |

| US9817576B2 (en) | 2015-05-27 | 2017-11-14 | Pure Storage, Inc. | Parallel update to NVRAM |

| US10846275B2 (en) | 2015-06-26 | 2020-11-24 | Pure Storage, Inc. | Key management in a storage device |

| US10983732B2 (en) | 2015-07-13 | 2021-04-20 | Pure Storage, Inc. | Method and system for accessing a file |

| US11232079B2 (en) | 2015-07-16 | 2022-01-25 | Pure Storage, Inc. | Efficient distribution of large directories |

| US10108355B2 (en) | 2015-09-01 | 2018-10-23 | Pure Storage, Inc. | Erase block state detection |

| US11341136B2 (en) | 2015-09-04 | 2022-05-24 | Pure Storage, Inc. | Dynamically resizable structures for approximate membership queries |

| US10762069B2 (en) | 2015-09-30 | 2020-09-01 | Pure Storage, Inc. | Mechanism for a system where data and metadata are located closely together |

| US10853266B2 (en) | 2015-09-30 | 2020-12-01 | Pure Storage, Inc. | Hardware assisted data lookup methods |

| US9768953B2 (en) | 2015-09-30 | 2017-09-19 | Pure Storage, Inc. | Resharing of a split secret |

| US9697884B2 (en) * | 2015-10-08 | 2017-07-04 | Rambus Inc. | Variable width memory module supporting enhanced error detection and correction |

| US9843453B2 (en) | 2015-10-23 | 2017-12-12 | Pure Storage, Inc. | Authorizing I/O commands with I/O tokens |

| US11762764B1 (en) | 2015-12-02 | 2023-09-19 | Pure Storage, Inc. | Writing data in a storage system that includes a first type of storage device and a second type of storage device |

| US9760479B2 (en) * | 2015-12-02 | 2017-09-12 | Pure Storage, Inc. | Writing data in a storage system that includes a first type of storage device and a second type of storage device |

| US10007457B2 (en) | 2015-12-22 | 2018-06-26 | Pure Storage, Inc. | Distributed transactions with token-associated execution |

| US10261690B1 (en) | 2016-05-03 | 2019-04-16 | Pure Storage, Inc. | Systems and methods for operating a storage system |

| US10140223B2 (en) | 2016-06-27 | 2018-11-27 | Qualcomm Incorporated | System and method for odd modulus memory channel interleaving |

| US11861188B2 (en) | 2016-07-19 | 2024-01-02 | Pure Storage, Inc. | System having modular accelerators |

| US11449232B1 (en) | 2016-07-22 | 2022-09-20 | Pure Storage, Inc. | Optimal scheduling of flash operations |

| US9672905B1 (en) | 2016-07-22 | 2017-06-06 | Pure Storage, Inc. | Optimize data protection layouts based on distributed flash wear leveling |

| US10768819B2 (en) | 2016-07-22 | 2020-09-08 | Pure Storage, Inc. | Hardware support for non-disruptive upgrades |

| US11604690B2 (en) | 2016-07-24 | 2023-03-14 | Pure Storage, Inc. | Online failure span determination |

| US10216420B1 (en) | 2016-07-24 | 2019-02-26 | Pure Storage, Inc. | Calibration of flash channels in SSD |

| US11080155B2 (en) | 2016-07-24 | 2021-08-03 | Pure Storage, Inc. | Identifying error types among flash memory |

| US11886334B2 (en) | 2016-07-26 | 2024-01-30 | Pure Storage, Inc. | Optimizing spool and memory space management |

| US10203903B2 (en) | 2016-07-26 | 2019-02-12 | Pure Storage, Inc. | Geometry based, space aware shelf/writegroup evacuation |

| US11797212B2 (en) | 2016-07-26 | 2023-10-24 | Pure Storage, Inc. | Data migration for zoned drives |

| US11734169B2 (en) | 2016-07-26 | 2023-08-22 | Pure Storage, Inc. | Optimizing spool and memory space management |

| US10366004B2 (en) | 2016-07-26 | 2019-07-30 | Pure Storage, Inc. | Storage system with elective garbage collection to reduce flash contention |

| US10162554B2 (en) * | 2016-08-03 | 2018-12-25 | Samsung Electronics Co., Ltd. | System and method for controlling a programmable deduplication ratio for a memory system |

| US11422719B2 (en) | 2016-09-15 | 2022-08-23 | Pure Storage, Inc. | Distributed file deletion and truncation |

| US10756816B1 (en) | 2016-10-04 | 2020-08-25 | Pure Storage, Inc. | Optimized fibre channel and non-volatile memory express access |

| US9747039B1 (en) | 2016-10-04 | 2017-08-29 | Pure Storage, Inc. | Reservations over multiple paths on NVMe over fabrics |

| US11550481B2 (en) | 2016-12-19 | 2023-01-10 | Pure Storage, Inc. | Efficiently writing data in a zoned drive storage system |

| US11307998B2 (en) | 2017-01-09 | 2022-04-19 | Pure Storage, Inc. | Storage efficiency of encrypted host system data |

| US11955187B2 (en) | 2017-01-13 | 2024-04-09 | Pure Storage, Inc. | Refresh of differing capacity NAND |

| US9747158B1 (en) | 2017-01-13 | 2017-08-29 | Pure Storage, Inc. | Intelligent refresh of 3D NAND |

| US10979223B2 (en) | 2017-01-31 | 2021-04-13 | Pure Storage, Inc. | Separate encryption for a solid-state drive |

| US10528488B1 (en) | 2017-03-30 | 2020-01-07 | Pure Storage, Inc. | Efficient name coding |

| US11016667B1 (en) | 2017-04-05 | 2021-05-25 | Pure Storage, Inc. | Efficient mapping for LUNs in storage memory with holes in address space |

| US10516645B1 (en) | 2017-04-27 | 2019-12-24 | Pure Storage, Inc. | Address resolution broadcasting in a networked device |

| US10141050B1 (en) | 2017-04-27 | 2018-11-27 | Pure Storage, Inc. | Page writes for triple level cell flash memory |

| US10944671B2 (en) | 2017-04-27 | 2021-03-09 | Pure Storage, Inc. | Efficient data forwarding in a networked device |

| US11467913B1 (en) | 2017-06-07 | 2022-10-11 | Pure Storage, Inc. | Snapshots with crash consistency in a storage system |

| US11138103B1 (en) | 2017-06-11 | 2021-10-05 | Pure Storage, Inc. | Resiliency groups |

| US11782625B2 (en) | 2017-06-11 | 2023-10-10 | Pure Storage, Inc. | Heterogeneity supportive resiliency groups |

| US11947814B2 (en) | 2017-06-11 | 2024-04-02 | Pure Storage, Inc. | Optimizing resiliency group formation stability |

| US10425473B1 (en) | 2017-07-03 | 2019-09-24 | Pure Storage, Inc. | Stateful connection reset in a storage cluster with a stateless load balancer |

| US10402266B1 (en) | 2017-07-31 | 2019-09-03 | Pure Storage, Inc. | Redundant array of independent disks in a direct-mapped flash storage system |

| US10877827B2 (en) | 2017-09-15 | 2020-12-29 | Pure Storage, Inc. | Read voltage optimization |

| US10210926B1 (en) | 2017-09-15 | 2019-02-19 | Pure Storage, Inc. | Tracking of optimum read voltage thresholds in nand flash devices |

| US10496330B1 (en) | 2017-10-31 | 2019-12-03 | Pure Storage, Inc. | Using flash storage devices with different sized erase blocks |

| US10884919B2 (en) | 2017-10-31 | 2021-01-05 | Pure Storage, Inc. | Memory management in a storage system |

| US11024390B1 (en) | 2017-10-31 | 2021-06-01 | Pure Storage, Inc. | Overlapping RAID groups |

| US10545687B1 (en) | 2017-10-31 | 2020-01-28 | Pure Storage, Inc. | Data rebuild when changing erase block sizes during drive replacement |

| US10515701B1 (en) | 2017-10-31 | 2019-12-24 | Pure Storage, Inc. | Overlapping raid groups |

| US10860475B1 (en) | 2017-11-17 | 2020-12-08 | Pure Storage, Inc. | Hybrid flash translation layer |

| US10990566B1 (en) | 2017-11-20 | 2021-04-27 | Pure Storage, Inc. | Persistent file locks in a storage system |

| US10929053B2 (en) | 2017-12-08 | 2021-02-23 | Pure Storage, Inc. | Safe destructive actions on drives |

| US10719265B1 (en) | 2017-12-08 | 2020-07-21 | Pure Storage, Inc. | Centralized, quorum-aware handling of device reservation requests in a storage system |

| US10929031B2 (en) | 2017-12-21 | 2021-02-23 | Pure Storage, Inc. | Maximizing data reduction in a partially encrypted volume |

| US10976948B1 (en) | 2018-01-31 | 2021-04-13 | Pure Storage, Inc. | Cluster expansion mechanism |

| US10467527B1 (en) | 2018-01-31 | 2019-11-05 | Pure Storage, Inc. | Method and apparatus for artificial intelligence acceleration |

| US10733053B1 (en) | 2018-01-31 | 2020-08-04 | Pure Storage, Inc. | Disaster recovery for high-bandwidth distributed archives |

| US11036596B1 (en) | 2018-02-18 | 2021-06-15 | Pure Storage, Inc. | System for delaying acknowledgements on open NAND locations until durability has been confirmed |

| US11494109B1 (en) | 2018-02-22 | 2022-11-08 | Pure Storage, Inc. | Erase block trimming for heterogenous flash memory storage devices |

| US11385792B2 (en) | 2018-04-27 | 2022-07-12 | Pure Storage, Inc. | High availability controller pair transitioning |

| US10931450B1 (en) | 2018-04-27 | 2021-02-23 | Pure Storage, Inc. | Distributed, lock-free 2-phase commit of secret shares using multiple stateless controllers |

| US10853146B1 (en) | 2018-04-27 | 2020-12-01 | Pure Storage, Inc. | Efficient data forwarding in a networked device |

| US11436023B2 (en) | 2018-05-31 | 2022-09-06 | Pure Storage, Inc. | Mechanism for updating host file system and flash translation layer based on underlying NAND technology |

| US10642733B1 (en) * | 2018-07-12 | 2020-05-05 | Lightbits Labs Ltd. | System and method for memory interface load balancing |

| US11438279B2 (en) | 2018-07-23 | 2022-09-06 | Pure Storage, Inc. | Non-disruptive conversion of a clustered service from single-chassis to multi-chassis |

| CN112513824B (zh) * | 2018-07-31 | 2024-04-09 | 华为技术有限公司 | 一种内存交织方法及装置 |

| US11520514B2 (en) | 2018-09-06 | 2022-12-06 | Pure Storage, Inc. | Optimized relocation of data based on data characteristics |

| US11354058B2 (en) | 2018-09-06 | 2022-06-07 | Pure Storage, Inc. | Local relocation of data stored at a storage device of a storage system |

| US11868309B2 (en) | 2018-09-06 | 2024-01-09 | Pure Storage, Inc. | Queue management for data relocation |

| US11500570B2 (en) | 2018-09-06 | 2022-11-15 | Pure Storage, Inc. | Efficient relocation of data utilizing different programming modes |

| US10783025B2 (en) | 2018-10-15 | 2020-09-22 | Dell Products, L.P. | Method and apparatus for predictive failure handling of interleaved dual in-line memory modules |

| US10454498B1 (en) | 2018-10-18 | 2019-10-22 | Pure Storage, Inc. | Fully pipelined hardware engine design for fast and efficient inline lossless data compression |

| US10976947B2 (en) | 2018-10-26 | 2021-04-13 | Pure Storage, Inc. | Dynamically selecting segment heights in a heterogeneous RAID group |

| US10990517B1 (en) * | 2019-01-28 | 2021-04-27 | Xilinx, Inc. | Configurable overlay on wide memory channels for efficient memory access |

| US11334254B2 (en) | 2019-03-29 | 2022-05-17 | Pure Storage, Inc. | Reliability based flash page sizing |

| US11775189B2 (en) | 2019-04-03 | 2023-10-03 | Pure Storage, Inc. | Segment level heterogeneity |

| US11099986B2 (en) | 2019-04-12 | 2021-08-24 | Pure Storage, Inc. | Efficient transfer of memory contents |

| TWI692774B (zh) | 2019-05-15 | 2020-05-01 | 瑞昱半導體股份有限公司 | 記憶體系統及記憶體系統的操作方法 |

| US11714572B2 (en) | 2019-06-19 | 2023-08-01 | Pure Storage, Inc. | Optimized data resiliency in a modular storage system |

| US11281394B2 (en) | 2019-06-24 | 2022-03-22 | Pure Storage, Inc. | Replication across partitioning schemes in a distributed storage system |

| CN112395216A (zh) * | 2019-07-31 | 2021-02-23 | 北京百度网讯科技有限公司 | 用于存储管理的方法、装置、设备和计算机可读存储介质 |

| US11893126B2 (en) | 2019-10-14 | 2024-02-06 | Pure Storage, Inc. | Data deletion for a multi-tenant environment |

| US11847331B2 (en) | 2019-12-12 | 2023-12-19 | Pure Storage, Inc. | Budgeting open blocks of a storage unit based on power loss prevention |

| US11416144B2 (en) | 2019-12-12 | 2022-08-16 | Pure Storage, Inc. | Dynamic use of segment or zone power loss protection in a flash device |

| US11704192B2 (en) | 2019-12-12 | 2023-07-18 | Pure Storage, Inc. | Budgeting open blocks based on power loss protection |

| US11137936B2 (en) * | 2020-01-21 | 2021-10-05 | Google Llc | Data processing on memory controller |

| US11188432B2 (en) | 2020-02-28 | 2021-11-30 | Pure Storage, Inc. | Data resiliency by partially deallocating data blocks of a storage device |

| US11222258B2 (en) | 2020-03-27 | 2022-01-11 | Google Llc | Load balancing for memory channel controllers |

| US11507297B2 (en) | 2020-04-15 | 2022-11-22 | Pure Storage, Inc. | Efficient management of optimal read levels for flash storage systems |

| US11256587B2 (en) | 2020-04-17 | 2022-02-22 | Pure Storage, Inc. | Intelligent access to a storage device |

| US11474986B2 (en) | 2020-04-24 | 2022-10-18 | Pure Storage, Inc. | Utilizing machine learning to streamline telemetry processing of storage media |

| US11416338B2 (en) | 2020-04-24 | 2022-08-16 | Pure Storage, Inc. | Resiliency scheme to enhance storage performance |

| US11768763B2 (en) | 2020-07-08 | 2023-09-26 | Pure Storage, Inc. | Flash secure erase |

| EP4189548A1 (en) * | 2020-08-03 | 2023-06-07 | ARRIS Enterprises LLC | Gateway device with clock speed that reduces electro-magnetic noise |

| US11681448B2 (en) | 2020-09-08 | 2023-06-20 | Pure Storage, Inc. | Multiple device IDs in a multi-fabric module storage system |

| US11513974B2 (en) | 2020-09-08 | 2022-11-29 | Pure Storage, Inc. | Using nonce to control erasure of data blocks of a multi-controller storage system |

| US11487455B2 (en) | 2020-12-17 | 2022-11-01 | Pure Storage, Inc. | Dynamic block allocation to optimize storage system performance |

| US11614880B2 (en) | 2020-12-31 | 2023-03-28 | Pure Storage, Inc. | Storage system with selectable write paths |

| US11847324B2 (en) | 2020-12-31 | 2023-12-19 | Pure Storage, Inc. | Optimizing resiliency groups for data regions of a storage system |

| WO2022160214A1 (zh) * | 2021-01-28 | 2022-08-04 | 华为技术有限公司 | 一种访问内存的方法和装置 |

| CN116472520A (zh) * | 2021-01-30 | 2023-07-21 | 华为技术有限公司 | 一种访问内存的方法和装置 |

| US11630593B2 (en) | 2021-03-12 | 2023-04-18 | Pure Storage, Inc. | Inline flash memory qualification in a storage system |

| US11507597B2 (en) | 2021-03-31 | 2022-11-22 | Pure Storage, Inc. | Data replication to meet a recovery point objective |

| US11832410B2 (en) | 2021-09-14 | 2023-11-28 | Pure Storage, Inc. | Mechanical energy absorbing bracket apparatus |

| WO2023122127A1 (en) * | 2021-12-21 | 2023-06-29 | Sambanova Systems Inc | Non-uniform memory interleaving processor and method |

| CN114661711B (zh) * | 2022-03-11 | 2023-08-29 | 上海原能细胞生物低温设备有限公司 | 样本存储位置分配方法、装置、电子设备及存储介质 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5341486A (en) * | 1988-10-27 | 1994-08-23 | Unisys Corporation | Automatically variable memory interleaving system |

| JPH11338768A (ja) * | 1998-05-22 | 1999-12-10 | Nec Kofu Ltd | メモリ制御方法、メモリ制御装置及びその記録媒体 |

| US7114040B2 (en) | 2004-03-02 | 2006-09-26 | Hewlett-Packard Development Company, L.P. | Default locality selection for memory objects based on determining the type of a particular memory object |

| US8806103B2 (en) | 2004-04-28 | 2014-08-12 | Hewlett-Packard Development Company, L.P. | System and method for interleaving memory |

| TWI299497B (en) * | 2004-06-24 | 2008-08-01 | Via Tech Inc | Method and related apparatus for accessing memory apparatus |

| JP2006018489A (ja) * | 2004-06-30 | 2006-01-19 | Hitachi Ltd | 複数ノード間のメモリインターリーブシステム |

| US8443162B2 (en) * | 2005-01-21 | 2013-05-14 | Qualcomm Incorporated | Methods and apparatus for dynamically managing banked memory |

| US20070022261A1 (en) | 2005-07-19 | 2007-01-25 | Gateway Inc. | Method of interleaving asymmetric memory arrays |

| US7552280B1 (en) * | 2006-06-28 | 2009-06-23 | Emc Corporation | Asymmetrically interleaving access to redundant storage devices |

| US20080250212A1 (en) | 2007-04-09 | 2008-10-09 | Ati Technologies Ulc | Method and apparatus for accessing memory using programmable memory accessing interleaving ratio information |

| US8095735B2 (en) | 2008-08-05 | 2012-01-10 | Convey Computer | Memory interleave for heterogeneous computing |

| US8271827B2 (en) | 2007-12-10 | 2012-09-18 | Qimonda | Memory system with extended memory density capability |

| US20100115233A1 (en) * | 2008-10-31 | 2010-05-06 | Convey Computer | Dynamically-selectable vector register partitioning |

| US8266408B2 (en) | 2009-03-17 | 2012-09-11 | Memoir Systems, Inc. | System and method for storing data in a virtualized high speed memory system |

| US8886898B2 (en) | 2009-08-19 | 2014-11-11 | Oracle America, Inc. | Efficient interleaving between a non-power-of-two number of entities |

| US9268720B2 (en) * | 2010-08-31 | 2016-02-23 | Qualcomm Incorporated | Load balancing scheme in multiple channel DRAM systems |

| US9529712B2 (en) * | 2011-07-26 | 2016-12-27 | Nvidia Corporation | Techniques for balancing accesses to memory having different memory types |

-

2013

- 2013-10-03 US US14/045,784 patent/US9465735B2/en active Active

-

2014

- 2014-10-03 CN CN201480054542.5A patent/CN105612501B/zh active Active

- 2014-10-03 CA CA2925131A patent/CA2925131A1/en not_active Abandoned

- 2014-10-03 KR KR1020167011540A patent/KR20160064223A/ko not_active Application Discontinuation

- 2014-10-03 BR BR112016007344A patent/BR112016007344A2/pt not_active Application Discontinuation

- 2014-10-03 JP JP2016518727A patent/JP6378325B2/ja not_active Expired - Fee Related

- 2014-10-03 WO PCT/US2014/058946 patent/WO2015051201A1/en active Application Filing

- 2014-10-03 EP EP14790887.5A patent/EP3053044B1/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20150100746A1 (en) | 2015-04-09 |

| EP3053044A1 (en) | 2016-08-10 |

| CN105612501B (zh) | 2018-11-13 |

| CA2925131A1 (en) | 2015-04-09 |

| JP2016532926A (ja) | 2016-10-20 |

| US9465735B2 (en) | 2016-10-11 |

| BR112016007344A2 (pt) | 2017-08-01 |

| WO2015051201A1 (en) | 2015-04-09 |

| EP3053044B1 (en) | 2019-11-20 |

| CN105612501A (zh) | 2016-05-25 |

| KR20160064223A (ko) | 2016-06-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6378325B2 (ja) | 非対称な記憶容量を有する複数チャネルメモリアーキテクチャにわたってデータを均一にインターリーブするためのシステムおよび方法 | |

| US9612648B2 (en) | System and method for memory channel interleaving with selective power or performance optimization | |

| US10067865B2 (en) | System and method for allocating memory to dissimilar memory devices using quality of service | |

| US9110795B2 (en) | System and method for dynamically allocating memory in a memory subsystem having asymmetric memory components | |

| US10140223B2 (en) | System and method for odd modulus memory channel interleaving | |

| US9430434B2 (en) | System and method for conserving memory power using dynamic memory I/O resizing | |

| CN106575273B (zh) | 用于扩展片上系统的存储器的系统和方法 | |

| US8959298B2 (en) | System and method for managing performance of a computing device having dissimilar memory types | |

| US20170109090A1 (en) | System and method for page-by-page memory channel interleaving | |

| US20170108914A1 (en) | System and method for memory channel interleaving using a sliding threshold address | |

| US20170108911A1 (en) | System and method for page-by-page memory channel interleaving | |

| US20160077959A1 (en) | System and Method for Sharing a Solid-State Non-Volatile Memory Resource |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160406 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170914 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170914 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180625 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180702 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180726 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6378325 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |