JP6205014B2 - Display device - Google Patents

Display device Download PDFInfo

- Publication number

- JP6205014B2 JP6205014B2 JP2016111710A JP2016111710A JP6205014B2 JP 6205014 B2 JP6205014 B2 JP 6205014B2 JP 2016111710 A JP2016111710 A JP 2016111710A JP 2016111710 A JP2016111710 A JP 2016111710A JP 6205014 B2 JP6205014 B2 JP 6205014B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- potential

- gate

- display device

- tft

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Description

本発明は、表示装置の駆動回路に関する。さらに本発明は、前記表示装置の駆動回路を

用いて作製された電子機器を含む。なお本明細書中、表示装置とは、画素に液晶素子を用

いてなる液晶表示装置および、有機エレクトロルミネッセンス(EL)素子を始めとした

自発光素子を用いてなる発光表示装置を含むものとする。駆動回路とは、表示装置に配置

された画素に映像信号を入力し、映像の表示を行うための処理を行う回路を指し、シフト

レジスタ等を始めとするパルス回路や、アンプ等を始めとする増幅回路を含むものとする

。

The present invention relates to a driving circuit for a display device. Furthermore, the present invention includes an electronic device manufactured using the driving circuit of the display device. Note that in this specification, a display device includes a liquid crystal display device using a liquid crystal element for a pixel and a light-emitting display device using a self-light-emitting element such as an organic electroluminescence (EL) element. A driving circuit refers to a circuit that inputs a video signal to a pixel arranged in a display device and performs processing for displaying a video, and includes a pulse circuit including a shift register and an amplifier. An amplifier circuit is included.

近年、絶縁体上、特にガラス基板上に半導体薄膜を形成した表示装置、特に薄膜トラン

ジスタ(以下、TFTと表記)を用いたアクティブマトリクス型表示装置の普及が顕著と

なっている。TFTを使用したアクティブマトリクス型表示装置は、マトリクス状に配置

された数十万から数百万の画素を有し、各画素に配置されたTFTによって各画素の電荷

を制御することによって映像の表示を行っている。

In recent years, a display device in which a semiconductor thin film is formed over an insulator, particularly a glass substrate, in particular, an active matrix display device using a thin film transistor (hereinafter referred to as TFT) has become widespread. An active matrix display device using TFTs has hundreds of thousands to millions of pixels arranged in a matrix, and displays the image by controlling the charge of each pixel by the TFT arranged in each pixel. It is carried out.

さらに最近の技術として、画素を構成する画素TFTの他に、画素部の周辺領域にTF

Tを用いて駆動回路を同時形成するポリシリコンTFTに関する技術が発展してきており

、装置の小型化、低消費電力化に大いに貢献し、それに伴って、近年その応用分野の拡大

が著しいモバイル情報端末の表示部等に、表示装置は不可欠なデバイスとなってきている

。

Furthermore, as a recent technology, in addition to the pixel TFT constituting the pixel, TF is provided in the peripheral region of the pixel portion.

A technology related to polysilicon TFTs that simultaneously form a drive circuit using T has been developed, greatly contributing to downsizing and low power consumption of the device. The display device has become an indispensable device for the display unit and the like.

表示装置の駆動回路としては、N型TFTとP型TFTを組み合わせたCMOS回路が

一般的に使用されている。CMOS回路の特徴として、論理が変わる(Hi電位からLo

電位へ、あるいはLo電位からHi電位へ)瞬間にのみ電流が流れ、ある論理の保持中に

は電流が流れない(実際には微小なリーク電流の存在がある)ため、回路全体での消費電

流を低く抑えることが可能な点や、高速駆動に有利な点が挙げられる。

As a drive circuit for a display device, a CMOS circuit in which an N-type TFT and a P-type TFT are combined is generally used. As a feature of CMOS circuits, logic changes (from Hi potential to Lo

The current flows only at the moment (from the potential or from the Lo potential to the Hi potential), and does not flow while holding a certain logic (actually there is a small leakage current), so the current consumption in the entire circuit Can be kept low, and it is advantageous for high-speed driving.

液晶や自発光素子を用いた表示装置の需要は、モバイル電子機器の小型化、軽量化に伴

って急速にその需要が増加しているが、歩留まり等の面から、その製造コストを十分に低

く抑えることが難しい。今後の需要はさらに急速に増加することは容易に予測され、その

ため表示装置をより安価に供給できるようにすることが望まれている。

Demand for display devices using liquid crystals and self-luminous elements has been increasing rapidly as mobile electronic devices have become smaller and lighter, but their production costs have been reduced sufficiently in terms of yield and other factors. It is difficult to suppress. It is easily predicted that future demand will increase more rapidly, and it is therefore desirable to be able to supply display devices at a lower cost.

絶縁体上に駆動回路を作製する方法としては、複数のフォトマスクを用いて、活性層、

配線等のパターンを露光、エッチングを行って作りこんでいく方法が一般的であるが、こ

のときの工程数の多さが製造コストに直接影響しているため、可能な限り少ない工程数で

製造することが理想的である。そこで、従来CMOS回路によって構成されていた駆動回

路を、N型もしくはP型のいずれか一方の導電型のみのTFTを用いて構成する。この方

法により、イオンドーピング工程の一部を省略することが出来、さらにフォトマスクの枚

数も削減することが出来る。

As a method for manufacturing a driver circuit over an insulator, an active layer, a plurality of photomasks,

It is common to create patterns by exposing and etching patterns such as wiring, but since the large number of processes at this time directly affects the manufacturing cost, it is possible to manufacture with as few processes as possible. Ideal to do. Therefore, a driving circuit that has been configured by a conventional CMOS circuit is configured by using only N-type or P-type TFTs. By this method, part of the ion doping process can be omitted, and the number of photomasks can be reduced.

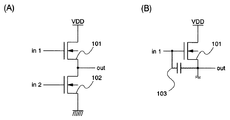

(本発明以前の技術の問題点)

図9(A)は、従来一般的に用いられているCMOSインバータ(I)と、一極性のみ

のTFTを用いて構成したインバータ(II)(III)の例を示している。(II)はTFT

負荷型のインバータ、(III)は抵抗負荷型のインバータである。以下に、それぞれの動

作について述べる。

(Problems of the technology prior to the present invention)

FIG. 9A shows an example of a CMOS inverter (I) that is generally used conventionally and inverters (II) and (III) that are configured using TFTs having only one polarity. (II) is TFT

A load type inverter (III) is a resistance load type inverter. Each operation will be described below.

図9(B)は、インバータに入力する信号の波形を示している。ここで、入力信号振幅

はVDD−GND間(GND<VDD)とする。具体的にはGND=0[V]として考える

。

FIG. 9B shows the waveform of a signal input to the inverter. Here, the input signal amplitude is between VDD and GND (GND <VDD). Specifically, it is considered that GND = 0 [V].

回路動作について説明する。なお、説明を明確かつ簡単にするため、回路を構成するN

型TFTのしきい値電圧は、そのばらつきがないものとして一律(VthN)とする。ま

た、P型TFTについても同様に、一律(VthP)とする。

The circuit operation will be described. For clarity and simplicity of explanation, N constituting the circuit

The threshold voltage of the type TFT is uniform (VthN) assuming that there is no variation. Similarly, the P-type TFT is set to be uniform (VthP).

CMOSインバータに図9(B)のような信号が入力されると、入力信号の電位がHi

(VDD)のとき、P型TFT901はOFFし、N型TFT902がONすることによ

り、出力ノードの電位はLo(GND)となる。逆に、入力信号の電位がLoのとき、P

型TFT901がONし、N型TFT902がOFFすることにより、出力ノードの電位

はHiとなる(図9(C))。

When a signal as shown in FIG. 9B is input to the CMOS inverter, the potential of the input signal becomes Hi.

At (VDD), the P-

When the

続いて、TFT負荷型インバータ(II)の動作について説明する。同じく図9(B)に

示すような信号が入力される場合を考える。まず、入力信号がLoのとき、N型TFT9

04はOFFする。一方、負荷TFT903は常に飽和動作していることから、出力ノー

ドの電位はHi方向に引き上げられる。一方、入力信号がHiのとき、N型TFT904

はONする。ここで、負荷TFT903の電流能力よりも、N型TFT904の電流能力

を十分に高くしておくことにより、出力ノードの電位はLo方向に引き下げられる。

Next, the operation of the TFT load type inverter (II) will be described. Consider the case where a signal as shown in FIG. First, when the input signal is Lo, the N-type TFT 9

04 turns off. On the other hand, since the load TFT 903 always operates in saturation, the potential of the output node is raised in the Hi direction. On the other hand, when the input signal is Hi, the N-

Turns on. Here, by making the current capability of the N-

抵抗負荷型インバータ(III)についても同様に、N型TFT906のON抵抗値を、

負荷抵抗905の抵抗値よりも十分に低くしておくことにより、入力信号がHiのときは

、N型TFT906がONすることにより、出力ノードはLo方向に引き下げられる。入

力信号がLoのときは、N型TFT906はOFFし、出力ノードはHi方向に引き上げ

られる。

Similarly, for the resistance load type inverter (III), the ON resistance value of the

By making it sufficiently lower than the resistance value of the

ただし、TFT負荷型インバータや抵抗負荷型インバータを用いる際、以下のような問

題点がある。図9(D)は、TFT負荷型インバータの出力波形を示したものであるが、

出力がHiのときに、907で示す分だけVDDよりも電位が低くなる。負荷TFT90

3において、出力ノード側の端子をソース、電源VDD側の端子をドレインとすると、ゲ

ート電極とドレイン領域が接続されているので、このときのゲート電極の電位はVDDで

ある。また、この負荷TFTがONしているための条件は、(TFT903のゲート−ソ

ース間電圧>VthN)であるから、出力ノードの電位は、最大でも(VDD−VthN

)までしか上昇しない。つまり、907はVthNに等しい。さらに、負荷TFT903

とN型TFT904の電流能力の比によっては、出力電位がLo電位のとき、908で示

す分だけGNDよりも電位が高くなる。これを十分にGNDに近づけるためには、負荷T

FT903に対し、N型TFT904の電流能力を十分に大きくする必要がある。同様に

、図9(E)は抵抗負荷型インバータの出力波形を示したものであるが、負荷抵抗905

の抵抗値とN型TFT906のON抵抗の比によっては、909で示す分だけ電位が高く

なる。つまり、ここに示した一極性のみのTFTを用いて構成したインバータを用いると

、入力信号の振幅に対し、出力信号の振幅減衰が生ずることになる。駆動回路を構成する

には、振幅が減衰することなく出力が得られなければならない。

However, when using a TFT load type inverter or a resistance load type inverter, there are the following problems. FIG. 9D shows the output waveform of the TFT load type inverter.

When the output is Hi, the potential is lower than VDD by the amount indicated by 907. Load TFT90

3, if the terminal on the output node side is the source and the terminal on the power supply VDD side is the drain, the gate electrode and the drain region are connected, so the potential of the gate electrode at this time is VDD. Further, since the condition for turning on the load TFT is (the gate-source voltage of the

) Only rises. That is, 907 is equal to VthN. Furthermore, the

Depending on the ratio of the current capability of the N-

It is necessary to sufficiently increase the current capability of the N-

Depending on the ratio between the resistance value of N-

本発明は、以上のような課題を鑑見てなされたものであり、一極性のみのTFTを用い

て製造工程を削減することにより低コストで作製が可能であり、かつ振幅減衰のない出力

を得ることが出来る表示装置の駆動回路を提供することを目的とする。

The present invention has been made in view of the above problems, and can be manufactured at a low cost by reducing the manufacturing process by using a TFT having only one polarity, and can provide an output without amplitude attenuation. It is an object to provide a driver circuit for a display device that can be obtained.

先程の図9(A)の(II)に示したTFT負荷型インバータにおいて、出力信号の振幅

が正常にVDD−GNDを取るための条件を考える。第1に、図1(A)のような回路に

おいて、出力信号の電位がLoとなるとき、その電位を十分にGNDに近づけるためには

、電源VDD−出力ノード間の抵抗値に対し、電源GND−出力ノード間の抵抗値が十分

に低くなっていればよい。すなわち、N型TFT102がONしている期間、N型TFT

101がOFFしていればよい。第2に、出力信号の電位がHiとなるとき、その電位が

VDDに等しくなるには、N型TFT101のゲート−ソース間電圧の絶対値が、Vth

Nを常に上回っていればよい。つまり、出力ノードのHi電位がVDDとなる条件を満た

すには、N型TFT101のゲート電極の電位は(VDD+VthN)よりも高くなる必

要がある。回路に供給される電源はVDD、GNDの2種類のみであるから、VDDより

も電位の高い第3の電源がない限り、条件を満たすことは出来ない。

In the TFT load type inverter shown in (II) of FIG. 9A, the conditions for the output signal amplitude to normally take VDD-GND are considered. First, in the circuit as shown in FIG. 1A, when the potential of the output signal becomes Lo, in order to bring the potential sufficiently close to GND, the resistance value between the power supply VDD and the output node is It is sufficient that the resistance value between the GND and the output node is sufficiently low. That is, during the period when the N-

101 should just be OFF. Second, when the potential of the output signal becomes Hi, in order for the potential to be equal to VDD, the absolute value of the gate-source voltage of the N-

It is only necessary to always exceed N. That is, in order to satisfy the condition that the Hi potential of the output node becomes VDD, the potential of the gate electrode of the N-

そこで、本発明では以下のような手段を講じた。図1(B)に示すように、N型TFT

101のゲート−ソース間に容量103を設ける。N型TFT101のゲート電極がある

電位をもって浮遊状態となったとき、出力ノードの電位を上昇させると、この容量103

による容量結合によって、出力ノードの電位上昇分に伴って、N型TFT101のゲート

電極の電位も持ち上げられる。この効果を利用すれば、N型TFT101のゲート電極の

電位をVDDよりも高く(正確には、VDD+VthNよりも高く)することが可能とな

る。よって出力ノードの電位を十分にVDDまで引き上げることが可能となる。

Therefore, the following measures are taken in the present invention. As shown in FIG. 1B, an N-type TFT

A

Due to the capacitive coupling, the potential of the gate electrode of the N-

なお、図1(B)において示した容量103は、実際に容量部分を作製しても良いし、

TFT101のゲート−ソース間に寄生する容量を利用するようにしても良い。

Note that the

A parasitic capacitance between the gate and source of the

本発明の構成を以下に記す。 The configuration of the present invention will be described below.

請求項1の記載によると、本発明の表示装置の駆動回路は、第1の不純物領域が第1の

電源と電気的に接続された、第1のトランジスタと、 第1の不純物領域が第2の電源と

電気的に接続された、第2のトランジスタと、 第1の不純物領域が第1の電源と電気的

に接続された、第3のトランジスタと、 第1の不純物領域が第2の電源と電気的に接続

された、第4のトランジスタと、容量とを有する表示装置の駆動回路であって、前記第1

乃至第4のトランジスタはいずれも同一導電型であり、 前記第1のトランジスタの第2

の不純物領域と、前記第2のトランジスタの第2の不純物領域とはいずれも前記容量の一

方の端子と電気的に接続され、 前記第3のトランジスタの第2の不純物領域と、前記第

4のトランジスタの第2の不純物領域と、前記第1のトランジスタのゲート電極とは、い

ずれも前記容量の他の一方の端子と電気的に接続され、 前記第2のトランジスタのゲー

ト電極と、前記第4のトランジスタのゲート電極は、入力信号線と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第1の電源と電気的に接続されていること

を特徴としている。

According to the first aspect of the present invention, the driver circuit for the display device according to the present invention includes a first transistor in which the first impurity region is electrically connected to the first power source, and the first impurity region is in the second state. A second transistor electrically connected to the first power source, a third transistor whose first impurity region is electrically connected to the first power source, and a first impurity region serving as the second power source. A display device drive circuit having a fourth transistor and a capacitor electrically connected to the first transistor, wherein

The fourth to fourth transistors all have the same conductivity type, and the second transistor of the first transistor

And the second impurity region of the second transistor are electrically connected to one terminal of the capacitor, the second impurity region of the third transistor, and the fourth impurity region of the second transistor, The second impurity region of the transistor and the gate electrode of the first transistor are both electrically connected to the other terminal of the capacitor, the gate electrode of the second transistor, and the fourth electrode The gate electrode of the transistor is electrically connected to the input signal line,

The gate electrode of the third transistor is electrically connected to the first power source.

請求項2の記載によると、本発明の表示装置の駆動回路は、第1の不純物領域が第1の

電源と電気的に接続された、第1のトランジスタと、 第1の不純物領域が第2の電源と

電気的に接続された、第2のトランジスタと、 第1の不純物領域が第1の電源と電気的

に接続された、第3のトランジスタと、 第1の不純物領域が第2の電源と電気的に接続

された、第4のトランジスタと、 容量とを有する表示装置の駆動回路であって、前記第

1乃至第4のトランジスタはいずれも同一導電型であり、 前記第1のトランジスタの第

2の不純物領域と、前記第2のトランジスタの第2の不純物領域とはいずれも前記容量の

一方の端子と電気的に接続され、 前記第3のトランジスタの第2の不純物領域と、前記

第4のトランジスタの第2の不純物領域と、前記第1のトランジスタのゲート電極とは、

いずれも前記容量の他の一方の端子と電気的に接続され、 前記第2のトランジスタのゲ

ート電極と、前記第4のトランジスタのゲート電極は、第1の入力信号線と電気的に接続

され、 前記第3のトランジスタのゲート電極は、第2の入力信号線と電気的に接続され

ていることを特徴としている。

According to a second aspect of the present invention, the driver circuit for the display device according to the present invention includes a first transistor in which the first impurity region is electrically connected to the first power source, and the first impurity region is in the second state. A second transistor electrically connected to the first power source, a third transistor whose first impurity region is electrically connected to the first power source, and a first impurity region serving as the second power source. And a fourth transistor electrically connected to the display device, and a capacitor, wherein the first to fourth transistors are all of the same conductivity type. The second impurity region and the second impurity region of the second transistor are both electrically connected to one terminal of the capacitor, the second impurity region of the third transistor, Second impurity region of transistor 4 A gate electrode of the first transistor,

Both are electrically connected to the other terminal of the capacitor, and the gate electrode of the second transistor and the gate electrode of the fourth transistor are electrically connected to the first input signal line, The gate electrode of the third transistor is electrically connected to the second input signal line.

請求項3の記載によると、本発明の表示装置の駆動回路は、 請求項2において、 前

記第2の入力信号線は、前記第1の入力信号線に入力される信号の反転信号が入力される

信号線であることを特徴としている。

According to a third aspect of the present invention, in the display device driving circuit according to the second aspect of the present invention, in the second aspect, the second input signal line receives an inverted signal of a signal input to the first input signal line. It is characterized by being a signal line.

請求項4の記載によると、本発明の表示装置の駆動回路は、 請求項1もしくは請求項

2において、 前記容量は、前記第1のトランジスタのゲート電極と、前記不純物領域の

うちいずれか一方との間の容量を用いることを特徴としている。

According to a fourth aspect of the present invention, in the display device driving circuit according to the first or second aspect of the present invention, in the first or second aspect, the capacitor includes a gate electrode of the first transistor and one of the impurity regions. It is characterized by using a capacity between.

請求項5の記載によると、本発明の表示装置の駆動回路は、 請求項1もしくは請求項

2において、 前記容量は、活性層材料、ゲート電極を構成する材料、あるいは配線材料

のうちのいずれか2つの材料を用いて構成された容量であることを特徴としている。

According to a fifth aspect of the present invention, in the display device drive circuit according to the first or second aspect of the present invention, the capacitor is any one of an active layer material, a material constituting a gate electrode, or a wiring material. It is characterized by a capacity constituted by using two materials.

請求項6の記載によると、本発明の表示装置の駆動回路は、 請求項1乃至請求項5の

いずれか1項において、 前記一導電型とは、Nチャネル型であることを特徴としている

。

According to a sixth aspect of the present invention, in the display device driving circuit according to the present invention, the one conductivity type is an N-channel type in any one of the first to fifth aspects.

請求項7の記載によると、本発明の表示装置の駆動回路は、 請求項1乃至請求項5の

いずれか1項において、 前記一導電型とは、Pチャネル型であることを特徴としている

。

According to a seventh aspect of the present invention, in the display device drive circuit according to the present invention, the one conductivity type is a P-channel type in any one of the first to fifth aspects.

請求項8の記載によると、本発明の表示装置の駆動回路は、 請求項6において、前記

入力信号がHi電位のときの電位は第3の電源電位に等しく、Lo電位のときの電位は第

4の電源電位に等しいとき、 第2の電源電位≦第4の電源電位<第3の電源電位≦第1

の電源電位を満たすことを特徴としている。

According to an eighth aspect of the present invention, in the display device driving circuit according to the sixth aspect, the potential when the input signal is the Hi potential is equal to the third power supply potential, and the potential when the input signal is the Lo potential is the first potential. When the power source potential is equal to 4, the second power source potential ≦ the fourth power source potential <the third power source potential ≦ the first power source potential

The power supply potential is satisfied.

請求項9の記載によると、本発明の表示装置の駆動回路は、 請求項7において、前記

入力信号がHi電位のときの電位は第3の電源電位に等しく、Lo電位のときの電位は第

4の電源電位に等しいとき、 第1の電源電位≦第4の電源電位<第3の電源電位≦第2

の電源電位を満たすことを特徴としている。

According to a ninth aspect of the present invention, in the display device driving circuit according to the seventh aspect, the potential when the input signal is the Hi potential is equal to the third power supply potential, and the potential when the input signal is the Lo potential is the first potential. When the power supply potential is equal to 4, the first power supply potential ≦ the fourth power supply potential <the third power supply potential ≦ the second power supply potential

The power supply potential is satisfied.

請求項10の記載によると、本発明の表示装置の駆動回路は、 請求項1乃至請求項9

のいずれか1項において、前記表示装置の駆動回路は、インバータ、バッファ、あるいは

レベルシフタであること、あるいはインバータ、バッファあるいはレベルシフタの構成要

件となっていることを特徴としている。

According to a tenth aspect of the present invention, the drive circuit for the display device according to the present invention includes the first to ninth aspects.

In any one of the above, the driving circuit of the display device is an inverter, a buffer, or a level shifter, or is a constituent requirement of the inverter, buffer, or level shifter.

本発明の表示装置の駆動回路によって、表示装置の駆動回路および画素部を、一導電型

のTFTのみによって構成することが可能となり、表示装置の作製工程を削減することに

よって、低コスト化、歩留まりの向上に寄与し、より安価に表示装置の供給が可能となる

。

With the display device driver circuit of the present invention, the display device driver circuit and the pixel portion can be formed using only one-conductivity type TFT, and the manufacturing cost of the display device can be reduced, thereby reducing costs and yield. The display device can be supplied at a lower cost.

図2(A)は、本発明の表示装置の駆動回路の1形態を示したものであり、インバータ

として機能する回路である。N型TFT201〜204および容量205によって構成さ

れており、点線枠206で囲われた部分が、図1(A)に示した回路に相当する。点線枠

210で囲われた部分が、出力振幅補償回路を構成している。出力振幅補償回路210は

、N型TFT203のゲート電極に浮遊状態を作り出すことを目的としたものであり、同

一の機能を有する限り、図2(A)

の構成に限定しない。

FIG. 2A illustrates one mode of a driver circuit of a display device of the present invention, which is a circuit that functions as an inverter. A portion formed by the N-

It is not limited to the configuration.

図2(A)の回路において、入力信号はN型TFT202およびN型TFT204のゲ

ート電極に入力される。N型TFT201は負荷として機能し、N型TFT201、20

2によって構成される回路からの出力(図2(A)中、このノードをαとおく)が、N型

TFT203のゲート電極に入力される。

In the circuit of FIG. 2A, an input signal is input to the gate electrodes of the N-

2 is input to the gate electrode of the N-type TFT 203 (the node in FIG. 2A is set to α).

回路の動作詳細について順を追って説明する。なお、電源電位はVDDおよびGND、

入力信号の振幅もVDD(Hi)−GND(Lo)とする。まず、入力信号の電位がHi

のとき、N型TFT202、204がONする。ここで、N型TFT201はゲート電極

とドレイン領域とが接続されているため飽和動作しているが、N型TFT202の電流能

力をN型TFT201の電流能力よりも十分に高くすることによって、ノードαの電位は

GND側に引き下げられる。これにより、N型TFT203がOFFし、出力ノードには

Lo電位が出力される。

The operation details of the circuit will be described step by step. The power supply potential is VDD and GND,

The amplitude of the input signal is also VDD (Hi) -GND (Lo). First, the potential of the input signal is Hi

At this time, the N-

続いて、入力信号の電位がLoのとき、N型TFT202、204がOFFする。これ

により、ノードαの電位は、VDD側に引き上げられ、その電位が(VDD−VthN)

となったところで一旦浮遊状態となる。一方、ノードαの電位が上昇を始めると、やがて

N型TFT203がONし、出力ノードの電位がVDD側に引き上げられる。ノードαが

浮遊状態となったとき、依然出力ノードの電位は上昇を続けているため、N型TFT20

3のゲート−ソース間容量205の存在によって、出力ノードの電位上昇に伴い、浮遊状

態にあるノードαの電位も上昇する。これにより、ノードαの電位が、(VDD+Vth

N)よりも高い電位となることが出来る。よって、出力ノードにはHi電位が出力され、

このときの電位はVDDに等しくなる。

Subsequently, when the potential of the input signal is Lo, the N-

When it becomes, it becomes a floating state once. On the other hand, when the potential of the node α starts to rise, the N-

As a result of the presence of the gate-

N) can be a higher potential. Therefore, the Hi potential is output to the output node,

The potential at this time is equal to VDD.

以上のような動作により、出力信号の振幅は、入力信号の振幅に対して減衰なく得られ

る。このように、2点間の容量結合を利用して電位を引き上げる方法をブートストラップ

法という。図2(B)は、図2(A)に示した回路の入力信号の波形を示したものであり

、図2(C)は、ノードαにおける電位の波形を示したものであり、図2(D)は出力信

号の波形を示したものである。図2(C)中、208で示される電位は、VDDよりもV

thNだけ低下した電位であり、ブートストラップによって、207で示す分だけ、ノー

ドαの電位が引き上げられる。結果、図2(D)に示すように、出力ノードがHi電位の

とき、その電位はVDDまで上昇し、VDD−GND間の振幅を有する出力信号を得るこ

とが出来る。

By the operation as described above, the amplitude of the output signal can be obtained without attenuation with respect to the amplitude of the input signal. A method of raising the potential by using capacitive coupling between two points in this way is called a bootstrap method. 2B shows the waveform of the input signal of the circuit shown in FIG. 2A, and FIG. 2C shows the waveform of the potential at the node α. (D) shows the waveform of the output signal. In FIG. 2C, the potential indicated by 208 is V more than VDD.

The potential is lowered by thN, and the potential of the node α is raised by the amount indicated by 207 by the bootstrap. As a result, as shown in FIG. 2D, when the output node is at the Hi potential, the potential rises to VDD, and an output signal having an amplitude between VDD and GND can be obtained.

ところで、本発明の表示装置の駆動回路においては、ブートストラップ法による出力信

号の振幅補償を動作の基本としているが、そのとき、容量結合を利用するTFTのゲート

電極が浮遊状態となっていることが前提となる。図10は、ブートストラップ法を利用し

た回路の構成例を挙げているが、図10(A)は本発明の表示装置の駆動回路の基本構成

を示しているが、ノードαが浮遊状態となっていることにより、TFT1003のゲート

−ソース間の容量1005を利用してノードαの電位を引き上げ、それによって出力信号

の振幅を補償する。図10(B)は3個のTFTからなる回路を示しているが、こちらに

ついても同様に、ノードβが浮遊状態となっていることにより、TFT1007のゲート

−ソース間容量1009を利用してノードβの電位を引き上げ、それによって出力信号の

振幅を補償する。

By the way, in the drive circuit of the display device of the present invention, the operation is based on the amplitude compensation of the output signal by the bootstrap method. At that time, the gate electrode of the TFT using the capacitive coupling is in a floating state. Is the premise. FIG. 10 shows a configuration example of a circuit using the bootstrap method. FIG. 10A shows a basic configuration of a driver circuit of the display device of the present invention, but the node α is in a floating state. Therefore, the potential of the node α is raised using the gate-

続いて、入力信号の振幅と電源電位について考える。今、高電位側の電源電位はVDD

、低電位側の電源電位はGNDであり、入力信号(in)の振幅はVDD−GNDであり

、inbは入力信号の反転信号である。ここで、in、inbの振幅がそれぞれVDD3

−GND(ただし、GND<VthN<VDD3<VDD−VthN)である場合のノー

ドα、ノードβの状態について考える。図10(A)において、inbがHiのとき、N

型TFT1001のゲート電極電位はVDD3となる。VthN<VDD3であるから、

N型TFT1001はONし、ノードαの電位はVDD側に引き上げられ、その電位が(

VDD3−VthN)となったところで浮遊状態となる。つまり、inbのHi電位がV

thNを上回っていれば、ノードαは確実に浮遊状態となることが出来、ブートストラッ

プによってN型TFT1003のゲート電極電位を引き上げる動作が可能となる。一方、

図10(B)においては、N型TFT1006のゲート電極電位は常にVDDであるから

、inbがHiのとき、ノードβの電位はVDD3まで引き上げられる。ただし今、VD

D3<VDD−VthNであるから、N型TFT1006は入力信号の電位に関わらず常

にONの状態を取る。よってノードβは浮遊状態とはならない。故に、ブートストラップ

によってノードβの電位を引き上げることが出来ないことになる。つまり、図10(B)

に示した回路の場合、ノードβが浮遊状態となるためには、inbのLo電位がGNDで

あるとき、少なくともHi電位が(VDD−VthN)以上にあるという最低条件がある

ため、低電圧駆動やTFTの特性ばらつきの面を考えると不利である。

Next, the amplitude of the input signal and the power supply potential will be considered. The power supply potential on the high potential side is now VDD

The power supply potential on the low potential side is GND, the amplitude of the input signal (in) is VDD-GND, and inb is an inverted signal of the input signal. Here, the amplitude of in and inb is VDD3

Consider the state of the nodes α and β when −GND (where GND <VthN <VDD3 <VDD−VthN). In FIG. 10A, when inb is Hi, N

The gate electrode potential of the

The N-

When it becomes VDD3-VthN), it enters a floating state. That is, the Hi potential of inb is V

If it exceeds thN, the node α can surely be in a floating state, and an operation of raising the gate electrode potential of the N-

In FIG. 10B, since the gate electrode potential of the N-

Since D3 <VDD−VthN, the N-

In the case of the circuit shown in FIG. 2, in order for the node β to be in a floating state, there is a minimum condition that at least the Hi potential is (VDD−VthN) or more when the Lo potential of inb is GND. And it is disadvantageous when considering the characteristics variation of TFT.

このように、入力信号の振幅が電源電圧よりも小さい場合の、ある特定の条件下では、

図10(B)のような構成ではノードβに浮遊状態を与えられない可能性が考えられるの

に対し、本発明で示した図10(A)の構成であれば、確実にノードαを浮遊状態に出来

るメリットがある。

Thus, under certain conditions when the amplitude of the input signal is smaller than the power supply voltage,

In the configuration as shown in FIG. 10B, there is a possibility that the floating state cannot be given to the node β. On the other hand, in the configuration shown in FIG. There is merit that can be made in the state.

以下に、本発明の実施例について記載する。 Examples of the present invention will be described below.

図3(A)は、本発明の表示装置の駆動回路の一形態であるインバータを複数段接続し

た回路を示している。表示装置の駆動回路等においては、このような回路をバッファとし

て用いることが多い。ここで、図3(A)のような回路を用いる場合、以下のようなデメ

リットが挙げられる。

FIG. 3A illustrates a circuit in which a plurality of inverters which are one form of the driver circuit of the display device of the present invention are connected. Such a circuit is often used as a buffer in a driver circuit or the like of a display device. Here, when the circuit as shown in FIG. 3A is used, the following disadvantages can be mentioned.

図3(A)において、入力信号がHiのとき、N型TFT302がONする。

ここで、N型TFT301は、ゲート−ドレイン間を短絡した負荷として機能しており、

常に飽和動作しているため、N型TFT302がONすることによって、VDD−GND

間に貫通電流が流れる。これは、各段のTFT303、304および305、306にお

いても同様であり、消費電流が大きくなってしまう。

In FIG. 3A, when the input signal is Hi, the N-

Here, the N-

Since saturation operation is always performed, VDD-GND is turned on when the N-

A through current flows between them. The same applies to the

このような問題を回避するための例として、図3(B)に示すような、2入力型のイン

バータを用いる方法が挙げられる。このような回路の場合、VDD−GND間に配置され

ているTFTは、入力信号の極性が常に逆であることから、排他的動作をするため、貫通

電流が流れない。

As an example for avoiding such a problem, there is a method using a two-input type inverter as shown in FIG. In the case of such a circuit, the TFT arranged between VDD and GND has an exclusive operation since the polarity of the input signal is always reversed, and therefore, a through current does not flow.

ただし、図3(B)の回路を用いる場合、入力信号として、反転、非反転の2相の信号

を用意する必要がある。

However, in the case of using the circuit of FIG. 3B, it is necessary to prepare an inverted and non-inverted two-phase signal as an input signal.

そこで、双方を組み合わせた形として、図3(C)に示すように、先頭段には本発明の

1入力型インバータを用い、2段目以降は2入力型インバータを用いる。2段目の入力は

、一方には前段の出力信号を、もう一方には前段の入力信号を入力すればよい。これによ

り、1入力型であり、かつ貫通電流を最小限に抑えたバッファとして用いることが出来る

。

Therefore, as a combination of both, as shown in FIG. 3C, the first input uses the one-input inverter of the present invention and the second and subsequent stages use the two-input inverter. As for the input of the second stage, it is only necessary to input the output signal of the previous stage to one side and the input signal of the previous stage to the other side. As a result, it can be used as a buffer that is of a single input type and has a minimum through current.

本発明の表示装置の駆動回路は、回路に供給する電源電位として、入力信号の振幅電位

と異なる電位を与えることにより、レベルシフタとして機能させることも容易である。以

下にその例を示す。

The driver circuit of the display device of the present invention can easily function as a level shifter by applying a potential different from the amplitude potential of the input signal as a power supply potential supplied to the circuit. An example is shown below.

まず、電源電位として、GND、VDD1、VDD2の3電位を考え、それぞれの大小

関係は、GND<VDD1<VDD2とする。このとき、GND−VDD1間の振幅を有

する信号を入力し、GND−VDD2間の振幅に変換して取り出す場合を例として考える

。

First, three potentials of GND, VDD1, and VDD2 are considered as power supply potentials, and the magnitude relationship of each is GND <VDD1 <VDD2. At this time, a case where a signal having an amplitude between GND and VDD1 is input and converted into an amplitude between GND and VDD2 is taken out as an example.

図4(A)に例を示す。回路の構成は実施形態および実施例1と同様で良い。

入力信号の振幅がGND−VDD1間であり、N型TFT401、403の不純物領域の

一端に接続される電源の電位をVDD2としている。

An example is shown in FIG. The configuration of the circuit may be the same as that of the embodiment and Example 1.

The amplitude of the input signal is between GND and VDD1, and the potential of the power source connected to one end of the impurity region of the N-

回路の動作について説明する。入力信号の波形を図4(B)に示す。GND−VDD1

間の振幅をもった信号が、N型TFT402および404のゲート電極に入力される。入

力信号がHi電位であるとき、N型TFT402、404がONし、ノードαにおける電

位がGND側に引き下げられ、N型TFT403はOFFする。よって出力ノードにおけ

る電位はLo電位となる。

The operation of the circuit will be described. The waveform of the input signal is shown in FIG. GND-VDD1

A signal having an amplitude in between is input to the gate electrodes of the N-

入力信号がLo電位であるとき、N型TFT402、404がOFFし、ノードαにお

ける電位がVDD2側に引き上げられる。したがってN型TFT403がONし、出力ノ

ードの電位が上昇する。一方、ノードαにおいては、その電位が(VDD2−N型TFT

403のしきい値電圧の絶対値)となったところで浮遊状態となる。その後、出力ノード

の電位上昇に伴い、N型TFT403のゲート−ソース間に存在する容量結合405によ

ってノードαの電位はさらに引き上げられ、VDD2よりも高い電位をとる(図4(C)

)。よって、出力ノードの電位はHi電位となり、GND−VDD2間の振幅を持った信

号が出力される(図4(D)実線)。

When the input signal is at the Lo potential, the N-

When the absolute value of the threshold voltage (403) is reached, the floating state is entered. Thereafter, as the potential of the output node rises, the potential of the node α is further raised by the

). Therefore, the potential of the output node becomes the Hi potential, and a signal having an amplitude between GND and VDD2 is output (solid line in FIG. 4D).

本実施例で示した回路がレベルシフタとして容易に扱うことが出来る理由として、高電

位側電源(VDD2)に接続されたTFT401、403のゲート電極には、低電圧振幅

の信号入力がない点が挙げられる。図5(A)に示す2入力型の回路において、高電位側

電源(VDD2)に接続されたTFT501に低電圧振幅の信号を入力しても、ノードβ

の電位はVDD1付近までしか上昇することができない。したがってTFT503もまた

、十分にONすることが出来ず、容量結合を用いてTFT503のゲート電極電位を持ち

上げることが出来ないため、正常動作が望めない。

The reason why the circuit shown in this embodiment can be easily handled as a level shifter is that the gate electrodes of the

Can only rise to near VDD1. Accordingly, the

よって、本実施例にて示したレベルシフタの直後にかかる負荷が大きく、バッファ等の

構成を必要とする場合には、図5(B)のように、1入力型の回路を2段用いて、その後

の入力信号の振幅を全て高電圧振幅とする必要がある。図5(B)においては、低電圧振

幅の信号が入力されるTFTは、点線枠506で囲まれた部分のTFTに限られ、1入力

型の回路を2段重ねることによって、3段目の2入力(TFT507、508のゲート電

極への入力)はいずれも高電圧振幅の信号が入力されるため、正常に動作することが出来

る。

Therefore, when the load applied immediately after the level shifter shown in this embodiment is large and a configuration of a buffer or the like is required, two stages of one-input type circuits are used as shown in FIG. All subsequent input signal amplitudes must be high voltage amplitudes. In FIG. 5B, a TFT to which a signal having a low voltage amplitude is input is limited to a portion surrounded by a

また、振幅変換を行う信号が反転信号を有している場合、互いの出力信号を、次段の反

転入力として用いる構成としても良い。図6に例を示す。入力信号はin、inbであり

、それぞれTFT602、614のゲート電極に入力される。

レベルシフタ1段目650の出力は、2段目のTFT606、617に入力され、660

の出力は、2段目のTFT605、618に入力される。2段目への入力信号は、いずれ

も高電圧振幅の信号であるから、以後は正常にバッファとして機能し、最終段より、出力

信号Out、outbを得る。

Further, in the case where the signal to be subjected to amplitude conversion has an inverted signal, the output signal of each other may be used as the inverted input of the next stage. An example is shown in FIG. Input signals are in and inb, which are input to the gate electrodes of the

The output of the

Are input to the second-

本実施例においては、本発明の表示装置の駆動回路を用いて表示装置を作製した例につ

いて説明する。

In this embodiment, an example in which a display device is manufactured using the display device driving circuit of the present invention will be described.

図7は、表示装置の概略図である。基板700上に、ソース信号線駆動回路701、ゲ

ート信号線駆動回路702および画素部703を一体形成にて作製している。画素部にお

いて、点線枠710で囲まれた部分が1画素である。図の例では、液晶表示装置の画素を

示しており、1個のTFT(以後、画素TFTと表記する)によって液晶素子の一電極に

印加される電荷の制御を行っている。ソース信号線駆動回路701、ゲート信号線駆動回

路702への信号入力は、フレキシブルプリント基板(Flexible Print Circuit:FPC

)704を介して、外部より供給される。

FIG. 7 is a schematic diagram of the display device. A source signal line driver circuit 701, a gate signal

) 704 is supplied from the outside via 704.

本実施例にて示す表示装置は、本発明の表示装置の駆動回路を用いて構成することによ

り、画素部を含む表示装置全体を構成する駆動回路を、画素TFTと同一の極性を有する

一極性のTFT(例えばN型TFT)のみを用いて作製している。これにより、半導体層

にP型を付与するイオンドーピング工程を省略することが可能となり、製造コストの削減

や歩留まり向上等に寄与することが出来る。

The display device shown in this embodiment is configured using the drive circuit of the display device of the present invention, so that the drive circuit constituting the entire display device including the pixel portion has the same polarity as the pixel TFT. This TFT is manufactured using only the TFT (for example, N-type TFT). Thereby, it is possible to omit the ion doping step of imparting P-type to the semiconductor layer, which can contribute to reduction of manufacturing cost, improvement of yield, and the like.

なお、本実施例の表示装置を構成したTFTの極性はN型であるが、P型TFTのみを

用いて駆動回路および画素TFTを構成することも、本発明によってもちろん可能となる

。この場合は、省略されるイオンドーピング工程は、半導体層にN型を付与する工程であ

ることを付記する。また、本発明は液晶表示装置のみならず、絶縁体上に駆動回路を一体

形成して作製する装置ならばいずれの物にも適用が可能である。

Although the polarity of the TFT constituting the display device of this embodiment is N-type, it is of course possible to configure the driving circuit and the pixel TFT using only the P-type TFT according to the present invention. In this case, it is noted that the ion doping step to be omitted is a step of imparting N-type to the semiconductor layer. The present invention can be applied not only to a liquid crystal display device but also to any device that is manufactured by integrally forming a drive circuit on an insulator.

本発明の表示装置の駆動回路は、様々な電子機器に用いられている表示装置の作製に適

用が可能である。このような電子機器には、携帯情報端末(電子手帳、モバイルコンピュ

ータ、携帯電話等)、ビデオカメラ、デジタルカメラ、パーソナルコンピュータ、テレビ

、携帯電話等が挙げられる。それらの一例を図8に示す。

The driver circuit for the display device of the present invention can be applied to manufacture of a display device used in various electronic devices. Examples of such electronic devices include portable information terminals (electronic notebooks, mobile computers, mobile phones, etc.), video cameras, digital cameras, personal computers, televisions, mobile phones, and the like. An example of them is shown in FIG.

図8(A)は液晶ディスプレイ(LCD)であり、筐体3001、支持台3002、表

示部3003等により構成されている。本発明の表示装置の駆動回路は、表示部3003

の作製に適用が可能である。

FIG. 8A illustrates a liquid crystal display (LCD), which includes a housing 3001, a

It can be applied to the production of

図8(B)はビデオカメラであり、本体3011、表示部3012、音声入力部301

3、操作スイッチ3014、バッテリー3015、受像部3016等により構成されてい

る。本発明の表示装置の駆動回路は、表示部3012の作製に適用が可能である。

FIG. 8B illustrates a video camera, which includes a main body 3011, a display portion 3012, and an

3, an

図8(C)はノート型のパーソナルコンピュータであり、本体3021、筐体3022

、表示部3023、キーボード3024等により構成されている。本発明の表示装置の駆

動回路は、表示部3023の作製に適用が可能である。

FIG. 8C illustrates a laptop personal computer, which includes a main body 3021 and a

, A

図8(D)は携帯情報端末であり、本体3031、スタイラス3032、表示部303

3、操作ボタン3034、外部インターフェイス3035等により構成されている。本発

明の表示装置の駆動回路は、表示部3033の作製に適用が可能である。

FIG. 8D illustrates a portable information terminal, which includes a

3, an operation button 3034, an

図8(E)は音響再生装置、具体的には車載用のオーディオ装置であり、本体3041

、表示部3042、操作スイッチ3043、3044等により構成されている。本発明の

表示装置の駆動回路は表示部3042の作製に適用が可能である。また、本実施例では車

載用オーディオ装置を例に挙げたが、携帯型もしくは家庭用のオーディオ装置に用いても

良い。

FIG. 8E illustrates a sound reproducing device, specifically an in-vehicle audio device.

, A

図8(F)はデジタルカメラであり、本体3051、表示部(A)3052、接眼部3

053、操作スイッチ3054、表示部(B)3055、バッテリー3056等により構

成されている。本発明の表示装置の駆動回路は、表示部(A)

3052および表示部(B)3055の作製に適用が可能である。

FIG. 8F illustrates a digital camera, which includes a main body 3051, a display portion (A) 3052, and an

053, an

The present invention can be applied to manufacture of 3052 and the display portion (B) 3055.

図8(G)は携帯電話であり、本体3061、音声出力部3062、音声入力部306

3、表示部3064、操作スイッチ3065、アンテナ3066等により構成されている

。本発明の表示装置の駆動回路は、表示部3064の作製に適用が可能である。

FIG. 8G illustrates a mobile phone, which includes a

3, a

なお、本実施例に示した例はごく一例であり、これらの用途に限定しないことを付記す

る。

It should be noted that the examples shown in this embodiment are just examples, and the present invention is not limited to these applications.

Claims (2)

前記駆動回路は、第1乃至第8のトランジスタを有し、The drive circuit includes first to eighth transistors,

前記第1乃至前記第8のトランジスタの導電型は、同じであり、The first to eighth transistors have the same conductivity type,

前記第2のトランジスタのゲートは、第1の配線と電気的に接続され、A gate of the second transistor is electrically connected to the first wiring;

前記第1の配線は、第1の信号を供給する機能を有し、The first wiring has a function of supplying a first signal;

前記第2のトランジスタのゲートは、前記第4のトランジスタのゲートと電気的に接続され、A gate of the second transistor is electrically connected to a gate of the fourth transistor;

前記第2のトランジスタのゲートは、前記第5のトランジスタのゲートと電気的に接続され、A gate of the second transistor is electrically connected to a gate of the fifth transistor;

前記第6のトランジスタのゲートは、前記第8のトランジスタのゲートと電気的に接続され、A gate of the sixth transistor is electrically connected to a gate of the eighth transistor;

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、One of a source and a drain of the first transistor is electrically connected to a gate of the first transistor;

前記第1のトランジスタのソース又はドレインの他方は、前記第3のトランジスタのゲートと電気的に接続され、The other of the source and the drain of the first transistor is electrically connected to the gate of the third transistor;

前記第1のトランジスタは、前記第3のトランジスタをオンにする電位の前記第3のトランジスタのゲートへの供給を制御する機能を有し、The first transistor has a function of controlling supply of a potential for turning on the third transistor to the gate of the third transistor;

前記第2のトランジスタは、前記第3のトランジスタをオフにする電位の前記第3のトランジスタのゲートへの供給を制御する機能を有し、The second transistor has a function of controlling supply of a potential for turning off the third transistor to the gate of the third transistor;

前記第3のトランジスタは、前記第6のトランジスタをオンにする電位の前記第6のトランジスタのゲートへの供給を制御する機能を有し、The third transistor has a function of controlling supply of a potential for turning on the sixth transistor to the gate of the sixth transistor;

前記第4のトランジスタは、前記第6のトランジスタをオフにする電位の前記第6のトランジスタのゲートへの供給を制御する機能を有し、The fourth transistor has a function of controlling supply of a potential for turning off the sixth transistor to the gate of the sixth transistor;

前記第5のトランジスタは、前記第7のトランジスタをオンにする電位の前記第7のトランジスタのゲートへの供給を制御する機能を有し、The fifth transistor has a function of controlling supply of a potential for turning on the seventh transistor to a gate of the seventh transistor;

前記第6のトランジスタは、前記第7のトランジスタをオフにする電位の前記第7のトランジスタのゲートへの供給を制御する機能を有し、The sixth transistor has a function of controlling supply of a potential for turning off the seventh transistor to the gate of the seventh transistor;

前記第7のトランジスタは、第1の電位の前記第8のトランジスタのソース又はドレインの一方への供給を制御する機能を有し、The seventh transistor has a function of controlling supply of a first potential to one of a source and a drain of the eighth transistor;

前記第8のトランジスタは、第2の電位の前記第7のトランジスタのソース又はドレインの一方への供給を制御する機能を有し、The eighth transistor has a function of controlling supply of a second potential to one of a source and a drain of the seventh transistor;

前記第7のトランジスタのソース又はドレインの一方からの出力信号に応じた電位が、前記画素に入力されることを特徴とする表示装置。The display device, wherein a potential corresponding to an output signal from one of a source and a drain of the seventh transistor is input to the pixel.

前記駆動回路は、第1乃至第8のトランジスタを有し、The drive circuit includes first to eighth transistors,

前記画素は、第9のトランジスタを有し、The pixel includes a ninth transistor;

前記第1乃至前記第9のトランジスタの導電型は、同じであり、The conductivity types of the first to ninth transistors are the same,

前記第2のトランジスタのゲートは、第1の配線と電気的に接続され、A gate of the second transistor is electrically connected to the first wiring;

前記第1の配線は、第1の信号を供給する機能を有し、The first wiring has a function of supplying a first signal;

前記第2のトランジスタのゲートは、前記第4のトランジスタのゲートと電気的に接続され、A gate of the second transistor is electrically connected to a gate of the fourth transistor;

前記第2のトランジスタのゲートは、前記第5のトランジスタのゲートと電気的に接続され、A gate of the second transistor is electrically connected to a gate of the fifth transistor;

前記第6のトランジスタのゲートは、前記第8のトランジスタのゲートと電気的に接続され、A gate of the sixth transistor is electrically connected to a gate of the eighth transistor;

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、One of a source and a drain of the first transistor is electrically connected to a gate of the first transistor;

前記第1のトランジスタのソース又はドレインの他方は、前記第3のトランジスタのゲートと電気的に接続され、The other of the source and the drain of the first transistor is electrically connected to the gate of the third transistor;

前記第1のトランジスタは、前記第3のトランジスタをオンにする電位の前記第3のトランジスタのゲートへの供給を制御する機能を有し、The first transistor has a function of controlling supply of a potential for turning on the third transistor to the gate of the third transistor;

前記第2のトランジスタは、前記第3のトランジスタをオフにする電位の前記第3のトランジスタのゲートへの供給を制御する機能を有し、The second transistor has a function of controlling supply of a potential for turning off the third transistor to the gate of the third transistor;

前記第3のトランジスタは、前記第6のトランジスタをオンにする電位の前記第6のトランジスタのゲートへの供給を制御する機能を有し、The third transistor has a function of controlling supply of a potential for turning on the sixth transistor to the gate of the sixth transistor;

前記第4のトランジスタは、前記第6のトランジスタをオフにする電位の前記第6のトランジスタのゲートへの供給を制御する機能を有し、The fourth transistor has a function of controlling supply of a potential for turning off the sixth transistor to the gate of the sixth transistor;

前記第5のトランジスタは、前記第7のトランジスタをオンにする電位の前記第7のトランジスタのゲートへの供給を制御する機能を有し、The fifth transistor has a function of controlling supply of a potential for turning on the seventh transistor to a gate of the seventh transistor;

前記第6のトランジスタは、前記第7のトランジスタをオフにする電位の前記第7のトランジスタのゲートへの供給を制御する機能を有し、The sixth transistor has a function of controlling supply of a potential for turning off the seventh transistor to the gate of the seventh transistor;

前記第7のトランジスタは、第1の電位の前記第8のトランジスタのソース又はドレインの一方への供給を制御する機能を有し、The seventh transistor has a function of controlling supply of a first potential to one of a source and a drain of the eighth transistor;

前記第8のトランジスタは、第2の電位の前記第7のトランジスタのソース又はドレインの一方への供給を制御する機能を有し、The eighth transistor has a function of controlling supply of a second potential to one of a source and a drain of the seventh transistor;

前記第7のトランジスタのソース又はドレインの一方からの出力信号に応じた電位が、前記第9のトランジスタのゲートに入力されることを特徴とする表示装置。A display device, wherein a potential corresponding to an output signal from one of a source and a drain of the seventh transistor is input to a gate of the ninth transistor.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016111710A JP6205014B2 (en) | 2016-06-03 | 2016-06-03 | Display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016111710A JP6205014B2 (en) | 2016-06-03 | 2016-06-03 | Display device |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015100679A Division JP6167133B2 (en) | 2015-05-18 | 2015-05-18 | Display device |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017084241A Division JP2017173833A (en) | 2017-04-21 | 2017-04-21 | Semiconductor device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016186644A JP2016186644A (en) | 2016-10-27 |

| JP6205014B2 true JP6205014B2 (en) | 2017-09-27 |

Family

ID=57202613

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016111710A Expired - Lifetime JP6205014B2 (en) | 2016-06-03 | 2016-06-03 | Display device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6205014B2 (en) |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3506851A (en) * | 1966-12-14 | 1970-04-14 | North American Rockwell | Field effect transistor driver using capacitor feedback |

| JPS55156427A (en) * | 1979-05-23 | 1980-12-05 | Sharp Corp | Bootstrap buffer circuit |

| JPH05224629A (en) * | 1992-02-18 | 1993-09-03 | Sharp Corp | Driving circuit for active matrix display device |

| JP2999328B2 (en) * | 1992-04-28 | 2000-01-17 | シャープ株式会社 | Active matrix substrate |

| JP4785271B2 (en) * | 2001-04-27 | 2011-10-05 | 株式会社半導体エネルギー研究所 | Liquid crystal display device, electronic equipment |

| JP4860765B2 (en) * | 2010-08-30 | 2012-01-25 | 株式会社半導体エネルギー研究所 | Semiconductor device and electronic equipment |

| JP5493023B2 (en) * | 2013-03-21 | 2014-05-14 | 株式会社半導体エネルギー研究所 | Display device |

| JP6167133B2 (en) * | 2015-05-18 | 2017-07-19 | 株式会社半導体エネルギー研究所 | Display device |

-

2016

- 2016-06-03 JP JP2016111710A patent/JP6205014B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016186644A (en) | 2016-10-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4785271B2 (en) | Liquid crystal display device, electronic equipment | |

| JP4439761B2 (en) | Liquid crystal display device, electronic equipment | |

| JP4860765B2 (en) | Semiconductor device and electronic equipment | |

| JP5493023B2 (en) | Display device | |

| JP5719956B2 (en) | Display device | |

| JP6167133B2 (en) | Display device | |

| JP5847969B2 (en) | Display device | |

| JP5690870B2 (en) | Display device | |

| JP2017173833A (en) | Semiconductor device | |

| JP6205014B2 (en) | Display device | |

| JP6628837B2 (en) | Electronics | |

| JP5025714B2 (en) | Display device, semiconductor device, display module, and electronic device | |

| JP2012078839A (en) | Driving circuit for display device | |

| JP5504367B2 (en) | Semiconductor device | |

| JP6584705B2 (en) | Liquid crystal display | |

| JP6584701B2 (en) | Semiconductor device | |

| JP6691185B2 (en) | Semiconductor device | |

| JP2019071671A (en) | Semiconductor device | |

| JP6434176B2 (en) | Semiconductor device | |

| JP6159043B1 (en) | Semiconductor device and display device | |

| JP6106227B2 (en) | Semiconductor device and display device | |

| JP2012042961A (en) | Semiconductor device and electronic appliance | |

| JP5799150B2 (en) | Semiconductor device | |

| JP5648113B2 (en) | Semiconductor device | |

| JP5393836B2 (en) | Display device, semiconductor device, display module, and electronic device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170228 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170421 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170808 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170901 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6205014 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |