JP6154976B1 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6154976B1 JP6154976B1 JP2017045566A JP2017045566A JP6154976B1 JP 6154976 B1 JP6154976 B1 JP 6154976B1 JP 2017045566 A JP2017045566 A JP 2017045566A JP 2017045566 A JP2017045566 A JP 2017045566A JP 6154976 B1 JP6154976 B1 JP 6154976B1

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- impurity element

- contact hole

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

Description

置およびその作製方法に関する。特に、本発明は、液晶表示装置に代表される電気光学装

置およびその様な電気光学装置を部品として搭載した半導体装置およびその作製方法に関

する。なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しう

る装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

FTを構成し、このTFTで形成した大面積集積回路を有する半導体装置の開発が進んで

いる。その代表例として、アクティブマトリクス型の液晶表示装置や発光装置が知られて

いる。特に、結晶質珪素膜を活性領域にしたTFTは電界効果移動度が高いことから、い

ろいろな機能回路を形成することも可能である。

行う画素回路や、CMOS回路を基本としたシフトレジスタ回路、レベルシフタ回路、バ

ッファ回路、サンプリング回路などの画素回路を制御するための駆動回路が一枚の基板上

に形成される。

絶縁膜と、各種金属材料等からなる配線とを有している。前記配線には、ソース配線やゲ

ート配線(ゲート電極を含む)などがある。これらの膜の厚さは数〜数百nm程度である

ため、薄膜と言うことができる。

より形成される。しかしながら、前記薄膜には内部応力があることが知られている。なお

、内部応力には真性応力と、前記薄膜と基板との熱膨張係数の差に起因する熱応力とが含

まれている。

することができるが、真性応力の発生メカニズムは必ずしも明確にはされておらず、むし

ろ膜の成長過程やその後の熱処理などによる相変化や組成変化が複雑に絡みあって発生し

ているものと考えられている。

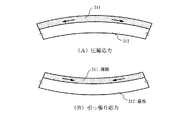

薄膜311が伸張しようとするときには、基板312は押し縮められ薄膜311を外側に

して形成するので、これを圧縮応力と呼んでいる。一方、図5(B)に示すように、基板

312に対して薄膜311が収縮しようとするときには、基板312はそれを妨げる方向

に引っ張るため薄膜を内側にして変形し、これを引っ張り応力と呼んでいる。一般に、引

っ張り応力の値は+で示し、圧縮応力の値は―で示すことが多い。

.13μmCMOSトランジスタ性能に対するエッチストップ窒化膜の応力の影響;応用

物理学会分科会シリコンテクノロジーNo.25 ULSIデバイス関連特集号(200

1)pp36―39」に記載されている。これによると、NMOSトランジスタはチャネ

ル形成領域が引っ張り応力を受けると移動度が向上し、PMOSトランジスタは圧縮応力

を受けると移動度が向上することが報告されている。

応力を有し、該内部応力が強いとピーリングが発生する場合があった。

また、配線と同一材料で形成されるゲート電極は、絶縁膜を介して半導体膜上に形成され

ている。前記ゲート電極の内部応力は半導体膜にまで作用し、前記絶縁膜と前記半導体膜

との界面や、前記半導体膜に歪みを与えることによって、しきい値電圧や電界効果移動度

に代表される電気的特性に悪影響を及ぼす場合がある。

リクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、半導体

装置の動作特性および信頼性を向上させ、歩留まりの向上を実現することを目的としてい

る。

を行うことで、前記配線を所望の内部応力に制御することを可能とする。特に本発明を、

ゲート電極に適用することは極めて有効である。また、所望の領域のみに不純物元素を導

入したり、熱処理を行って所望の内部応力に制御することも可能とする。

力を引っ張り応力とし、pチャネル型TFTにおけるチャネル形成領域が受ける応力を圧

縮応力とすることも可能である。また、nチャネル型TFTにおけるチャネル形成領域の

方が、pチャネル型TFTにおけるチャネル形成領域よりも相対的に引っ張り応力を強く

することも、pチャネル型TFTにおけるチャネル形成領域の方が、nチャネル型TFT

におけるチャネル形成領域よりも相対的に圧縮応力を強くすることも可能である。このよ

うにすることで、TFTの電気的特性を良好なものとし、さらに半導体装置の動作特性も

大幅に向上することが可能となる。

ーピング法などにより行えばよい。このような不純物元素の導入の方法において、薄膜へ

打ち込まれるイオンのエネルギーは、薄膜を形成する元素の結合エネルギーと比較して非

常に大きい。そのため、前記薄膜へ打ち込まれるイオンは、前記半導体膜を形成する原子

を格子点から弾き飛ばして格子位置に存在するようになったり、打ち込まれるイオンや格

子点から弾き飛ばされた原子は格子間位置に存在するようになる。このようにして薄膜が

伸張するので、薄膜が圧縮応力を有している場合、前記圧縮応力は増大し、薄膜が引っ張

り応力を有している場合、前記引っ張り応力は緩和される。

列の規則性は向上する。そのため、薄膜が収縮するので、薄膜が引っ張り応力を有してい

る場合、前記引っ張り応力は増大し、薄膜が圧縮応力を有している場合、前記圧縮応力は

緩和される。

膜中に加速されたイオンが打ち込まれるので、前記イオンは結晶格子の隙間に沿って衝突

を起すことなく深いところまで進入することが可能となる。(チャネリング)そのため、

内部応力を制御するための不純物元素の導入において、ドーズ量は少なくて済み、また、

低加速度の電圧で行うことが可能となる。

多くの原子が導入されているので、格子間位置に存在していた原子が格子位置に戻る以上

に原子が存在することになる。そのため、不純物元素の導入を行わない場合よりも薄膜の

収縮が小さいので、引っ張り応力の増加量も小さくなる。つまり、後工程で熱処理を行う

ことが分かっている場合は、予め不純物元素を導入しておけば、内部応力の変化量を小さ

くすることが可能となる。

ことで、所望の内部応力に制御することが可能となる。もちろん、不純物の導入や熱処理

は1回に限らず、複数回行ってもよい。本発明はこれらの特性を配線に適用し、該配線の

応力を制御することで、半導体装置の動作特性および信頼性を向上させるものである。特

に、TFTのゲート電極における内部応力が制御されることで、半導体膜が受ける応力を

制御することが可能となる。そのため、しきい値電圧や電界効果移動度に代表される電気

的特性を向上させることが可能となる。また、個々のゲート電極の応力を制御することも

可能であることから、電気的特性のばらつきを抑えることも可能となる。

における内部応力を±1GPa以下とすることを特徴としている。

行って、前記導電膜における内部応力を±1GPa以下とすることを特徴としている。

導入して、前記導電膜における内部応力を±1GPa以下とすることを特徴としている。

オン注入法、イオンシャワードーピング法などにより行うことができる。

不純物元素、p型を付与する不純物元素、および希ガス元素から選ばれた一種または複数

種の元素であることが望ましい。n型を付与する不純物元素やp型を付与する不純物元素

はソース領域やドレイン領域を形成する上で欠かすことのできない不純物元素である。そ

のため、新たに他の不純物元素を用意する必要がなく経済的である。特に、ゲート電極に

不純物元素を導入する場合、ソース領域およびドレイン領域に前記不純物元素を導入する

工程と同時に導入することが可能であるため、工程数を増やすことなく導入できるため好

ましい。また、希ガス元素は不活性元素であるため、TFTの電気的特性に影響を及ぼさ

ないため好ましい。

、前記圧縮応力は増大し、薄膜における内部応力が引っ張り応力である場合は、前記引っ

張り応力が緩和したのち、圧縮応力を有するようになることもある。つまり、不純物元素

の導入量によって、薄膜における内部応力が圧縮応力となる場合もあれば、引っ張り応力

となる場合もある。

なることが望ましい。導電膜の内部応力が強いとピーリングを発生することが知られてお

り、一般にピーリングの発生を抑制することのできる目安は±1GPa以下となっている

。もちろん、ピーリングの発生は、導電膜が形成される条件等に大きく影響する。

あっても良い。

ネスアニール炉を用いた熱アニール法等を適用することができる。

する。熱処理の時間が長いほど、また熱処理の温度が高いほど、薄膜における内部応力が

引っ張り応力である場合は、前記引っ張り応力は増大し、薄膜における内部応力が圧縮応

力である場合は、前記圧縮応力が緩和したのち、引っ張り応力を有するようになることも

ある。つまり、熱処理の条件によって、薄膜における内部応力が圧縮応力となる場合もあ

れば、引っ張り応力となる場合もある。

および導電膜を有し、前記半導体膜は引っ張り応力を受けており、前記導電膜は不純物元

素が導入されていることを特徴としている。

および導電膜を有し、前記半導体膜は圧縮応力を受けており、前記導電膜は不純物元素が

導入されていることを特徴としている。

ネル型TFTは、第1の半導体膜と、前記第1の半導体膜上に形成された第1の導電膜と

を有し、前記pチャネル型TFTは、第2の半導体膜と、前記第2の半導体膜上に形成さ

れた第2の導電膜とを有し、前記第1の半導体膜は引っ張り応力を受けており、前記第2

の半導体膜は圧縮応力を受けており、前記第1の導電膜および前記第2の導電膜は不純物

元素が導入されていることを特徴としている。

、p型を付与する不純物元素、および希ガス元素から選ばれた一種または複数種の元素で

あることが望ましい。n型を付与する不純物元素やp型を付与する不純物元素はソース領

域やドレイン領域を形成する上で欠かすことのできない不純物元素である。そのため、新

たに他の不純物元素を用意する必要がなく経済的である。特に、ゲート電極に不純物元素

を導入する場合、ソース領域およびドレイン領域に前記不純物元素を導入する工程と同時

に導入することが可能であるため、工程数を増やすことなく導入できるため好ましい。ま

た、希ガス元素は不活性元素であるため、TFTの電気的特性に影響を及ぼさないため好

ましい。

装置を形成することを特徴としている。

る。

(a)従来の作製プロセスに適合した、簡単な方法である。

(b)所望の内部応力を有する配線の形成を実現できる。そのため、他の膜における応力

をも低減することができる。また、配線のパターニング処理も良好に行うことができる。

(c)以上の利点を満たした上で、アクティブマトリクス型の液晶表示装置に代表される

半導体装置において、半導体装置の動作特性および信頼性を向上させ、歩留まりの向上を

実現することができる。

本発明の実施形態について、図1を用いて説明する。本実施形態では、本発明をTFT

のゲート電極に適用した場合について説明する。

基板や単結晶シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したも

のを用いても良い。また、処理温度に耐えうる耐熱性を有するプラスチック基板を用いて

もよい。

絶縁膜から成る下地絶縁膜11を形成する。ここでは下地膜11として単層構造を用いた

例を示したが、前記絶縁膜を2層以上積層させた構造としても良い。なお、下地絶縁膜1

1を形成しなくてもよい。

有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)

により成膜した後、公知の結晶化処理(レーザ結晶化法、熱結晶化法、またはニッケルな

どの触媒を用いた熱結晶化法等)を行って結晶質半導体膜を形成する。この半導体膜12

の厚さは25〜200nm(好ましくは30〜100nm)で形成する。半導体膜の材料

に限定はないが、好ましくは珪素または珪素ゲルマニウム(SiGe)合金などで形成す

ると良い。

パッタ法等を用い、厚さを40〜150nmとして珪素を含む絶縁膜の単層または積層構

造で形成する。なお、この絶縁膜13はゲート絶縁膜となる。

nmの導電膜14を形成する。ここでは、導電膜14として単層構造を用いた例を示した

が、前記導電膜を2層以上積層させた構造としても良い。

い場合がある。そのため、不純物元素の導入を行って、前記導電膜14における内部応力

を緩和させ、所望の内部応力にする。不純物元素の導入は、プラズマドーピング法、イオ

ン注入法、またはイオンシャワードーピング法などにより行えば良い。また、導入する不

純物元素は、n型を付与する不純物元素、p型を付与する不純物元素、および希ガス元素

から選ばれた一種または複数種の元素を用い、加速電圧30〜120keV、ドーズ量を

1×1012〜9×1016/cm2とし、ピークの濃度が1×1017〜1×1022/cm3と

なるように行う。

(図1(C))もちろん、最適な不純物元素の導入条件は、導電膜の状態や所望とする内

部応力によっても異なる。また、レジストからなるマスクを用いて、所望の領域のみに不

純物元素を導入すれば、前記所望の領域のみの内部応力を変化させることも可能である。

に及ぼす応力が低減できる。そして、このような導電膜を用いてTFTを作製すると、そ

の電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

本発明の実施形態について、図1を用いて説明する。本実施形態では、不純物元素を導入

した後、熱処理を行うことにより内部応力を制御する場合について説明する。

大し、圧縮応力であるなら緩和する。熱処理は、ファーネスアニール炉を用いた熱アニー

ル法、レーザアニール法、RTA法等、公知の方法により行えばよい。例えば、ファーネ

スアニール炉を用いた熱アニール法を行うのであれば、温度500〜1000℃程度の窒

素雰囲気中に3分〜12時間程度曝せばよい。もちろん、最適な熱処理の条件は、導電膜

の状態や所望とする内部応力によっても異なる。また、長時間の熱処理は、TFTの作製

工程における半導体膜の結晶化や不純物元素の活性化と同時に行えば、新たに工程を増加

させることなく行うことができ、効率が良い。

みの内部応力を変化させることも可能である。

に及ぼす応力が低減できる。そして、このような導電膜を用いてTFTを作製すると、そ

の電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

本発明の実施形態について、図2を用いて説明する。本実施形態では、不純物元素を導

入した後、熱処理を行うことにより内部応力を制御する場合について説明する。

nmの導電膜17を形成する。ここでは、導電膜17として単層構造を用いた例を示した

が、前記導電膜を2層以上積層させた構造としても良い。

がある。そのため、熱処理を行って、前記導電膜17における内部応力を変化させる。熱

処理は、ファーネスアニール炉を用いる熱アニール法、RTA法、レーザアニール法等、

公知の方法を用いれば良い。(図2(B))

大し、圧縮応力であるなら緩和する。(図2(C))熱処理は、ファーネスアニール炉を

用いた熱アニール法、レーザアニール法、RTA法等、公知の方法により行えばよい。例

えば、ファーネスアニール炉を用いた熱アニール法を行うのであれば、温度500〜10

00℃程度の窒素雰囲気中に3分〜12時間程度曝せばよい。もちろん、最適な熱処理の

条件は、導電膜の状態や所望とする内部応力によっても異なる。

ラズマドーピング法、イオン注入法、またはイオンシャワードーピング法などにより行え

ば良い。また、導入する不純物元素は、n型を付与する不純物元素、p型を付与する不純

物元素、および希ガス元素から選ばれた一種または複数種の元素を用い、加速電圧30〜

120keV、ドーズ量を1×1012〜9×1016/cm2とし、ピークの濃度が1×1

017〜1×1022/cm3となるように行う。(図2(D))また、熱処理を行った後に

不純物元素を導入することで、チャネリングにより、少ないドーズ量や低加速度の電圧で

内部応力を変化させることができる。

に及ぼす応力が低減できる。そして、このような導電膜を用いてTFTを作製すると、そ

の電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

ととする。

んである。

にW(タングステン)を、不純物元素としてArを用いたが、本発明は特にこれらに限定

されるものではない。

、CVD法により膜厚70nmの窒化酸化珪素膜(組成比Si=32.8%、O=63.

7%、H=3.5%)を形成した後、950℃で30分の熱処理を行った。そして、窒化

酸化珪素膜を除去した。W上に窒化酸化珪素膜を形成したのは、熱処理によってWがピー

リングを起すことを防止するためである。不純物元素の導入はイオンシャワードーピング

法により行い、その条件は表1に示す。また、不純物元素の導入は、熱処理前、熱処理後

、窒化酸化珪素膜を除去後の3つの条件において行った。その結果を図3に示す。ここで

は、内部応力の変化が引っ張り応力の増加であるときは+とし、圧縮応力の増加であると

きは―としている。

ていることが分かる。熱処理後に不純物元素を導入すると、熱処理によって結晶性が向上

するため、不純物元素が膜中深くまで導入しやすくなり、内部応力は圧縮応力の方向へ大

きく変化する。しかしながら、窒化酸化珪素膜を介してArを導入すると、Wにおける実

質的なArの導入量が少ないため、圧縮応力の方向への変化も小さい。

物元素を導入せず、熱処理のみを行った場合についても内部応力の変化を調べた。図4よ

り、加速電圧30keVでは、不純物元素を導入しない場合よりも引っ張り応力の増加が

大きい。これは、不純物元素の導入によって圧縮応力が増大した分、熱処理による引っ張

り応力も増大したと考えられる。また、80keVでは引っ張り応力の方向への変化が小

さいことから、加速電圧が高いと、膜中に十分深くまで不純物元素が導入されるため、熱

処理による影響を受けにくいと考えられる。

内部応力は引っ張り応力が増加することが確認できた。つまり、不純物元素の導入、もし

くは不純物元素の導入および熱処理の両方を行うことにより、内部応力を制御することが

可能となり、所望の内部応力を有する導電膜を得ることができる。

明する。

基板や単結晶シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したも

のを用いてもよい。また、処理温度に耐えうる耐熱性を有するプラスチック基板を用いて

もよい。

絶縁膜から成る下地絶縁膜11を形成する。ここでは下地絶縁膜11として単層構造を用

いる例を示しているが、前記絶縁膜の2層以上積層させた構造を用いても良い。なお、下

地絶縁膜を形成しなくてもよい。本実施例では、膜厚150nmの酸化窒化珪素膜11(

組成比Si=32%、O=27%、N=24%、H=17%)を形成する。

21を得る。ここで、半導体層20はnチャネル型TFTを形成するものとし、半導体層

21はpチャネル型TFTを形成するものとする。半導体膜は、非晶質構造を有する半導

体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により成膜

した後、公知の結晶化処理(レーザ結晶化法、熱結晶化法、またはニッケルなどの触媒を

用いた熱結晶化法等)を行って結晶質半導体膜を形成する。この半導体膜12の厚さは2

5〜200nm(好ましくは30〜100nm)で形成する。半導体膜の材料に限定はな

いが、好ましくは珪素または珪素ゲルマニウム(SiGe)合金などで形成すると良い。

本実施例では、レーザ光を照射して結晶構造を有する半導体膜を形成し、パターニングを

行って半導体層20、21を形成する。

たはスパッタ法を用い、厚さを40〜150nmとして珪素を含む絶縁膜の単層または積

層構造で形成する。なお、この絶縁膜13はゲート絶縁膜となる。本実施例では、プラズ

マCVD法により110nmの厚さで酸化窒化珪素膜(組成比Si=32%、O=59%

、N=7%、H=2%)で形成する。

nmの導電膜23を形成する。ここでは、導電膜23として単層構造を用いる例を示した

が、前記導電膜23を2層以上積層させた構造としても良い。

また、導電膜としてはTa、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素

、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、

リン等の不純物元素を導入した多結晶珪素膜に代表される半導体膜を用いてもよい。また

、AgPdCu合金を用いてもよい。本実施例では、スパッタ法により、膜厚400nm

のTa膜を形成する。また、スパッタ法で形成される膜は圧縮応力を有することが多い。

ッチング処理を行って、第1の導電膜24および第2の導電膜25を形成する。(図6(

B))

純物元素の導入は、プラズマドーピング法、イオン注入法、イオンシャワードーピング法

などにより行えばよい。本実施例ではn型を付与する不純物元素として、Asを用いる。

また、第1の不純物元素の導入では、第2の不純物元素の導入で導入される不純物元素の

量より、第1の不純物元素の導入での導入量を多くしておく。第1の不純物元素の導入を

行うことで、nチャネル型TFTとして機能するための不純物領域27が形成されるが、

第1の導電膜24および第2の導電膜25にもAsが導入され、圧縮応力15は増大する

。

のとき、nチャネル型TFTを形成する半導体層20はレジストから成るマスク26bに

よって覆われているため、不純物元素は導入されない。本実施例ではp型を付与する不純

物元素として、Bを用いる。第2の不純物元素の導入を行うことで、pチャネル型TFT

として機能するための不純物領域28が形成されるが、第2の導電膜25にもBが導入さ

れ、前記第2の導電膜25の圧縮応力15はさらに増大する。

導電膜24よりも不純物元素が多く導入されている。

る。また、前記熱処理により、第1の導電膜24および第2の導電膜25における内部応

力も変化する。しかしながら、前記第1の導電膜24および前記第2の導電膜25に導入

された不純物元素の量が異なるため、熱処理後の内部応力も異なる。第1の導電膜24は

不純物元素の導入量が少ないため、熱処理によって、引っ張り応力の増加の方向16へ大

きく変化し、前記第1の導電膜24における内部応力は引っ張り応力となる。そのため、

nチャネル型TFTを形成する半導体膜が受ける応力は引っ張り応力となる。また、第2

の導電膜25は不純物元素の導入量が多いため、熱処理によって、内部応力はあまり変化

せず、前記第2の導電膜25における内部応力は圧縮応力となる。そのため、nチャネル

型TFTを形成する半導体膜が受ける応力は圧縮応力となる。

膜が受ける応力を引っ張り応力とし、pチャネル型TFTを形成する半導体膜が受ける応

力を圧縮応力とすることができる。そして、このような半導体膜を用いてTFTを作製す

ると、その電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

。

覆って絶縁膜を形成し、前記半導体層上に前記絶縁膜を介して導電層を形成した後、該導

電層をマスクとして前記半導体膜に不純物元素を導入する。また、実施例2で示す方法に

従ってもよい。

実施例では、層間絶縁膜29を単層構造としているが、2層以上の積層構造としても良い

。

り応力が強い場合がある。そのため、不純物元素を導入して、前記導電膜の内部応力を圧

縮応力の増加の方向へ変化させる。このような方法で内部応力を制御し、±1GPa以下

の内部応力を有する導電膜を形成することができ、パターニングを行って配線31〜33

を形成するときに、配線パターンがずれることを防ぐ。

り、層間絶縁膜や半導体膜に及ぼす応力を低減することが可能となる。

そして、このような導電層を用いてTFTを作製すると、その電気的特性は良好なものと

なり、半導体装置の動作特性も大幅に向上し得る。

について、図8を用いて説明する。

や単結晶シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを

用いてもよい。また、処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよ

い。

00nmの導電膜20を形成した後、フォトリソグラフィ法によりパターニング処理を行

って形成する。ここでは、導電膜35として単層構造を用いる例を示したが、前記導電膜

を2層以上積層させた構造としても良い。また、導電膜としてはTa、W、Ti、Mo、

Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分とする合金材料若し

くは化合物材料で形成してもよい。

また、リン等の不純物元素を導入した多結晶珪素膜に代表される半導体膜を用いてもよい

。また、AgPdCu合金を用いてもよい。本実施例では、スパッタ法により、膜厚40

0nmのAl−Ti膜を形成する。

へ変化させる。これは後工程における熱処理によって、導電膜における内部応力が引っ張

り応力の増加の方向へ変化するので、前記内部応力を緩和させるために予め行っておく処

理である。

はスパッタ法を用い、厚さを40〜150nmとして珪素を含む絶縁膜の単層または積層

構造で形成する。なお、この絶縁膜36はゲート絶縁膜となる。本実施例では、プラズマ

CVD法により110nmの厚さで酸化窒化珪素膜(組成比Si=32%、O=59%、

N=7%、H=2%)で形成する。

る半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)によ

り成膜した後、公知の結晶化処理(レーザ結晶化法、熱結晶化法、またはニッケルなどの

触媒を用いた熱結晶化法等)を行って結晶質半導体膜を形成する。この半導体膜37の厚

さは25〜200nm(好ましくは30〜100nm)で形成する。半導体膜の材料に限

定はないが、好ましくは珪素または珪素ゲルマニウム(SiGe)合金などで形成すると

良い。本実施例では、プラズマCVD法を用い、55nmの非晶質珪素膜を成膜した後、

ニッケルを含む溶液を非晶質珪素膜上に保持させる。この非晶質珪素膜に脱水素化(50

0℃、1時間)を行った後、熱結晶化(550℃、4時間)を行う。熱処理によって半導

体膜37は結晶構造を有する半導体膜となる。また、予め不純物元素が導入してあるため

、導電膜35における内部応力の変化量は小さくてすむ。

に及ぼす応力が低減できる。そして、このような導電膜を用いてTFTを作製すると、そ

の電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

FET)に適用してCMOS回路を構成した場合の例について図21〜図23を用いて説

明する。

N型ウェル403を形成する。単結晶シリコン基板はP型であってもN型であっても良い

。この様な構成はいわゆるツインタブ構造であり、ウェル濃度は1×1018/cm3以下

(代表的には1×1016〜5×1017/cm3)で形成される。

した後、熱酸化工程によってシリコン表面に30nm厚の酸化膜(後のゲート絶縁膜)4

05を形成する。(図21(A))

はゲート電極を構成する材料として導電性を有するシリコン膜を用いるが、他にもTa、

W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分と

する合金材料若しくは化合物材料を用いることができる。

型MOSFETとなる領域(図面向かって右側)をレジストマスク408で覆い、単結晶

シリコン基板401に対してn型を付与する不純物元素を導入する。(図21(B))不

純物元素の導入の方法は、レーザドーピング法、プラズマドーピング法、イオン注入法お

よびイオンシャワードーピング法のいずれかの方法を用い、濃度が5×1018〜 1×10

19/cm3となる様に導入する。本実施例では、n型を付与する不純物元素として、As

を用いる。こうして形成される不純物領域410、411の一部(チャネル形成領域と接

する側の端部)は後にnチャネル型MOSFETのLDD領域として機能する。

そして、単結晶シリコン基板401に対してp型を付与する不純物元素を導入する。(図

21(C))本実施例では、n型を付与する不純物元素として、B(ボロン)を用いる。

このようにして、後にpチャネル型MOSFETのLDD領域として機能する不純物領域

414、415を形成する。

クを行い、サイドウォール416、417を形成する。(図22(A)

)

を付与する不純物元素を 1×1020/cm3の濃度で導入する。こうしてソース領域41

9、ドレイン領域420が形成され、サイドウォール416の下にはLDD領域421が

形成される。(図22(B))

付与する不純物元素を1×1020/cm3の濃度で導入する。こうしてドレイン領域42

3、ソース領域424が形成され、サイドウォール417の下にはLDD領域425が形

成される。(図22(C))さらに、レジストマスク422で覆ったまま、希ガス元素か

ら選ばれた一種または複数種の元素を導入する。このようにして、第2のゲート電極40

7に第1のゲート電極406よりも不純物元素を多量に導入する。これにより、前記第2

のゲート電極407の圧縮応力は前記第1のゲート電極406より強く、pチャネル型M

OSFETにおけるチャネル形成領域が受ける圧縮応力も、nチャネル型MOSFETに

おけるチャネル形成領域が受ける応力よりも強くなる。

を行う。

ート電極の表面にチタンシリサイド層426を形成する。勿論、他の金属膜を用いた金属

シリサイドを形成することもできる。シリサイド層を形成した後、チタン膜は除去する。

のゲート電極407の内部応力も変化するが、第2のゲート電極407は第1のゲート電

極406より不純物元素の導入量が多いため、内部応力の変化は小さい。そのため、第2

のゲート電極407の圧縮応力は第1のゲート電極406より強く、pチャネル型MOS

FETにおけるチャネル形成領域が受ける圧縮応力も、nチャネル型MOSFETにおけ

るチャネル形成領域が受ける応力よりも強い。

9、ドレイン電極430を形成する。勿論、電極形成後に水素化を行うことも有効である

。

電極の内部応力が制御されたCMOS回路の電気的特性は、良好なものとなり、半導体装

置の動作特性も大幅に向上し得る。

る。本明細書ではCMOS回路、及び駆動回路と、画素TFT、保持容量とを有する画素

部を同一基板上に形成された基板を、便宜上アクティブマトリクス基板と呼ぶ。

れるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラスからなる

基板501を用いる。なお、基板501としては、石英基板や単結晶シリコン基板、金属

基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本実施

例の処理温度に耐えうる耐熱性が有するプラスチック基板を用いてもよい。本実施例では

合成石英ガラス基板を用いる。

たは酸化窒化珪素膜などの絶縁膜から成る膜厚10〜150nm(好ましくは50〜10

0nm)の下地膜を形成する。そして、本実施例の処理温度に耐え得るTa、W、Cr、

Mo等の導電性材料およびその積層構造により300nm程度の膜厚で下部遮光膜を形成す

る。前記下部遮光膜はゲート配線としての機能も有する。本実施例では膜厚75nmの結

晶質珪素膜を形成し、続いて膜厚150nmのWSix(x=2.0〜2.8)を成膜し

た後、不要な部分をエッチングして下部遮光膜503を形成する。なお、本実施例では、

下部遮光膜503として単層構造を用いるが、前記絶縁膜を2層以上積層させた構造を用

いても良い。

珪素膜などの絶縁膜から成る膜厚10〜650nm(好ましくは50〜600nm)の下

地膜504を形成する。本実施例では下地膜504として単層構造を用いるが、前記絶縁

膜を2層以上積層させた構造を用いても良い。本実施例では、下地膜504としては、プ

ラズマCVD法を用い、SiH4、NH3、及びN2Oを反応ガスとして成膜される膜厚5

80nmの酸化窒化珪素膜504(組成比Si=32%、O=27%、N=24%、H=

17%)を350℃にて形成する。

を有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等

)により、25〜80nm(好ましくは30〜60nm)の厚さで形成する。半導体膜の

材料に限定はないが、好ましくは珪素または珪素ゲルマニウム(SiGe)合金などで形

成すると良い。

た、ニッケルなどの触媒を用いた熱結晶化法の他に、公知の結晶化処理(レーザ結晶化法

、熱結晶化法等)を組み合わせて行ってもよい。本実施例では、酢酸ニッケル溶液(重量

換算濃度10ppm、体積5ml)をスピンコートにより膜上全面に塗布して金属含有層

405を形成し、温度600度の窒素雰囲気中に12時間曝す。

レーザやYAGレーザ、YVO4レーザ等を用いることができる。これらのレーザを用い

る場合には、レーザ発振器から放射されたレーザビームを光学系で線状に集光し半導体膜

に照射する方法を用いると良い。結晶化の条件は実施者が適宣選択するものであるが、エ

キシマレーザを用いる場合はパルス発振周波数300Hzとし、レーザーエネルギー密度

を100〜800mJ/cm2(代表的には200〜700mJ/cm2)とする。また、YAGレーザ

を用いる場合にはその第2高調波を用いパルス発振周波数1〜300Hzとし、レーザー

エネルギー密度を300〜1000mJ/cm2(代表的には350〜800mJ/cm2)とすると良

い。そして幅100〜1000μm、例えば400μmで線状に集光したレーザビームを

基板全面に渡って照射し、この時の線状レーザビームの重ね合わせ率(オーバーラップ率

)を50〜98%として行ってもよい。

または低減するために、ゲッタリングを行う。ゲッタリングについては特開平10−27

0363号公報に開示している方法を適用すればよい。本実施例では、マスクとして、膜

厚50nmの酸化珪素膜を形成し、パターニングを行って、所望の形状の酸化珪素膜50

6a〜506dを得る。そして、半導体膜に選択的に15族に属する元素(代表的にはP

(リン))を導入し、熱処理を行うことで、半導体層から金属元素を除去または半導体特

性に影響しない程度にまで低減することができる。このようにして作製した活性領域を有

するTFTはオフ電流値が下がり、結晶性が良いことから高い電界効果移動度が得られ、

良好な特性を達成することができる。

る。(図9(D))

結晶性を向上させるために熱処理を行って、半導体層の上部を熱酸化させるのが望ましい

。本実施例では、減圧CVD装置で20nmの酸化珪素膜を成膜した後、ファーネスアニ

ール炉で熱処理を行う。この処理により、半導体層507a〜510aの上部は酸化され

る。そして、酸化珪素膜および半導体層の酸化した部分をエッチングすると、結晶性の向

上した半導体層507b〜510bが得られる。

不純物元素(ボロンまたはリン)を導入してもよい。

1のゲート絶縁膜511はプラズマCVD法またはスパッタ法を用い、厚さを20〜15

0nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により35

nmの厚さで酸化窒化珪素膜(組成比Si=32%、O=59%、N=7%、H=2%)

で形成した。もちろん、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪

素を含む絶縁膜を用いても良い。

silicate)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波

(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。こ

のようにして作製される酸化珪素膜は、その後400〜500℃の熱アニールによりゲー

ト絶縁膜として良好な特性を得ることができる。

導体層510aを露出させ、該半導体層510aに不純物元素を導入する。(図10(B

))このとき、他の領域にはレジスト513が形成されており、不純物元素は導入されな

い。本実施例では、不純物元素としてP(リン)を用い、加速電圧10keV、ドーズ量

5×1014/cm2として不純物元素を導入する。

CVD法またはスパッタ法を用い、厚さを20〜150nmとして珪素を含む絶縁膜で形

成する。本実施例では、プラズマCVD法により50nmの厚さで酸化窒化珪素膜(組成

比Si=32%、O=59%、N=7%、H=2%)

で形成した。もちろん、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪

素を含む絶縁膜を用いても良い。

の導電膜515と、膜厚100〜400nmの第2の導電膜516aとを積層形成する。

本実施例では、膜厚30nmのTaN膜からなる第1の導電膜515と、膜厚370nm

のW膜からなる第2の導電膜516aを積層形成する。TaN膜はスパッタ法で形成し、

Taのターゲットを用い、窒素を含む雰囲気内でスパッタした。また、W膜は、Wのター

ゲットを用いたスパッタ法で形成する。その他に6フッ化タングステン(WF6)を用い

る熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するために

は低抵抗化を図る必要があり、W膜の抵抗率は20μΩcm以下にすることが望ましい。

いるが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cu、Cr、Ndから

選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成しても

よい。また、リン等の不純物元素を導入した結晶質珪素膜に代表される半導体膜を用いて

もよい。また、AgPdCu合金を用いてもよい。また、第1の導電膜をタンタル(Ta

)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化チタン(Ti

N)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化タンタル(

TaN)膜で形成し、第2の導電膜をAl膜とする組み合わせ、第1の導電膜を窒化タン

タル(TaN)膜で形成し、第2の導電膜をCu膜とする組み合わせとしてもよい。

純物元素の導入を行う。不純物元素の導入はプラズマドーピング法、イオン注入法、また

はイオンシャワードーピング法で行えば良い。これにより、圧縮応力の増加の方向へ変化

し、所望の内部応力を有する第2の導電膜516bを形成することができる。(図10(

D))本実施例では、加速電圧70keVとし、Arを用いて不純物元素を導入する。

電極及び配線を形成するためのエッチング処理を行う。本実施例ではエッチング条件とし

て、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用い、

エッチング用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を25/25/

10(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力

を投入してプラズマを生成してエッチングを行った。基板側(試料ステージ)にも150

WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。

する。(図11(A))不純物元素を導入するときの条件は1×1013〜5×1014/cm2

とし、加速電圧を30〜80keVとして行う。本実施例ではドーズ量を1.5×1013

/cm2とし、加速電圧を60keVとして行う。n型を付与する不純物元素として15族

に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P

)を用いる。この場合、導電層517〜521がn型を付与する不純物元素に対するマス

クとなり、自己整合的に低濃度不純物領域523〜524が形成される。低濃度不純物領

域523〜524には1×1018〜1×1020/cm3の濃度範囲でn型を付与する不純物元

素を添加する。ここで、pチャネル型TFTを形成する半導体層にはレジストによるマス

ク522が形成されており、n型を付与する不純物元素は導入されない。

示すように、第5の不純物元素の導入を行う。不純物元素を導入しするときの条件はドー

ズ量を1×1013〜1×1015/cm2とし、加速電圧を30〜120keVとして行う。こ

のとき、pチャネル型TFTを形成する半導体層にn型を付与する不純物元素を導入しな

いためにマスク525bを形成し、また、nチャネル型TFTを形成するための半導体層

に選択的に高濃度不純物領域を形成するためにマスク525a、525cを形成する。本

実施例ではドーズ量を2×1015/cm2とし、加速電圧を50keVとして行った。こ

うして、高濃度不純物領域526、529が形成される。

aおよび532bを形成して、図11(C)に示すように、第6の不純物元素の導入を行

う。この第6の不純物元素の導入により、pチャネル型TFTの活性層となる半導体層に

前記一導電型とは逆の導電型を付与する不純物元素が添加された不純物領域533を形成

する。第2の導電層518を不純物元素に対するマスクとして用い、p型を付与する不純

物元素を添加して自己整合的に不純物領域を形成する。本実施例では、不純物領域533

はジボラン(B2H6)を用いたイオンシャワードーピング法で形成する。イオンシャワー

ドーピング法の条件はドーズ量を1×1013〜1×1014/cm2とし、加速電圧を30〜1

20keVとして行う。この第6の不純物元素の導入の際には、nチャネル型TFTを形

成する半導体層はレジストからなるマスク532aおよび532bで覆われている。

示すように、第7の不純物元素の導入を行う。不純物元素を導入するときの条件はドーズ

量を1×1013〜1×1015/cm2とし、加速電圧を20〜120keVとして行う。この

とき、nチャネル型TFTを形成する半導体層にp型を付与する不純物元素を導入しない

ためにマスク534a、534cを形成し、また、pチャネル型TFTを形成するための

半導体層に選択的に高濃度不純物領域を形成するためにマスク534bを形成する。本実

施例ではドーズ量を1×1015/cm2とし、加速電圧を40keVとして行う。こうし

て、高濃度不純物領域535が形成される。

形成される。

。この第1の層間絶縁膜538としては、プラズマCVD法またはスパッタ法を用い、厚

さを100〜200nmとして珪素を含む絶縁膜で形成する。

本実施例では、プラズマCVD法により膜厚150nmの酸化窒化珪素膜を形成した。も

ちろん、第1の層間絶縁膜538は酸化窒化珪素膜に限定されるものでなく、他の珪素を

含む絶縁膜を単層または積層構造として用いても良い。

ぞれの半導体層に添加された不純物元素の活性化を行う。この熱処理はファーネスアニー

ル炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が1ppm以下、好

ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜55

0℃で行えばよく、本実施例では550℃、4時間の熱処理で活性化処理を行った。なお

、熱アニール法の他に、レーザアニール法、またはラピッドサーマルアニール法(RTA

法)を適用することができる。

料が熱に弱い場合には、本実施例のように配線等を保護するため層間絶縁膜(珪素を主成

分とする絶縁膜、例えば窒化珪素膜)を形成した後で熱処理を行うことが好ましい。

とができる。この工程は第1の層間絶縁膜461に含まれる水素により半導体層のダング

リングボンドを終端する工程である。もちろん、第1の層間絶縁膜の存在に関係なく半導

体層を水素化することもできる。水素化の他の手段として、プラズマ水素化(プラズマに

より励起された水素を用いる)や、3〜100%の水素を含む雰囲気中で300〜450

℃で1〜12時間の熱処理を行っても良い。

2の層間絶縁膜539を形成する。本実施例では、膜厚1μmの窒化酸化珪素膜を形成す

る。

0〜542を形成する。また、画素部556においては、ソース配線543、545、ド

レイン電極544を形成する。なお、これらの配線は、膜厚50nmのTi膜と、膜厚5

00nmの合金膜(AlとTiとの合金膜)との積層膜をパターニングして形成する。

には同じ符号を用いている。図12(C)中の鎖線A−A’は図13中の鎖線A―A’で

切断した断面図に対応している。また、図12(C)中の鎖線B−B’は図13中の鎖線

B―B’で切断した断面図に対応している。

3の層間絶縁膜560を形成する。本実施例では、膜厚1.8μmの窒化酸化珪素膜を形

成する。

持つ膜を所望の形状にパターニングして遮光膜561、562を形成する。この遮光膜5

61、562は画素の開口部以外を遮光するように網目状に配置する。さらに、この遮光

膜117を覆うように第4の層間絶縁膜563を無機絶縁材料により形成する。

00nm厚形成し、所望の形状にパターニングすることで画素電極564、565を形成す

る。

回路555と、画素TFT553、保持容量554とを有する画素部556が同一基板上

に形成されたアクティブマトリクス基板が完成する。

導体膜に及ぼす応力が低減できる。そして、このようなゲート電極を用いてTFTを作製

すると、その電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る

。

もちろん、実施例4で形成するTFTや実施例5で形成するMOSFETを用いてアクテ

ィブマトリクス基板を作製することも可能である。

置を作製する工程を以下に説明する。説明には図15を用いる。

記アクティブマトリクス基板上、少なくとも画素電極564、565上に配向膜567を

形成しラビング処理を行う。なお、本実施例では配向膜567を形成する前に、アクリル

樹脂膜等の有機樹脂膜をパターニングすることによって基板間隔を保持するための柱状の

スペーサ572を所望の位置に形成した。また、柱状のスペーサに代えて、球状のスペー

サを基板全面に散布してもよい。

化膜573を形成する。

形成し、対向基板の全面に配向膜574を形成し、ラビング処理を施した。

ル材568で貼り合わせる。シール材568にはフィラーが混入されていて、このフィラ

ーと柱状スペーサによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、

両基板の間に液晶材料575を注入し、封止剤(図示せず)によって完全に封止する。液

晶材料575には公知の液晶材料を用いれば良い。このようにして図15に示す反射型液

晶表示装置が完成する。そして、必要があれば、アクティブマトリクス基板または対向基

板を所望の形状に分断する。さらに、対向基板のみに偏光板(図示しない)を貼りつけた

。そして、公知の技術を用いてFPCを貼りつけた。

御されていることから、半導体膜に及ぼす応力も低減することが可能となり、前記液晶表

示装置の動作特性も大幅に向上し得る。そして、このような液晶表示装置は各種電子機器

の表示部として用いることができる。

可能である。

いて、発光装置とは、基板上に形成された発光素子を該基板とカバー材の間に封入した表

示用パネルおよび該表示用パネルにIC(Integrated Circuit)を実装した表示用モジュ

ールを総称したものである。なお、発光素子は、電場を加えることで発生するルミネッセ

ンス(Electro Luminescence)が得られる有機化合物を含む層(発光層)と陽極層と、陰

極層とを有する。また、有機化合物におけるルミネッセンスには、一重項励起状態から基

底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)

があり、これらのうちどちらか、あるいは両方の発光を含む。

れた駆動回路は図16のCMOS回路を用いて形成される。従って、構造の説明はnチャ

ネル型TFT551とpチャネル型TFT552の説明を参照すれば良いが、nチャネル

型TFT551とpチャネル型TFT552のゲート電極にArを導入することで内部応

力を制御しており、半導体膜に及ぼす応力を低減してある。そのため、TFTの電気的特

性を向上させることが可能となっている。なお、本実施例ではシングルゲート構造として

いるが、ダブルゲート構造もしくはトリプルゲート構造であっても良い。

FT551を用いて形成される。したがって、構造の説明はnチャネル型TFT551の

説明を参照すれば良いが、nチャネル型TFT551のゲート電極にArを導入すること

で内部応力を制御しており、半導体膜に及ぼす応力を低減してある。そのため、TFTの

電気的特性を向上させることが可能となっている。

、チャネル形成領域が一つ形成されるシングルゲート構造もしくは三つ形成されるトリプ

ルゲート構造であっても良い。

機能する。また、配線704はソース配線(図示せず)とスイッチングTFTのソース領

域とを電気的に接続する配線として機能し、配線705はドレイン配線(図示せず)とス

イッチングTFTのドレイン領域とを電気的に接続する配線として機能する。

される。従って、構造の説明はpチャネル型TFT552の説明を参照すれば良いが、p

チャネル型TFT552のゲート電極にArを導入することで内部応力を制御しており、

半導体膜に及ぼす応力を低減してある。そのため、TFTの電気的特性を向上させること

が可能となっている。なお、本実施例ではシングルゲート構造としているが、ダブルゲー

ト構造もしくはトリプルゲート構造であっても良い。

素電極711と電気的に接続する電極である。

としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物

、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電

膜にガリウムを添加したものを用いても良い。画素電極711は、上記配線を形成する前

に平坦な層間絶縁膜710上に形成する。本実施例においては、樹脂からなる平坦化膜7

10を用いてTFTによる段差を平坦化することは非常に重要である。後に形成される発

光層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従っ

て、発光層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化してお

くことが望ましい。

バンク712は100〜400nmの珪素を含む絶縁膜もしくは有機樹脂膜をパターニン

グして形成すれば良い。

要である。本実施例ではバンク712の材料となる絶縁膜中にカーボン粒子や金属粒子を

添加して抵抗率を下げ、静電気の発生を抑制する。この際、抵抗率は1×106〜1×1

012Ωm(好ましくは1×108〜1×1010Ωm)となるようにカーボン粒子や金属粒

子の添加量を調節すれば良い。

していないが、本実施例ではR(赤)、G(緑)、B(青)の各色に対応した発光層を作

り分けている。また、本実施例では蒸着法により低分子系有機発光材料を形成している。

具体的には、正孔注入層として20nm厚の銅フタロシアニン(CuPc)膜を設け、そ

の上に発光層として70nm厚のトリス−8−キノリノラトアルミニウム錯体(Alq3

)膜を設けた積層構造としている。

Alq3にキナクリドン、ペリレンもしくはDCM1といった蛍光色素を添加することで

発光色を制御することができる。

に限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わ

せて発光層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い

。例えば、本実施例では低分子系有機発光材料を発光層として用いる例を示したが、高分

子系有機発光材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無

機材料を用いることも可能である。

これらの有機発光材料や無機材料は公知の材料を用いることができる。

、導電膜としてアルミニウムとリチウムとの合金膜を用いる。勿論、公知のMgAg膜(

マグネシウムと銀との合金膜)を用いても良い。陰極材料としては、周期表の1族もしく

は2族に属する元素からなる導電膜もしくはそれらの元素を添加した導電膜を用いれば良

い。

光素子715は、画素電極(陽極)711、発光層713及び陰極714で形成されたダ

イオードを指す。

である。パッシベーション膜716としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素

膜を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いる。

、特にDLC(ダイヤモンドライクカーボン)膜を用いることは有効である。DLC膜は

室温から100℃以下の温度範囲で成膜可能であるため、耐熱性の低い発光層713の上

方にも容易に成膜することができる。また、DLC膜は酸素に対するブロッキング効果が

高く、発光層713の酸化を抑制することが可能である。そのため、この後に続く封止工

程を行う間に発光層713が酸化するといった問題を防止できる。

わせる。封止材717としては紫外線硬化樹脂を用いれば良く、内部に吸湿効果を有する

物質もしくは酸化防止効果を有する物質を設けることは有効である。また、本実施例にお

いてカバー材718はガラス基板や石英基板やプラスチック基板(プラスチックフィルム

も含む)の両面に炭素膜(好ましくはダイヤモンドライクカーボン膜)を形成したものを

用いる。

た後、パッシベーション膜716を形成するまでの工程をマルチチャンバー方式(または

インライン方式)の成膜装置を用いて、大気解放せずに連続的に処理することは有効であ

る。また、さらに発展させてカバー材718を貼り合わせる工程までを大気解放せずに連

続的に処理することも可能である。

従えば、その他にも信号分割回路、D/Aコンバータ、オペアンプ、γ補正回路などの論

理回路を同一の絶縁体上に形成可能であり、さらにはメモリやマイクロプロセッサをも形

成しうる。

発光装置について図17を用いて説明する。なお、必要に応じて図16で用いた符号を引

用する。

7(A)をC−C’で切断した断面図である。点線で示された801はソース側駆動回路

、806は画素部、807はゲート側駆動回路である。また、901はカバー材、902

は第1シール材、903は第2シール材であり、第1シール材902で囲まれた内側には

封止材907が設けられる。

を伝送するための配線であり、外部入力端子となるFPC(フレキシブルプリントサーキ

ット)905からビデオ信号やクロック信号を受け取る。なお、ここではFPCしか図示

されていないが、このFPCにはプリント配線基板(PWB)が取り付けられていても良

い。本明細書における発光装置には、発光装置本体だけでなく、それにFPCもしくはP

WBが取り付けられた状態をも含むものとする。

806、ゲート側駆動回路807が形成されており、画素部806は電流制御TFT60

4とそのドレインに電気的に接続された画素電極711を含む複数の画素により形成され

る。また、ゲート側駆動回路807はnチャネル型TFT601とpチャネル型TFT6

02とを組み合わせたCMOS回路(図16参照)を用いて形成される。

ンク712が形成され、画素電極711上には発光層713および発光素子の陰極714

が形成される。

05に電気的に接続されている。さらに、画素部806及びゲート側駆動回路807に含

まれる素子は全て陰極714およびパッシベーション膜567で覆われている。

材901と発光素子との間隔を確保するために樹脂膜からなるスペーサを設けても良い。

そして、第1シール材902の内側には封止材907が充填されている。なお、第1シー

ル材902、封止材907としてはエポキシ系樹脂を用いるのが好ましい。また、第1シ

ール材902はできるだけ水分や酸素を透過しない材料であることが望ましい。さらに、

封止材907の内部に吸湿効果をもつ物質や酸化防止効果をもつ物質を含有させても良い

。

接着剤としても機能する。また、本実施例ではカバー材901を構成するプラスチック基

板901aの材料としてFRP(Fiberglass-Reinforced Plastics)、PVF(ポリビニ

ルフロライド)、マイラー、ポリエステルまたはアクリルを用いることができる。

面)を覆うように第2シール材903を設ける。第2シール材903は第1シール材90

2と同じ材料を用いることができる。

ら完全に遮断することができ、外部から水分や酸素等の発光層の酸化による劣化を促す物

質が侵入することを防ぐことができる。従って、信頼性の高い発光装置が得られる。

れていることから、半導体膜に及ぼす応力も低減することが可能となり、前記発光装置の

動作特性も大幅に向上し得る。そして、このような発光装置は各種電子機器の表示部とし

て用いることができる。

可能である。

マトリクス型液晶表示装置、アクティブマトリクス型EC表示装置、アクティブマトリク

ス型発光装置)に用いることが出来る。即ち、それら電気光学装置を表示部に組み込んだ

電子機器全てに本発明を実施出来る。

マウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、カーステレオ

、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子

書籍等)などが挙げられる。それらの一例を図18、図19及び図20に示す。

表示部3003、キーボード3004等を含む。本発明を表示部3003に適用すること

ができる。

03、操作スイッチ3104、バッテリー3105、受像部3106等を含む。本発明を

表示部3102に適用することができる。

、カメラ部3202、受像部3203、操作スイッチ3204、表示部3205等を含む

。本発明は表示部3205に適用できる。

ム部3303等を含む。本発明は表示部3302に適用することができる。

ーヤーであり、本体3401、表示部3402、スピーカ部3403、記録媒体3404

、操作スイッチ3405等を含む。なお、このプレーヤーは記録媒体としてDVD(Di

gtial Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲ

ームやインターネットを行なうことができる。本発明は表示部3402に適用することが

できる。

3、操作スイッチ3504、受像部(図示しない)等を含む。本発明を表示部3502に

適用することができる。

02等を含む。本発明は投射装置3601の一部を構成する液晶表示装置3808やその

他の駆動回路に適用することができる。

ー3703、スクリーン3704等を含む。本発明は投射装置2702の一部を構成する

液晶表示装置3808やその他の駆動回路に適用することができる。

3702の構造の一例を示した図である。投射装置3601、3702は、光源光学系3

801、ミラー3802、3804〜3806、ダイクロイックミラー3803、プリズ

ム3807、液晶表示装置3808、位相差板3809、投射光学系3810で構成され

る。投射光学系2810は、投射レンズを含む光学系で構成される。本実施例は三板式の

例を示したが、特に限定されず、例えば単板式であってもよい。また、図19(C)中に

おいて矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、

位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。

した図である。本実施例では、光源光学系3801は、リフレクター3811、光源38

12、レンズアレイ3813、3814、偏光変換素子3815、集光レンズ3816で

構成される。なお、図19(D)に示した光源光学系は一例であって特に限定されない。

例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相

差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

合を示しており、反射型の電気光学装置及び発光装置での適用例は図示していない。

03、表示部3904、操作スイッチ3905、アンテナ3906等を含む。本発明を表

示部3904に適用することができる。

3、記憶媒体4004、操作スイッチ4005、アンテナ4006等を含む。本発明は表

示部4002、4003に適用することができる。

等を含む。本発明は表示部4103に適用することができる。本発明のディスプレイは特

に大画面化した場合において有利であり、対角10インチ以上(特に30インチ以上)の

ディスプレイには有利である。

とが可能である。また、本実施例の電子機器は実施例2〜7のどのような組み合わせから

なる構成を用いても実現することができる。また、実施例8を図18および図20におけ

る電子機器に適用することも可能である。

Claims (5)

- 基板上の、遮光膜と、

前記遮光膜上の、結晶性半導体膜と、

前記結晶性半導体膜上の、ゲート電極と、

前記ゲート電極上の、第1の絶縁膜と、

前記第1の絶縁膜の第1のコンタクトホールを介して、前記結晶性半導体膜の不純物領域と電気的に接続された、ドレイン電極と、

前記ドレイン電極上の、第2の絶縁膜と、

前記第2の絶縁膜上の、配線と、

前記配線上の、第3の絶縁膜と、

前記第2の絶縁膜の第2のコンタクトホール及び前記第3の絶縁膜の第3のコンタクトホールを介して、前記ドレイン電極と電気的に接続された、画素電極と、を有し、

前記結晶性半導体膜は、前記遮光膜の端部より内側にある、端部を有し、

前記遮光膜は、前記結晶性半導体膜のチャネル形成領域と重なり、

前記配線は、遮光性を有し、

前記配線は、網目状に配置されていることを特徴とする半導体装置。 - 基板上の、遮光膜と、

前記遮光膜上の、結晶性半導体膜と、

前記結晶性半導体膜上の、ゲート電極と、

前記ゲート電極上の、第1の絶縁膜と、

前記第1の絶縁膜の第1のコンタクトホールを介して、前記結晶性半導体膜の不純物領域と電気的に接続された、ドレイン電極と、

前記ドレイン電極上の、第2の絶縁膜と、

前記第2の絶縁膜上の、配線と、

前記配線上の、第3の絶縁膜と、

前記第2の絶縁膜の第2のコンタクトホール及び前記第3の絶縁膜の第3のコンタクトホールを介して、前記ドレイン電極と電気的に接続された、画素電極と、を有し、

前記結晶性半導体膜は、前記遮光膜の端部より内側にある、端部を有し、

前記遮光膜は、前記結晶性半導体膜のチャネル形成領域と重なり、

前記配線は、遮光性を有し、

前記配線は、網目状に配置され、

前記第1のコンタクトホールは、前記第2のコンタクトホールとずれ、

前記第1のコンタクトホールは、前記第3のコンタクトホールとずれていることを特徴とする半導体装置。 - 基板上の、遮光膜と、

前記遮光膜上の、結晶性半導体膜と、

前記結晶性半導体膜上の、ゲート電極と、

前記ゲート電極上の、第1の絶縁膜と、

前記第1の絶縁膜の第1のコンタクトホールを介して、前記結晶性半導体膜の不純物領域と電気的に接続された、ドレイン電極と、

前記ドレイン電極上の、第2の絶縁膜と、

前記第2の絶縁膜上の、配線と、

前記配線上の、第3の絶縁膜と、

前記第2の絶縁膜の第2のコンタクトホール及び前記第3の絶縁膜の第3のコンタクトホールを介して、前記ドレイン電極と電気的に接続された、画素電極と、を有し、

前記結晶性半導体膜は、前記遮光膜の端部より内側にある、端部を有し、

前記遮光膜は、前記結晶性半導体膜のチャネル形成領域と重なり、

前記配線は、遮光性を有し、

前記配線は、開口部を有するように網目状に配置され、

前記開口部と重なる位置に、前記画素電極と、前記第1のコンタクトホール乃至第3のコンタクトホールと、前記ドレイン電極と、前記ゲート電極と、前記チャネル形成領域と、前記遮光膜と、を有し、

前記第1のコンタクトホールは、前記第2のコンタクトホールとずれ、

前記第1のコンタクトホールは、前記第3のコンタクトホールとずれていることを特徴とする半導体装置。 - 基板上の、遮光膜と、

前記遮光膜上の、結晶性半導体膜と、

前記結晶性半導体膜上の、ゲート電極と、

前記ゲート電極上の、第1の絶縁膜と、

前記第1の絶縁膜の第1のコンタクトホールを介して、前記結晶性半導体膜の不純物領域と電気的に接続された、ドレイン電極と、

前記ドレイン電極上の、第2の絶縁膜と、

前記第2の絶縁膜上の、配線と、

前記配線上の、第3の絶縁膜と、

前記第2の絶縁膜の第2のコンタクトホール及び前記第3の絶縁膜の第3のコンタクトホールを介して、前記ドレイン電極と電気的に接続された、画素電極と、を有し、

前記結晶性半導体膜は、前記遮光膜の端部より内側にある、端部を有し、

前記遮光膜は、前記結晶性半導体膜のチャネル形成領域と重なり、

前記配線は、遮光性を有し、

前記配線は、ソース線と重なり、且つ、開口部を有するように網目状に配置され、

前記開口部と重なる位置に、前記画素電極と、前記第1のコンタクトホール乃至第3のコンタクトホールと、前記ドレイン電極と、前記ゲート電極と、前記チャネル形成領域と、前記遮光膜と、を有し、

前記第1のコンタクトホールは、前記第2のコンタクトホールとずれ、

前記第1のコンタクトホールは、前記第3のコンタクトホールとずれていることを特徴とする半導体装置。 - 請求項1乃至請求項4のいずれか一において、

前記遮光膜は、前記ゲート電極の導電性材料と共通した導電性材料を有することを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017045566A JP6154976B1 (ja) | 2017-03-10 | 2017-03-10 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017045566A JP6154976B1 (ja) | 2017-03-10 | 2017-03-10 | 半導体装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016163400A Division JP2016213202A (ja) | 2016-08-24 | 2016-08-24 | 発光装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP6154976B1 true JP6154976B1 (ja) | 2017-06-28 |

| JP2017130679A JP2017130679A (ja) | 2017-07-27 |

Family

ID=59218541

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017045566A Expired - Lifetime JP6154976B1 (ja) | 2017-03-10 | 2017-03-10 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6154976B1 (ja) |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1195687A (ja) * | 1997-09-20 | 1999-04-09 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| JP2000196093A (ja) * | 1998-12-25 | 2000-07-14 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000276076A (ja) * | 1999-01-21 | 2000-10-06 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000353811A (ja) * | 1999-04-07 | 2000-12-19 | Semiconductor Energy Lab Co Ltd | 電気光学装置およびその作製方法 |

| JP2001094112A (ja) * | 1999-09-27 | 2001-04-06 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2001109394A (ja) * | 1999-07-23 | 2001-04-20 | Semiconductor Energy Lab Co Ltd | 画像認識装置一体型表示装置 |

| JP2016122850A (ja) * | 2016-02-03 | 2016-07-07 | 株式会社半導体エネルギー研究所 | 半導体装置 |

-

2017

- 2017-03-10 JP JP2017045566A patent/JP6154976B1/ja not_active Expired - Lifetime

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1195687A (ja) * | 1997-09-20 | 1999-04-09 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| JP2000196093A (ja) * | 1998-12-25 | 2000-07-14 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000276076A (ja) * | 1999-01-21 | 2000-10-06 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000353811A (ja) * | 1999-04-07 | 2000-12-19 | Semiconductor Energy Lab Co Ltd | 電気光学装置およびその作製方法 |

| JP2001109394A (ja) * | 1999-07-23 | 2001-04-20 | Semiconductor Energy Lab Co Ltd | 画像認識装置一体型表示装置 |

| JP2001094112A (ja) * | 1999-09-27 | 2001-04-06 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2016122850A (ja) * | 2016-02-03 | 2016-07-07 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2017130679A (ja) | 2017-07-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4831885B2 (ja) | 半導体装置の作製方法 | |

| US7208355B2 (en) | Semiconductor device and method for preparing the same | |

| JP4869509B2 (ja) | 半導体装置の作製方法 | |

| JP5105690B2 (ja) | 半導体装置の作製方法 | |

| JP5046439B2 (ja) | 半導体装置の作製方法 | |

| JP2015122538A (ja) | 半導体装置 | |

| JP6068767B2 (ja) | 半導体装置 | |

| JP5292453B2 (ja) | 半導体装置の作製方法 | |

| JP6154976B1 (ja) | 半導体装置 | |

| JP6412181B2 (ja) | 半導体装置 | |

| JP5779692B2 (ja) | 半導体装置 | |

| JP5703148B2 (ja) | 半導体装置 | |

| JP5448268B2 (ja) | 半導体装置 | |

| JP2018139313A (ja) | 半導体装置 | |

| JP2021056516A (ja) | 表示装置 | |

| JP2020096192A (ja) | 表示装置 | |

| JP2016213202A (ja) | 発光装置 | |

| JP2019075572A (ja) | 半導体装置 | |

| JP4302357B2 (ja) | 半導体装置の作製方法 | |

| JP6087970B2 (ja) | 表示装置、表示モジュール及び電子機器 | |

| JP2012142571A (ja) | 半導体装置 | |

| JP4641598B2 (ja) | 半導体装置の作製方法 | |

| JP4968982B2 (ja) | 半導体装置の作製方法 | |

| JP5799132B2 (ja) | 表示装置、表示モジュール、及び電子機器 | |

| JP2018190996A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20170510 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170523 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170602 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6154976 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |