JP6090447B2 - Arithmetic processing device and control method of arithmetic processing device - Google Patents

Arithmetic processing device and control method of arithmetic processing device Download PDFInfo

- Publication number

- JP6090447B2 JP6090447B2 JP2015527120A JP2015527120A JP6090447B2 JP 6090447 B2 JP6090447 B2 JP 6090447B2 JP 2015527120 A JP2015527120 A JP 2015527120A JP 2015527120 A JP2015527120 A JP 2015527120A JP 6090447 B2 JP6090447 B2 JP 6090447B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- supply voltage

- voltage value

- operating frequency

- calibration

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000012545 processing Methods 0.000 title claims description 58

- 238000000034 method Methods 0.000 title claims description 43

- 230000008569 process Effects 0.000 claims description 33

- 238000005259 measurement Methods 0.000 claims description 25

- 230000008859 change Effects 0.000 claims description 16

- 238000004364 calculation method Methods 0.000 claims description 3

- 238000010586 diagram Methods 0.000 description 28

- 238000012360 testing method Methods 0.000 description 28

- 238000004088 simulation Methods 0.000 description 21

- 238000012790 confirmation Methods 0.000 description 9

- 230000006870 function Effects 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 4

- 238000012937 correction Methods 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 101100129500 Caenorhabditis elegans max-2 gene Proteins 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 230000009471 action Effects 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/3296—Power saving characterised by the action undertaken by lowering the supply or operating voltage

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3206—Monitoring of events, devices or parameters that trigger a change in power modality

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/30—Monitoring

- G06F11/3058—Monitoring arrangements for monitoring environmental properties or parameters of the computing system or of the computing system component, e.g. monitoring of power, currents, temperature, humidity, position, vibrations

- G06F11/3062—Monitoring arrangements for monitoring environmental properties or parameters of the computing system or of the computing system component, e.g. monitoring of power, currents, temperature, humidity, position, vibrations where the monitored property is the power consumption

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Test And Diagnosis Of Digital Computers (AREA)

- Microcomputers (AREA)

- Power Sources (AREA)

Description

本発明は、演算処理装置及び演算処理装置の制御方法に関する。 The present invention relates to an arithmetic processing device and a control method for the arithmetic processing device.

演算処理装置で消費電力を抑えるための技術に、処理負荷等に応じて動作周波数(動作クロックの周波数)及び電源電圧を動的に制御する動的電圧・周波数制御(DVFS:Dynamic Voltage and Frequency Scaling)がある。例えば、DVFSでは、動作周波数が高ければ電源電圧を高く設定し、動作周波数が低ければ電源電圧を低く設定する。 Dynamic voltage and frequency scaling (DVFS: Dynamic Voltage and Frequency Scaling) that dynamically controls the operating frequency (frequency of the operating clock) and power supply voltage according to the processing load, etc. ) For example, in DVFS, if the operating frequency is high, the power supply voltage is set high, and if the operating frequency is low, the power supply voltage is set low.

DVFS制御で用いる複数の動作周波数と電源電圧値を決定するには、下記<1>〜<3>のような方法がある。

<1>シミュレーションにより見積もる。

<2>DVFS制御で用いる一部の動作周波数と電源電圧値を、それぞれ実際に試験を行うことで測定し、残りは測定結果から算出することで補間する。

<3>DVFS制御で用いるすべての動作周波数と電源電圧値を、それぞれ実際に試験を行うことで測定する。In order to determine a plurality of operating frequencies and power supply voltage values used in DVFS control, there are the following methods <1> to <3>.

<1> Estimate by simulation.

<2> Some operating frequencies and power supply voltage values used in DVFS control are measured by actually performing tests, and the remainder is interpolated by calculating from the measurement results.

<3> All operating frequencies and power supply voltage values used in DVFS control are measured by actually performing tests.

また、例えば、半導体集積回路でのプロセスばらつきによる動作速度の変化をプロセスモニタ回路を用いて測定し、測定結果を基にプロセスばらつきに応じた電源電圧の補正を行う技術が提案されている(例えば、特許文献1参照)。また、演算処理装置の動作周波数と電源電圧を決める際に、ダイナミックにテストを実行し、テストにより得られた情報を操作して、不揮発性メモリに保管する技術が提案されている(例えば、特許文献2参照)。 In addition, for example, a technique has been proposed in which a change in operating speed due to process variation in a semiconductor integrated circuit is measured using a process monitor circuit, and a power supply voltage is corrected according to the process variation based on the measurement result (for example, , See Patent Document 1). Further, a technique has been proposed in which, when determining the operating frequency and power supply voltage of an arithmetic processing unit, a test is dynamically executed, information obtained by the test is manipulated, and stored in a nonvolatile memory (for example, a patent) Reference 2).

しかしながら、例えば特許文献1に記載されているような、プロセスばらつきによる動作速度の変化をプロセスモニタ回路で測定し電源電圧を補正する技術では、プロセスモニタ回路と実際の回路動作とを補正する手段がない。そのため、プロセスモニタ回路の回路特性が、プロセスばらつきにより実際に動作する回路の特性に合っていない場合には、最適な電源電圧値が得られない。また、例えば特許文献2に記載されているようなダイナミックにテストを実行して情報を得る技術では、動作周波数及び電源電圧の最適値を求めるために多大な時間を要してしまう。

However, in a technique for measuring a change in operation speed due to process variation by a process monitor circuit and correcting a power supply voltage as described in

ここで、予めシミュレーションにより、演算処理装置におけるDVFS制御で用いる動作周波数と電源電圧値を決める場合について、図13A及び図13Bを参照して説明する。図13A及び図13Bは、シミュレーション結果に基づく動作周波数に対する電源電圧値の設定例を示す図である。図13A及び図13Bのそれぞれにおいて、横軸が動作周波数であり、縦軸が電圧値である。 Here, a case where the operating frequency and the power supply voltage value used in the DVFS control in the arithmetic processing device are determined in advance by simulation will be described with reference to FIGS. 13A and 13B. 13A and 13B are diagrams illustrating setting examples of the power supply voltage value with respect to the operating frequency based on the simulation result. In each of FIG. 13A and FIG. 13B, a horizontal axis is an operating frequency and a vertical axis | shaft is a voltage value.

図13Aにおいて、V101がシミュレーションにより得られた、動作周波数に対する電源電圧値を示している。また、V102が製造時にプロセスばらつきが速い側にばらついた場合における電源電圧値を示し、V103が製造時にプロセスばらつきが遅い側にばらついた場合における電源電圧値を示している。製造時にプロセスばらつきが遅い側にばらついたとしても演算処理装置の誤動作を回避するためには、動作周波数に対する電源電圧値はV103となる。さらに、プロセスばらつき以外にも、電源回路及び回路動作に伴う電圧降下やDVFSでの電源電圧遷移によるノイズ等によって発生する、演算処理装置に供給する電源電圧の変動に対するマージン等も考慮すると、動作周波数に対する電源電圧値はV104となる。 In FIG. 13A, V101 shows the power supply voltage value with respect to the operating frequency obtained by simulation. Further, V102 indicates a power supply voltage value when the process variation is fast at the time of manufacturing, and V103 indicates a power supply voltage value when the process variation is at the slow side during manufacturing. In order to avoid the malfunction of the arithmetic processing unit even if the process variation varies at the time of manufacturing, the power supply voltage value with respect to the operating frequency is V103. Furthermore, in addition to process variations, considering the margin for fluctuations in the power supply voltage supplied to the processing unit, which is caused by voltage drop due to the power supply circuit and circuit operation, noise due to power supply voltage transition in DVFS, etc. The power supply voltage value for V is V104.

つまり、演算処理装置におけるDVFS制御で用いる動作周波数と電源電圧値の初期設定値は、動作マージンを考慮すると、図13Bに示す(F0,V0)〜(F5,V5)となる。これは、演算処理装置の実際の性能に対して必要以上のマージンが含まれる可能性があり、例えば製造時にプロセスばらつきが速い側にばらついた場合の動作周波数に対する電源電圧値V102に対して、設定される電源電圧値は最も過剰となる。このように、シミュレーションによってDVFS制御で用いる動作周波数と電源電圧値を決めると、個々の演算処理装置のプロセスばらつきに応じた適切な電源電圧値が得られず、無駄な電力を消費することとなる。That is, the initial setting values of the operating frequency and the power supply voltage value used in the DVFS control in the arithmetic processing device are (F 0 , V 0 ) to (F 5 , V 5 ) shown in FIG. This may include an unnecessarily large margin for the actual performance of the arithmetic processing unit. For example, it is set with respect to the power supply voltage value V102 with respect to the operating frequency when the process variation varies at the time of manufacturing. The supplied power supply voltage value is the most excessive. As described above, when the operating frequency and power supply voltage value used in the DVFS control are determined by simulation, an appropriate power supply voltage value corresponding to the process variation of each arithmetic processing device cannot be obtained, and wasteful power is consumed. .

また、演算処理装置におけるDVFS制御で用いる動作周波数と電源電圧値の一部を実際に試験を行って測定し、残りを測定結果に基づいて計算等により求める場合について、図14A及び図14Bを参照して説明する。図14A及び図14Bは、実測定に基づく動作周波数に対する電源電圧値の設定例を示す図である。図14A及び図14Bのそれぞれにおいて、横軸が動作周波数であり、縦軸が電圧値である。 14A and 14B, refer to FIGS. 14A and 14B for a case where a part of the operating frequency and power supply voltage value used in the DVFS control in the arithmetic processing unit is actually tested and measured, and the rest is obtained by calculation based on the measurement result. To explain. 14A and 14B are diagrams illustrating setting examples of the power supply voltage value with respect to the operating frequency based on actual measurement. In each of FIG. 14A and FIG. 14B, a horizontal axis is an operating frequency and a vertical axis | shaft is a voltage value.

図14A及び図14Bにおいて、三角で示す印が演算処理装置の実際の性能(動作周波数に対し、正常に動作する電源電圧値)を示している。図14A及び図14Bにおいて、塗りつぶされた三角が実際に試験を行って測定された動作周波数に対する電源電圧値を示し、破線の三角が未測定の動作周波数に対する電源電圧値を示している。また、図14A及び図14Bにおいて、動作周波数に対する電源電圧値V102、V104は、図13A及び図13Bに示した動作周波数に対する電源電圧値V102、V104に対応する。 14A and 14B, the marks indicated by triangles indicate the actual performance (power supply voltage value that operates normally with respect to the operating frequency) of the arithmetic processing unit. 14A and 14B, the filled triangles indicate the power supply voltage values with respect to the operating frequencies actually measured by the test, and the broken triangles indicate the power supply voltage values with respect to the unmeasured operating frequencies. 14A and 14B, power supply voltage values V102 and V104 with respect to the operating frequency correspond to power supply voltage values V102 and V104 with respect to the operating frequency shown in FIGS. 13A and 13B.

図14Aに示すように、例えば、未測定の動作周波数に対する電源電圧値を、測定された動作周波数に対する電源電圧値を用いて直線で補間すると、動作周波数に対する電源電圧値はV201となる。ここで、演算処理装置におけるクリティカルパスは、演算処理装置が有するすべてのパスから決まるため、クリティカルパスの動作周波数と電源電圧の特性は一般に線形にはならない。したがって、未測定の動作周波数に対する電源電圧値を、測定された動作周波数に対する電源電圧値を用いて直線で補間すると、例えば図14Aに示す1401のように、設定する電源電圧値が実際の性能を得るために要求される電源電圧値より低くなってしまうことがある。これによる演算処理装置の誤動作を回避するために、V202として示すように、測定された動作周波数に対する電源電圧にマージンを設定し、それを用いて未測定の動作周波数に対する電源電圧値を求めることが考えられる。しかし、演算処理装置は、このマージンにより無駄な電力を消費することとなる。 As shown in FIG. 14A, for example, when a power supply voltage value for an unmeasured operating frequency is interpolated with a straight line using a power supply voltage value for the measured operating frequency, the power supply voltage value for the operating frequency becomes V201. Here, since the critical path in the arithmetic processing device is determined from all the paths of the arithmetic processing device, the characteristics of the operating frequency and power supply voltage of the critical path are generally not linear. Therefore, when the power supply voltage value for the unmeasured operating frequency is interpolated with a straight line using the power supply voltage value for the measured operating frequency, the power supply voltage value to be set shows the actual performance, for example, 1401 shown in FIG. 14A. It may be lower than the power supply voltage value required for obtaining. In order to avoid the malfunction of the arithmetic processing unit due to this, as shown as V202, a margin is set for the power supply voltage with respect to the measured operating frequency, and the power supply voltage value for the unmeasured operating frequency can be obtained by using a margin. Conceivable. However, the arithmetic processing unit consumes wasted power due to this margin.

また、図14Bに示すように、例えば、未測定の動作周波数に対する電源電圧値として、高い側の動作周波数で測定された電源電圧値を流用すると、演算処理装置の動作は保証される。しかし、例えば図14Bに示す1402、1403などのように、設定する電源電圧値が実際の性能を得るために要求される電源電圧値に対して過剰になり、無駄な電力を消費することとなる。 As shown in FIG. 14B, for example, if the power supply voltage value measured at the higher operating frequency is used as the power supply voltage value for the unmeasured operating frequency, the operation of the arithmetic processing unit is guaranteed. However, for example, 1402 and 1403 shown in FIG. 14B, the power supply voltage value to be set is excessive with respect to the power supply voltage value required for obtaining the actual performance, and wasteful power is consumed. .

また、それぞれの演算処理装置で実際に試験を行い、DVFS制御で用いるすべての動作周波数と電源電圧値を測定することで、個々の演算処理装置について動作周波数に対する適切な電源電圧値を得ることは可能である。しかし、DVFS制御で用いるすべての動作周波数と電源電圧値を実際に試験を行って測定すると、多大な試験時間(コスト)を要してしまう。 In addition, it is possible to obtain an appropriate power supply voltage value with respect to the operating frequency for each arithmetic processing unit by actually testing each arithmetic processing unit and measuring all the operating frequencies and power source voltage values used in the DVFS control. Is possible. However, if all the operating frequencies and power supply voltage values used in DVFS control are actually tested and measured, a great amount of test time (cost) is required.

本発明の目的は、試験時間の増大を抑制し、プロセスばらつきを考慮したDVFS制御を行うことができる演算処理装置及び演算処理装置の制御方法を提供することにある。 An object of the present invention is to provide an arithmetic processing device and a control method for the arithmetic processing device capable of performing DVFS control in consideration of process variation while suppressing an increase in test time.

演算処理装置の一態様は、DVFS制御で用いる複数の動作周波数及び電源電圧値を設定するテーブルと、電源電圧の変化に応じて遅延変化を検出するクリティカルパスモニタ回路と、制御回路とを有する。制御回路は、テーブル内の測定して得られた動作周波数及び電源電圧値でのクリティカルパスモニタ回路のキャリブレーション処理を行い、キャリブレーション処理により得られた電源電圧値に係るキャリブレーション値を参照してテーブル内の測定していない動作周波数に対する電源電圧値の調整をクリティカルパスモニタ回路を用いて行い、調整した電源電圧値を前記テーブルに設定する。 One aspect of the arithmetic processing apparatus includes a table that sets a plurality of operating frequencies and power supply voltage values used in DVFS control, a critical path monitor circuit that detects a delay change according to a change in the power supply voltage, and a control circuit. The control circuit performs calibration processing of the critical path monitor circuit for the measured operating frequency and power supply voltage value obtained in the table, with reference to the calibration value according to the power supply voltage value obtained by the calibration process Then , adjustment of the power supply voltage value for the operating frequency not measured in the table is performed using the critical path monitor circuit, and the adjusted power supply voltage value is set in the table.

DVFS制御で用いる複数の動作周波数及び電源電圧値の一部を試験により測定することで試験時間の増大を抑制することができ、測定された動作周波数及び電源電圧値でのキャリブレーション値を参照しクリティカルパスモニタ回路を用いて、測定していない動作周波数に対する電源電圧値を調整することでプロセスばらつきを考慮した電源電圧値を設定することができる。 By measuring some of the multiple operating frequencies and power supply voltage values used in DVFS control, the increase in test time can be suppressed. Refer to the calibration values at the measured operating frequencies and power supply voltage values. By using the critical path monitor circuit to adjust the power supply voltage value for the operating frequency that is not measured, it is possible to set the power supply voltage value in consideration of process variations.

以下、本発明の実施形態を図面に基づいて説明する。 Hereinafter, embodiments of the present invention will be described with reference to the drawings.

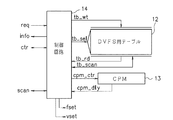

図1は、本発明の実施形態における演算処理装置としてのCPU(Central

Processing Unit)の構成例を示す図である。CPU10は、CPUコア11、DVFS用テーブル12、制御回路14、周波数制御部15、スキャン制御部17、及びメモリ18を有する。FIG. 1 shows a CPU (Central Processing Unit) as an arithmetic processing unit according to an embodiment of the present invention.

It is a figure which shows the structural example of Processing Unit. The

CPUコア11は、電圧制御部19から電源電圧vdd−cが供給され、周波数制御部15から供給されるクロック信号clk−cを動作クロックとして動作し、メモリ18等に格納されているプログラムを読み出して実行する。CPUコア11は、電源電圧vdd−cの変化に応じて遅延変化(ディレイ変化)を検出するクリティカルパスモニタ(CPM:Critical Path Monitor)回路13を有する。

The

DVFS用テーブル12は、CPUコア11に対する動的電圧・周波数制御(DVFS:Dynamic Voltage and Frequency Scaling)で用いる動作周波数と電源電圧値を設定するテーブルである。DVFS用テーブル12には、DVFS制御で用いる複数の動作周波数と電源電圧値の組の情報が格納されている。各組の情報は、DVFS制御で用いる動作周波数、その動作周波数に対する電源電圧値、その電源電圧値の状態を示す情報、CPM回路13のキャリブレーションのグループ及びキャリブレーション値を含む。

The DVFS table 12 is a table for setting an operating frequency and a power supply voltage value used in dynamic voltage and frequency control (DVFS) for the

制御回路14は、CPUコア11に対するDVFS制御に係る各種の制御を行う。制御回路14は、例えば、DVFS用テーブル12の制御や、CPM回路13の制御や、CPUコア11に供給するクロック信号clk−c及び電源電圧vdd−cの設定制御を行う。

The

周波数制御部15は、クロック信号CPU CLKが入力されるとともに、制御回路14からの周波数設定信号fsetが入力される。周波数制御部15は、周波数設定信号fsetに応じて逓倍率(あるいは分周比)を制御して、クロック信号CPU CLKを基に、周波数設定信号fsetに応じた周波数のクロック信号clk−cを生成して出力する。周波数制御部15は、例えばPLL(Phase Locked Loop)回路である。

The

スキャン制御部17は、CPU10におけるスキャン動作を制御する。例えば、スキャン制御部17による制御により、メモリ18から読み出したデータ等(scan dat/ctr)をスキャンシフト動作によってDVFS用テーブル12に書き込むことが可能である。メモリ18は、例えば不揮発性メモリであり、CPU11で実行するプログラムやDVFS用テーブル12の初期設定値が格納されている。

The

電圧制御部19は、供給される電源を基に、制御回路14からの電圧設定信号vsetに応じた電圧値の電源電圧vdd−cを生成して出力する。電圧制御部19は、例えば電圧制御を行うVRM(Voltage Regulator Module)、DC−DCコンバータである。なお、図1において、電圧制御部19は、CPU10の外部に設けているが、CPU10の内部に設けるようにしても良い。

The

また、図1において、信号tb_wtは、DVFS用テーブル12に係るライト制御信号であり、信号tb_selは、DVFS用テーブル12内のデータ(情報)の組を選択する制御信号である。信号tb_rdは、DVFS用テーブル12に係るリード制御信号であり、信号tb_scanは、DVFS用テーブル12に対するスキャン信号である。 In FIG. 1, a signal tb_wt is a write control signal related to the DVFS table 12, and a signal tb_sel is a control signal for selecting a set of data (information) in the DVFS table 12. The signal tb_rd is a read control signal related to the DVFS table 12, and the signal tb_scan is a scan signal for the DVFS table 12.

また、信号reqは、DVFS用テーブル12の設定動作、DVFS用テーブル12内のデータ値による周波数設定及び電圧設定、DVFS用テーブル12の参照を行うための要求信号である。信号infoは、DVFS用テーブル12への設定要求に対する応答信号(設定ステータスやDVFS用テーブル12内のデータ等)である。信号ctrは、制御回路14に対する制御信号である。また、信号cpm_ctrは、CPM回路13を起動及びキャリブレーションする制御信号であり、信号cpm_dlyは、CPM回路13の動作により得られるタイミングマージン情報信号である。信号scanは、スキャンシフト動作によるデータ設定に係る信号である。

The signal req is a request signal for performing the setting operation of the DVFS table 12, the frequency setting and the voltage setting according to the data value in the DVFS table 12, and the reference of the DVFS table 12. The signal info is a response signal to the setting request to the DVFS table 12 (setting status, data in the DVFS table 12, etc.). The signal ctr is a control signal for the

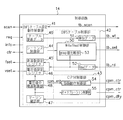

図2は、図1に示したCPU10におけるDVFS用テーブル設定に係る構成例を示す図である。図2において、図1に示した構成要素と同一の機能を有する構成要素には同一の符号を付している。本実施形態においては、DVFS用テーブル12には、起動時の初期値として、一部は実際に試験を行って測定した動作周波数と電源電圧値との組が設定され、残りはシミュレーションにより得られた動作周波数と電源電圧値との組が設定される。そして、CPU10の起動時に、制御回路14は、測定により得られた動作周波数及び電源電圧値を設定してCPM回路13のキャリブレーション処理を行う。制御回路14は、このキャリブレーション処理により得られたキャリブレーション値を、シミュレーションにより得られた(測定していない)動作周波数と電源電圧値との組のキャリブレーション値として流用し、CPM回路13を利用して測定していない動作周波数に対する適切な電源電圧値を求める。

FIG. 2 is a diagram showing a configuration example relating to the DVFS table setting in the

DVFS用テーブル12は、DVFS制御で用いる動作周波数と電源電圧値を設定するテーブルであり、図3に示すように、選択デコーダ21及びレジスタ22〜26を有する複数のレジスタアレイを有する。図3は、本実施形態におけるDVFS用テーブル12の構成例を示す図である。図3において、図1、図2に示した構成要素と同一の機能を有する構成要素には同一の符号を付している。

The DVFS table 12 is a table for setting an operating frequency and a power supply voltage value used in DVFS control, and includes a plurality of register arrays including a

レジスタ22は、DVFS制御で用いる動作周波数を保存するレジスタであり、レジスタ23は、レジスタ22に保存されている動作周波数に対する電源電圧値を保存するレジスタである。レジスタ24は、レジスタ23に保存されている電源電圧値の状態を示すフラグレジスタであり、電源電圧値の状態としては、例えばシミュレーション値、実測値、補正値がある。レジスタ25は、CPM回路13のキャリブレーションのグループを示すレジスタであり、レジスタ26は、CPM回路13のキャリブレーション値を保存するレジスタである。

The

それぞれ1つのレジスタ22〜26を組み合わせて1組のレジスタ群とし、各レジスタ群に、DVFS制御で用いる動作周波数、電源電圧値、電源電圧値の状態、CPM回路13のキャリブレーションのグループ及びキャリブレーション値が格納される。レジスタ群(レジスタ22〜26の組)は、選択デコーダ21による制御信号tb_selに応じた選択によって任意に選択可能である。

Each

また、DVFS用テーブル12内のレジスタ22〜26は、制御回路14からの、ライトデータ/制御に係る信号tb_wt、レジスタの組の選択/制御に係る信号tb_sel、及びリードデータ/制御に係る信号tb_rdによりデータの書き込みや読み出しが可能である。また、DVFS用テーブル12内のレジスタ22〜26は、制御回路14からのスキャン信号/制御に係る信号tb_scanに応じたスキャンシフト動作によってもデータの書き込みや読み出しが可能である。

Further, the

CPM回路13は、電源電圧vdd−cの変化に応じて遅延変化(ディレイ変化)を検出する回路であり、図4に示すように、パルス発生部31、オフセット部32、クリティカルパス部33、論理積(AND)演算部35、変換部36、及びマージン情報信号出力部39を有する。図4は、本実施形態におけるCPM回路13の構成例を示す図である。図4において、図1、図2に示した構成要素と同一の機能を有する構成要素には同一の符号を付している。

The

パルス発生部31は、制御回路14からの信号cpm_ctrに含まれるイネーブル信号enableに基づいて、CPM回路13におけるタイミングマージン観測のためのパルス信号を発生して出力する。オフセット部32は、制御回路14からの信号cpm_ctrに含まれるキャリブレーション信号calibに基づいて、パルス発生部31で発生したパルス信号に時間的なオフセット(遅延)を付加する。クリティカルパス部33の複数のレプリカパス34−1、34−2、…、34−nが有するデバイスは、CPU10内のデバイスも含めてプロセスばらつきの影響を受けるが、オフセット部32でのオフセットの付加によりタイミングマージンの指標を調整することが可能である。

The

クリティカルパス部33は、複数のレプリカパス34−1、34−2、…、34−n(nは2以上の整数)を有し、入力されるパルス信号をそれぞれのレプリカパス34−1、34−2、…、34−nにて伝搬して出力する。レプリカパス34−1、34−2、…、34−nは、回路構成が異なるが、各パスにおける遅延(ディレイ)が合わせられている。

The

AND演算部35は、クリティカルパス部33の複数のレプリカパス34−1、34−2、…、34−nからの出力を論理積演算し、演算結果を出力する。すなわち、AND演算部35は、レプリカパス34−1、34−2、…、34−nのすべてから、伝搬されたパルス信号が出力されたことを検出すると、出力をアサートする。つまり、AND演算部35は、複数のレプリカパス34−1、34−2、…、34−nの内のワーストパスでの遅延を検出する。

The AND

変換部36は、複数の遅延回路37−1、37−2、…、及び複数のフリップフロップ38−1、38−2、…38−m(mは2以上の整数)を有する。遅延回路37−1、37−2、…は、縦属接続(カスケード接続)されている。AND演算部35の出力が、初段の遅延回路37−1及びフリップフロップ38−1に入力される。また、遅延回路37−(i−1)(i=2〜mの整数)の出力が、遅延回路37−i及びフリップフロップ38−iに入力される。フリップフロップ38−1、38−2、…38−mのそれぞれは、入力を同期して取り込んで出力する。したがって、フリップフロップ38−1、38−2、…38−mの出力値が変化しているエッジを検出することで、タイミングマージンが観測可能である。マージン情報信号出力部39は、変換部36の複数のフリップフロップ38−1、38−2、…38−mに基づいて、マージン情報信号cpm_dlyを生成し出力する。

The

制御回路14は、DVFS制御に係る各種の制御を行う回路であり、図5に示すように、DVFSテーブル設定動作制御部41、DVFSテーブル制御部42、及びCPM制御部43を有する。図5は、本実施形態における制御回路14の構成例を示す図である。図5において、図1、図2に示した構成要素と同一の機能を有する構成要素には同一の符号を付している。

The

DVFSテーブル設定動作制御部41は、DVFS用テーブル12の設定に係る動作を制御する。DVFSテーブル設定動作制御部41は、シーケンス制御部44、周波数設定レジスタ45、電圧値設定レジスタ46、マージン確認部47、電圧値の増減制御部48、及びテーブル更新データ生成部49を有する。シーケンス制御部44は、DVFS用テーブル12の設定におけるCPM回路13のキャリブレーション動作やCPM回路13を利用した電源電圧値の設定動作を制御する。

The DVFS table setting

周波数設定レジスタ45は、DVFS制御での装置の動作周波数の設定値を示すレジスタである。周波数設定レジスタ45は、DVFSテーブル制御部42を介してDVFS用テーブル12から読み出された動作周波数の設定値が設定され、設定値に応じた周波数設定信号fsetを出力する。

The

電圧値設定レジスタ46は、DVFS制御での装置の電源電圧の設定値を示すレジスタである。電圧値設定レジスタ46は、DVFSテーブル制御部42を介してDVFS用テーブル12から読み出された電源電圧の設定値、又はCPM回路13からのタイミングマージン情報信号cpm_dlyにより決まる電源電圧の設定値が設定され、設定値に応じた電圧設定信号vsetを出力する。

The voltage

マージン確認部47は、CPM回路13からのタイミングマージン情報信号cpm_dlyに基づいて、DVFS制御時におけるマージンを判断する。マージン確認部47は、CPM回路13のキャリブレーション動作時には、タイミングマージン情報信号cpm_dlyに基づいてCPM回路13のキャリブレーションを行うか否かを判断する。また、マージン確認部47は、CPM回路13を利用した電源電圧値の調整時には、タイミングマージン情報信号cpm_dly及び許容値から電圧値のマージンを判断する。

The

電圧値の増減制御部48は、CPM回路13を利用した電源電圧値の調整時に、マージン確認部47の判断結果に基づいて電源電圧の設定値に対する増減制御を行う。テーブル更新データ生成部49は、CPM回路13のキャリブレーション動作やCPM回路13を利用した電源電圧値の設定動作において、DVFS用テーブル12に書き込む更新データを生成する。テーブル更新データ生成部49は、例えば電源電圧値、電源電圧値の状態、キャリブレーション値を生成する。

The voltage value increase /

DVFSテーブル制御部42は、DVFS用テーブル12に対するデータの書き込み及び読み出しを制御する。DVFSテーブル制御部42は、ライト/リード制御部50、及びレジスタ51、52を有する。ライト/リード制御部50は、DVFSテーブル設定動作制御部41からの信号に基づいて、データの書き込み及び読み出しを行うDVFS用テーブル12のデータの組を選択するための信号tb_selを生成して出力する。レジスタ51は、DVFS用テーブル12への書き込みデータを保持するレジスタであり、レジスタ52は、DVFS用テーブル12からの読み出しデータを保持するレジスタである。

The DVFS

CPM制御部43は、CPM回路13の動作を制御する。CPM制御部43は、回路動作制御部54及びキャリブレーション制御部55を有する。回路動作制御部54は、DVFSテーブル設定動作制御部41からの起動信号cpm_enbに応じて、CPM回路13の起動を制御する。キャリブレーション制御部55は、DVFSテーブル設定動作制御部41のマージン確認部47の出力に応じて、CPM回路13のキャリブレーション値を生成して出力する。

The

次に、本実施形態におけるDVFS用テーブルの設定に係る動作について説明する。図6は、本実施形態におけるDVFS用テーブルの設定の動作例を示すフローチャートである。なお、図6に示す各処理は、試験時にステップS101の処理が行われ、その後の装置の起動時にステップS102及びS103の処理が行われる。 Next, an operation related to the setting of the DVFS table in the present embodiment will be described. FIG. 6 is a flowchart showing an operation example of setting the DVFS table in the present embodiment. In addition, each process shown in FIG. 6 performs the process of step S101 at the time of a test, and performs the process of step S102 and S103 at the time of starting of an apparatus after that.

まず、試験装置により実際に動作させる試験を演算処理装置としてのCPU10で行い、DVFS制御での動作周波数に対して、正常に動作する電源電圧値を測定により求める(S101)。このステップS101における試験による電源電圧値の実測は、DVFS制御において制御し得るすべての動作周波数に対しては行わずに、一部の動作周波数に対して行う。このように、すべての動作周波数に対して試験を行うのではなく、一部の動作周波数に対して試験を行うことで、試験時間の増大を抑制することができる。ここで、試験を行うことによって測定された動作周波数に対する電源電圧値は、測定対象となったCPU10と関連付けて、任意の記憶装置等に保存しておく。

First, a test that is actually operated by the test apparatus is performed by the

次に、CPU10の起動時に、制御回路14は、ステップS101において測定された動作周波数及び電源電圧値(実測値)を設定して、CPM回路13のキャリブレーション処理を行う(S102)。このステップS102におけるCPM回路13のキャリブレーション処理により、測定された動作周波数及び電源電圧値の組に対するCPM回路13のキャリブレーション値が得られる。制御回路14は、得られたCPM回路13のキャリブレーション値をDVFS用テーブル12に書き込む。また、CPM回路13のキャリブレーション値は、同じキャリブレーションのグループの測定していない動作周波数及び電源電圧値の組に対しても流用するので、制御回路14は、DVFS用テーブル12における同じグループの測定していない動作周波数及び電源電圧値の組に対してもキャリブレーション値を書き込む。

Next, when the

次に、制御回路14は、測定していない動作周波数及び電源電圧値(シミュレーション値)を設定して、CPM回路13を利用し、その動作周波数に対して正常に動作する電源電圧値を求める(S103)。制御回路14は、ステップS102において得られたキャリブレーション値でキャリブレーションされたCPM回路13からのタイミングマージン情報に基づき、動作周波数に対する電源電圧値の最適化を行う。このように、実測値によりキャリブレーションされたCPM回路13を用いて動作周波数に対する電源電圧値を求めることで、対象のCPU10におけるプロセスばらつきを考慮した電源電圧値を得ることができる。そして、制御回路14は、得られた電源電圧値等をDVFS用テーブル12に書き込む。以上のようにして、DVFS制御での動作周波数に対する電源電圧値の設定を行う。

Next, the

以下、前述したステップS101〜S103での動作を詳細に説明する。

図7は、図6に示したステップS101での動作例を示すフローチャートである。試験装置を用いて、DVFS制御で用いる動作周波数の一部について、シミュレーションにより見積もった動作周波数及び電源電圧値で、演算処理装置としてのCPU10の試験を開始する(S201)。そして、試験装置で電源電圧値を変えながら試験を行うことで、動作周波数に対し、正常に動作する電源電圧値をマージンも含めて測定する(S202)。次に、DVFS用テーブル12の設定データとして使用するために、試験で測定された動作周波数に対する電源電圧値を、測定対象となったCPU10と関連付けて、任意の記憶装置等に保存する(S203)。これにより、DVFS制御で用いる動作周波数の一部について、マージンも含めた電源電圧値が測定により求まる。Hereinafter, the operation in steps S101 to S103 described above will be described in detail.

FIG. 7 is a flowchart showing an operation example in step S101 shown in FIG. Using the test apparatus, a test of the

図8は、図6に示したステップS102及びS103での動作例を示すフローチャートである。図8において、ステップS301〜S307が、図6に示したステップS102での動作に対応し、ステップS308〜S314が、図6に示したステップS103での動作に対応する。 FIG. 8 is a flowchart showing an operation example in steps S102 and S103 shown in FIG. 8, steps S301 to S307 correspond to the operation in step S102 shown in FIG. 6, and steps S308 to S314 correspond to the operation in step S103 shown in FIG.

まず、CPU10の起動時に、制御回路14のDVFSテーブル設定動作制御部41は、信号scan、ctrに応じてスキャンシフト動作を行い、信号tb_scanを介して、DVFS用テーブル12にデータを設定する(S301)。DVFS用テーブル12に設定するデータには、DVFS制御で用いる動作周波数、電源電圧値(シミュレーション値、実測値)、電源電圧値の状態、CPM回路13のキャリブレーションのグループ、キャリブレーション値(初期値は不定)が含まれる。

First, when the

次に、DVFSテーブル設定動作制御部41のシーケンス制御部44は、DVFSテーブル制御部42を介してDVFS用テーブル12のデータを読み出し、テーブル12内の情報を確認する(S302)。シーケンス制御部44は、読み出したデータの電源電圧値の状態を示すフラグを確認した結果、電源電圧値が実測値であれば、DVFS用テーブル12から読み出したデータの動作周波数及び電源電圧値(実測値)を周波数設定レジスタ45及び電圧値設定レジスタ46に設定する(S303)。DVFSテーブル設定動作制御部41は、信号ctrを用いて、CPUコア11に供給されるクロック信号clk−c及び電源電圧vdd−cの設定、及び正しく設定されたことの確認を行う。

Next, the

そして、CPM制御部43は、信号cpm_ctrを介してCPM回路13のキャリブレーションを行う。CPM制御部43は、例えば図9に示すようにCPM回路13の変換部36の出力値が変化しているエッジが中央になるように、CPM回路13のキャリブレーション値を変更する(S304)。

Then, the

CPM回路13のキャリブレーションが完了すると、DVFSテーブル設定動作制御部41は、得られたキャリブレーション値を、DVFSテーブル制御部42を介してDVFS用テーブル12に書き込む(S305)。このとき、DVFSテーブル設定動作制御部41は、処理対象の実測値の動作周波数及び電源電圧値の組に加え、同じキャリブレーションのグループの動作周波数及び電源電圧値の組に対しても、同じキャリブレーション値を書き込む。また、DVFSテーブル設定動作制御部41は、処理対象の実測値の動作周波数及び電源電圧値の組における電源電圧値の状態を示すフラグをキャリブレーション済に設定する(S306)。

When the calibration of the

続いて、シーケンス制御部44は、CPM回路13のキャリブレーションが必要な実測値の動作周波数及び電源電圧値の組がDVFS用テーブル12にあるか否かを判断する(S307)。シーケンス制御部44は、DVFS用テーブル12から読み出したデータを基に、CPM回路13のキャリブレーションを行っていない、すなわち電源電圧値の状態を示すフラグがキャリブレーション済となっていない実測値の動作周波数及び電源電圧値の組があるか否かを判断する。

Subsequently, the

判断の結果、CPM回路13のキャリブレーションが必要な実測値の動作周波数及び電源電圧値の組がある場合にはステップS303に戻って前述した動作を行う。一方、CPM回路13のキャリブレーションが必要な実測値の動作周波数及び電源電圧値の組がない場合には、ステップS308に進む。このようにして、CPM回路13のキャリブレーションを、DVFS用テーブル12の動作周波数及び電源電圧値の各組について電源電圧値の状態を示すフラグを確認しながら行うことで、DVFS用テーブル12の動作周波数及び電源電圧値のすべての組についてCPM回路13のキャリブレーション値を設定することが可能である。

As a result of the determination, when there is a set of the actual operation frequency and the power supply voltage value that require calibration of the

次に、シーケンス制御部44は、DVFSテーブル制御部42を介してDVFS用テーブル12のデータを読み出し、読み出したデータの電源電圧値の状態を示すフラグを確認する(S308)。そして、シーケンス制御部44は、DVFS用テーブル12に、電源電圧値の状態を示すフラグがキャリブレーション済となっていないシミュレーション値の動作周波数及び電源電圧値の組があるか否かを判断する(S309)。

Next, the

シーケンス制御部44は、読み出したデータの電源電圧値の状態を示すフラグが、キャリブレーション済でないシミュレーション値であれば、その動作周波数及び電源電圧値(シミュレーション値)を周波数設定レジスタ45及び電圧値設定レジスタ46に設定する(S310)。DVFSテーブル設定動作制御部41は、信号ctrを用いて、CPUコア11に供給されるクロック信号clk−c及び電源電圧vdd−cの設定、及び正しく設定されたことの確認を行う。

If the flag indicating the state of the power supply voltage value of the read data is a simulation value that has not been calibrated, the

そして、CPM制御部43は、信号cpm_ctrを介してCPM回路13を動作させる。このとき、DVFS用テーブル12に設定済みのCPM回路13のキャリブレーション値が適用される。DVFSテーブル設定動作制御部41のマージン確認部47は、信号cpm_dlyにより設定した動作周波数に対するタイミングマージンを確認する(S311)。

Then, the

次に、DVFSテーブル設定動作制御部41は、電源電圧値のキャリブレーションが必要であるか否かを判断する(S312)。DVFSテーブル設定動作制御部41は、確認されたタイミングマージンが予め定めた許容値を超えると電源電圧値のキャリブレーションが必要であると判断し、超えていなければ電源電圧値のキャリブレーションが必要ないと判断する。

Next, the DVFS table setting

判断の結果、電源電圧値のキャリブレーションが必要である場合には、DVFSテーブル設定動作制御部41の電圧値の増減制御部48は、タイミングマージンが許容値以上であれば電源電圧値を下げ、タイミングマージンが許容値以下であれば電源電圧値を上げて、電圧値設定レジスタ46に設定する。そして、タイミングマージンを再度確認することで、DVFSテーブル設定動作制御部41は、設定した動作周波数に対する電源電圧値の調整を行う(S313)。例えば図9に示すようにCPM回路13の変換部36の出力値が変化しているエッジが中央になるように、電源電圧値を変更する。

If the power supply voltage value needs to be calibrated as a result of the determination, the voltage value increase /

そして、許容値内にタイミングマージンが入ると、DVFSテーブル設定動作制御部41は、DVFSテーブル制御部42を介してDVFS用テーブル12に、電圧値設定レジスタ46に設定されている電源電圧値を書き込むとともに、その電源電圧値の状態を示すフラグをキャリブレーション済に設定する(S314)。

When the timing margin falls within the allowable value, the DVFS table setting

このようにして、電源電圧値の状態を示すフラグがキャリブレーション済となっていないシミュレーション値の動作周波数及び電源電圧値の組がなくなるまで繰り返して、電源電圧値の調整を行い、DVFS用テーブル12内のすべての組について動作周波数及び電源電圧値を設定する。そして、設定が完了すると、DVFSテーブル設定動作制御部41は、信号infoによりDVFS用テーブル12のデータが確定されたことをCPUコア11に通知する。

In this manner, the power supply voltage value is adjusted repeatedly until there is no longer the combination of the operating frequency and the power supply voltage value of the simulation value for which the flag indicating the state of the power supply voltage value has not been calibrated, and the DVFS table 12 The operating frequency and power supply voltage value are set for all of the sets. When the setting is completed, the DVFS table setting

なお、電源電圧値を調整する際に、電源電圧値を変化させてもタイミングマージンが許容値に入らない場合には、DVFSテーブル設定動作制御部41が、信号infoによりDVFS用テーブル12の設定動作において不具合が発生したことをCPUコア11に通知するようにしても良い。また、この設定されたDVFS用テーブル12のデータを、不揮発性の記憶装置等に保持しておくことで、再度起動する際にCPM回路13のキャリブレーションやCPM回路13を利用した電源電圧値の調整に係る動作を省くことが可能である。

When adjusting the power supply voltage value, if the timing margin does not fall within the allowable value even if the power supply voltage value is changed, the DVFS table setting

図10A〜図10Eは、前述したDVFS用テーブルの設定に係る動作によるDVFS用テーブル12のデータ変化の例を示す図である。DVFS用テーブル12には、インデックスind(indは0、1、2、…、Mid−x、…、Mid、…、Max−2、Max−1、Max)の各タップについての、動作周波数Find、電源電圧値Vind_sim、Vind_tst、又はVind_cpm、電源電圧値の状態、CPM回路13のキャリブレーションのグループ、キャリブレーション値が格納されている。

FIG. 10A to FIG. 10E are diagrams showing examples of data changes in the DVFS table 12 due to operations related to the setting of the DVFS table described above. In the DVFS table 12, the operating frequency Find, for each tap of the index ind (ind is 0, 1, 2, ..., Mid-x, ..., Mid, ..., Max-2, Max-1, Max). The power supply voltage value Vind_sim, Vind_tst, or Vind_cpm, the state of the power supply voltage value, the calibration group of the

なお、図10A〜図10Eにおいて、電源電圧値は、シミュレーション値をVind_simで示し、実測値をVind_tstで示し、CPM回路13を利用して得られた補正値をVind_cpmで示す。また、図10A〜図10Eに示す例において、CPM回路13のキャリブレーションのグループは、インデックスindが0〜2の設定値は第0グループに属し、インデックスindがMid−x〜Midの設定値は第2グループに属し、インデックスindがMax−2〜Midの設定値は第3グループに属するものとする。

10A to 10E, the power supply voltage value is indicated by Vind_sim, a simulation value is indicated by Vind_tst, and a correction value obtained by using the

実際に試験を行って実測値を測定する前は、図10Aに示すように、動作周波数Findに対する電源電圧値は、すべてシミュレーション値であるVind_simとなっており、電源電圧値の状態を示すフラグは、シミュレーション値であることを示す“00”となっている。実際に試験を行って実測値を測定すると、図10Bに示すように、測定を行った動作周波数F0、Fmid、Fmaxのそれぞれに対する電源電圧値が、実測値であるV0_tst、Vmid_tst、Vmax_tstとなり、さらに図10Cに示すように、電源電圧値の状態を示すフラグが、実測値であることを示す“10”となる。 Before actually measuring and measuring the actual value, as shown in FIG. 10A, all the power supply voltage values for the operating frequency Find are Vind_sim, which is a simulation value, and the flag indicating the state of the power supply voltage value is “00” indicating the simulation value. When actually measured and measured values are measured, as shown in FIG. 10B, power supply voltage values for the measured operating frequencies F0, Fmid, and Fmax are measured values V0_tst, Vmid_tst, and Vmax_tst, respectively. As shown in FIG. 10C, the flag indicating the state of the power supply voltage value is “10” indicating the actual measurement value.

続いて、実測された動作周波数及び電源電圧値を用いて、装置の起動時にCPM回路13のキャリブレーションを行うと、図10Dに示すように、キャリブレーションを行った電源電圧値の状態を示すフラグが、キャリブレーション済であることを示す“11”となる。また、同じキャリブレーションのグループに同じキャリブレーション値が書き込まれる。例えば、実測した動作周波数F0及び電源電圧値V0_tstに設定して行ったCPM回路13のキャリブレーションにより得られたキャリブレーション値“zzzzzzz”が第0グループのキャリブレーション値とされる。また、実測した動作周波数Fmid及び電源電圧値Vmid_tstに設定して得られたキャリブレーション値“yyyyyyy”が第2グループのキャリブレーション値とされ、実測した動作周波数Fmax及び電源電圧値Vmax_tstに設定して得られたキャリブレーション値“xxxxxxx”が第3グループのキャリブレーション値とされる。

Subsequently, when the

そして、測定していない、シミュレーション値の動作周波数及び電源電圧値の組に対してCPM回路13を利用した電源電圧値の調整を行うと、図10Eに示すように、電源電圧値の調整を行った動作周波数F1、F2、Fmid-x、Fmax-2、Fmax-1等に対する電源電圧値が、補正値であるV1_cpm、V2_cpm、Vmid-x_cpm、Vmax-2_cpm、Vmax-1_cpmとなり、電源電圧値の状態を示すフラグが、補正値(キャリブレーション済)であることを示す“01”となる。

Then, when the power supply voltage value is adjusted using the

本実施形態によれば、DVFS用テーブル12に、電源電圧値の状態を示す情報、及びCPM回路13のキャリブレーションに係る情報を設定する。そして、DVFS制御で用いる複数の動作周波数及び電源電圧値の一部について、実際の試験を行って動作周波数に対する電源電圧値を測定し、測定していない動作周波数に対する電源電圧値は、起動時に処理することで、試験時間の増大を抑制することが可能になる。また、図15に示すように、測定していない動作周波数に対する電源電圧値は、測定された動作周波数及び電源電圧値によりキャリブレーションされたCPM回路13を利用して調整することで、プロセスばらつきに応じて最適化された電源電圧値を設定することが可能になり、電力性能を向上させることが可能となる。

According to the present embodiment, information indicating the state of the power supply voltage value and information related to calibration of the

図15は、本実施形態における動作周波数に対する電源電圧値の設定例を示す図である。図15において、横軸が動作周波数であり、縦軸が電圧値である。また、図15において、動作周波数に対する電源電圧値V102、V104は、図13A及び図13Bに示した動作周波数に対する電源電圧値V102、V104に対応する。図15において、Cal0、Cal3、Cal5は、実際に試験を行って測定された動作周波数F0、F3、F5に対する電源電圧値でCPM回路13をキャリブレーションして得られたキャリブレーション値である。また、四角で示す印は、CPM回路13のキャリブレーション前におけるCPM回路13の出力におけるエッジが中央となる電源電圧値を示す。

FIG. 15 is a diagram illustrating a setting example of the power supply voltage value with respect to the operating frequency in the present embodiment. In FIG. 15, the horizontal axis is the operating frequency, and the vertical axis is the voltage value. In FIG. 15, power supply voltage values V102 and V104 with respect to the operating frequency correspond to power supply voltage values V102 and V104 with respect to the operating frequency shown in FIGS. 13A and 13B. In FIG. 15, Cal0, Cal3, and Cal5 are calibration values obtained by calibrating the

なお、前述した説明では、DVFS用テーブル12の設定に係る動作は、制御回路14が制御して行うようにしているが、これに限定されるものではない。制御回路14内で値を保持するレジスタを配置し、設定に係る動作の制御は、CPUコア11がメモリ18等から読み出したプログラムを実行することで制御を行うようにしても良い。

In the above description, the operation related to the setting of the DVFS table 12 is controlled by the

なお、前述した実施形態では、演算処理装置としてのCPU10において、1つのCPM回路13を配置する例を示したが、図11に示すように複数のCPM回路13を配置するようにしても良い。例えば、複数のCPUコア11を搭載し、複数のCPUコア11共通でDVFS制御を行う場合などが考えられる。図11は、本実施形態における演算処理装置の他の構成例を示す図である。図11には、DVFS用テーブル設定に係る構成例を図示している。図11において、図1〜図5に示した構成要素と同一の機能を有する構成要素には同一の符号を付している。

In the above-described embodiment, an example in which one

図11に示す例では、複数のCPM回路13−1、13−2、13−3、…を有するが、DVFS用テーブル12は1つとしている。そのため、CPM制御部43にワーストパス検出部56を設け、ワーストパス検出部56が、複数のCPM回路13−1、13−2、13−3、…の内から最もタイミングマージンが劣るタイミングマージン情報、すなわちワーストパスのタイミングマージン情報を検出してマージン確認部47に出力する。これにより、前述した実施形態と同様にDVFS用テーブル12の設定を行うことが可能である。

In the example shown in FIG. 11, a plurality of CPM circuits 13-1, 13-2, 13-3,. Therefore, the worst

また、図12に示すように、DVFS用テーブル12、CPM回路13、及び制御回路14の組を複数配置するようにしても良い。例えば、複数のCPUコア11を搭載し、CPUコア11毎にDVFS制御を行う場合などが考えられる。図12は、本実施形態における演算処理装置の他の構成例を示す図である。図12には、DVFS用テーブル設定に係る構成例を図示している。図12において、図1〜図5に示した構成要素と同一の機能を有する構成要素には同一の符号を付している。

Further, as shown in FIG. 12, a plurality of sets of the DVFS table 12, the

図12に示した例では、DVFS用テーブル12−1、CPM回路13−1、及び制御回路14−1を組とし、DVFS用テーブル12−2、CPM回路13−2、及び制御回路14−2を組とし、DVFS用テーブル12−3、CPM回路13−3、及び制御回路14−3を組として、それぞれの組で前述したDVFS用テーブルの設定の動作を独立して行えば良い。 In the example shown in FIG. 12, the DVFS table 12-1, the CPM circuit 13-1, and the control circuit 14-1 are paired, and the DVFS table 12-2, the CPM circuit 13-2, and the control circuit 14-2 are combined. The DVFS table 12-3, the CPM circuit 13-3, and the control circuit 14-3 may be used as a set, and the DVFS table setting operation described above may be performed independently for each set.

なお、本実施形態は、例えばCPU(又はMPU)及びメモリ等を有する演算処理装置が、メモリ等に記憶されたプログラムを実行することで実現でき、前記プログラムは本発明の実施形態に含まれる。また、前記プログラムを記録した記録媒体は本発明の実施形態に含まれる。前記プログラムを記録する記録媒体としては、例えばCD−ROM、フレキシブルディスク、ハードディスク、磁気テープ、光磁気ディスク、不揮発性メモリカード等を用いることができる。 Note that this embodiment can be realized by, for example, an arithmetic processing device having a CPU (or MPU) and a memory executing a program stored in the memory or the like, and the program is included in the embodiment of the present invention. A recording medium on which the program is recorded is included in an embodiment of the present invention. As a recording medium for recording the program, for example, a CD-ROM, a flexible disk, a hard disk, a magnetic tape, a magneto-optical disk, a nonvolatile memory card, or the like can be used.

また、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。 In addition, each of the above-described embodiments is merely an example of implementation in carrying out the present invention, and the technical scope of the present invention should not be construed as being limited thereto. That is, the present invention can be implemented in various forms without departing from the technical idea or the main features thereof.

DVFS制御を行う演算処理装置にて、DVFS制御で用いる動作周波数及び電源電圧値を測定するための試験時間の増大を抑制することが可能になり、またプロセスばらつきに応じた最適な電源電圧値を設定してDVFS制御を行うことが可能になる。 In an arithmetic processing unit that performs DVFS control, it is possible to suppress an increase in test time for measuring the operating frequency and power supply voltage value used in DVFS control, and an optimum power supply voltage value corresponding to process variations can be set. This makes it possible to perform DVFS control.

Claims (9)

電源電圧の変化に応じて遅延変化を検出するクリティカルパスモニタ回路と、

前記テーブル内の測定して得られた前記動作周波数及び前記電源電圧値での前記クリティカルパスモニタ回路のキャリブレーション処理を行い、前記キャリブレーション処理により得られた電源電圧値に係るキャリブレーション値を参照して前記テーブル内の測定していない前記動作周波数に対する前記電源電圧値の調整を前記クリティカルパスモニタ回路を用いて行い、調整した前記電源電圧値を前記テーブルに設定する制御回路とを有することを特徴とする演算処理装置。 A table for setting a plurality of operating frequencies used in dynamic voltage / frequency control and power supply voltage values for the operating frequencies;

A critical path monitor circuit that detects a delay change according to a change in the power supply voltage;

Referring to the performed calibration processing of the critical path monitor circuit, a calibration value according to the power supply voltage value obtained by the calibration process in the measurement above the operating frequency and the power supply voltage value obtained in said table And adjusting the power supply voltage value with respect to the operating frequency not measured in the table using the critical path monitor circuit, and a control circuit for setting the adjusted power supply voltage value in the table. Arithmetic processing device characterized.

前記制御回路は、測定していない前記動作周波数に対する前記電源電圧値の調整を、グループ内の測定して得られた前記動作周波数及び前記電源電圧値での前記キャリブレーション処理により得られた電源電圧値に係るキャリブレーション値を参照して行うことを特徴とする請求項1記載の演算処理装置。 A plurality of groups including both the power supply voltage value for the operating frequency obtained by measuring the operating frequency and the power supply voltage value in the table, respectively, and the power supply voltage value for the operating frequency not measured; Divided into

The control circuit adjusts the power supply voltage value with respect to the operating frequency that has not been measured, the power supply voltage obtained by the calibration processing at the operating frequency and the power supply voltage value obtained by measuring within the group The arithmetic processing device according to claim 1, wherein the calculation processing device is performed with reference to a calibration value related to the value .

前記テーブル内の測定して得られた前記動作周波数及び前記電源電圧値に設定したときの前記クリティカルパスモニタ回路での遅延に応じたマージン情報に基づいて前記動作周波数に対するタイミングマージンが許容値を超えているか否かを判断する判断部と、

前記判断部での判断結果に基づいて前記クリティカルパスモニタ回路のキャリブレーション処理を行うキャリブレーション制御部とを有することを特徴とする請求項1記載の演算処理装置。 The control circuit includes:

A timing margin for the operating frequency exceeds an allowable value based on margin information corresponding to a delay in the critical path monitor circuit when the operating frequency obtained by measurement in the table and the power supply voltage value are set. A determination unit for determining whether or not

The arithmetic processing apparatus according to claim 1, further comprising: a calibration control unit that performs calibration processing of the critical path monitor circuit based on a determination result in the determination unit.

前記テーブル内の測定していない前記動作周波数及び前記電源電圧値に設定したときの前記クリティカルパスモニタ回路での遅延に応じたマージン情報に基づいて前記動作周波数に対するタイミングマージンが許容値を超えているか否かを判断する判断部と、

前記判断部での判断結果に基づいて前記動作周波数に対する前記電源電圧値の増減を制御する増減制御部とを有することを特徴とする請求項1記載の演算処理装置。 The control circuit includes:

Whether the timing margin for the operating frequency exceeds an allowable value based on margin information corresponding to a delay in the critical path monitor circuit when the operating frequency and the power supply voltage value not measured in the table are set A determination unit for determining whether or not ,

The arithmetic processing apparatus according to claim 1, further comprising: an increase / decrease control unit that controls increase / decrease of the power supply voltage value with respect to the operating frequency based on a determination result of the determination unit.

前記クリティカルパスモニタ回路での遅延に応じたマージン情報に基づいて前記動作周波数に対するタイミングマージンが許容値を超えているか否かを判断する判断部と、

前記テーブル内の測定して得られた前記動作周波数及び前記電源電圧値に設定したときの前記判断部での判断結果に基づいて前記クリティカルパスモニタ回路のキャリブレーション処理を行うキャリブレーション制御部と、

前記テーブル内の測定していない前記動作周波数及び前記電源電圧値に設定したときの前記判断部での判断結果に基づいて前記動作周波数に対する前記電源電圧値の増減を制御する増減制御部とを有することを特徴とする請求項1記載の演算処理装置。 The control circuit includes:

A determination unit that determines whether a timing margin for the operating frequency exceeds an allowable value based on margin information according to a delay in the critical path monitor circuit;

A calibration control unit that performs calibration processing of the critical path monitor circuit based on a determination result in the determination unit when the operating frequency and the power supply voltage value obtained by measurement in the table are set;

An increase / decrease control unit that controls increase / decrease of the power supply voltage value with respect to the operating frequency based on a determination result of the determination unit when the operating frequency and the power supply voltage value that are not measured in the table are set. The arithmetic processing apparatus according to claim 1.

前記制御回路は、複数の前記クリティカルパスモニタ回路の内の1つの前記クリティカルパスモニタ回路を用いて、前記キャリブレーション処理及び前記電源電圧値の調整を行うことを特徴とする請求項1記載の演算処理装置。 A plurality of critical path monitor circuits;

2. The calculation according to claim 1, wherein the control circuit performs the calibration process and the adjustment of the power supply voltage value by using one critical path monitor circuit among the plurality of critical path monitor circuits. Processing equipment.

前記テーブル内の測定して得られた前記動作周波数及び前記電源電圧値での前記クリティカルパスモニタ回路のキャリブレーション処理を行い、

前記キャリブレーション処理により得られた電源電圧値に係るキャリブレーション値を参照して前記テーブル内の測定していない前記動作周波数に対する前記電源電圧値の調整を前記クリティカルパスモニタ回路を用いて行い、

調整された前記電源電圧値を前記テーブルに設定することを特徴とする演算処理装置の制御方法。 Control of an arithmetic processing unit having a table for setting a plurality of operating frequencies used in dynamic voltage / frequency control and a power supply voltage value for the operating frequency, and a critical path monitor circuit for detecting a delay change according to the change of the power supply voltage A method,

Performing calibration processing of the critical path monitor circuit at the operating frequency and the power supply voltage value obtained by measurement in the table,

To adjust the power supply voltage for the measured non the operating frequency in the calibration the table refers to the calibration value according to the power supply voltage value obtained by processing using the critical path monitor circuit,

A control method for an arithmetic processing unit, wherein the adjusted power supply voltage value is set in the table.

前記テーブル内の測定して得られた前記動作周波数及び前記電源電圧値での前記クリティカルパスモニタ回路のキャリブレーション処理を実行させ、前記クリティカルパスモニタ回路の出力に基づいて電源電圧値に係るキャリブレーション値を求める処理と、

前記キャリブレーション処理により得られた電源電圧値に係るキャリブレーション値を適用して前記テーブル内の測定していない前記動作周波数及び前記電源電圧値で前記クリティカルパスモニタ回路を動作させ、前記クリティカルパスモニタ回路の出力に基づいて前記動作周波数に対する前記電源電圧値を調整する処理と、

調整された前記電源電圧値を前記テーブルに設定する処理とを実行させるためのプログラム。 In a processing unit having a table for setting a plurality of operating frequencies used in dynamic voltage / frequency control and a power supply voltage value for the operating frequency, and a critical path monitor circuit for detecting a delay change according to a change in the power supply voltage,

Calibration is performed on the power supply voltage value based on the output of the critical path monitor circuit by executing calibration processing of the critical path monitor circuit at the operating frequency and the power supply voltage value obtained by measurement in the table . Processing to find a value ;

Wherein by applying a calibration value according to the power supply voltage value obtained by the calibration process is operated the critical path monitor circuit in measured non wherein the operating frequency and the power supply voltage value in the table, the critical path monitor a process for adjusting the power supply voltage value for the operating frequency based on the output of the circuit,

A program for executing the process of setting the adjusted power supply voltage value in the table.

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2013/069604 WO2015008372A1 (en) | 2013-07-19 | 2013-07-19 | Arithmetic processing device and control method for arithmetic processing device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2015008372A1 JPWO2015008372A1 (en) | 2017-03-02 |

| JP6090447B2 true JP6090447B2 (en) | 2017-03-08 |

Family

ID=52345865

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015527120A Expired - Fee Related JP6090447B2 (en) | 2013-07-19 | 2013-07-19 | Arithmetic processing device and control method of arithmetic processing device |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP6090447B2 (en) |

| WO (1) | WO2015008372A1 (en) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6859695B2 (en) | 2016-12-19 | 2021-04-14 | 富士通株式会社 | Information processing equipment, information processing methods and information processing programs |

| CN114546090B (en) * | 2022-02-21 | 2024-09-20 | 上海壁仞科技股份有限公司 | Adaptive voltage frequency adjustment method and device |

| CN115328248B (en) * | 2022-08-17 | 2024-08-06 | 上海燧原科技股份有限公司 | Voltage self-adaptive adjusting method and device of integrated circuit and electronic equipment |

| CN117555738B (en) * | 2024-01-09 | 2024-04-05 | 悦芯科技股份有限公司 | DPS power supply board for memory FT test |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002359289A (en) * | 2001-03-29 | 2002-12-13 | Mitsubishi Electric Corp | Semiconductor device equipped with process monitor circuit, and testing method and manufacturing method therefor |

| JP2004070805A (en) * | 2002-08-08 | 2004-03-04 | Fujitsu Ltd | Semiconductor integrated circuit with controlled internal power source voltage |

| JP2008098322A (en) * | 2006-10-11 | 2008-04-24 | Nec Corp | Optimum control system, lsi optimum control circuit, and lsi optimum control method for use in the circuit |

| JP5712732B2 (en) * | 2011-03-31 | 2015-05-07 | ソニー株式会社 | Information processing apparatus, information processing system, information processing apparatus control method, and program |

| JP5794010B2 (en) * | 2011-07-19 | 2015-10-14 | 富士通株式会社 | Information processing apparatus, control program, and control method |

-

2013

- 2013-07-19 JP JP2015527120A patent/JP6090447B2/en not_active Expired - Fee Related

- 2013-07-19 WO PCT/JP2013/069604 patent/WO2015008372A1/en active Application Filing

Also Published As

| Publication number | Publication date |

|---|---|

| JPWO2015008372A1 (en) | 2017-03-02 |

| WO2015008372A1 (en) | 2015-01-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5175728B2 (en) | Test apparatus, adjustment method, and adjustment program | |

| JP4786262B2 (en) | Interface circuit | |

| KR101374465B1 (en) | Testing device and testing method | |

| JP6090447B2 (en) | Arithmetic processing device and control method of arithmetic processing device | |

| JP2010108217A (en) | Memory interface and method of operating the same | |

| US7543258B2 (en) | Clock design apparatus and clock design method | |

| TWI352996B (en) | Tester for testing semiconductor device | |

| KR20180005081A (en) | Memory device having command window generator | |

| US7739572B2 (en) | Tester for testing semiconductor device | |

| US8135968B2 (en) | Semiconductor apparatus including power management integrated circuit | |

| JPWO2009028034A1 (en) | Electronic device and diagnostic apparatus | |

| US8726114B1 (en) | Testing of SRAMS | |

| US20140140159A1 (en) | Short asynchronous glitch | |

| JP4849996B2 (en) | Delay circuit, test apparatus, program, semiconductor chip, initialization method, and initialization circuit | |

| KR20110121185A (en) | Semiconductor memory apparatus | |

| CN116615703A (en) | Task mode Vmin prediction and calibration | |

| JP2011066317A (en) | Semiconductor device | |

| JP2014095598A (en) | Semiconductor integrated circuit | |

| JP2010123807A (en) | Semiconductor integrated circuit and power source voltage control system | |

| JP2011010178A (en) | Communication apparatus | |

| JP2010252444A (en) | Device, method, and program for power source management | |

| JP2005011451A (en) | Test device and program | |

| JP2008152873A (en) | Memory test system | |

| KR20150078012A (en) | Semiconductor memory apparatus and test method using the same | |

| KR101004686B1 (en) | Semiconductor memory device and operation method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170123 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6090447 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |