JP6027166B2 - Game machine - Google Patents

Game machine Download PDFInfo

- Publication number

- JP6027166B2 JP6027166B2 JP2015061506A JP2015061506A JP6027166B2 JP 6027166 B2 JP6027166 B2 JP 6027166B2 JP 2015061506 A JP2015061506 A JP 2015061506A JP 2015061506 A JP2015061506 A JP 2015061506A JP 6027166 B2 JP6027166 B2 JP 6027166B2

- Authority

- JP

- Japan

- Prior art keywords

- random number

- variable display

- game

- value

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Pinball Game Machines (AREA)

Description

本発明は、パチンコ遊技機やスロットマシン等の遊技機に関する。 The present invention relates to a gaming machine such as a pachinko game machine or a slot machine.

遊技機として、遊技球などの遊技媒体を発射装置によって遊技領域に発射し、遊技領域に設けられている入賞口などの入賞領域に遊技媒体が入賞して始動条件が成立すると、複数種類の識別情報(以下、表示図柄)を可変表示装置にて可変表示し、その表示結果により所定の遊技価値を付与するか否かを決定する、いわゆる可変表示ゲームによって遊技興趣を高めたパチンコ遊技機がある。こうしたパチンコ遊技機では、可変表示ゲームにおける表示図柄の可変表示が完全に停止した際の停止図柄態様が特定表示態様となったときに、遊技者にとって有利な特定遊技状態(大当り遊技状態)となる。例えば、大当り遊技状態となったパチンコ遊技機は、大入賞口又はアタッカと呼ばれる特別電動役物を開放状態とし、遊技者に対して遊技球の入賞が極めて容易となる状態を一定時間継続的に提供する。 As a gaming machine, when a game medium such as a game ball is launched into a game area by a launching device, and the game medium wins a prize area such as a prize opening provided in the game area and a start condition is satisfied, a plurality of types of identification are made. There is a pachinko gaming machine in which information (hereinafter referred to as a display symbol) is variably displayed on a variable display device, and the game interest is enhanced by a so-called variable display game that determines whether or not to give a predetermined game value based on the display result. . In such a pachinko gaming machine, a specific game state (big hit game state) advantageous to the player is obtained when the stop symbol mode when the variable display of the display symbol in the variable display game is completely stopped becomes the specific display mode. . For example, a pachinko gaming machine that has become a big hit game state has a special electric accessory called a big prize opening or an attacker opened, and a state where a player can easily win a game ball for a certain period of time continuously. provide.

また、メダルやコイン、あるいは、パチンコ遊技機と同様の遊技球といった遊技媒体を用いて1ゲームに対する所定数の賭数を設定した後、遊技者がスタートレバーを操作することにより可変表示装置による表示図柄の可変表示を開始し、遊技者が各可変表示装置に対応して設けられた停止ボタンを操作することにより、その操作タイミングから予め定められた最大遅延時間の範囲内で表示図柄の可変表示を停止し、全ての可変表示装置の可変表示を停止したときに導出された表示結果に従って入賞が発生し、入賞に応じて予め定められた所定の遊技媒体が払い出され、特定入賞が発生した場合に、遊技状態を所定の遊技価値を遊技者に与える状態にするように構成されスロットマシンがある。 In addition, after setting a predetermined number of bets for one game using a game medium such as a medal, a coin, or a game ball similar to a pachinko gaming machine, the player operates the start lever to display on the variable display device. The variable display of the display symbol is started within the range of the maximum delay time determined in advance from the operation timing by starting the variable display of the symbol and the player operating the stop button provided corresponding to each variable display device. And a winning is generated according to the display result derived when the variable display of all the variable display devices is stopped, and a predetermined game medium predetermined according to the winning is paid out, and a specific winning is generated. In some cases, there is a slot machine configured to change the gaming state to a state in which a predetermined gaming value is given to the player.

こうした遊技機において、遊技機の動作を制御するために用いられる制御データの記憶内容が不正に変更されたかを検査するセキュリティチェックが実行されるものが提案されている(例えば特許文献1)。 In such a gaming machine, there has been proposed one in which a security check for inspecting whether or not the storage content of control data used for controlling the operation of the gaming machine has been illegally changed is executed (for example, Patent Document 1).

上記特許文献1に記載の技術では、セキュリティチェックの実行時間が一定である場合に、遊技機の動作を制御するプログラムの実行開始タイミングが解析されてしまい、その解析結果に基づく狙い撃ちや、いわゆる「ぶら下げ基板」を接続して不正信号を入力させることにより、特定遊技状態とする処理が不正に実行されるおそれがある。

In the technique described in

この発明は、上記実状に鑑みてなされたものであり、遊技機の動作を制御するプログラムの解析結果に基づく狙い撃ちなどの不正行為を防止できる遊技機を提供することを目的とする。 This invention has been made in consideration of the above, and an object thereof is to provide a gaming machine capable of prevent illegal acts such as shooting based on the result of analysis of the program for controlling the operation of the gaming machine.

(1)上記目的を達成するため、本願の請求項に係る遊技機は、遊技者にとって有利な有利状態(例えば大当り遊技状態など)に制御可能な遊技機(例えばパチンコ遊技機1など)であって、初期設定処理(例えばセキュリティチェックプログラム506Aによるセキュリティチェック処理など)を実行した後、制御データ(例えばROM506のユーザプログラムエリアにおける記憶データなど)に基づき遊技の進行を制御する遊技制御処理(例えば遊技制御用タイマ割込み処理など)を実行する制御用CPU(例えばCPU505など)を内蔵した遊技制御用マイクロコンピュータ(例えば遊技制御用マイクロコンピュータ100など)と、前記制御データを記憶する不揮発性メモリ(例えばROM506など)と、前記遊技制御用マイクロコンピュータに内蔵又は外付けされて乱数値となる数値データを生成する乱数回路(例えば乱数回路509など)とを備え、前記遊技制御用マイクロコンピュータは、前記初期設定処理において前記不揮発性メモリの記憶内容が変更されたか否かを検査するセキュリティチェック処理を実行するセキュリティチェック手段(例えばCPU505がステップS9〜ステップS14の処理を実行する部分など)と、前記セキュリティチェック手段によるセキュリティチェック処理を含む前記初期設定処理の実行時間を、前記初期設定処理が実行されるごとに所定の時間範囲で変化させることが可能な可変セキュリティ時間設定手段(例えばセキュリティ時間設定KSESのビット番号[4−3]に基づきCPU505がステップS5〜ステップS8の処理を実行する部分など)と、前記制御用CPUの動作とは別個にカウント値を更新するカウント手段と、前記遊技機のシステムリセット毎に、前記カウント手段によるカウント値を用いて、前記数値データの初期値をランダムに設定する初期値設定手段と、遊技制御処理において前記乱数回路から読み出した乱数値を用いて、前記有利状態に制御するか否かを判定する判定手段(例えばCPU505がステップS101にて始動入賞判定処理を実行した後、ステップS240の処理を実行する部分など)とを含み、前記不揮発性メモリは、前記遊技制御用マイクロコンピュータに内蔵され、前記遊技制御用マイクロコンピュータは、前記制御用CPU以外による前記不揮発性メモリの外部読出を制限する読出制限回路(例えば内部リソースアクセス制御回路501Aなど)を含み、第1識別情報の可変表示を実行する第1可変表示実行手段と、第2識別情報の可変表示を実行する第2可変表示実行手段と、前記第1識別情報の可変表示パターンを選択するための第1可変表示パターン選択処理と、前記第2識別情報の可変表示パターンを選択するための第2可変表示パターン選択処理と、を同一の処理ルーチンにより実行する可変表示パターン選択手段とをさらに備える。

(1) In order to achieve the above object, the gaming machine according to the claims of the present application is a gaming machine (for example,

上記(1)に記載の遊技機によれば、セキュリティチェック処理を実行する初期設定処理の実行時間を、初期設定処理が実行されるごとに所定の時間範囲で変化させる。これにより、遊技制御処理の実行開始タイミングを特定することが困難になり、遊技制御処理プログラムの解析結果に基づく狙い撃ちや、いわゆる「ぶら下げ基板」を接続することによる不正行為を防止することができる。

また、制御用CPU以外による不揮発性メモリの外部読出を制限する読出制限回路が遊技制御用マイクロコンピュータに含まれている。これにより、不揮発性メモリに記憶されている遊技制御処理プログラムを遊技制御用マイクロコンピュータの外部から読み出して解析などをすることが困難になり、遊技制御処理プログラムの解析結果に基づく狙い撃ちや、いわゆる「ぶら下げ基板」を接続することによる不正行為を防止することができる。

According to the gaming machine described in (1) above, the execution time of the initial setting process for executing the security check process is changed within a predetermined time range each time the initial setting process is executed. This makes it difficult to identify the execution start timing of the game control process, pick off and based on the result of analysis of the game control process program, it is possible to prevent cheating by connecting the so-called "hanging board" .

Further, the game control microcomputer includes a read restriction circuit for restricting external reading of the nonvolatile memory other than the control CPU. This makes it difficult to read the game control processing program stored in the non-volatile memory from the outside of the game control microcomputer for analysis, and aiming based on the analysis result of the game control processing program, so-called `` it is possible to prevent fraud by connecting the hanging board ".

(2)あるいは、遊技者にとって有利な有利状態(例えば大当り遊技状態など)に制御可能な遊技機(例えばパチンコ遊技機1など)であって、初期設定処理(例えばセキュリティチェックプログラム506Aによるセキュリティチェック処理など)を実行した後、制御データ(例えばROM506のユーザプログラムエリアにおける記憶データなど)に基づき遊技の進行を制御する遊技制御処理(例えば遊技制御用タイマ割込み処理など)を実行する制御用CPU(例えばCPU505など)を内蔵した遊技制御用マイクロコンピュータ(例えば遊技制御用マイクロコンピュータ100など)と、前記制御データを記憶する不揮発性メモリ(例えばROM506など)と、前記遊技制御用マイクロコンピュータに内蔵又は外付けされて乱数値となる数値データを生成する乱数回路(例えば乱数回路509など)とを備え、前記遊技制御用マイクロコンピュータは、前記初期設定処理において前記不揮発性メモリの記憶内容が変更されたか否かを検査するセキュリティチェック処理を実行するセキュリティチェック手段(例えばCPU505がステップS9〜ステップS14の処理を実行する部分など)と、前記セキュリティチェック手段によるセキュリティチェック処理を含む前記初期設定処理の実行時間を、固定時間に加えて予め選択可能な複数の延長時間のいずれかに設定可能な延長セキュリティ時間設定手段(例えばセキュリティ時間設定KSESのビット番号[2−0]に基づきCPU505がステップS1〜ステップS4の処理を実行する部分など)と、前記制御用CPUの動作とは別個にカウント値を更新するカウント手段と、前記遊技機のシステムリセット毎に、前記カウント手段によるカウント値を用いて、前記数値データの初期値をランダムに設定する初期値設定手段と、遊技制御処理において前記乱数回路から読み出した乱数値を用いて、前記有利状態に制御するか否かを判定する判定手段(例えばCPU505がステップS101にて始動入賞判定処理を実行した後、ステップS240の処理を実行する部分など)とを含み、前記不揮発性メモリは、前記遊技制御用マイクロコンピュータに内蔵され、前記遊技制御用マイクロコンピュータは、前記制御用CPU以外による前記不揮発性メモリの外部読出を制限する読出制限回路(例えば内部リソースアクセス制御回路501Aなど)を含み、第1識別情報の可変表示を実行する第1可変表示実行手段と、第2識別情報の可変表示を実行する第2可変表示実行手段と、前記第1識別情報の可変表示パターンを選択するための第1可変表示パターン選択処理と、前記第2識別情報の可変表示パターンを選択するための第2可変表示パターン選択処理と、を同一の処理ルーチンにより実行する可変表示パターン選択手段とをさらに備える。

(2) Alternatively, a gaming machine (for example,

上記(2)に記載の遊技機によれば、セキュリティチェック処理を実行する初期設定処理の実行時間を、固定時間に加えて予め選択可能な複数の延長時間のいずれかに設定する。これにより、遊技制御処理の実行開始タイミングを特定することが困難になり、遊技制御処理プログラムの解析結果に基づく狙い撃ちや、いわゆる「ぶら下げ基板」を接続することによる不正行為を防止することができる。

また、制御用CPU以外による不揮発性メモリの外部読出を制限する読出制限回路が遊技制御用マイクロコンピュータに含まれている。これにより、不揮発性メモリに記憶されている遊技制御処理プログラムを遊技制御用マイクロコンピュータの外部から読み出して解析などをすることが困難になり、遊技制御処理プログラムの解析結果に基づく狙い撃ちや、いわゆる「ぶら下げ基板」を接続することによる不正行為を防止することができる。

あるいは、前記遊技制御用マイクロコンピュータは、各々を識別可能な複数種類の識別情報(例えば特別図柄や飾り図柄など)の可変表示パターンを、複数種類のうちのいずれかに決定する可変表示パターン決定手段を更に含み、前記可変表示パターン決定手段による決定結果に基づいて、前記識別情報の可変表示を実行する可変表示実行手段を更に備える。

According to the gaming machine described in (2) above, the execution time of the initial setting process for executing the security check process is set to one of a plurality of pre-selectable extended times in addition to the fixed time. This makes it difficult to identify the execution start timing of the game control process, pick off and based on the result of analysis of the game control process program, it is possible to prevent cheating by connecting the so-called "hanging board" .

Further, the game control microcomputer includes a read restriction circuit for restricting external reading of the nonvolatile memory other than the control CPU. This makes it difficult to read the game control processing program stored in the non-volatile memory from the outside of the game control microcomputer for analysis, and aiming based on the analysis result of the game control processing program, so-called `` it is possible to prevent fraud by connecting the hanging board ".

Alternatively, the game control microcomputer may determine a variable display pattern of a plurality of types of identification information (for example, special symbols, decorative symbols, etc.) that can be identified as one of a plurality of types. And further includes variable display executing means for executing variable display of the identification information based on the determination result by the variable display pattern determining means.

以下、図面を参照しつつ、本発明の一実施形態を詳細に説明する。図1は、本実施の形態におけるパチンコ遊技機の正面図であり、主要部材の配置レイアウトを示す。パチンコ遊技機(遊技機)1は、大別して、遊技盤面を構成する遊技盤(ゲージ盤)2と、遊技盤2を支持固定する遊技機用枠(台枠)3とから構成されている。遊技盤2には、ガイドレールによって囲まれた、ほぼ円形状の遊技領域が形成されている。この遊技領域には、遊技媒体としての遊技球が、図2に示す発射モータ61を含む打球発射装置により発射されて打ち込まれる。

Hereinafter, an embodiment of the present invention will be described in detail with reference to the drawings. FIG. 1 is a front view of a pachinko gaming machine according to the present embodiment and shows an arrangement layout of main members. The pachinko gaming machine (gaming machine) 1 is roughly composed of a gaming board (gauge board) 2 constituting a gaming board surface and a gaming machine frame (base frame) 3 for supporting and fixing the

遊技盤2の所定位置(図1に示す例では、遊技領域の右側方)には、第1特別図柄表示装置4Aと、第2特別図柄表示装置4Bとが設けられている。第1特別図柄表示装置4Aと第2特別図柄表示装置4Bはそれぞれ、例えば7セグメントやドットマトリクスのLED(発光ダイオード)等から構成され、可変表示ゲームの一例となる特図ゲームにおいて、各々が識別可能な複数種類の識別情報(特別識別情報)である特別図柄(「特図」ともいう)を、変動可能に表示(可変表示)する。例えば、第1特別図柄表示装置4Aと第2特別図柄表示装置4Bはそれぞれ、「0」〜「9」を示す数字や「−」を示す記号等から構成される複数種類の特別図柄を可変表示する。なお、第1特別図柄表示装置4Aや第2特別図柄表示装置4Bにて表示される特別図柄は、「0」〜「9」を示す数字や「−」を示す記号等から構成されるものに限定されず、例えば7セグメントのLEDにおいて点灯させるものと消灯させるものとの組合せを異ならせた複数種類の点灯パターンが、複数種類の特別図柄として予め設定されていればよい。複数種類の特別図柄には、それぞれに対応した図柄番号が付されている。一例として、「0」〜「9」を示す数字それぞれには、「0」〜「9」の図柄番号が付され、「−」を示す記号には、「10」の図柄番号が付されていればよい。以下では、第1特別図柄表示装置4Aにより可変表示される特別図柄を「第1特図」ともいい、第2特別図柄表示装置4Bにより可変表示される特別図柄を「第2特図」ともいう。

A first special

遊技盤2における遊技領域の中央付近には、画像表示装置5が設けられている。画像表示装置5は、例えばLCD(液晶表示装置)等から構成され、各種の演出画像を表示する表示領域を形成している。画像表示装置5の表示領域では、特図ゲームにおける第1特別図柄表示装置4Aによる第1特図の可変表示や第2特別図柄表示装置4Bによる第2特図の可変表示のそれぞれに対応して、例えば3つといった複数に分割された可変表示部となる飾り図柄表示部にて、各々が識別可能な複数種類の識別情報(装飾識別情報)である飾り図柄を可変表示する。この飾り図柄の可変表示も、可変表示ゲームに含まれる。

An

一例として、画像表示装置5の表示領域には、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rが配置されている。そして、特図ゲームにおいて、第1特別図柄表示装置4Aによる第1特図の可変表示と、第2特別図柄表示装置4Bによる第2特図の可変表示とのうち、いずれかの可変表示が開始されることに対応して、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rの全部において飾り図柄の可変表示(例えば上下方向あるいは左右方向のスクロール表示など)が開始される。その後、特図ゲームにおける可変表示結果として確定特別図柄が停止表示(完全停止表示)されるときに、画像表示装置5における「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにて、飾り図柄の可変表示結果となる確定飾り図柄(最終停止図柄)が停止表示(完全停止表示)される。なお、「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rは、画像表示装置5の表示領域内で移動可能とされ、飾り図柄を縮小あるいは拡大して表示することができるようにしてもよい。特別図柄や飾り図柄が完全停止表示されたときには、各図柄の可変表示における表示結果が確定的に表示され、それ以後は今回の可変表示が進行しないことを遊技者が認識できる表示状態となる。これに対して、飾り図柄の可変表示を開始してから可変表示結果となる確定飾り図柄が完全停止表示されるまでの可変表示中には、飾り図柄の変動速度が「0」となって、飾り図柄が停留して表示され、例えば微少な揺れや伸縮などを生じさせる表示状態となることがある。このような表示状態は、仮停止表示ともいい、可変表示における表示結果が確定的に表示されていないものの、スクロール表示や更新表示による飾り図柄の変動が進行していないことを遊技者が認識可能となる。なお、仮停止表示には、微少な揺れや伸縮なども生じさせず、所定時間(例えば1秒間)よりも短い時間だけ、飾り図柄を完全停止表示することなどが含まれてもよい。完全停止表示や仮停止表示のように、特別図柄や飾り図柄の変動が進行していないことを遊技者が認識できる程度に表示図柄を停止表示することは、導出表示ともいう。

As an example, “left”, “middle”, and “right” decorative

「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにて可変表示される飾り図柄には、例えば8種類の図柄(英数字「1」〜「8」あるいは漢数字「一」〜「八」、英文字「A」〜「H」、所定のモチーフに関連する8個のキャラクタを示す演出画像、数字や文字あるいは記号とキャラクタとを組み合わせた演出画像など。なお、キャラクタを示す演出画像は、例えば人物や動物、これら以外の物体、もしくは、文字などの記号、あるいは、その他の任意の図形を示す画像であればよい。)が含まれていればよい。また、こうした8種類の飾り図柄の他に、ブランク図柄(大当り組合せを構成しない図柄)が含まれていてもよい。飾り図柄のそれぞれには、対応する図柄番号が付されている。例えば、「1」〜「8」を示す英数字それぞれに対して、「1」〜「8」の図柄番号が付されている。なお、可変表示される飾り図柄の種類数は、8種類のものに限定されず、任意の複数種類からなる飾り図柄であればよい。

The decorative symbols variably displayed on the “left”, “middle”, and “right” decorative

飾り図柄の変動中には、「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにおいて、例えば図柄番号が小さいものから大きいものへと順次に、上方から下方へ、あるいは、右側から左側へと、流れるようなスクロール表示が行われる。そして、図柄番号が最大(例えば「8」)である飾り図柄が表示されると、続いて図柄番号が最小(例えば「1」)である飾り図柄が表示される。あるいは、飾り図柄表示部5L、5C、5Rのうち少なくともいずれか1つ(例えば「左」の飾り図柄表示部5Lなど)において、図柄番号が大きいものから小さいものへとスクロール表示を行って、図柄番号が最小である飾り図柄が表示されると、続いて図柄番号が最大である飾り図柄が表示されるようにしてもよい。

While the decorative symbols are changing, in the decorative

画像表示装置5の表示領域には、始動入賞記憶表示部5Hも配置されている。始動入賞記憶表示部5Hでは、可変表示の保留数(特図保留記憶数)を特定可能に表示する保留記憶表示が行われる。ここで、可変表示の保留は、普通入賞球装置6Aが形成する第1始動入賞口や普通可変入賞球装置6Bが形成する第2始動入賞口に遊技球が進入(始動入賞)したときに発生する。すなわち、特図ゲームや飾り図柄の可変表示といった可変表示ゲームを実行するための始動条件(「実行条件」ともいう)は成立したが、先に成立した開始条件に基づく可変表示ゲームが実行中であることやパチンコ遊技機1が大当り遊技状態に制御されていることなどにより、可変表示ゲームを開始するための開始条件は成立していないときに、成立した始動条件に対応する可変表示の保留が行われる。

In the display area of the

一例として、始動入賞記憶表示部5Hには、始動入賞の発生に基づき先に始動条件が成立した可変表示ゲームから順に左から右へと、表示色が変更される複数の表示部位が設けられている。そして、第1始動入賞口に遊技球が進入したことに基づき第1特別図柄表示装置4Aにおける第1特図を用いた特図ゲームの始動条件(第1始動条件)が成立したときには、通常非表示(透過色)となっている表示部位のうちの1つ(例えば非表示となっている表示部位のうち左端の表示部位)を青色表示に変化させる。また、第2始動入賞口に遊技球が進入したことに基づき第2特別図柄表示装置4Bにおける第2特図を用いた特図ゲームの始動条件(第2始動条件)が成立したときには、通常非表示となっている表示部位のうちの1つを赤色表示に変化させる。その後、第1特図を用いた特図ゲームの開始条件(第1開始条件)と第2特図を用いた特図ゲームの開始条件(第2開始条件)のいずれかが成立したときには、例えば左端の表示部位における表示を除去するとともに、各表示部位における表示を1つずつ左方向に移動させる。このとき、青色表示や赤色表示に変化していた表示部位のうちの1つ(例えば表示色が変化していた表示部位のうち右端の表示部位)は、非表示に戻る。ここで、保留記憶表示を行う際に、可変表示ゲームの始動条件が成立したことに基づく特図保留記憶数は特定できたものの、その始動条件が第1始動条件であるか第2始動条件であるかを特定できない場合に、例えば特図保留記憶数に対応する個数の表示部位を灰色表示に変化させることなどにより、特図保留記憶数の表示態様を所定の表示態様に変更してもよい。

As an example, the start winning memory display section 5H is provided with a plurality of display parts whose display colors are changed from left to right in order from the variable display game in which the start condition is established based on the occurrence of the start winning. Yes. When the start condition (first start condition) of the special figure game using the first special figure in the first special

なお、始動入賞記憶表示部5Hでは、特図保留記憶数を示す数字を表示することなどにより、特図保留記憶数を遊技者等が認識できるようにしてもよい。始動入賞記憶表示部5Hとともに、あるいは始動入賞記憶表示部5Hに代えて、特図保留記憶数を表示する表示器を設けるようにしてもよい。図1に示す例では、始動入賞記憶表示部5Hとともに、第1特別図柄表示装置4A及び第2特別図柄表示装置4Bの上部に、特図保留記憶数を特定可能に表示するための第1保留表示器25Aと第2保留表示器25Bとが設けられている。第1保留表示器25Aは、普通入賞球装置6Aが形成する第1始動入賞口に進入した有効始動入賞球数としての第1保留記憶数を特定可能に表示する。第2保留表示器25Bは、普通可変入賞球装置6Bが形成する第2始動入賞口に進入した有効始動入賞球数としての第2保留記憶数を特定可能に表示する。第1保留表示器25Aと第2保留表示器25Bはそれぞれ、例えば第1保留記憶数と第2保留記憶数のそれぞれにおける上限値(例えば「4」)に対応した個数(例えば4個)のLEDを含んで構成されている。

In the start winning memory display section 5H, a number indicating the special figure reserved memory number may be displayed so that the player or the like can recognize the special figure reserved memory number. A display for displaying the number of reserved special figure memories may be provided together with the start winning memory display unit 5H or instead of the start winning memory display unit 5H. In the example shown in FIG. 1, together with the start winning memory display section 5H, the first hold for displaying the number of special figure hold memories identifiable on the upper part of the first special

画像表示装置5の表示領域には、飾り図柄とは異なる識別情報としての色図柄を可変表示する色図柄表示部が設けられていてもよい。一例として、色図柄表示部には、第1特別図柄表示装置4Aによる第1特図を用いた特図ゲームが開始されるときに、色図柄の変動(例えば表示色の更新表示)が開始される「左」の色図柄表示部と、第2特別図柄表示装置4Bによる第2特図を用いた特図ゲームが開始されるときに、色図柄の変動が開始される「右」の色図柄表示部とが含まれていればよい。そして、特図ゲームにおいて可変表示結果となる確定特別図柄が完全停止表示されるときには、色図柄の変動が終了して、色図柄の可変表示結果となる確定色図柄が完全停止表示される。「左」及び「右」の色図柄表示部にて可変表示される色図柄には、例えば4種類の図柄(「黄色」、「緑色」、「赤色」、「青色」など)といった、複数種類の色図柄が含まれていればよい。色図柄のそれぞれには、対応する図柄番号が付されている。一例として、「黄色」、「緑色」、「赤色」、「青色」の色図柄それぞれに対して、「1」〜「4」の図柄番号が付されていればよい。

The display area of the

画像表示装置5の下方には、普通入賞球装置6Aと、普通可変入賞球装置6Bとが設けられている。普通入賞球装置6Aは、例えば所定の玉受部材によって常に一定の開放状態に保たれる第1始動入賞口を形成する。普通可変入賞球装置6Bは、図2に示す普通電動役物用のソレノイド81によって垂直位置となる通常開放状態と傾動位置となる拡大開放状態とに変化する一対の可動翼片を有する電動チューリップ型役物(普通電動役物)を備え、第2始動入賞口を形成する。一例として、普通可変入賞球装置6Bでは、普通電動役物用のソレノイド81がオフ状態であるときに可動翼片が垂直位置となることにより、遊技球が第2始動入賞口に進入しにくい通常開放状態となる。その一方で、普通可変入賞球装置6Bでは、普通電動役物用のソレノイド81がオン状態であるときに可動翼片が傾動位置となることにより、遊技球が第2始動入賞口に進入しやすい拡大開放状態となる。なお、普通可変入賞球装置6Bは、通常開放状態であるときでも、第2始動入賞口には遊技球が進入可能であるものの、拡大開放状態であるときよりも遊技球が進入する可能性が低くなるように構成してもよい。あるいは、普通可変入賞球装置6Bは、通常開放状態において、例えば第2始動入賞口を閉鎖することなどにより、第2始動入賞口には遊技球が進入しないように構成してもよい。

Below the

普通入賞球装置6Aに形成された第1始動入賞口に進入した遊技球は、例えば図2に示す第1始動口スイッチ22Aによって検出される。普通可変入賞球装置6Bに形成された第2始動入賞口に進入した遊技球は、例えば図2に示す第2始動口スイッチ22Bによって検出される。第1始動口スイッチ22Aによって遊技球が検出されたことに基づき、所定個数(例えば3個)の遊技球が賞球として払い出され、第1保留記憶数が所定の上限値(例えば「4」)以下であれば、第1始動条件が成立する。第2始動口スイッチ22Bによって遊技球が検出されたことに基づき、所定個数(例えば3個)の遊技球が賞球として払い出され、第2保留記憶数が所定の上限値以下であれば、第2始動条件が成立する。なお、第1始動口スイッチ22Aによって遊技球が検出されたことに基づいて払い出される賞球の個数と、第2始動口スイッチ22Bによって遊技球が検出されたことに基づいて払い出される賞球の個数は、互いに同一の個数であってもよいし、異なる個数であってもよい。

A game ball that has entered the first start winning opening formed in the normal

普通入賞球装置6Aと普通可変入賞球装置6Bの下方には、特別可変入賞球装置7が設けられている。特別可変入賞球装置7は、図2に示す大入賞口扉用のソレノイド82によって開閉駆動される大入賞口扉を備え、その大入賞口扉によって開放状態(第1状態)と閉鎖状態(第2状態)とに変化する大入賞口を形成する。一例として、特別可変入賞球装置7では、大入賞口扉用のソレノイド82がオフ状態であるときに大入賞口扉が大入賞口を閉鎖状態にする。その一方で、特別可変入賞球装置7では、大入賞口扉用のソレノイド82がオン状態であるときに大入賞口扉が大入賞口を開放状態にする。特別可変入賞球装置7に形成された大入賞口に進入した遊技球は、例えば図2に示すカウントスイッチ23によって検出される。カウントスイッチ23によって遊技球が検出されたことに基づき、所定個数(例えば13個)の遊技球が賞球として払い出される。

A special variable winning

遊技盤2の所定位置(図1に示す例では、遊技領域の左側方)には、普通図柄表示器20が設けられている。一例として、普通図柄表示器20は、第1特別図柄表示装置4Aや第2特別図柄表示装置4Bと同様に7セグメントやドットマトリクスのLED等から構成され、特別図柄とは異なる複数種類の識別情報である普通図柄(「普図」あるいは「普通図」ともいう)を変動可能に表示(可変表示)する。このような普通図柄の可変表示は、普図ゲーム(「普通図ゲーム」ともいう)と称される。普通図柄表示器20は、例えば「0」〜「9」を示す数字や「−」を示す記号等から構成される複数種類の普通図柄を可変表示する。複数種類の普通図柄には、それぞれに対応した図柄番号が付されている。一例として、「0」〜「9」を示す数字それぞれには、「0」〜「9」の図柄番号が付され、「−」を示す記号には、「10」の図柄番号が付されていればよい。なお、普通図柄表示器20は、「0」〜「9」を示す数字や「−」を示す記号等を普通図柄として可変表示するものに限定されず、例えば「○」と「×」とを示す装飾ランプ(又はLED)を交互に点灯させることや、「左」、「中」、「右」といった複数の装飾ランプ(又はLED)を所定順序で点灯させることにより、普通図柄を可変表示するものであってもよい。普通図柄表示器20の上方には、普図保留表示器25Cが設けられている。普図保留表示器25Cは、例えば4個のLEDを含んで構成され、通過ゲート41を通過した有効通過球数としての普図保留記憶数を表示する。

A

遊技盤2の表面には、上記の構成以外にも、遊技球の流下方向や速度を変化させる風車及び多数の障害釘が設けられている。また、第1始動入賞口、第2始動入賞口及び大入賞口とは異なる入賞口として、例えば所定の玉受部材によって常に一定の開放状態に保たれる一般入賞口が1つ又は複数設けられてもよい。この場合には、一般入賞口のいずれかに進入した遊技球が所定の一般入賞球スイッチによって検出されたことに基づき、所定個数(例えば10個)の遊技球が賞球として払い出されればよい。遊技領域の最下方には、いずれの入賞口にも進入しなかった遊技球が取り込まれるアウト口が設けられている。遊技機用枠3の左右上部位置には、効果音等を再生出力するためのスピーカ8L、8Rが設けられており、さらに遊技領域周辺部には、遊技効果ランプ9が設けられている。パチンコ遊技機1の遊技領域における各構造物(例えば普通入賞球装置6A、普通可変入賞球装置6B、特別可変入賞球装置7等)の周囲には、装飾用LEDが配置されていてもよい。

In addition to the above configuration, the surface of the

遊技機用枠3の右下部位置には、遊技媒体としての遊技球を遊技領域に向けて発射するために遊技者等によって操作される打球操作ハンドルとなる操作ノブ30が設けられている。例えば、遊技者等による操作量(回転量)に応じて遊技球の弾発力を調整する。打球操作ハンドルには、打球発射装置が備える発射モータの駆動を停止させるための単発発射スイッチや、タッチリング(タッチセンサ)が設けられていればよい。遊技領域の下方における遊技機用枠3の所定位置には、賞球として払い出された遊技球や所定の球貸機により貸し出された遊技球を、打球発射装置へと供給可能に保持(貯留)する打球供給皿(上皿)が設けられている。例えば打球供給皿の上面における手前側の中央位置といった、パチンコ遊技機1の遊技機用枠3における所定位置には、押下操作などにより遊技者が操作可能な操作ボタンが設置されていてもよい。また、打球供給皿の下方には、打球供給皿に収容不能となった遊技球を保持(貯留)する余剰球受皿(下皿)が設けられている。

At the lower right position of the

さらに、パチンコ遊技機1に隣接する所定位置には、プリペイドカード等を用いた球貸しを可能にするための処理が実行されるプリペイドカードユニット(カードユニット)が設置されてもよい。カードユニットは、プリペイドカードを取り込んで球貸しの処理を実行するだけでなく、会員カードや現金を取り込んで球貸しの処理を実行するものであってもよい。

Furthermore, a prepaid card unit (card unit) for executing processing for enabling ball lending using a prepaid card or the like may be installed at a predetermined position adjacent to the

普通図柄表示器20による普図ゲームは、遊技領域に設けられた通過ゲート41を通過した遊技球が図2に示すゲートスイッチ21によって検出されたことといった、普通図柄表示器20にて普通図柄の可変表示を実行するための普図始動条件が成立した後に、例えば前回の普図ゲームが終了したことといった、普通図柄の可変表示を開始するための普図開始条件が成立したことに基づいて、開始される。この普図ゲームでは、普通図柄の変動を開始させた後、所定の可変表示時間が経過すると、普通図柄の可変表示結果となる確定普通図柄を完全停止表示する。普通図柄の可変表示時間は、例えば各普図ゲームの開始時に、所定の乱数値を示す数値データを抽出することなどにより、複数種類の可変表示時間のうちで、いずれかに決定されればよい。普図ゲームにおける普通図柄の可変表示結果となる確定普通図柄として、例えば「7」を示す数字といった、特定の普通図柄(普図当り図柄)が停止表示されれば、普通図柄の可変表示結果が「普図当り」となる。その一方、確定普通図柄として、例えば「7」を示す数字以外の数字や記号といった、普図当り図柄以外の普通図柄が停止表示されれば、普通図柄の可変表示結果が「普図ハズレ」となる。普通図柄の可変表示結果が「普図当り」となったことに対応して、普通可変入賞球装置6Bを構成する電動チューリップの可動翼片が傾動位置となる拡大開放制御が行われ、所定時間が経過すると垂直位置に戻る通常開放制御が行われる。

In the normal game with the

第1特別図柄表示装置4Aによる特図ゲームは、普通入賞球装置6Aに形成された第1始動入賞口に進入した遊技球が図2に示す第1始動口スイッチ22Aによって検出されたことなどにより第1始動条件が成立した後に第1開始条件が成立したことに基づいて、開始される。第1開始条件は、例えば前回の特図ゲームや大当り遊技状態あるいは小当り遊技状態が終了したときなどに、第1特図を用いた今回の特図ゲームが開始可能となることにより成立する。第2特別図柄表示装置4Bによる特図ゲームは、普通可変入賞球装置6Bに形成された第2始動入賞口に進入した遊技球が図2に示す第2始動口スイッチ22Bによって検出されたことなどにより第2始動条件が成立した後に第2開始条件が成立したことに基づいて、開始される。第2開始条件は、例えば前回の特図ゲームや大当り遊技状態あるいは小当り遊技状態が終了したときなどに、第2特図を用いた今回の特図ゲームが開始可能となることにより成立する。

The special symbol game by the first special

第1特別図柄表示装置4Aや第2特別図柄表示装置4Bによる特図ゲームでは、特別図柄の可変表示を開始させた後、所定の可変表示時間が経過すると、特別図柄の可変表示結果となる確定特別図柄を完全停止表示する。特別図柄の可変表示時間は、各特図ゲームの開始時に、例えば図14に示すような変動パターン種別決定用の乱数値MR4を示す数値データや、変動パターン決定用の乱数値MR5を示す数値データなどに基づいて決定された変動パターンに対応して、複数種類の可変表示時間のうちで、いずれかに決定される。特図ゲームにおける特別図柄の可変表示結果となる確定特別図柄として、特定の特別図柄(大当り図柄)が停止表示されれば、特定表示結果としての「大当り」となり、大当り図柄とは異なる所定の特別図柄(小当り図柄)が停止表示されれば、所定表示結果としての「小当り」となり、大当り図柄や小当り図柄以外の特別図柄(ハズレ図柄)が停止表示されれば、非特定表示結果としての「ハズレ」となる。特図ゲームでの可変表示結果が「大当り」になった後には、特定遊技状態としての大当り遊技状態に制御される。また、特図ゲームでの可変表示結果が「小当り」になった後には、大当り遊技状態とは異なる小当り遊技状態に制御される。この実施の形態におけるパチンコ遊技機1では、一例として、「1」、「3」、「7」を示す数字を大当り図柄とし、「5」を示す数字を小当り図柄とし、「−」を示す記号をハズレ図柄としている。なお、第1特別図柄表示装置4Aによる特図ゲームにおける大当り図柄や小当り図柄、ハズレ図柄といった各図柄は、第2特別図柄表示装置4Bによる特図ゲームにおける各図柄とは異なる特別図柄となるようにしてもよいし、双方の特図ゲームにおいて共通の特別図柄が大当り図柄や小当り図柄、ハズレ図柄となるようにしてもよい。

In the special symbol game by the first special

この実施の形態では、大当り図柄となる「1」、「3」、「7」の数字を示す特別図柄のうち、「3」、「7」の数字を示す特別図柄を15ラウンド大当り図柄とし、「1」の数字を示す特別図柄を2ラウンド大当り図柄とする。特図ゲームにおける確定特別図柄として15ラウンド大当り図柄が停止表示された後に制御される第1特定遊技状態としての大当り遊技状態(15ラウンド大当り状態)では、特別可変入賞球装置7の開閉板が、第1期間となる所定期間(例えば29秒間)あるいは所定個数(例えば9個)の入賞球が発生するまでの期間にて大入賞口を開放状態とすることにより、特別可変入賞球装置7を遊技者にとって有利な第1状態に変化させるラウンドが実行される。こうしてラウンド中に大入賞口を開放状態とした開閉板は、遊技盤2の表面を落下する遊技球を受け止め、その後に大入賞口を閉鎖状態とすることにより、特別可変入賞球装置7を遊技者にとって不利な第2状態に変化させて、1回のラウンドを終了させる。15ラウンド大当り状態では、大入賞口の開放サイクルであるラウンドの実行回数が、第1回数(例えば「15」)となる。ラウンドの実行回数が「15」となる15ラウンド大当り状態における遊技は、15回開放遊技とも称される。

In this embodiment, among the special symbols indicating the numbers “1”, “3”, and “7” that are jackpot symbols, the special symbols indicating the numbers “3” and “7” are 15 round jackpot symbols, A special symbol indicating the number “1” is a two-round jackpot symbol. In the big hit gaming state (15 round big hit state) as the first specific gaming state controlled after the 15 round big hit symbol is stopped and displayed as a confirmed special symbol in the special figure game, the open / close plate of the special variable winning

特図ゲームにおける確定特別図柄として2ラウンド大当り図柄が停止表示された後に制御される第2特定遊技状態としての大当り遊技状態(2ラウンド大当り状態)では、各ラウンドで特別可変入賞球装置7を遊技者にとって有利な第1状態に変化させる期間(開閉板により大入賞口を開放状態とする期間)が、15ラウンド大当り状態における第1期間よりも短い第2期間(例えば0.5秒間)となる。また、2ラウンド大当り状態では、ラウンドの実行回数が、15ラウンド大当り状態における第1回数よりも少ない第2回数(例えば「2」)となる。なお、2ラウンド大当り状態では、各ラウンドで大入賞口を開放状態とする期間が第2期間となることと、ラウンドの実行回数が第2回数となることのうち、少なくともいずれか一方が行われるように制御されればよく、それ以外の制御は15ラウンド大当り状態と同様に行われるようにしてもよい。ラウンドの実行回数が「2」となる2ラウンド大当り状態における遊技は、2回開放遊技とも称される。なお、2ラウンド大当り状態では、各ラウンドで特別可変入賞球装置7とは別個に設けられた所定の入賞球装置を、遊技者にとって不利な第2状態から遊技者にとって有利な第1状態に変化させ、所定期間(第1期間又は第2期間)が経過した後に第2状態へと戻すようにしてもよい。

In the big hit gaming state (two round big hit state) as the second specific gaming state controlled after the two round big hit symbol is stopped and displayed as the confirmed special symbol in the special figure game, the special variable winning

また、15ラウンド大当り図柄となる「3」、「7」の数字を示す特別図柄のうち、「3」の数字を示す特別図柄が特図ゲームにおける確定特別図柄として停止表示されたことに基づく15ラウンド大当り状態が終了した後には、特別遊技状態の1つとして、通常状態に比べて特図ゲームにおける特別図柄の変動時間(特図変動時間)が短縮される時短状態に制御される。ここで、通常状態とは、大当り遊技状態等の特定遊技状態や時短状態等の特別遊技状態以外の遊技状態のことであり、パチンコ遊技機1の初期設定状態(例えばシステムリセットが行われた場合のように、電源投入後に初期化処理を実行した状態)と同一の制御が行われる。時短状態は、所定回数(例えば100回)の特図ゲームが実行されることと、可変表示結果が「大当り」となることのうち、いずれかの条件が先に成立したときに、終了すればよい。なお、特図ゲームにおける確定特別図柄として15ラウンド大当り図柄のうち「3」の数字を示す特別図柄が停止表示されたことに基づく15ラウンド大当り状態が終了した後には、時短状態とはならずに通常状態となるようにしてもよい。こうした「3」の数字を示す特別図柄のように、特図ゲームにおける確定特別図柄として停止表示されたことに基づく大当り遊技状態が終了した後に時短状態や通常状態に制御される15ラウンド大当り図柄は、通常大当り図柄(「非確変大当り図柄」ともいう)と称される。特図ゲームにおける確定特別図柄が通常大当り図柄となる場合における特別図柄や飾り図柄の可変表示態様は、可変表示結果が「大当り」となる場合における「通常」(「通常大当り」ともいう)の可変表示態様(「大当り種別」ともいう)と称される。

Further, among the special symbols indicating the numbers “3” and “7” which are the 15-round jackpot symbol, the special symbol indicating the number “3” is stopped and displayed as the confirmed special symbol in the

15ラウンド大当り図柄となる「3」、「7」の数字を示す特別図柄のうち、「7」の数字を示す特別図柄が特図ゲームにおける確定特別図柄として停止表示されたことに基づく15ラウンド大当り状態が終了した後や、2ラウンド大当り図柄となる「1」の数字を示す特別図柄が特図ゲームにおける確定特別図柄として停止表示されたことに基づく2ラウンド大当り状態が終了した後には、時短状態とは異なる特別遊技状態の1つとして、例えば通常状態に比べて特図変動時間が短縮されるとともに、継続して確率変動制御(確変制御)が行われる確変状態(高確率遊技状態)に制御される。この確変状態では、各特図ゲームや飾り図柄の可変表示において、可変表示結果が「大当り」となって更に大当り遊技状態に制御される確率が、通常状態よりも高くなるように向上する。このような確変状態は、特図ゲームの実行回数に関わりなく、次に可変表示結果が「大当り」となるまで継続してもよい。これに対して、確変状態となった後に、所定回数(例えば100回)の特図ゲームが実行されることと、可変表示結果が「大当り」となることのうち、いずれかの条件が先に成立したときに、終了するようにしてもよい。また、確変状態において所定回数の特図ゲームが実行されたり可変表示結果が「大当り」となる以前であっても、特図ゲームが開始されるときに、所定の割合で確変状態が終了することがあるようにしてもよい。 Out of the special symbols showing the numbers “3” and “7” that will be the 15-round jackpot symbol, the 15-round jackpot is based on the special symbol showing the number “7” being stopped and displayed as a confirmed special symbol in the special game. After the state is over, or after the two round jackpot state is over based on the fact that the special symbol indicating the number “1” that becomes the two-round jackpot symbol is stopped and displayed as the confirmed special symbol in the special figure game, As one of the special game states different from the normal game state, for example, the special figure change time is shortened compared to the normal state, and the probability change state (high probability game state) in which probability change control (probability change control) is continuously performed is controlled. Is done. In this probability change state, the variable display result of each special figure game and the decorative symbol variable display is improved so that the probability that the variable display result becomes “big hit” and is further controlled to the big hit gaming state is higher than in the normal state. Such a probability change state may be continued until the next variable display result becomes “big hit” regardless of the number of executions of the special game. On the other hand, after the certainty change state is reached, any one of the conditions that the special game is executed a predetermined number of times (for example, 100 times) or the variable display result is “big hit” is first. You may make it complete | finish when it is materialized. In addition, even if the special figure game is executed a predetermined number of times in the probability change state or before the variable display result is “big hit”, the probability change state ends at a predetermined rate when the special figure game is started. There may be.

「7」の数字を示す特別図柄のように、特図ゲームにおける確定特別図柄として停止表示されたことに基づく大当り遊技状態が終了した後に確変状態に制御される15ラウンド大当り図柄は、確変大当り図柄と称される。特図ゲームにおける確定特別図柄が確変大当り図柄となる場合における特別図柄や飾り図柄の可変表示態様は、可変表示結果が「大当り」となる場合における「確変」(「確変大当り」ともいう)の可変表示態様(「大当り種別」ともいう)と称される。「1」の数字を示す特別図柄のように、特図ゲームにおける確定特別図柄として停止表示されたことに基づく大当り遊技状態が終了した後に確変状態に制御される2ラウンド大当り図柄は、突確大当り図柄と称される。特図ゲームにおける確定特別図柄が突確大当り図柄となる場合における特別図柄や飾り図柄の可変表示態様は、可変表示結果が「大当り」となる場合における「突確」(「突確大当り」あるいは「突然確変大当り」ともいう)の可変表示態様(「大当り種別」ともいう)と称される。 Like the special symbol indicating the number “7”, the 15-round jackpot symbol controlled to the probable change state after the jackpot gaming state based on being stopped and displayed as the confirmed special symbol in the special symbol game is a probabilistic big hit symbol. It is called. The variable display mode of special symbols and decorative symbols when the confirmed special symbol in the special figure game becomes a probable big hit symbol is variable "probable change" (also called "probable big hit") when the variable display result is "big hit". It is referred to as a display mode (also referred to as “big hit type”). Like the special symbol indicating the number “1”, the two-round big hit symbol controlled to the probable change state after the big hit gaming state based on being stopped and displayed as the confirmed special symbol in the special figure game is a sudden big hit symbol. It is called. The variable display mode of special symbols and decorative symbols when the confirmed special symbol in the special figure game is a sudden big hit symbol is “surprise” (“surprise big hit” or “sudden probability big hit” when the variable display result is “big hit”. ")" As a variable display mode (also referred to as "big hit type").

確変状態や時短状態では、普通図柄表示器20による普図ゲームにおける普通図柄の可変表示時間を通常状態のときよりも短くする制御や、各回の普図ゲームで普通図柄の可変表示結果が「普図当り」となる確率を通常状態のときよりも向上させる制御、可変表示結果が「普図当り」となったことに基づく普通可変入賞球装置6Bにおける可動翼片の傾動時間を通常状態のときよりも長くする制御、その傾動回数を通常状態のときよりも増加させる制御といった、第2始動入賞口に遊技球が進入する可能性を高めて第2始動条件が成立しやすくなることで遊技者にとって有利となる制御が行われる。なお、確変状態や時短状態では、これらの制御のいずれか1つが行われるようにしてもよいし、複数の制御が組み合わせられて行われるようにしてもよい。確変状態と時短状態とでは、行われる制御が異なるようにしてもよいし、行われる制御の組合せ(同一の制御を含んでも含まなくてもよい)が異なるようにしてもよい。

In the probabilistic state and the short time state, the normal

特図ゲームにおける確定特別図柄として小当り図柄が停止表示された後には、大当り遊技状態とは異なる小当り遊技状態に制御される。この小当り遊技状態では、2ラウンド大当り状態と同様に特別可変入賞装置7を遊技者にとって有利な第1状態に変化させる可変入賞動作が行われる。すなわち、小当り遊技状態では、例えば特別可変入賞球装置7が備える開閉板により大入賞口を第2期間にわたり開放状態とする動作が、第2回数に達するまで繰り返し実行される。なお、小当り遊技状態では、2ラウンド大当り状態と同様に、大入賞口を開放状態とする期間が第2期間となることと、大入賞口を開放状態とする動作の実行回数が第2回数となることのうち、少なくともいずれか一方が行われるように制御されればよい。小当り遊技状態が終了した後には、遊技状態の変更が行われず、可変表示結果が「小当り」となる以前の遊技状態に継続して制御されることになる。ただし、可変表示結果が「小当り」となる可変表示ゲームに対応して、時短状態を終了する旨の判定がなされた場合には、小当り遊技状態の終了後に、通常状態へと制御されることになる。可変入賞動作により大入賞口を開放状態とする回数が「2」である小当り遊技状態における遊技は、2ラウンド大当り状態における遊技と同様に、2回開放遊技とも称される。なお、2ラウンド大当り状態における各ラウンドで特別可変入賞球装置7とは別個に設けられた入賞球装置を第1状態に変化させる場合には、小当り遊技状態でも、2ラウンド大当り状態と同様の態様で、その入賞球装置を第1状態に変化させるようにすればよい。

After the small hit symbol is stopped and displayed as the confirmed special symbol in the special symbol game, the small hit game state different from the big hit game state is controlled. In this small hit gaming state, a variable winning operation for changing the special

画像表示装置5の表示画面では、第1特別図柄表示装置4Aや第2特別図柄表示装置4Bによる特別図柄の可変表示に対応して、飾り図柄の可変表示が行われる。すなわち、画像表示装置5の表示画面では、第1開始条件と第2開始条件のいずれか一方が成立したことに基づいて、例えば「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rにおける全部にて飾り図柄の加速表示(全図柄加速表示)を行い、所定速度に達すれば、飾り図柄の定速表示(全図柄定速表示)を行う。こうした全図柄加速表示や全図柄定速表示は、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rの全部にて飾り図柄を可変表示する全図柄変動に含まれる。こうした全図柄変動の後、例えば「左」→「右」→「中」といった所定順序で飾り図柄の減速表示(各図柄減速表示)を行い、変動速度が「0」となれば、飾り図柄を停留して表示する一方で、例えば微少な揺れや伸縮などを生じさせる仮停止表示を行う。そして、飾り図柄の可変表示を開始してからの経過時間が変動パターンなどに基づいて決定された可変表示時間に達したときには、可変表示結果となる確定飾り図柄を完全停止表示する。なお、確定飾り図柄を停止表示する手順としては、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rにおいて所定順序で飾り図柄を減速表示するものに限定されず、「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにおいて同時に確定飾り図柄となる飾り図柄を減速表示(全図柄減速表示)するものが含まれていてもよい。

On the display screen of the

全図柄変動が開始された後には、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rのうち全部又は一部の飾り図柄表示部にて、飾り図柄をリーチ表示状態で導出表示することがある。ここで、リーチ表示状態とは、画像表示装置5の表示画面にて導出表示された飾り図柄が大当り組合せの一部を構成しているときに未だ導出表示されていない飾り図柄(「リーチ変動図柄」ともいう)については変動が継続している表示状態、あるいは、全部又は一部の飾り図柄が大当り組合せの全部又は一部を構成しながら同期して変動している表示状態のことである。具体的には、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rにおける一部(例えば「左」及び「右」の飾り図柄表示部5L、5Rなど)では予め定められた大当り組合せを構成する飾り図柄(例えば「7」の英数字を示す飾り図柄)が導出表示されているときに未だ導出表示されていない残りの飾り図柄表示部(例えば「中」の飾り図柄表示部5Cなど)では飾り図柄が変動している表示状態、あるいは、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rにおける全部又は一部で飾り図柄が大当り組合せの全部又は一部を構成しながら同期して変動している表示状態である。また、リーチ表示状態となったことに対応して、画像表示装置5の表示画面に飾り図柄とは異なるアニメーション画像や実写画像といった演出画像を表示させたり、背景画像の表示態様を変化させたり、飾り図柄の変動態様を変化させたりすることがある。このような演出画像の表示や背景画像の表示態様の変化、飾り図柄の変動態様の変化を、リーチ演出表示(あるいは単にリーチ演出)という。リーチ演出の中には、それが出現すると、通常のリーチ演出(ノーマルリーチ)に比べて大当りが発生しやすい(高い確率で大当りとなる)ように設定されたものがある。このような特別のリーチ演出を、スーパーリーチ演出(あるいは単に「スーパーリーチ」)ともいう。一例として、スーパーリーチとなるリーチ演出には、ノーマルリーチと同様のリーチ演出を所定時間が経過するまで行ってから、例えば背景画像の表示態様や、表示されるキャラクタ、飾り図柄の変動方向といった飾り図柄の変動態様のうち、少なくともいずれか1つがリーチ表示状態となる以前やノーマルリーチのときとは異なるものとなることにより、演出態様が変化(いわゆる「発展」)して、スーパーリーチに特有のリーチ演出における導入部分が開始されるものが含まれていればよい。また、スーパーリーチとなるリーチ演出には、飾り図柄がリーチ表示状態で導出表示されたときに、ノーマルリーチと同様のリーチ演出を行うことなく、スーパーリーチに特有のリーチ演出における導入部分が開始されるものが含まれていてもよい。

After all symbols change is started, the decorative symbols are reach-displayed on all or some of the decorative

また、飾り図柄の可変表示中には、リーチ演出とは異なり、飾り図柄がリーチ状態で導出表示される可能性があることや、可変表示結果が「大当り」となる可能性があることを、飾り図柄の可変表示態様などにより遊技者に報知するための特定演出が実行されることがある。この実施の形態では、「滑り」、「擬似連」、「イントロ」、「発展チャンス目」、「発展チャンス目終了」といった特定演出が実行可能に設定されている。なお、この実施の形態における特定演出は、対応する演出動作が実行されるか否か応じて特図変動時間が変化するものであればよい。例えば、ある特定演出が実行される場合には、その特定演出が実行されない場合に比べて、特図変動時間が長くなるものであればよい。 In addition, during the variable display of decorative symbols, unlike reach production, there is a possibility that the decorative symbols may be derived and displayed in the reach state, and that the variable display result may be a “hit”, There may be a case where a specific effect for informing the player is given in accordance with a variable display mode of the decorative design. In this embodiment, specific effects such as “sliding”, “pseudo-continuous”, “intro”, “development opportunity”, and “end of development opportunity” are set to be executable. In addition, the specific effect in this embodiment should just change a special figure fluctuation time according to whether a corresponding effect operation is performed. For example, when a specific effect is executed, it is only necessary that the special figure change time becomes longer than when the specific effect is not executed.

「滑り」の特定演出では、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rにおける全部にて飾り図柄を変動させる全図柄変動を行ってから、2つ以上の飾り図柄表示部(例えば「左」及び「右」の飾り図柄表示部5L、5Rなど)にて飾り図柄を仮停止表示させた後、その仮停止表示した飾り図柄表示部のうち所定数(例えば「1」又は「2」)の飾り図柄表示部(例えば「左」の飾り図柄表示部5Lと「右」の飾り図柄表示部5Rのいずれか一方又は双方)にて飾り図柄を再び変動させた後に停止表示させることで、停止表示する飾り図柄を変更させる演出表示が行われる。なお、特定演出における飾り図柄の仮停止表示では、飾り図柄が停留して表示される一方で、例えば揺れ変動表示を行うことや短時間の停留だけで直ちに飾り図柄を再変動させることなどによって、遊技者に停止表示された飾り図柄が確定しない旨を報知すればよい。あるいは、仮停止表示でも、停止表示された飾り図柄が確定したと遊技者が認識する程度に飾り図柄を停留させてから、飾り図柄を再変動させるようにしてもよい。

In the specific effect of “sliding”, after performing all symbol variations that change the ornament symbols in all of the “left”, “middle”, and “right” ornament

「擬似連」の特定演出では、特別図柄や飾り図柄の可変表示を開始するための第1開始条件あるいは第2開始条件が1回成立したことに対応して、全図柄変動が開始されてから、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rの全部にて順次に又は同時に飾り図柄を仮停止表示させた後、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rの全部にて飾り図柄を再び変動させる再可変表示動作(再変動)を、所定回(例えば最大3回まで)実行する演出動作である。一例として、「擬似連」の特定演出では、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rにて、擬似連チャンス目として予め定められた複数種類の飾り図柄の組合せのいずれかが仮停止表示される。そして、再変動の回数が多くなるに従って、可変表示結果が「大当り」となる割合が高くなるように設定されていればよい。これにより、遊技者は、擬似連チャンスのいずれかが仮停止表示されることで、「擬似連」の特定演出が行われると認識でき、再変動の回数が多くなるに従って、可変表示結果が「大当り」となる期待感が高められる。この実施の形態では、「擬似連」の特定演出において、再変動が1回〜3回行われることにより、第1開始条件あるいは第2開始条件が1回成立したことに基づき、飾り図柄の可変表示があたかも2回〜4回続けて開始されたかのように見せることができる。

In the “pseudo-ream” specific production, all symbol fluctuations are started in response to the first start condition or the second start condition for starting the variable display of special symbols and decorative symbols being established once. , “Left”, “Medium”, “Right” decorative symbols are displayed on all 5 L, 5 C, 5 R sequentially or simultaneously, and then “Left”, “Middle”, “Right” "Revariable display operation (revariation) for changing the decorative symbols again in all of the decorative

「擬似連」の特定演出が実行される飾り図柄の可変表示中には、擬似連続変動の進行に伴って、例えば画像表示装置5の表示画面における所定位置に予め用意されたキャラクタを示す演出画像を表示することや、スピーカ8L、8Rから所定の音声(特別音)を出力させること、遊技効果ランプ9を所定の点灯パターンで点灯させること、遊技領域内あるいは遊技領域外に設けられた演出用役物が備える複数の可動部材を動作させることといった、所定の演出動作が実行されてもよい。一例として、全部の飾り図柄表示部5L、5C、5Rにて飾り図柄を仮停止表示させた後、全部の飾り図柄表示部5L、5C、5Rにて飾り図柄を再可変表示させるときには、キャラクタを示す演出画像の表示、特別音の出力、ランプの点灯、可動部材の動作のうち、いずれか1つ、あるいは、複数の動作を組み合わせた演出動作が行われることにより、擬似連続変動が行われることを認識可能に報知するようにしてもよい。

During the variable display of the decorative pattern in which the specific effect of “pseudo-continuation” is executed, an effect image showing a character prepared in advance at a predetermined position on the display screen of the

「イントロ」の特定演出では、全図柄変動が開始されてから、例えば飾り図柄がリーチ表示状態で導出表示される以前に、リーチ演出にて行われる演出表示の導入部分といった、リーチ演出と予め関連づけられた所定の演出表示が行われる。一例として、「イントロ」の特定演出では、スーパーリーチ演出にて行われる演出表示の導入部分に相当する演出表示が行われる。こうした「イントロ」の特定演出が実行されることにより、飾り図柄がリーチ表示状態で導出表示された後にノーマルリーチよりも高い確率で「大当り」となるスーパーリーチ演出が実行されることに対する、遊技者の期待感が高められる。 In the specific effect of “Intro”, it is associated with the reach effect in advance, such as the introduction part of the effect display that is performed in the reach effect, for example, before the decorative symbol is derived and displayed in the reach display state after all the symbol changes are started. The predetermined production display is performed. As an example, in the specific effect of “Intro”, an effect display corresponding to the introduction part of the effect display performed in the super reach effect is performed. By executing such a specific effect of “Intro”, the player's response to the fact that the super-reach effect is executed with a higher probability of “hit” than the normal reach after the decorative symbol is derived and displayed in the reach display state. Expectation is enhanced.

「発展チャンス目」の特定演出では、全図柄変動が開始されてから、全部の飾り図柄表示部5L、5C、5Rにて、予め定められた発展チャンス目を構成する飾り図柄を仮停止表示させた後、飾り図柄がリーチ表示状態で導出表示されて所定のリーチ演出が開始される。一例として、「発展チャンス目」の特定演出では、「左」、「中」、「右」の飾り図柄表示部5L、5C、5Rにて、発展チャンス目として予め定められた複数種類の飾り図柄の組合せのいずれかが仮停止表示される。これにより、遊技者は、複数種類の発展チャンス目のいずれかが仮停止表示されたときに、飾り図柄がリーチ表示状態で導出表示される可能性があることや、可変表示結果が「大当り」となる可能性があることを認識でき、飾り図柄がリーチ表示状態で導出表示される期待感や、可変表示結果が「大当り」となる期待感が高められる。

In the specific effect of “Development Opportunity”, after all the symbol changes are started, the decorative symbols constituting the predetermined development opportunity are temporarily displayed on all the decorative

「発展チャンス目終了」の特定演出では、「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにおける全部にて飾り図柄を変動させてから、全部の飾り図柄表示部5L、5C、5Rにて、発展チャンス目として予め定められた組合せの飾り図柄を、確定飾り図柄として停止表示(最終停止表示)させる演出表示が行われる。一例として、「発展チャンス目終了」の特定演出では、「発展チャンス目」の特定演出で仮停止表示される発展チャンス目のいずれかが、確定飾り図柄として停止表示され、飾り図柄の可変表示が終了する。こうして、発展チャンス目のいずれかが導出表示されたときには、「発展チャンス目」の特定演出により飾り図柄がリーチ表示状態で導出表示されることもあれば、「発展チャンス目終了」の特定演出により飾り図柄の可変表示が終了することもある。これにより、発展チャンス目のいずれかが導出表示(仮停止表示)されたときに、飾り図柄がリーチ表示状態で導出表示されることに対する期待感を高め、「発展チャンス目」の特定演出により飾り図柄がリーチ表示状態で導出表示されたときには、飾り図柄の可変表示が継続しつつ、可変表示結果が「大当り」となる可能性があることから、遊技者の喜悦感を高めることができる。

In the specific production of “end of development chance”, the decorative symbols are changed in all of the “left”, “middle”, and “right” decorative

さらに、飾り図柄の可変表示中には、リーチ演出や特定演出とは異なり、例えば所定のキャラクタ画像やメッセージ画像を表示することなどといった、飾り図柄の可変表示態様以外の表示態様により、飾り図柄の可変表示状態がリーチ状態となる可能性があることや、可変表示結果が「大当り」となる可能性があることを、遊技者に報知するための予告演出が実行されることがある。例えば、「キャラクタ表示」、「ステップアップ画像」、「背景変更」といった予告演出が実行可能に設定されていればよい。なお、予告演出は、対応する演出動作が実行されるか否かによって特図変動時間に変化が生じないものであればよい。「キャラクタ表示」の予告演出では、「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにおける全部にて飾り図柄を変動させてから、2つ以上の飾り図柄表示部(例えば「左」及び「右」の飾り図柄表示部5L、5Rなど)にて飾り図柄を導出表示させる以前に、画像表示装置5の表示領域における所定位置に予め用意されたキャラクタ画像を表示させる演出表示が行われる。「ステップアップ画像」の予告演出では、「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにおける全部にて飾り図柄を変動させてから、2つ以上の飾り図柄表示部にて飾り図柄を導出表示させる以前に、画像表示装置5の表示領域にて、予め用意された複数種類の演出画像を所定の順番に従って切り替えて表示させる演出表示が行われることがある。なお、「ステップアップ画像」の予告演出では、予め用意された複数種類の演出画像のうちいずれか1つ(例えば所定の順番において最初に表示される演出画像など)が表示された後、演出画像が切り替えられることなく、予告演出における演出表示を終了させることがあるようにしてもよい。「背景変更」の予告演出では、画像表示装置5の表示領域における背景画像の表示を、複数種類のいずれかに変更させる演出表示が行われる。

Furthermore, during the variable display of the decorative pattern, unlike the reach effect or the specific effect, for example, by displaying the decorative pattern in a display mode other than the variable display mode of the decorative pattern, such as displaying a predetermined character image or message image. A notice effect may be executed to notify the player that the variable display state may become a reach state and that the variable display result may be a “hit”. For example, the notice effect such as “character display”, “step-up image”, and “background change” may be set to be executable. Note that the notice effect may be any one that does not change in the special figure fluctuation time depending on whether or not the corresponding effect operation is executed. In the notice effect of “character display”, two or more decorative symbols are displayed after the decorative symbols are changed in all of the “left”, “middle”, and “right” decorative

特図ゲームにおける確定特別図柄として、ハズレ図柄となる特別図柄が停止表示される場合には、飾り図柄の可変表示が開始されてから、飾り図柄の可変表示状態がリーチ状態とならずに、所定の非リーチ組合せとなる確定飾り図柄や、複数種類の発展チャンス目のいずれかとなる確定飾り図柄が、停止表示されることがある。このような飾り図柄の可変表示態様は、可変表示結果が「ハズレ」となる場合における「非リーチ」(「通常ハズレ」ともいう)の可変表示態様と称される。 If a special symbol that will be a lost symbol is stopped and displayed as a special symbol to be confirmed in the special symbol game, the decorative symbol variable display state will not reach the reach state after the variable symbol variable display starts. There are cases where a fixed decorative symbol that is a non-reach combination or a fixed decorative symbol that is one of a plurality of types of development chances is stopped and displayed. Such a decorative display variable display mode is referred to as a “non-reach” (also referred to as “normal loss”) variable display mode when the variable display result is “losing”.

特図ゲームにおける確定特別図柄として、ハズレ図柄となる特別図柄が停止表示される場合には、飾り図柄の可変表示が開始されてから、飾り図柄の可変表示状態がリーチ状態となったことに対応して、リーチ演出が実行された後に、あるいは、リーチ演出が実行されずに、所定のリーチハズレ組合せとなる確定飾り図柄が停止表示されることがある。このような飾り図柄の可変表示結果は、可変表示結果が「ハズレ」となる場合における「リーチ」(「リーチハズレ」ともいう)の可変表示態様と称される。 When a special symbol that becomes a losing symbol is stopped and displayed as a confirmed special symbol in the special symbol game, it corresponds to the fact that the decorative symbol variable display state has reached the reach state after the decorative symbol variable display has started. Then, after the reach effect is executed, or when the reach effect is not executed, a confirmed decorative pattern that becomes a predetermined reach-losing combination may be stopped and displayed. Such a variable display result of the decorative design is referred to as a variable display mode of “reach” (also referred to as “reach lose”) when the variable display result is “losing”.

特図ゲームにおける確定特別図柄として、15ラウンド大当り図柄となる特別図柄のうち通常大当り図柄である「3」の数字を示す特別図柄が停止表示される場合には、飾り図柄の可変表示状態がリーチ状態となったことに対応して、所定のリーチ演出が実行された後に、所定の通常大当り組合せとなる確定飾り図柄が停止表示される。ここで、通常大当り組合せとなる確定飾り図柄は、例えば画像表示装置5における「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにて可変表示される図柄番号が「1」〜「8」の飾り図柄のうち、図柄番号が偶数「2」、「4」、「6」、「8」である飾り図柄のいずれか1つが、「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにて所定の有効ライン上に揃って停止表示されるものであればよい。このように通常大当り組合せを構成する図柄番号が偶数「2」、「4」、「6」、「8」である飾り図柄は、通常図柄(「非確変図柄」ともいう)と称される。そして、特図ゲームにおける確定特別図柄が通常大当り図柄となることに対応して、所定のリーチ演出が実行された後に、通常大当り組合せの確定飾り図柄が停止表示される飾り図柄の可変表示態様は、可変表示結果が「大当り」となる場合における「通常」(「通常大当り」ともいう)の可変表示態様(大当り種別ともいう)と称される。こうして「通常」の可変表示態様により可変表示結果が「大当り」となった後には、15ラウンド大当り遊技状態に制御され、その15ラウンド大当り状態が終了すると、時短状態又は通常状態に制御されることになる。

When the special symbol indicating the number “3”, which is a normal big hit symbol, is stopped and displayed as a special symbol to be confirmed in the special figure game as the 15 round big hit symbol, the variable symbol display state of the decorative symbol is reached. Corresponding to the state, after a predetermined reach effect is executed, a predetermined decorative symbol that is a predetermined normal jackpot combination is stopped and displayed. Here, for example, the symbol numbers that are variably displayed on the “left”, “middle”, and “right” decorative

特図ゲームにおける確定特別図柄として、15ラウンド大当り図柄となる特別図柄のうち確変大当り図柄である「7」の数字を示す特別図柄が停止表示される場合には、飾り図柄の可変表示状態がリーチ状態となったことに対応して、大当り種別が「通常」である場合と同様のリーチ演出が実行された後に、所定の確変大当り組合せとなる確定飾り図柄が停止表示されることがある。ここで、確変大当り組合せとなる確定飾り図柄は、例えば画像表示装置5における「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにて可変表示される図柄番号が「1」〜「8」の飾り図柄のうち、図柄番号が奇数「1」、「3」、「5」、「7」である飾り図柄のいずれか1つが、「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにて所定の有効ライン上に揃って停止表示されるものであればよい。このように確変大当り組合せを構成する図柄番号が奇数「1」、「3」、「5」、「7」である飾り図柄は、確変図柄と称される。そして、特図ゲームにおける確定特別図柄が確変大当り図柄となることに対応して、リーチ演出が実行された後に、確変大当り組合せの確定飾り図柄が停止表示される飾り図柄の可変表示態様は、可変表示結果が「大当り」となる場合における「第1確変」の可変表示態様(大当り種別ともいう)と称される。こうして「第1確変」の可変表示態様により可変表示結果が「大当り」となった後には、15ラウンド大当り状態に制御され、その15ラウンド大当り状態が終了すると、確変状態に制御されることになる。

When the special symbol indicating the number “7”, which is the probability variable big hit symbol, is stopped and displayed as a special symbol to be confirmed in the special figure game as a 15-round big hit symbol, the variable display state of the decorative symbol is reached. Corresponding to the state, after the reach effect similar to the case where the big hit type is “normal” is executed, a fixed decorative symbol that becomes a predetermined probability variation big hit combination may be stopped and displayed. Here, the confirmed decorative symbols that are the probable big hit combinations are, for example, symbol numbers that are variably displayed on the decorative

特図ゲームにおける確定特別図柄として、15ラウンド大当り図柄となる特別図柄のうち確変大当り図柄である「7」の数字を示す特別図柄が停止表示される場合には、飾り図柄の可変表示状態がリーチ状態となったことに対応して、可変表示態様が「通常」である場合とは異なるリーチ演出が実行された後に、所定の確変大当り組合せとなる確定飾り図柄が停止表示されることがある。このように特図ゲームにおける確定特別図柄が確変大当り図柄となることに対応して、飾り図柄の可変表示態様が「通常」である場合とは異なるリーチ演出が実行された後に、確変大当り組合せの確定飾り図柄が停止表示される飾り図柄の可変表示態様は、可変表示結果が「大当り」となる場合における「第2確変」の可変表示態様(大当り種別ともいう)と称される。こうして「第2確変」の可変表示態様により可変表示結果が「大当り」となった後には、15ラウンド大当り状態に制御され、その15ラウンド大当り状態が終了すると、確変状態に制御されることになる。 When the special symbol indicating the number “7”, which is the probability variable big hit symbol, is stopped and displayed as a special symbol to be confirmed in the special figure game as a 15-round big hit symbol, the variable display state of the decorative symbol is reached. Corresponding to the state, after the reach effect different from the case where the variable display mode is “normal” is executed, the fixed decorative symbol that becomes a predetermined probability variation big hit combination may be stopped and displayed. In this way, in response to the confirmed special symbol in the special figure game becoming a probable big hit symbol, after the reach effect different from the case where the decorative symbol variable display mode is “normal” is executed, The variable display mode of the decorative pattern in which the fixed decorative pattern is stopped and displayed is referred to as a “second probability change” variable display mode (also referred to as a jackpot type) when the variable display result is “big hit”. Thus, after the variable display result is “big hit” by the variable display mode of “second positive change”, the control is made to the 15 round big hit state, and when the 15 round big hit state is finished, the variable change state is controlled to the positive change state. .

特図ゲームにおける確定特別図柄として、15ラウンド大当り図柄となる特別図柄のうち確変大当り図柄である「7」の数字を示す特別図柄が停止表示される場合には、飾り図柄の可変表示状態がリーチ状態となったことに対応して、飾り図柄の可変表示態様が「通常」である場合と同様のリーチ演出が実行された後に、通常大当り組合せの確定飾り図柄が停止表示されることがある。このように特図ゲームにおける確定特別図柄が確変大当り図柄となることに対応して、飾り図柄の可変表示態様が「通常」である場合と同様のリーチ演出が実行された後に、通常大当り組合せの確定飾り図柄が停止表示される飾り図柄の可変表示態様は、可変表示結果が「大当り」となる場合における「第3確変」の可変表示態様(大当り種別ともいう)と称される。こうして「第3確変」の可変表示態様により可変表示結果が「大当り」となった後には、15ラウンド大当り状態に制御され、その15ラウンド大当り状態が終了すると、確変状態に制御されることになる。 When the special symbol indicating the number “7”, which is the probability variable big hit symbol, is stopped and displayed as a special symbol to be confirmed in the special figure game as a 15-round big hit symbol, the variable display state of the decorative symbol is reached. Corresponding to the state, after the reach effect similar to the case where the decorative symbol variable display mode is “normal” is performed, the fixed symbol combination of the normal jackpot combination may be stopped and displayed. In this way, in response to the confirmed special symbol in the special figure game becoming a probable big hit symbol, after the reach effect similar to the case where the variable display mode of the decorative symbol is “normal” is executed, The decorative display variable display mode in which the fixed decorative design is stopped and displayed is referred to as a “third probability change” variable display mode (also referred to as a jackpot type) when the variable display result is “big hit”. Thus, after the variable display result is “big hit” by the variable display mode of “third probability change”, the game is controlled to the 15 round big hit state, and when the 15 round big hit state is finished, it is controlled to the positive change state. .

このように、可変表示結果が「大当り」となるときの大当り種別が「第1確変」や「第2確変」である場合には、飾り図柄の可変表示にて確変大当り組合せとなる確定飾り図柄が停止表示されることで、15ラウンド大当り状態に制御された後に確変状態となることが確定する。その一方で、可変表示結果が「大当り」となるときの大当り種別が「第3確変」である場合には、大当り種別が「通常」となる場合と同様に、飾り図柄の可変表示にて通常大当り組合せとなる確定飾り図柄が停止表示される。そのため、大当り種別が「第3確変」である場合には、確変状態となるか否かを、飾り図柄の可変表示結果からは遊技者が認識することはできない。すなわち、確変大当り組合せとなる確定飾り図柄は、大当り遊技状態に制御されることが確定する特定表示結果に含まれるとともに、確変状態に制御されることが確定する特別表示結果に含まれる。その一方で、通常大当り組合せとなる確定飾り図柄は、確変状態に制御されることが確定しない特別表示結果以外の特定表示結果(非特別表示結果)に含まれる。 In this way, when the big hit type when the variable display result is “big hit” is “first probability variation” or “second probability variation”, the fixed decorative symbol that becomes the probability variation big hit combination by variable display of the decorative symbol Is stopped and displayed, it is determined that the probability change state is reached after being controlled to the 15 round big hit state. On the other hand, when the big hit type when the variable display result is “big hit” is “third probability variation”, the variable symbol display is normally performed in the same manner as when the big hit type is “normal”. The confirmed decorative pattern that is a jackpot combination is stopped and displayed. Therefore, when the big hit type is “third probability variation”, the player cannot recognize whether or not the probability variation state is obtained from the variable display result of the decorative symbols. That is, the confirmed decorative symbol that becomes the probability variation jackpot combination is included in the specific display result that is determined to be controlled to the jackpot gaming state, and is included in the special display result that is determined to be controlled to the probability variation state. On the other hand, a confirmed decorative pattern that is normally a big hit combination is included in a specific display result (non-special display result) other than a special display result that is not determined to be controlled in a certain variation state.

特図ゲームにおける確定特別図柄として、2ラウンド大当り図柄となる「1」の数字を示す特別図柄が停止表示される場合には、飾り図柄の可変表示状態がリーチ状態とならずに、所定の非リーチ組合せとなる確定飾り図柄が停止表示されることや、複数種類の発展チャンス目のいずれかとなる確定飾り図柄が停止表示されること、あるいは、複数種類の突確チャンス目として予め定められた飾り図柄の組合せのいずれかとなる確定飾り図柄が停止表示されることがある。また、特図ゲームにおける確定特別図柄として、2ラウンド大当り図柄となる「1」の数字を示す特別図柄が停止表示される場合には、飾り図柄の可変表示状態がリーチ状態となったことに対応して、所定のリーチ演出が実行された後に、所定のリーチハズレ組合せとなる確定飾り図柄が停止表示されることがある。このように特図ゲームにおける確定特別図柄が2ラウンド大当り図柄である「1」の数字を示す特別図柄となることに対応して、各種の確定飾り図柄が停止表示される飾り図柄の可変表示態様は、可変表示結果が「大当り」となる場合における「突確」(「突確大当り」あるいは「突然確変大当り」ともいう)の可変表示態様(大当り種別ともいう)と称される。こうして「突確」の可変表示態様により可変表示結果が「大当り」となった後には、2ラウンド大当り状態に制御され、その2ラウンド大当り状態が終了すると、確変状態に制御されることになる。 When a special symbol indicating the number “1” that is a two-round jackpot symbol is stopped and displayed as a confirmed special symbol in the special symbol game, the decorative symbol variable display state does not reach the reach state, and a predetermined non- A fixed decorative symbol that is a reach combination is stopped and displayed, a fixed decorative symbol that is one of multiple types of development chances is stopped or displayed, or a decorative symbol that is preset as multiple types of chances of chance There is a case where a fixed decorative symbol that is one of the combinations is stopped and displayed. In addition, when the special symbol indicating the number “1”, which is a two-round jackpot symbol, is stopped and displayed as a confirmed special symbol in the special symbol game, the variable symbol display state of the decorative symbol is changed to the reach state. Then, after a predetermined reach effect is executed, a confirmed decorative pattern that becomes a predetermined reach-losing combination may be stopped and displayed. In this way, in response to the confirmed special symbol in the special symbol game becoming a special symbol indicating the number “1”, which is a two-round jackpot symbol, various decorative decorative variable display modes in which various confirmed decorative symbols are stopped and displayed. Is referred to as a variable display mode (also referred to as a jackpot type) of “surprise accuracy” (also referred to as “sudden probability big hit” or “sudden probability change big hit”) when the variable display result is “big hit”. Thus, after the variable display result is “big hit” by the variable display mode of “surprise accuracy”, it is controlled to the two round big hit state, and when the two round big hit state is finished, it is controlled to the probability changing state.

特図ゲームにおける確定特別図柄として、小当り図柄となる「5」の数字を示す特別図柄が停止表示される場合には、飾り図柄の可変表示態様が「突確」である場合と同様にして飾り図柄の可変表示が行われた後、所定の非リーチ組合せとなる確定飾り図柄が停止表示されることや、複数種類の発展チャンス目のいずれかとなる確定飾り図柄が停止表示されること、あるいは、所定のリーチハズレ組合せとなる確定飾り図柄が停止表示されることがある。このように特図ゲームにおける確定特別図柄が小当り図柄である「5」の数字を示す特別図柄となることに対応して、各種の確定飾り図柄が停止表示される飾り図柄の可変表示態様は、「小当り」の可変表示態様(小当り種別ともいう)と称される。ここで、複数種類の突確チャンス目のいずれかとなる確定飾り図柄は、飾り図柄の可変表示態様が「突確」となる場合に限り停止表示され、可変表示態様が「小当り」となる場合などには確定飾り図柄として停止表示されない。すなわち、飾り図柄の可変表示にて突確チャンス目となる確定飾り図柄が停止表示された場合には、「突確」の可変表示態様により可変表示結果が「大当り」となることが確定する。可変表示結果が「小当り」となった後には、2ラウンド大当り状態と同様の可変入賞動作が行われる小当り遊技状態に制御され、その小当り遊技状態が終了すると、遊技状態が変更されないことから、可変表示結果が「小当り」となる以前の遊技状態が継続する。なお、可変表示結果が「小当り」となる可変表示ゲームに対応して、確変状態や時短状態を終了する旨の判定がなされた場合には、小当り遊技状態の終了後に、通常状態へと制御されることになる。 When a special symbol indicating the number “5” as a small hit symbol is stopped and displayed as a confirmed special symbol in the special symbol game, the ornament is displayed in the same manner as when the variable display mode of the decorative symbol is “surprise”. After the variable display of the symbol is performed, the fixed decorative symbol that is a predetermined non-reach combination is stopped, the fixed decorative symbol that is one of multiple types of development opportunities is stopped, or There is a case where a fixed decorative symbol that is a predetermined reach-losing combination is stopped and displayed. In this way, in response to the confirmed special symbol in the special symbol game becoming a special symbol indicating the number “5” as the small hit symbol, the variable display mode of the decorative symbols on which various confirmed decorative symbols are stopped and displayed is as follows. , “Small hit” variable display mode (also referred to as “small hit type”). Here, the confirmed decorative pattern that is one of the multiple types of random chances is stopped only when the variable display mode of the decorative pattern is “Accuracy”, and when the variable display mode is “Small”. Is not stopped and displayed as a confirmed decorative pattern. In other words, when a fixed decorative pattern that is a chance of a chance of success is stopped and displayed in a variable display of decorative symbols, it is determined that the variable display result is “big hit” by the variable display mode of “accuracy”. After the variable display result is “small hit”, the game is controlled to the small hit gaming state in which the variable winning action similar to the two round big hit state is performed, and when the small hit gaming state ends, the gaming state is not changed. Therefore, the gaming state before the variable display result becomes “small hit” continues. If it is determined that the probability change state or the short-time state is to be ended in response to the variable display game in which the variable display result is “small hit”, the normal state is returned after the end of the small hit gaming state. Will be controlled.

可変表示結果が「大当り」となるときの大当り種別が「通常」、「第1確変」、「第3確変」のいずれかである場合には、飾り図柄の可変表示中に、特定変動表示としての変動中昇格演出が実行されることがある。変動中昇格演出では、画像表示装置5における「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rの有効ライン上に通常大当り組合せとなる飾り図柄を仮停止表示させた後に、例えば「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rにて同一の飾り図柄が揃った状態で再び変動させ、確変大当り組合せとなる飾り図柄と、通常大当り組合せとなる飾り図柄のうちいずれかを、確定飾り図柄として停止表示(最終停止表示)させる。ここで、飾り図柄の可変表示態様が「通常」や「第3確変」であることに対応して変動中昇格演出が実行される場合には、その変動中昇格演出として、仮停止表示させた飾り図柄を再変動させた後に通常大当り組合せとなる確定飾り図柄を停止表示する変動中昇格失敗演出が行われる。これに対して、可変表示態様が「第1確変」であることに対応して変動中昇格演出が実行される場合には、その変動中昇格演出として、仮停止表示させた飾り図柄を再変動させた後に確変大当り組合せとなる確定飾り図柄を停止表示する変動中昇格成功演出が行われる。

If the big hit type when the variable display result is “big hit” is any one of “normal”, “first probability variation”, or “third probability variation”, a specific variation display is made during variable display of decorative symbols. Promotional effects may be executed during the change. In the fluctuating promotion effect, a decorative symbol that is normally a big hit combination is temporarily displayed on the effective lines of the “left”, “middle”, and “right” decorative

可変表示結果が「大当り」となるときの大当り種別が「通常」と「第3確変」のいずれかである場合には、可変表示結果が停止表示されてから、15ラウンド大当り状態に制御された後、その15ラウンド大当り状態が終了するまでの期間にて、確変状態に制御するか否かの報知演出としての大当り中昇格演出が実行される。ここで、大当り中昇格演出が実行されるタイミングは、可変表示結果が停止表示されてから、15ラウンド大当り状態における最初のラウンドが開始される以前の期間であってもよいし、15ラウンド大当り状態においていずれかのラウンドが実行中の期間であってもよいし、15ラウンド大当り状態においていずれかのラウンドが終了してから次のラウンドが開始されるまでの期間であってもよいし、15ラウンド大当り状態において最終のラウンドが終了してから、次の可変表示ゲームが開始されるまでの期間であってもよい。あるいは、15ラウンド大当り状態の終了後における最初の特別図柄や飾り図柄の変動中に、大当り中昇格演出に相当する演出動作が行われるようにしてもよい。15ラウンド大当り状態において最終のラウンドが終了してから実行される大当り中昇格演出を、特に「エンディング昇格演出」ということもある。 When the big hit type when the variable display result is “big hit” is either “normal” or “third probability variation”, the variable display result is stopped and displayed, and then controlled to the 15 round big hit state. Thereafter, during the period until the 15-round big hit state is completed, a promotion effect during the big hit is executed as a notification effect as to whether or not to control to the probable change state. Here, the timing at which the jackpot promotion effect is executed may be a period before the start of the first round in the 15 round big hit state after the variable display result is stopped and displayed, or the 15 round big hit state May be a period during which any one of the rounds is being executed, or may be a period from the end of any round to the start of the next round in the 15 round big hit state, or 15 rounds. It may be a period from the end of the last round in the big hit state to the start of the next variable display game. Alternatively, an effect operation corresponding to the promotion effect during the big hit may be performed during the fluctuation of the first special symbol or decorative design after the end of the 15th round big hit state. The jackpot promotion effect executed after the final round in the 15 round jackpot state is sometimes referred to as “ending promotion effect” in particular.

大当り中昇格演出には、確定飾り図柄が通常大当り組合せであるにもかかわらず遊技状態が確変状態となる昇格がある旨を報知する大当り中昇格成功演出と、確変状態となる昇格がない旨を報知する大当り中昇格失敗演出とがある。一例として、大当り中昇格演出では、画像表示装置5の表示領域にて飾り図柄を可変表示させ、通常図柄と、確変図柄のうちいずれかを、演出表示結果として停止表示させる。このとき、大当り中昇格失敗演出では通常図柄を演出表示結果として停止表示させる一方、大当り中昇格成功演出では確変図柄を演出表示結果として停止表示させればよい。他の一例として、大当り中昇格演出では、画像表示装置5の表示領域にて飾り図柄とは異なる所定の演出画像が表示されてもよい。例えば、大当り中昇格演出として、ルーレットゲームを示す演出画像の表示を行う。このとき、大当り中昇格失敗演出では回転するルーレットに投入されたボールが「偶数」に入って「残念!」という演出画像の表示を行う一方、大当り中昇格成功演出では回転するルーレットに投入されたボールが「奇数」に入って「確変!」という演出画像の表示を行う。特図ゲームにおける確定特別図柄として「7」の数字を示す特別図柄が停止表示されることに対応して、「第3確変」の大当り種別により可変表示結果が「大当り」となった後には、大当り中昇格成功演出を実行することにより、確変状態となる昇格がある旨を報知する。特図ゲームにおける確定特別図柄として「3」の数字を示す特別図柄が停止表示されることに対応して、「通常」の大当りにより可変表示結果が「大当り」となった後には、例えば大当り中昇格失敗演出が実行される一方で、大当り中昇格成功演出は実行されず、確変状態となる昇格がある旨の報知が行われない。

In the jackpot promotion effect, there is a jackpot promotion promotion effect that informs that there is a promotion that the gaming state becomes a probable change state even though the confirmed decorative pattern is a normal jackpot combination, and that there is no promotion that becomes a probable change state There is a promotion promotion failure during the jackpot to be notified. As an example, in the jackpot promotion effect, the decorative symbol is variably displayed in the display area of the

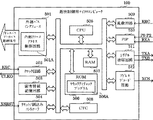

パチンコ遊技機1には、例えば図2に示すような電源基板10、主基板11、演出制御基板12、音声制御基板13、ランプ制御基板14、払出制御基板15、発射制御基板17といった、各種の制御基板が搭載されている。また、パチンコ遊技機1には、主基板11と演出制御基板12との間で伝送される各種の制御信号を中継するための中継基板18なども搭載されている。なお、音声制御基板13やランプ制御基板14は、演出制御基板12とは別個の独立した基板によって構成されてもよいし、演出制御基板12にまとめられて1つの基板として構成されてもよい。その他、パチンコ遊技機1の背面には、例えば情報端子基板やインタフェース基板などといった、各種の制御基板が配置されている。インタフェース基板は、パチンコ遊技機1に隣接してカードユニットが設置される場合に、払出制御基板15とカードユニットとの間に介在する制御基板である。

The

電源基板10は、主基板11、演出制御基板12、払出制御基板15等の各制御基板と独立して設置され、パチンコ遊技機1内の各制御基板及び機構部品が使用する電圧を生成する。例えば、電源基板10では、図3に示すように、AC24V、VLP(直流+24V)、VSL(直流+30V)、VDD(直流+12V)、VCC(直流+5V)及びVBB(直流+5V)を生成する。電源基板10は、例えば図3に示すように、変圧回路301と、直流電圧生成回路302と、電源監視回路303と、クリアスイッチ304とを備えて構成されている。また、電源基板10には、バックアップ電源となるコンデンサが設けられていてもよい。このコンデンサは、例えばVBB(直流+5V)の電源ラインから充電されるものであればよい。加えて、電源基板10には、パチンコ遊技機1内の各制御基板及び機構部品への電力供給を実行又は遮断するための電源スイッチが設けられていてもよい。あるいは、電源スイッチは、パチンコ遊技機1において、電源基板10の外に設けられていてもよい。

The

変圧回路301は、例えば商用電源が入力側(一次側)に印加されるトランスや、トランスの入力側に設けられた過電圧保護回路としてのバリスタなどを備えて構成されたものであればよい。ここで、変圧回路301が備えるトランスは、商用電源と電源基板10の内部とを電気的に絶縁するためのものであればよい。変圧回路301は、その出力電圧として、AC24Vを生成する。直流電圧生成回路302は、例えばAC24Vを整流素子で整流昇圧することによってVSLを生成する整流平滑回路を含んでいる。VSLは、ソレノイド駆動用の電源電圧として用いられる。また、直流電圧生成回路302は、例えばAC24Vを整流素子で整流することによってVLPを生成する整流回路を含んでいる。VLPは、遊技効果ランプ9等の発光体を点灯するための電源電圧として用いられる。加えて、直流電圧生成回路302は、例えばVSLに基づいてVDDおよびVCCを生成するDC−DCコンバータを含んでいる。このDC−DCコンバータは、例えば1つ又は複数のスイッチングレギュレータと、そのスイッチングレギュレータの入力側に接続された比較的大容量のコンデンサとを含み、外部からパチンコ遊技機1への電力供給が停止したときに、VSL、VDD、VBB等の直流電圧が比較的緩やかに低下するように構成されたものであればよい。VDDは、例えば図2に示すゲートスイッチ21、第1及び第2始動口スイッチ22A、22B、カウントスイッチ23といった、遊技媒体を検出する各種スイッチに供給され、これらのスイッチを作動させるために用いられる。

For example, the

図3に示すように、変圧回路301から出力されたAC24Vは、例えば所定のコネクタや電源ラインを介して、払出制御基板15へと伝送される。VLPは、例えば所定のコネクタや電源ラインを介して、ランプ制御基板14へと伝送される。VSL、VDD及びVCCは、例えば所定のコネクタや電源ラインを介して、主基板11、ランプ制御基板14及び払出制御基板15へと伝送される。VBBは、例えば所定のコネクタや電源ラインを介して、主基板11及び払出制御基板15へと伝送される。なお、演出制御基板12及び音声制御基板13には、ランプ制御基板14を経由して各電圧が供給されればよい。あるいは、演出制御基板12及び音声制御基板13には、ランプ制御基板14を経由することなく、電源基板10から直接に各電圧が供給されてもよい。

As shown in FIG. 3, AC24V output from the

電源監視回路303は、例えば停電監視リセットモジュールICを用いて構成され、電源断信号を出力する電源監視手段を実現する回路である。例えば、電源監視回路303は、パチンコ遊技機1において用いられる所定電圧(一例としてVLP)が所定値(一例として+20V)以下になった期間が、予め決められている時間(一例として56ミリ秒)以上継続したときに、電源断信号を出力する。あるいは、電源監視回路303は、パチンコ遊技機1において用いられる所定電圧が所定値以下になると、直ちに電源断信号を出力するようにしてもよい。電源断信号は、例えばローレベルとなることでオン状態となる電気信号であればよい。電源監視回路303から出力された電源断信号は、例えば電源基板10に搭載された出力ドライバ回路によって増幅された後に所定のコネクタや信号ラインを介して、払出制御基板15へと伝送され、払出制御基板15から主基板11へと伝送される。なお、外部からパチンコ遊技機1に供給される電力の供給停止を検出するための条件としては、パチンコ遊技機1において用いられる所定電圧が所定値以下になったことに限られず、外部からの電力が途絶えたことを検出できる任意の条件であればよい。例えば、AC24V等の交流波そのものを監視して交流波が途絶えたことを検出条件としてもよいし、交流波をデジタル化した信号を監視して、デジタル信号が平坦になったことをもって交流波が途絶えたことの検出条件としてもよい。

The

また、電源監視回路303は、例えば所定電圧(一例としてVCC)が所定値(一例として+5V強)以下になったときに、リセット信号を出力してもよい。リセット信号は、例えばローレベルとなることでオン状態となる電気信号であればよい。電源監視回路303から出力されたリセット信号は、例えば電源基板10に搭載された出力ドライバ回路によって増幅された後に所定のコネクタや信号ラインを介して、主基板11、ランプ制御基板14及び払出制御基板15へと伝送される。なお、演出制御基板12には、ランプ制御基板14を経由してリセット信号が伝送されればよい。さらに、リセット信号を出力する回路は、電源監視回路303とは別個に設けられたウォッチドッグタイマ内蔵IC、あるいはシステムリセットICなどを用いて構成されてもよい。

The power

パチンコ遊技機1への電力供給が停止するときには、電源監視回路303が、電源断信号を出力(ローレベルに設定)してから所定期間が経過したときに、リセット信号を出力(ローレベルに設定)する。ここでの所定期間は、例えば図2に示す主基板11に搭載されている遊技制御用マイクロコンピュータ100及び払出制御基板15に搭載されている払出制御用マイクロコンピュータ150が、所定の電源断処理を実行するのに十分な時間であればよい。すなわち、電源監視回路303は、停電信号としての電源断信号を出力した後、遊技制御用マイクロコンピュータ100及び払出制御用マイクロコンピュータ150が所定の電源断処理を実行完了してから、動作停止信号としてのリセット信号を出力(ローレベルに設定)する。電源監視回路303から出力されたリセット信号を受信した遊技制御用マイクロコンピュータ100や払出制御用マイクロコンピュータ150は、動作停止状態となり、各種の制御処理の実行が停止される。また、パチンコ遊技機1への電力供給が開始され、例えば所定電圧(一例としてVCC)が所定値(一例として+5V強)を超えたときに、電源監視回路303はリセット信号の出力を停止(ハイレベルに設定)する。

When the power supply to the

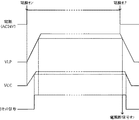

図4は、パチンコ遊技機1への電力供給が開始されたとき、及び電力供給が停止するときにおける、AC24V、VLP、VCC、リセット信号及び電源断信号の状態を、模式的に示すタイミング図である。図4に示すように、パチンコ遊技機1への電力供給が開始されたときに、VLP及びVCCは徐々に規定値(直流+24V及び直流+5V)に達する。このとき、VLPが第1の所定値を超えると、電源監視回路303は電源断信号の出力を停止(ハイレベルに設定)してオフ状態とする。また、VCCが第2の所定値を超えると、電源監視回路303はリセット信号の出力を停止(ハイレベルに設定)してオフ状態とする。他方、パチンコ遊技機1への電力供給が停止するときに、VLP及びVCCは徐々に低下する。このとき、VLPが第1の所定値にまで低下すると、電源監視回路303は電源断信号をオン状態として出力(ローレベルに設定)する。また、VCCが第2の所定値にまで低下すると、電源監視回路303はリセット信号をオン状態として出力(ローレベルに設定)する。

FIG. 4 is a timing diagram schematically showing the states of AC 24 V, VLP, VCC, reset signal, and power-off signal when power supply to the

図3に示す電源基板10が備えるクリアスイッチ304は、例えば押しボタン構造を有し、押下などの操作に応じてクリア信号を出力する。クリア信号は、例えばローレベルとなることでオン状態となる電気信号であればよい。クリアスイッチ304から出力されたクリア信号は、例えば所定のコネクタや信号ラインを介して、主基板11へと伝送され、主基板11から払出制御基板15へと伝送される。また、クリアスイッチ304の操作がなされていないときには、クリア信号の出力を停止(ハイレベルに設定)する。なお、クリアスイッチ304は、押しボタン構造以外の他の構成(例えばスライドスイッチ構造やトグルスイッチ構造、ダイヤルスイッチ構造など)であってもよい。

The

主基板11は、メイン側の制御基板であり、パチンコ遊技機1における遊技の進行を制御するための各種回路が搭載されている。主基板11は、主として、特図ゲームにおいて用いる乱数の設定機能、所定位置に配設されたスイッチ等からの信号の入力を行う機能、演出制御基板12や払出制御基板15などからなるサブ側の制御基板に宛てて、指令情報の一例となる制御コマンドを制御信号として出力して送信する機能、ホールの管理コンピュータに対して各種情報を出力する機能などを備えている。また、主基板11は、第1特別図柄表示装置4Aと第2特別図柄表示装置4Bを構成する各LED(例えばセグメントLED)などの点灯/消灯制御を行って第1特図や第2特図の可変表示を制御することや、普通図柄表示器20の点灯/消灯/発色制御などを行って普通図柄表示器20による普通図柄の可変表示を制御することといった、所定の表示図柄の可変表示を制御する機能も備えている。主基板11は、例えば図2に示すように、遊技制御用マイクロコンピュータ100と、制御用クロック生成回路111と、乱数用クロック生成回路112と、スイッチ回路114と、ソレノイド回路115とを備えている。また、主基板11には、遊技開始スイッチ31が設置されている。

The

ここで、制御用クロック生成回路111は、遊技制御用マイクロコンピュータ100の外部にて、所定周波数の発振信号となる制御用クロックCCLKを生成する。制御用クロック生成回路111により生成された制御用クロックCCLKは、例えば図7に示すような遊技制御用マイクロコンピュータ100の制御用外部クロック端子EXCを介してクロック回路502に供給される。乱数用クロック生成回路112は、遊技制御用マイクロコンピュータ100の外部にて、制御用クロックCCLKの発振周波数とは異なる所定周波数の発振信号となる乱数用クロックRCLKを生成する。乱数用クロック生成回路112により生成された乱数用クロックRCLKは、例えば図7に示すような遊技制御用マイクロコンピュータ100の乱数用外部クロック端子ERCを介して乱数回路509に供給される。一例として、乱数用クロック生成回路112により生成される乱数用クロックRCLKの発振周波数は、制御用クロック生成回路111により生成される制御用クロックCCLKの発振周波数以下となるようにすればよい。

Here, the control

スイッチ回路114は、遊技球検出用の各種スイッチからの検出信号を取り込んで遊技制御用マイクロコンピュータ100に伝送する。ソレノイド回路115は、遊技制御用マイクロコンピュータ100からのソレノイド駆動信号をソレノイド81、82に伝送する。遊技開始スイッチ31は、例えば押しボタン構造を有し、パチンコ遊技機1において遊技機用枠3を閉じて遊技者が通常遊技を行う状態でパチンコ遊技機1の外部から触れることのできない所定箇所に配設されていればよい。そして、例えばパチンコ遊技機1の電源投入時やシステムリセット時などに、パチンコ遊技機1の初期設定を行った後に遊技開始を指示するために操作される。なお、遊技開始スイッチ31は、押しボタン構造以外の他の構成(例えばスライドスイッチ構造やトグルスイッチ構造、ダイヤルスイッチ構造など)であってもよい。

The switch circuit 114 takes in detection signals from various switches for detecting game balls and transmits them to the

図2に示すように、主基板11には、ゲートスイッチ21、第1始動口スイッチ22A、第2始動口スイッチ22B及びカウントスイッチ23からの検出信号を伝送する配線が接続されている。なお、ゲートスイッチ21、第1始動口スイッチ22A、第2始動口スイッチ22B及びカウントスイッチ23は、例えばセンサと称されるものなどのように、遊技媒体としての遊技球を検出できる任意の構成を有するものであればよい。また、主基板11には、第1特別図柄表示装置4Aや第2特別図柄表示装置4B、普通図柄表示器20、第1保留表示器25A、第2保留表示器25B、普図保留表示器25Cなどの表示制御を行うための指令信号を伝送する配線が接続されている。さらに、主基板11には、普通電動役物用のソレノイド81や大入賞口扉用のソレノイド82などの駆動制御を行うための指令信号を伝送する配線が接続されている。

As shown in FIG. 2, wiring for transmitting detection signals from the

主基板11と演出制御基板12との間では、例えば主基板11から中継基板18を介して演出制御基板12へと向かう単一方向のみでシリアル通信を行うことにより、各種の制御コマンドが伝送される。演出制御基板12は、主基板11とは独立したサブ側の制御基板であり、中継基板18を介して主基板11から送信された制御コマンドを受信して、画像表示装置5、スピーカ8L、8R及び遊技効果ランプ9等の発光体といった演出用の電気部品(演出装置)を制御するための各種回路が搭載されている。すなわち、演出制御基板12は、画像表示装置5における表示動作や、スピーカ8L、8Rからの音声出力動作、遊技効果ランプ9等の発光体における点灯動作及び消灯動作などを制御する機能を備えている。演出制御基板12には、音声制御基板13やランプ制御基板14に制御信号を伝送する配線や、画像表示装置5に画像データ信号を伝送する配線などが接続されている。

Various control commands are transmitted between the

主基板11には、例えば中継基板18に対応して主基板側コネクタが設けられるとともに、この主基板側コネクタと遊技制御用マイクロコンピュータ100との間に、出力バッファ回路が接続されていてもよい。この出力バッファ回路は、例えば主基板11から中継基板18を介して演出制御基板12へ向かう方向にのみ制御信号を通過させることができ、中継基板18から主基板11への信号の入力を阻止する。したがって、演出制御基板12や中継基板18の側から主基板11の側に信号が伝わる余地はない。なお、主基板11と演出制御基板12との間に中継基板18を設けない構成としてもよい。これにより、主基板11と演出制御基板12との間における配線引き回しの自由度を高めることができる。

The

中継基板18には、例えば主基板11から演出制御基板12に対して制御信号を伝送するための配線に、伝送方向規制回路が設けられていればよい。伝送方向規制回路は、主基板11対応の主基板用コネクタにアノードが接続されるとともに演出制御基板12対応の演出制御基板用コネクタにカソードが接続されたダイオードと、一端がダイオードのカソードに接続されるとともに他端がグランド(GND)接続された抵抗とから構成されている。この構成により、伝送方向規制回路は、演出制御基板12から中継基板18への信号の入力を阻止して、主基板11から演出制御基板12へ向かう方向にのみ信号を通過させることができる。したがって、演出制御基板12の側から主基板11側に信号が伝わる余地はない。この実施の形態では、中継基板18において制御信号を伝送するための配線に伝送方向規制回路を設けるとともに、主基板11にて遊技制御用マイクロコンピュータ100と主基板側コネクタの間に出力バッファ回路を設けることで、外部から主基板11への不正な信号の入力を防止することができる。

For example, the relay board 18 may be provided with a transmission direction regulating circuit in a wiring for transmitting a control signal from the

主基板11と払出制御基板15との間では、例えば双方向でシリアル通信を行うことにより、各種の制御コマンドや通知信号が伝送される。払出制御基板15は、主基板11とは独立したサブ側の制御基板であり、主基板11から送信された制御コマンドや通知信号を受信して、払出モータ51による遊技球の払出動作を制御するための各種回路が搭載されている。すなわち、払出制御基板15は、払出モータ51による賞球の払出動作を制御する機能を備えている。また、払出制御基板15は、例えばインタフェース基板を介したカードユニットとの通信結果に応じて払出モータ51の駆動制御を行って、球貸し動作を制御する機能を備えていてもよい。払出制御基板15には、満タンスイッチ26や球切れスイッチ27からの検出信号を受信するための配線や、払出モータ位置センサ71や払出カウントスイッチ72、エラー解除スイッチ73からの検出信号を受信するための配線が接続されている。加えて、払出制御基板15には、払出モータ51における遊技球の払出制御を行うための指令信号を送信するための配線や、エラー表示用LED74における表示制御を行うための指令信号を送信するための配線、インタフェース基板を介してカードユニットとの間で通信を行うための配線などが接続されている。

Various control commands and notification signals are transmitted between the

ここで、満タンスイッチ26は、例えば遊技盤2の背面下方にて打球供給皿と余剰球受皿の間を連通する余剰球通路の側壁に設置され、余剰球受皿の満タンを検出するためのものである。賞球又は球貸し要求に基づく遊技球が多数払い出されて打球供給皿が満杯になり、遊技球が連絡口に到達した後、さらに遊技球が払い出されると、遊技球は余剰球通路を経て余剰球受皿へと導かれる。さらに遊技球が払い出されると、例えば所定の感知レバーが満タンスイッチ26を押圧してオンする。

Here, the

また、球切れスイッチ27は、例えば遊技盤2の背面にて遊技球を払出モータ51が設置された払出装置へと誘導する誘導レールの下流に設置され、誘導レールの下流にてカーブ樋を介して連通された2列の球通路内における遊技球の有無を検出するためのものである。一例として、球切れスイッチ27は、球通路に27〜28個の遊技球が存在することを検出できるような位置に係止片によって係止され、球貸しの一単位の最大払出個数(例えば100円分に相当する25個)以上が確保されていることを確認可能にする。なお、誘導レールは、遊技盤2の背面上方にて補給球としての遊技球を貯留する貯留タンクからの遊技球を払出装置へと誘導するものであり、球通路の下部には、払出モータ51が設置された払出装置が固定されている。

In addition, the ball break switch 27 is installed downstream of the guide rail that guides the game ball to the payout device in which the

エラー解除スイッチ73は、払出制御用マイクロコンピュータ150が所定のエラー状態に制御されているときに、ソフトウェアリセットによって、そのエラー状態を解除するためのスイッチである。エラー表示用LED74は、例えば7セグメントLEDにより構成され、払出制御用マイクロコンピュータ150にてセットされたエラーフラグなどに基づいて、各種のエラーに対応するエラーコードを表示するためのものである。

The error release switch 73 is a switch for releasing the error state by software reset when the payout control microcomputer 150 is controlled to a predetermined error state. The

図2に示す発射制御基板17は、操作ノブ30の操作量に応じて、所定の発射装置による遊技球の発射動作を制御するためのものである。発射制御基板17には、例えば電源基板10あるいは主基板11からの駆動信号を伝送する配線や、払出制御基板15及びインタフェース基板を介してカードユニットからの接続信号を伝送する配線、及び操作ノブ30からの配線が接続されるとともに、発射モータ61への配線が接続されている。なお、カードユニットからの接続信号は、払出制御基板15にて分岐されて発射制御基板17に伝送されてもよいし、カードユニットからインタフェース基板を介し、払出制御基板15を経由せずに発射制御基板17に伝送されてもよい。発射制御基板17は、操作ノブ30の操作量に対応して発射モータ61の駆動力を調整する。発射モータ61は、例えば発射制御基板17により調整された駆動力により発射バネを弾性変形させ、発射バネの付勢力を打撃ハンマに伝達して遊技球を打撃することにより、遊技球を操作ノブ30の操作量に対応した速度で遊技領域に向けて発射させる。

The

中継基板18を介して主基板11から演出制御基板12に対して送信される制御コマンドは、例えば電気信号として伝送される演出制御コマンドである。この実施の形態において、演出制御コマンドは、主基板11に搭載された遊技制御用マイクロコンピュータ100が備えるCPU505(図7参照)によって送信設定が行われ、その設定に基づいて遊技制御用マイクロコンピュータ100が備えるシリアル通信回路511(図7参照)の第2チャネル送信回路571B(図25参照)により、演出制御基板12に対して送信される。以下の説明では、主基板11から演出制御基板12に対する演出制御コマンドの送信動作に、こうした遊技制御用マイクロコンピュータ100に設けられたCPU505やシリアル通信回路511による一連の動作が含まれているものとする。この場合、演出制御基板12の側では、例えば演出制御用マイクロコンピュータ120のCPUが、主基板11から伝送されたシリアル信号形式の通信データを受信した際に発生する受信割込み要求に基づく割込み処理を実行することにより、演出制御コマンドを取り込んで所定のバッファ(例えば演出用受信コマンドバッファ)等に格納してもよい。なお、演出制御コマンドは、複数本の信号線(例えば8本の演出制御信号線)で主基板11から中継基板18を介し演出制御基板12に対して送信されてもよい。この場合には、演出制御コマンドを送信するための信号線に加えて、演出制御コマンドの取込みを要求する取込信号(演出制御INT信号)を送信するための信号線が配線されてもよい。

The control command transmitted from the

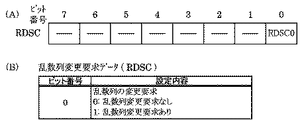

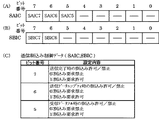

演出制御コマンドには、例えば画像表示装置5における画像表示動作を制御するために用いられる表示制御コマンドや、スピーカ8L、8Rからの音声出力を制御するために用いられる音声制御コマンド、遊技効果ランプ9といった発光体の点灯動作などを制御するために用いられるランプ制御コマンドが含まれている。図5(A)は、この実施の形態で用いられる表示制御コマンドの内容の一例を示す説明図である。表示制御コマンドは、例えば2バイト構成であり、1バイト目はMODE(コマンドの分類)を示し、2バイト目はEXT(コマンドの種類)を表す。MODEデータの先頭ビット(ビット番号[7])は必ず“1”とされ、EXTデータの先頭ビットは“0”とされる。なお、図5(A)に示された表示制御コマンドの形態は一例であって、他のコマンド形態を用いてもよい。また、この例では、表示制御コマンドが2バイト構成であるとしているが、表示制御コマンドを構成するバイト数は、1であってもよいし、3以上の複数であってもよい。

The effect control command includes, for example, a display control command used for controlling an image display operation in the

図5(A)に示す例において、コマンド8001Hは、第1特別図柄表示装置4Aによる特図ゲームにおける第1特図の変動開始を指定する第1変動開始コマンドである。コマンド8002Hは、第2特別図柄表示装置4Bによる特図ゲームにおける第2特図の変動開始を指定する第2変動開始コマンドである。コマンド81XXHは、特図ゲームにおける特別図柄の可変表示に対応して画像表示装置5における「左」、「中」、「右」の各飾り図柄表示部5L、5C、5Rで可変表示される飾り図柄などの変動パターンを指定する変動パターン指定コマンドである。ここで、XXHは不特定の16進数であることを示し、演出制御コマンドによる指示内容に応じて任意に設定される値であればよい。変動パターン指定コマンドでは、指定する変動パターンなどに応じて、異なるEXTデータが設定される。

In the example shown in FIG. 5A, the command 8001H is a first change start command for designating the start of change of the first special figure in the special figure game by the first special

この実施の形態では、第1及び第2変動開始コマンドと、変動パターン指定コマンドとを、互いに別個の演出制御コマンドとして用意している。これに対して、第1特図及び第2特図のいずれが変動開始となるかの指定内容と、変動パターンの指定内容とを、1つの演出制御コマンドにより特定可能となるように構成してもよい。一例として、変動開始となる特別図柄(第1特図あるいは第2特図)と変動パターンとの組合せに対応してEXTデータが設定される演出制御コマンドを用意して、その演出制御コマンドにより、変動開始となる特別図柄と変動パターンとを特定できるようにしてもよい。ここで、変動開始となる特別図柄と変動パターンとを1つの演出制御コマンドにより特定可能となるように構成した場合には、1つの変動パターンに対して、変動開始となる特別図柄(第1特図あるいは第2特図)に応じた2種類の演出制御コマンドを用意しなければならないことがある。これに対して、変動開始となる特別図柄を指定する演出制御コマンドと、変動パターンを指定する演出制御コマンドとを別個に用意すれば、変動開始となる特別図柄に対応した2種類の演出制御コマンドと、変動パターンの種類数に対応した個数の演出制御コマンドとを用意すればよく、予め用意するコマンドの種類や、コマンドテーブルの記憶容量などを、削減することができる。 In this embodiment, the first and second change start commands and the change pattern designation command are prepared as separate effect control commands. On the other hand, the designation content indicating which of the first special figure and the second special figure is to be changed and the designated content of the fluctuation pattern are configured to be specified by one effect control command. Also good. As an example, an effect control command in which EXT data is set corresponding to a combination of a special symbol (first special figure or second special figure) that starts change and a change pattern is prepared. You may enable it to specify the special symbol and fluctuation pattern which become a fluctuation start. Here, when the special symbol and the variation pattern that start the variation can be specified by one effect control command, the special symbol (the first special feature that starts the variation) for one variation pattern. There are cases where it is necessary to prepare two types of effect control commands according to the figure or the second special figure). On the other hand, if an effect control command for designating a special symbol for starting variation and an effect control command for designating a variation pattern are prepared separately, two types of effect control commands corresponding to the special symbol for starting variation are prepared. And the number of effect control commands corresponding to the number of types of variation patterns may be prepared, and the types of commands prepared in advance, the storage capacity of the command table, and the like can be reduced.

コマンド8CXXHは、特別図柄や飾り図柄などの可変表示結果を指定する可変表示結果通知コマンドである。可変表示結果通知コマンドでは、例えば図5(B)に示すように、可変表示結果が「ハズレ」、「大当り」、「小当り」のいずれとなるかの事前判定結果、また、可変表示結果が「大当り」となる場合における大当り種別が「通常」、「第1確変」〜「第3確変」、「突確」のいずれとなるかの大当り種別決定結果に対応して、異なるEXTデータが設定される。より具体的には、コマンド8C00Hは、可変表示結果が「ハズレ」となる旨の事前判定結果を示す第1可変表示結果通知コマンドである。コマンド8C01Hは、可変表示結果が「大当り」となる場合における大当り種別が「通常」となる旨の事前判定結果及び大当り種別決定結果を示す第2可変表示結果通知コマンドである。コマンド8C02Hは、可変表示結果が「大当り」となる場合における大当り種別が「第1確変」となる旨の事前判定結果及び大当り種別決定結果を示す第3可変表示結果通知コマンドである。コマンド8C03Hは、可変表示結果が「大当り」となる場合における大当り種別が「第2確変」となる旨の事前判定結果及び大当り種別決定結果を示す第4可変表示結果通知コマンドである。コマンド8C04Hは、可変表示結果が「大当り」となる場合における大当り種別が「第3確変」となる旨の事前判定結果及び大当り種別決定結果を示す第5可変表示結果通知コマンドである。コマンド8C05Hは、可変表示結果が「大当り」となる場合における大当り種別が「突確」となる旨の決定結果を示す第6可変表示結果通知コマンドである。コマンド8C06Hは、可変表示結果が「小当り」となる旨の決定結果を示す第7可変表示結果通知コマンドである。 Command 8CXXH is a variable display result notification command for designating a variable display result such as a special symbol or a decorative symbol. In the variable display result notification command, for example, as shown in FIG. 5B, a prior determination result indicating whether the variable display result is “lost”, “big hit”, or “small hit”, and the variable display result is Different EXT data is set corresponding to the big hit type determination result of whether the big hit type is “normal”, “first probability variation” to “third probability variation”, or “surprise probability” in the case of “big hit” The More specifically, the command 8C00H is a first variable display result notification command indicating a prior determination result indicating that the variable display result is “lost”. The command 8C01H is a second variable display result notification command indicating a prior determination result and a big hit type determination result that the big hit type is “normal” when the variable display result is “big hit”. The command 8C02H is a third variable display result notification command indicating a prior determination result and a big hit type determination result that the big hit type is “first probability change” when the variable display result is “big hit”. The command 8C03H is a fourth variable display result notification command indicating a prior determination result and a big hit type determination result that the big hit type is “second probability change” when the variable display result is “big hit”. The command 8C04H is a fifth variable display result notification command indicating a prior determination result and a big hit type determination result that the big hit type is “third probability change” when the variable display result is “big hit”. The command 8C05H is a sixth variable display result notification command indicating a determination result that the big hit type is “surprise” when the variable display result is “big hit”. The command 8C06H is a seventh variable display result notification command indicating a determination result indicating that the variable display result is “small hit”.