JP5976308B2 - 攻撃の場合のマイクロ回路カードの指令手段の電源の安全確保 - Google Patents

攻撃の場合のマイクロ回路カードの指令手段の電源の安全確保 Download PDFInfo

- Publication number

- JP5976308B2 JP5976308B2 JP2011273503A JP2011273503A JP5976308B2 JP 5976308 B2 JP5976308 B2 JP 5976308B2 JP 2011273503 A JP2011273503 A JP 2011273503A JP 2011273503 A JP2011273503 A JP 2011273503A JP 5976308 B2 JP5976308 B2 JP 5976308B2

- Authority

- JP

- Japan

- Prior art keywords

- module

- cell

- attack

- control signal

- detected

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/073—Special arrangements for circuits, e.g. for protecting identification code in memory

- G06K19/07309—Means for preventing undesired reading or writing from or onto record carriers

- G06K19/07363—Means for preventing undesired reading or writing from or onto record carriers by preventing analysis of the circuit, e.g. dynamic or static power analysis or current analysis

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computer Security & Cryptography (AREA)

- General Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Read Only Memory (AREA)

- Storage Device Security (AREA)

- Credit Cards Or The Like (AREA)

- Power Sources (AREA)

Description

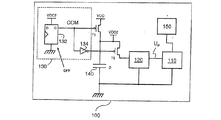

モジュールへの攻撃を検出するための手段と、

攻撃が検出されたときに、不揮発性メモリのセルへの書き込み動作を指令するために、プログラミング電圧の印加可能なチャージポンプに充電することができる指令手段と、

通常の動作の際に電力が供給され、攻撃が検出されたときにのみ前記チャージポンプへと電力を供給するように構成されたコンデンサと、を備えるモジュールに関する。

110: セル(OTPセル)

120: チャージポンプ

130: 変数書込指令手段

132: D型フリップフロップ

134: NOTゲート

140: コンデンサ

150: プロセッサ

500: マイクロ回路カード

510: EEPROMセル

520: 抵抗器

530: 第1のダイオード

540: 第2のダイオード

560: NOTゲート

600: マイクロ回路カード

Claims (10)

- 当該モジュールへの攻撃を検出するための手段と、

攻撃が検出されたときに、不揮発性メモリのセル(110、510)への書き込み動作を指令するために、プログラミング電圧(UP)の印加可能なチャージポンプ(120)に充電することができる指令手段(130)と、

通常の動作の際に電力が供給され、攻撃が検出されたときにのみ前記チャージポンプ(120)へと電力を供給するように構成されたコンデンサ(140)とを備えており、

前記コンデンサ(140)が、攻撃が検出されたときに前記指令手段(130)にも電力を供給することを特徴とするモジュール(100、500、600)。 - 前記指令手段(130)が、フリップフロップ(132)及びNOTゲート(134)を備えており、前記フリップフロップの出力が、通常の動作においては第1のレベルにあり、攻撃が検出されたときに第2のレベルにあり、前記第2のレベルが、前記書き込み動作の継続時間の全体において高のままであることを特徴とする請求項1に記載のモジュール(100、500、600)。

- 前記セル(110)が、ワン・タイム・プログラマブル(OTP)セルであることを特徴とする請求項1又は2に記載のモジュール(100)。

- 前記セル(510)が、EEPROMメモリのセルであることを特徴とする請求項1又は2に記載のモジュール(500、600)。

- 制御信号(SC)を含んでおり、

前記制御信号(SC)のレベル(NH、NB)が前記セル(510)の書き込み又はブランク状態を表わし、

前記制御信号(SC)が、攻撃が検出されたときに当該モジュール(500)の重要信号(SIV)を維持するために使用されることを特徴とする請求項4に記載のモジュール(500)。 - 前記重要信号(SIV)が、リセット信号、クロック信号、又は当該モジュール(500)の外部の機器に接続された入力/出力信号の中から選択されることを特徴とする請求項5に記載のモジュール(500)。

- 制御信号(SC)を含んでおり、

前記制御信号(SC)のレベル(NH、NB)が前記セル(510)の書き込み又はブランク状態を表わし、

前記制御信号(SC)が、当該モジュールの重要部品(150)への電力の供給を制御するスイッチ(T3)に対する指令に使用されることを特徴とする請求項4に記載のモジュール(600)。 - 前記スイッチ(T3)が、PMOSトランジスタであることを特徴とする請求項7に記載のモジュール(600)。

- 前記重要部品が、プロセッサ(150)であることを特徴とする請求項7に記載のモジュール(600)。

- ISO 7816規格によるマイクロ回路カードで構成される請求項1に記載のモジュール(100、500、600)。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR1060465 | 2010-12-14 | ||

| FR1060465A FR2968806B1 (fr) | 2010-12-14 | 2010-12-14 | Securisation de l'alimentation de moyens de commande d'une carte a microcircuit en cas d'attaque |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012128860A JP2012128860A (ja) | 2012-07-05 |

| JP2012128860A5 JP2012128860A5 (ja) | 2016-04-07 |

| JP5976308B2 true JP5976308B2 (ja) | 2016-08-23 |

Family

ID=45093630

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011273503A Active JP5976308B2 (ja) | 2010-12-14 | 2011-12-14 | 攻撃の場合のマイクロ回路カードの指令手段の電源の安全確保 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8453261B2 (ja) |

| EP (1) | EP2466528B1 (ja) |

| JP (1) | JP5976308B2 (ja) |

| FR (1) | FR2968806B1 (ja) |

| TW (1) | TWI524276B (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5776927B2 (ja) * | 2011-03-28 | 2015-09-09 | ソニー株式会社 | 情報処理装置及び方法、並びにプログラム |

| US8912814B2 (en) * | 2012-11-12 | 2014-12-16 | Chaologix, Inc. | Clocked charge domain logic |

| JP6387767B2 (ja) * | 2014-09-26 | 2018-09-12 | 大日本印刷株式会社 | 電子情報記録媒体、icカード、チェック方法、及び処理プログラム |

| US10685118B2 (en) | 2017-05-15 | 2020-06-16 | Ut-Battelle, Llc | System and method for monitoring power consumption to detect malware |

| CN109067435B (zh) * | 2018-07-12 | 2021-12-14 | 徐正兴 | 用于近场通信装置的设备 |

| US11074345B2 (en) | 2019-05-30 | 2021-07-27 | Ut-Battelle, Llc | Rootkit detection system |

| EP3839750A1 (en) * | 2019-12-18 | 2021-06-23 | Thales Dis France Sa | Method for secure executing of a security related process |

| CN115840969B (zh) * | 2023-02-27 | 2023-04-28 | 合肥天帷信息安全技术有限公司 | 一种数据存储安全等级保护测评系统 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6507913B1 (en) * | 1999-12-30 | 2003-01-14 | Yeda Research And Development Co. Ltd. | Protecting smart cards from power analysis with detachable power supplies |

| CN1922564B (zh) * | 2004-02-24 | 2011-01-26 | Nxp股份有限公司 | Ic侵入检测 |

| FR2935823B1 (fr) * | 2008-09-11 | 2010-10-01 | Oberthur Technologies | Procede et dispositif de protection d'un microcircuit contre les attaques. |

-

2010

- 2010-12-14 FR FR1060465A patent/FR2968806B1/fr active Active

-

2011

- 2011-12-12 EP EP11193003.8A patent/EP2466528B1/fr active Active

- 2011-12-13 US US13/324,780 patent/US8453261B2/en active Active

- 2011-12-14 JP JP2011273503A patent/JP5976308B2/ja active Active

- 2011-12-14 TW TW100146306A patent/TWI524276B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| TW201232419A (en) | 2012-08-01 |

| EP2466528B1 (fr) | 2013-07-10 |

| JP2012128860A (ja) | 2012-07-05 |

| TWI524276B (zh) | 2016-03-01 |

| FR2968806B1 (fr) | 2013-01-18 |

| US8453261B2 (en) | 2013-05-28 |

| FR2968806A1 (fr) | 2012-06-15 |

| EP2466528A1 (fr) | 2012-06-20 |

| US20120151608A1 (en) | 2012-06-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5976308B2 (ja) | 攻撃の場合のマイクロ回路カードの指令手段の電源の安全確保 | |

| KR101110994B1 (ko) | 에러 동작으로부터 집적 회로를 보호하는 방법 및 장치 | |

| KR101705794B1 (ko) | 2차전지 보호 회로, 2차전지 보호 장치, 전지팩 및 데이터 기입 방법 | |

| US20100132047A1 (en) | Systems and methods for tamper resistant memory devices | |

| JP2012128860A5 (ja) | ||

| US10275017B2 (en) | Power circuit and memory device using the same | |

| JP2009123071A (ja) | データ処理回路及び通信携帯端末装置 | |

| KR100883457B1 (ko) | 비휘발성 저장 장치와 방법 및 디지털 저장 매체 | |

| JP3641182B2 (ja) | 自己破壊型半導体装置 | |

| KR101662573B1 (ko) | 비휘발성 메모리에서의 의도하지 않은 영구적인 기록-보호 방지 방법 | |

| US9741450B2 (en) | Memory comprising a circuit for detecting a glitch on a line of the memory | |

| JP6066554B2 (ja) | ヒューズによって保護されたマイクロ回路カード | |

| CN108629185B (zh) | 服务器可信平台度量控制系统及其运行方法 | |

| JP6063759B2 (ja) | 半導体記憶装置 | |

| EP3667533A1 (en) | Method for securing a system in case of an undesired power-loss | |

| US7710762B2 (en) | Device for protecting SRAM data | |

| CN110968531A (zh) | 一种ssd的数据销毁方法、系统及装置 | |

| JP6387767B2 (ja) | 電子情報記録媒体、icカード、チェック方法、及び処理プログラム | |

| JP3938376B2 (ja) | テスト端子無効化回路 | |

| JP2005056439A (ja) | メモリデータ制御装置 | |

| JP2002099468A (ja) | 書き込み制御回路 | |

| JP2006172384A (ja) | 半導体装置 | |

| CN112115520A (zh) | 内部电源供电结构及方法、安全芯片和电子卡 | |

| JP2006277012A (ja) | 半導体集積回路 | |

| US20130070551A1 (en) | Percolation Tamper Protection Circuit for Electronic Devices |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20141126 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20151021 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151117 |

|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20160217 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160621 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160720 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5976308 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |