JP5575310B2 - デジタル信号処理のためのタイルベースインタリーブ処理及びデインタリーブ処理 - Google Patents

デジタル信号処理のためのタイルベースインタリーブ処理及びデインタリーブ処理 Download PDFInfo

- Publication number

- JP5575310B2 JP5575310B2 JP2013169110A JP2013169110A JP5575310B2 JP 5575310 B2 JP5575310 B2 JP 5575310B2 JP 2013169110 A JP2013169110 A JP 2013169110A JP 2013169110 A JP2013169110 A JP 2013169110A JP 5575310 B2 JP5575310 B2 JP 5575310B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- data items

- dram

- sequence

- chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/06—Addressing a physical block of locations, e.g. base addressing, module addressing, memory dedication

- G06F12/0607—Interleaved addressing

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2703—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques the interleaver involving at least two directions

- H03M13/2707—Simple row-column interleaver, i.e. pure block interleaving

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/276—Interleaving address generation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6502—Reduction of hardware complexity or efficient processing

- H03M13/6505—Memory efficient implementations

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- Probability & Statistics with Applications (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Error Detection And Correction (AREA)

- Static Random-Access Memory (AREA)

- Dram (AREA)

Description

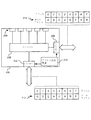

102 オンチップメモリ

104 DSP

106 転送エンジン

108 ハードウェア周辺装置

110 制御プロセッサ

112 DRAM

210 アドレス生成要素

Claims (29)

- 第1シーケンスに配置される複数のデータアイテムを格納する第1メモリであって、各データアイテムが前記第1メモリ上の関連するメモリアドレスを有し、前記複数のデータアイテムがデータアイテムのブロックのサブセットからなる、前記第1メモリと、

第2メモリと、

前記第1メモリと前記第2メモリとに接続され、DRAMに対するポートを有する転送エンジンであって、第1メモリ転送段階において前記第1メモリから前記DRAMに前記複数のデータアイテムを直接転送し、第2メモリ転送段階において前記DRAMから前記第2メモリに前記複数のデータアイテムを直接転送するよう構成される前記転送エンジンと、

を有するデジタル信号処理システムオンチップであって、

前記第1メモリ転送段階において、前記転送エンジンは、所定のメモリリードアドレスの非リニアシーケンスに従って前記第1メモリから前記複数のデータアイテムを読み込み、前記複数のデータアイテムを前記DRAMに書き込むよう構成され、

前記第2メモリ転送段階において、前記転送エンジンは、リニアアドレスシーケンスの各バーストがDRAMインタフェースのバーストサイズに基づき選択された長さを有する、リニアアドレスシーケンスのバーストに従って前記DRAMから前記複数のデータアイテムを読み込み、前記複数のデータアイテムが前記第1シーケンスと異なる第2シーケンスにより前記第2メモリに配置されるように、所定のメモリライトアドレスの非リニアシーケンスに従って前記複数のデータアイテムを前記第2メモリに書き込むよう構成され、

前記第1シーケンスと前記第2シーケンスとの1つは、ロー・カラムインタリーブされたデータを有するデジタル信号処理システムオンチップ。 - 前記第1メモリと前記第2メモリとは共にSRAMである、請求項1記載のデジタル信号処理システムオンチップ。

- 前記第1メモリと前記第2メモリとは、同一のオンチップメモリである、請求項1又は2記載のデジタル信号処理システムオンチップ。

- 前記DRAMをさらに有する、請求項1乃至3何れか一項記載のデジタル信号処理システムオンチップ。

- 前記転送エンジンはさらに、前記データアイテムのブロックのすべてが前記第2メモリに書き込まれるまで、前記第1及び第2メモリ転送段階を繰り返すよう構成される、請求項1乃至4何れか一項記載のデジタル信号処理システムオンチップ。

- 前記所定のメモリリードアドレスの非リニアシーケンスと前記所定のメモリライトアドレスの非リニアシーケンスとを生成するよう構成される少なくとも1つのアドレス生成要素をさらに有する、請求項1乃至5何れか一項記載のデジタル信号処理システムオンチップ。

- 前記データアイテムのブロックは、データアイテムのいくつかのロー及びデータアイテムのいくつかのカラムを有するグリッドとして構成されるとして定義される、請求項1乃至6何れか一項記載のデジタル信号処理システムオンチップ。

- 前記グリッドはさらに、各タイルが前記グリッドの矩形部分を有し、さらにデータアイテムのR個のロー及びC個のカラムを有する複数のタイルを有し、

前記複数のデータアイテムは、1以上のタイルを有する、請求項7記載のデジタル信号処理システムオンチップ。 - 前記所定のメモリリードアドレスの非リニアシーケンスは、前記第1の複数のデータアイテムの各タイルについて、固定数のメモリアドレスにより分離され、初期的なスタートアドレスからスタートする不連続なメモリアドレスのシーケンスを有し、

前記固定数は、前記グリッドのロー数未満の数に対応し、

前記タイルの境界に到達するまで、各追加的なシーケンスがオフセット初期的なスタートアドレスからスタートする不連続なメモリアドレスの1以上の追加的なシーケンスに続く、請求項8記載のデジタル信号処理システムオンチップ。 - 前記所定のメモリライトアドレスの非リニアシーケンスは、前記第2メモリの固定数のメモリアドレスにより分離され、前記第2メモリの初期的なスタートアドレスからスタートするC個の連続的なメモリアドレスのグループのシーケンスを有し、

前記固定数は、前記グリッドにおけるカラム数未満のCに対応する、請求項8又は9記載のデジタル信号処理システムオンチップ。 - 前記複数のデータアイテムは、前記グリッドのタイルを有する、請求項8乃至10何れか一項記載のデジタル信号処理システムオンチップ。

- 前記第2メモリ転送段階において、前記リニアアドレスシーケンスのバーストは、前記第2メモリの固定数のメモリアドレスにより分離され、前記第2メモリの初期的なスタートアドレスからスタートするX個の連続的なメモリアドレスのバーストのシーケンスを有し、

Xは、前記グリッドのタイルのデータアイテムの個数に等しい、請求項8乃至11何れか一項記載のデジタル信号処理システムオンチップ。 - 前記第1メモリ転送段階において、前記転送エンジンは、各リニアアドレスシーケンスのバーストがDRAMインタフェースのバーストサイズに基づき選択された長さを有する、リニアアドレスシーケンスのバーストに従って前記複数のデータアイテムを前記DRAMに書き込むよう構成される、請求項8乃至12何れか一項記載のデジタル信号処理システムオンチップ。

- 前記第1メモリ転送段階において、前記リニアアドレスシーケンスのバーストは、前記第2メモリの固定数のメモリアドレスにより分離され、前記第2メモリの初期的なスタートアドレスからスタートするX個の連続的なメモリアドレスのバーストのシーケンスを有し、

Xは、前記グリッドのタイルのデータアイテムの個数に等しい、請求項13記載のデジタル信号処理システムオンチップ。 - タイルは、前記DRAMインタフェースのバーストのサイズに基づきサイジングされる、請求項8乃至14何れか一項記載のデジタル信号処理システムオンチップ。

- デジタル信号処理システムにおいてデータアイテムのブロックに対してインタリーブ又はデインタリーブ処理を実行する方法であって、

第1オンチップメモリから、所定のメモリリードアドレスの非リニアシーケンスに従って第1シーケンスに格納されている第1の複数のデータアイテムを読み込むステップであって、前記第1の複数のデータアイテムは前記データアイテムのブロックのサブセットからなる、読み込むステップと、

前記第1の複数のデータアイテムをDRAMに書き込むステップと、

前記DRAMから、リニアアドレスシーケンスの各バーストがDRAMインタフェースのバーストサイズに基づき選択される長さを有する、リニアアドレスシーケンスのバーストに従って前記第1の複数のデータアイテムを読み込むステップと、

前記データアイテムが前記第1シーケンスと異なる第2シーケンスにより第2オンチップメモリ上に配置されるように、所定のメモリライトアドレスの非リニアシーケンスに従って前記第1の複数のデータアイテムを前記第2オンチップメモリに書き込むステップと、

を有し、

前記第1シーケンスと前記第2シーケンスとの1つは、ロー・カラムインタリーブされたデータを有する方法。 - 前記第1オンチップメモリと前記第2オンチップメモリとは共にSRAMである、請求項16記載の方法。

- 前記第1オンチップメモリと前記第2オンチップメモリとは同一のオンチップメモリである、請求項16又は17記載の方法。

- 前記DRAMは、第3オンチップメモリである、請求項16乃至18何れか一項記載の方法。

- 前記データアイテムのブロックの全体が前記第2オンチップメモリに書き込まれるまで、当該方法を繰り返すステップをさらに有する、請求項16乃至19何れか一項記載の方法。

- 前記データアイテムのブロックは、データアイテムのいくつかのロー及びデータアイテムのいくつかのカラムを有するグリッドとして構成されるとして定義される、請求項16乃至20何れか一項記載の方法。

- 前記グリッドはさらに、各タイルが前記グリッドの矩形部分を有し、さらにデータアイテムのR個のロー及びC個のカラムを有する複数のタイルを有し、

前記第1の複数のデータアイテムは、1以上のタイルを有する、請求項21記載の方法。 - 前記第1オンチップメモリから、所定のメモリリードアドレスの非リニアシーケンスに従って第1シーケンスに格納されている第1の複数のデータアイテムを読み込むステップは、前記第1の複数のデータアイテムの各タイルについて、

(i)前記第1オンチップメモリの初期的なスタートアドレスのデータアイテムを読み込むステップと、

(ii)固定数のデータアイテムをスキップするステップであって、前記固定数は前記グリッドのロー数未満のものに対応する、前記スキップするステップと、

(iii)データアイテムを読み込むステップと、

(iv)前記タイルの境界に到達するまで、ステップ(ii)及び(iii)を繰り返すステップと、

(v)前記初期的なスタートアドレスにオフセットを加えるステップと、

(vi)前記タイルの各データアイテムが読み込まれるまで、ステップ(i)〜(v)を繰り返すステップと、

を有する、請求項22記載の方法。 - 前記所定のメモリライトアドレスの非リニアシーケンスに従って前記第1の複数のデータアイテムを前記第2オンチップメモリに書き込むステップは、

(i)前記第1の複数のデータアイテムからのC個のデータアイテムを前記第2オンチップメモリの複数の連続的なアドレスであって、前記第2オンチップメモリの前記タイルの初期的なスタートアドレスからスタートする前記複数の連続的なアドレスに書き込むステップと、

(ii)前記第2オンチップメモリの固定数のアドレスをスキップするステップであって、前記固定数は前記グリッドのカラム数未満のCに対応する、前記スキップするステップと、

(iii)前記第1の複数のデータアイテムからのC個のデータアイテムを前記第2オンチップメモリの複数の連続的なアドレスに書き込むステップと、

(iv)ステップ(ii)及び(iii)を繰り返すステップと、

を有する、請求項22又は23記載の方法。 - 前記第1の複数のデータアイテムを前記DRAMに書き込むステップは、

(i)前記第1の複数のデータアイテムからのX個のデータアイテムを前記DRAMの前記タイルの初期的なスタートアドレスからスタートする前記DRAMの複数の連続的なアドレスに書き込むステップと、

(ii)前記DRAMの固定数のアドレスをスキップするステップと、

(iii)前記第1の複数のデータアイテムからのX個のデータアイテムを前記DRAMの複数の連続的なアドレスに書き込むステップと、

(iv)ステップ(ii)及び(iii)を繰り返すステップと、

を有し、

Xは、前記グリッドのタイルのデータアイテムの個数に等しい、請求項22乃至24何れか一項記載の方法。 - 前記DRAMから、リニアアドレスシーケンスのバーストに従って前記第1の複数のデータアイテムを読み込むステップは、

(i)前記第1の複数のデータアイテムからのX個のデータアイテムを前記DRAMの初期的なスタートアドレスからスタートする前記DRAMの複数の連続的なアドレスから読み込むステップと、

(ii)前記DRAMの固定数のアドレスをスキップするステップと、

(iii)前記第1の複数のデータアイテムからのX個のデータアイテムを前記DRAMの複数の連続的なアドレスから読み込むステップと、

(iv)ステップ(ii)及び(iii)を繰り返すステップと、

を有し、

Xは、前記グリッドのタイルのデータアイテムの個数に等しい、請求項22乃至25何れか一項記載の方法。 - タイルは、前記DRAMインタフェースのバーストのサイズに基づきサイジングされる、請求項25又は26記載の方法。

- コンピュータ上で実行されると、請求項16乃至27何れか一項記載の方法の全てのステップを実行するよう構成されるコンピュータプログラムコード手段を有するコンピュータプログラム。

- コンピュータ可読媒体上に格納される請求項28記載のコンピュータプログラム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB1215425.8A GB2497154B (en) | 2012-08-30 | 2012-08-30 | Tile based interleaving and de-interleaving for digital signal processing |

| GB1215425.8 | 2012-08-30 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014050103A JP2014050103A (ja) | 2014-03-17 |

| JP2014050103A5 JP2014050103A5 (ja) | 2014-04-24 |

| JP5575310B2 true JP5575310B2 (ja) | 2014-08-20 |

Family

ID=47074965

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013169110A Active JP5575310B2 (ja) | 2012-08-30 | 2013-08-16 | デジタル信号処理のためのタイルベースインタリーブ処理及びデインタリーブ処理 |

Country Status (6)

| Country | Link |

|---|---|

| US (4) | US10296456B2 (ja) |

| JP (1) | JP5575310B2 (ja) |

| CN (1) | CN103678190B (ja) |

| DE (1) | DE102013014168B4 (ja) |

| GB (1) | GB2497154B (ja) |

| TW (1) | TWI604726B (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9256531B2 (en) | 2012-06-19 | 2016-02-09 | Samsung Electronics Co., Ltd. | Memory system and SoC including linear addresss remapping logic |

| GB2497154B (en) * | 2012-08-30 | 2013-10-16 | Imagination Tech Ltd | Tile based interleaving and de-interleaving for digital signal processing |

| US10186236B2 (en) * | 2013-05-23 | 2019-01-22 | Intel Corporation | Universal codec |

| KR102354992B1 (ko) | 2015-03-02 | 2022-01-24 | 삼성전자주식회사 | 양안 시차 영상에 대한 타일 기반 렌더링 방법 및 장치 |

| KR102341267B1 (ko) | 2015-05-04 | 2021-12-20 | 삼성전자주식회사 | 양안 시차 영상에 대한 렌더링 방법 및 장치 |

| CN105681904A (zh) * | 2016-01-18 | 2016-06-15 | 四川长虹电器股份有限公司 | 提高电视响应速度的方法 |

| TWI617138B (zh) * | 2016-01-26 | 2018-03-01 | 晨星半導體股份有限公司 | 時間解交錯電路與方法 |

| CN107038122A (zh) * | 2016-02-04 | 2017-08-11 | 晨星半导体股份有限公司 | 时间解交错电路与方法 |

| US11979340B2 (en) | 2017-02-12 | 2024-05-07 | Mellanox Technologies, Ltd. | Direct data placement |

| WO2018152841A1 (en) * | 2017-02-27 | 2018-08-30 | Alto Beam (China) Inc. | Apparatus for performing deinterleaving of a binary data stream and dvb-t2 receiver |

| CN109728826B (zh) * | 2017-10-27 | 2023-07-07 | 深圳市中兴微电子技术有限公司 | 一种数据交织与解交织方法和装置 |

| GB202008299D0 (en) * | 2020-06-02 | 2020-07-15 | Imagination Tech Ltd | Manipulation of data in a memory |

| US20220197653A1 (en) * | 2020-12-22 | 2022-06-23 | Intel Corporation | Processors, methods, systems, and instructions to select and store data elements from strided data element positions in a first dimension from three source two-dimensional arrays in a result two-dimensional array |

| US20220206854A1 (en) * | 2020-12-24 | 2022-06-30 | Intel Corporation | Apparatuses, methods, and systems for instructions for aligning tiles of a matrix operations accelerator |

| US20240015217A1 (en) * | 2022-07-06 | 2024-01-11 | Mellanox Technologies, Ltd. | Patterned Remote Direct Memory Access (RDMA) |

Family Cites Families (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5802387A (en) * | 1996-12-27 | 1998-09-01 | Lucent Technologies Inc. | Efficient data transfer in a digital signal processor |

| WO1999007132A1 (en) * | 1997-07-31 | 1999-02-11 | British Telecommunications Public Limited Company | Generation of voice messages |

| JP3738134B2 (ja) * | 1998-06-19 | 2006-01-25 | 三洋電機株式会社 | デジタル信号処理装置 |

| JP2000307440A (ja) * | 1999-04-23 | 2000-11-02 | Denso Corp | データ列変換装置,及びデータ伝送システム |

| AU5679401A (en) * | 2000-05-22 | 2001-12-03 | Yozan Inc. | Address converter, interleaver and de-interleaver |

| US6868519B2 (en) * | 2001-04-23 | 2005-03-15 | Lucent Technologies Inc. | Reducing scintillation effects for optical free-space transmission |

| US7177988B2 (en) | 2002-01-24 | 2007-02-13 | Broadcom Corporation | Method and system for synchronizing processor and DMA using ownership flags |

| JP3980901B2 (ja) * | 2002-02-12 | 2007-09-26 | 沖電気工業株式会社 | デジタル信号処理装置 |

| JPWO2003085838A1 (ja) * | 2002-04-05 | 2005-08-18 | ソニー株式会社 | インターリーブ装置及びインターリーブ方法、並びにデインターリーブ装置及びデインターリーブ方法 |

| GB2391337B (en) * | 2002-04-26 | 2005-06-15 | Motorola Inc | Instruction cache and method for reducing memory conflicts |

| US7600163B2 (en) * | 2003-09-23 | 2009-10-06 | Realtek Semiconductor Corp. | Convolutional interleaver and deinterleaver |

| CN100512361C (zh) | 2004-06-22 | 2009-07-08 | 中兴通讯股份有限公司 | 一种非对称数字用户线中卷积交织和解交织的实现装置 |

| CN101032085B (zh) | 2004-09-29 | 2010-06-09 | 松下电器产业株式会社 | 数据交织装置 |

| US20060236045A1 (en) | 2005-04-13 | 2006-10-19 | Analog Devices, Inc. | Apparatus for deinterleaving interleaved data using direct memory access |

| US20080028188A1 (en) * | 2006-07-25 | 2008-01-31 | Legend Silicon | Time de-interleaver implementation using sdram in a tds-ofdm receiver |

| JP2008159109A (ja) | 2006-12-21 | 2008-07-10 | Matsushita Electric Ind Co Ltd | データ転送装置 |

| US8108648B2 (en) * | 2007-06-25 | 2012-01-31 | Sonics, Inc. | Various methods and apparatus for address tiling |

| CN101237240B (zh) | 2008-02-26 | 2011-07-20 | 北京海尔集成电路设计有限公司 | 一种利用外部存储器实现卷积交织/解交织的方法及设备 |

| US20090313399A1 (en) | 2008-06-13 | 2009-12-17 | Texas Instruments Incorporated | Direct memory access channel |

| US8352834B2 (en) * | 2009-11-12 | 2013-01-08 | Broadlogic Network Technologies Inc. | High throughput interleaver / deinterleaver |

| GB2502556B (en) * | 2012-05-30 | 2017-08-02 | Imagination Tech Ltd | Noise variance estimation and interference detection |

| GB2499270B (en) * | 2012-06-07 | 2014-07-09 | Imagination Tech Ltd | Efficient demapping of constellations |

| GB2505446B (en) * | 2012-08-30 | 2014-08-13 | Imagination Tech Ltd | Memory address generation for digital signal processing |

| GB2497154B (en) * | 2012-08-30 | 2013-10-16 | Imagination Tech Ltd | Tile based interleaving and de-interleaving for digital signal processing |

| GB2513677B (en) * | 2013-10-17 | 2015-09-02 | Imagination Tech Ltd | Channel impulse response |

| GB2531367B (en) * | 2015-01-09 | 2016-12-28 | Imagination Tech Ltd | Impulsive noise rejection |

| TWI569587B (zh) * | 2015-02-06 | 2017-02-01 | 晨星半導體股份有限公司 | 解迴旋交錯器 |

| GB2536655B (en) * | 2015-03-24 | 2017-09-20 | Imagination Tech Ltd | Logging events with timestamps |

| GB2536658B (en) * | 2015-03-24 | 2017-03-22 | Imagination Tech Ltd | Controlling data flow between processors in a processing system |

| GB2536069B (en) * | 2015-03-25 | 2017-08-30 | Imagination Tech Ltd | SIMD processing module |

| US10216412B2 (en) * | 2017-02-14 | 2019-02-26 | Arm Limited | Data processing systems |

| US10387160B2 (en) * | 2017-04-01 | 2019-08-20 | Intel Corporation | Shared local memory tiling mechanism |

| US10896043B2 (en) * | 2018-09-28 | 2021-01-19 | Intel Corporation | Systems for performing instructions for fast element unpacking into 2-dimensional registers |

-

2012

- 2012-08-30 GB GB1215425.8A patent/GB2497154B/en active Active

-

2013

- 2013-03-12 US US13/794,796 patent/US10296456B2/en active Active

- 2013-08-06 TW TW102128080A patent/TWI604726B/zh active

- 2013-08-16 JP JP2013169110A patent/JP5575310B2/ja active Active

- 2013-08-26 DE DE102013014168.0A patent/DE102013014168B4/de active Active

- 2013-08-29 CN CN201310384449.8A patent/CN103678190B/zh active Active

-

2019

- 2019-04-11 US US16/381,268 patent/US10657050B2/en active Active

-

2020

- 2020-04-10 US US16/845,303 patent/US11210217B2/en active Active

-

2021

- 2021-11-18 US US17/529,954 patent/US11755474B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20200242029A1 (en) | 2020-07-30 |

| US20140068168A1 (en) | 2014-03-06 |

| CN103678190A (zh) | 2014-03-26 |

| DE102013014168A1 (de) | 2014-03-06 |

| US20220075723A1 (en) | 2022-03-10 |

| US11755474B2 (en) | 2023-09-12 |

| US10296456B2 (en) | 2019-05-21 |

| US10657050B2 (en) | 2020-05-19 |

| CN103678190B (zh) | 2016-10-26 |

| US20190236006A1 (en) | 2019-08-01 |

| DE102013014168B4 (de) | 2016-07-07 |

| TW201419837A (zh) | 2014-05-16 |

| JP2014050103A (ja) | 2014-03-17 |

| TWI604726B (zh) | 2017-11-01 |

| US11210217B2 (en) | 2021-12-28 |

| GB2497154A (en) | 2013-06-05 |

| GB2497154B (en) | 2013-10-16 |

| GB201215425D0 (en) | 2012-10-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5575310B2 (ja) | デジタル信号処理のためのタイルベースインタリーブ処理及びデインタリーブ処理 | |

| US9684592B2 (en) | Memory address generation for digital signal processing | |

| US20200358456A1 (en) | Decoder for low-density parity-check codes | |

| US20210374512A1 (en) | Multicast network and memory transfer optimizations for neural network hardware acceleration | |

| US11721373B2 (en) | Shared multi-port memory from single port | |

| JP5752666B2 (ja) | デジタル信号処理用のメモリアクセス | |

| TWI601424B (zh) | 時間解交錯電路與方法 | |

| CN107241163B (zh) | 一种交织处理方法及装置 | |

| Briki et al. | A conflict-free memory mapping approach to design parallel hardware interleaver architectures with optimized network and controller | |

| JP2004312348A (ja) | インターリーブ/デインターリーブ方法及び装置 | |

| US9442661B2 (en) | Multidimensional storage array and method utilizing an input shifter to allow an entire column or row to be accessed in a single clock cycle | |

| JP6863661B2 (ja) | レートデマッチング及びデインターリーブ回路 | |

| JP2009239684A (ja) | クロスインターリーブの効率化 | |

| CN110383785B (zh) | 在dvb-t2接收机中执行二进制数据流的时域去交织的装置 | |

| JP4936223B2 (ja) | アフィン変換装置および方法 | |

| CN117009287A (zh) | 一种于弹性队列存储的动态可重构处理器 | |

| US20140129756A1 (en) | Data processing device and data processing method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140311 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140311 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20140311 |

|

| TRDD | Decision of grant or rejection written | ||

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20140522 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140603 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140701 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5575310 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |