JP5473406B2 - ネットワーク処理装置及びその処理方法 - Google Patents

ネットワーク処理装置及びその処理方法 Download PDFInfo

- Publication number

- JP5473406B2 JP5473406B2 JP2009126822A JP2009126822A JP5473406B2 JP 5473406 B2 JP5473406 B2 JP 5473406B2 JP 2009126822 A JP2009126822 A JP 2009126822A JP 2009126822 A JP2009126822 A JP 2009126822A JP 5473406 B2 JP5473406 B2 JP 5473406B2

- Authority

- JP

- Japan

- Prior art keywords

- datagram

- processing

- information

- reassembly

- reassembling

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/16—Implementation or adaptation of Internet protocol [IP], of transmission control protocol [TCP] or of user datagram protocol [UDP]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

- H04L49/9084—Reactions to storage capacity overflow

- H04L49/9089—Reactions to storage capacity overflow replacing packets in a storage arrangement, e.g. pushout

- H04L49/9094—Arrangements for simultaneous transmit and receive, e.g. simultaneous reading/writing from/to the storage element

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/16—Implementation or adaptation of Internet protocol [IP], of transmission control protocol [TCP] or of user datagram protocol [UDP]

- H04L69/161—Implementation details of TCP/IP or UDP/IP stack architecture; Specification of modified or new header fields

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/16—Implementation or adaptation of Internet protocol [IP], of transmission control protocol [TCP] or of user datagram protocol [UDP]

- H04L69/166—IP fragmentation; TCP segmentation

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Computer Security & Cryptography (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

Description

フラグメント化されたIPデータグラムを受信し、該IPデータグラムをリアセンブル処理する処理手段と、

リアセンブル処理対象外のIPデータグラムを特定する情報を保持する保持手段と、を有し、

前記処理手段は、前記保持手段に保持された情報で特定されるIPデータグラムを受信した場合、該IPデータグラムをリアセンブル処理せず、

前記保持手段は、前記処理手段によるリアセンブル処理が終了したIPデータグラムを特定する情報を保持することを特徴とする。

図1は、第一の実施形態におけるプロトコル処理装置の構成の一例を示すブロック図である。図1において、CPU101は、後述するROMに格納された制御プログラム(ソフトウェア)に従ってTCP/IPネットワークのプロトコル処理を実行する。ROM102にはCPU101が実行するソフトウェアが格納されている。RAM103はCPU101がプロトコル処理を実行時に、ワークエリアとして使用される。

図6は、リアセンブル初期化処理の処理手順を示すフローチャートである。尚、リアセンブル初期化処理はリアセンブル処理開始時に行われるが、これはフラグメント化されたIPデータグラム受信が前提となる。また、この処理には、受信したIPデータグラムのIPヘッダ情報が引数(Header)として渡される。

図7は、リアセンブル通常処理の処理手順を示すフローチャートである。尚、このリアセンブル通常処理は、フラグメント化されたIPデータグラムの受信時に行われる。また、詳細は後述するが、IPデータグラム受信時に受信したIPデータグラムのIPヘッダ情報と合致する管理エントリが存在するか否かを確認するために、リアセンブル処理対象管理テーブル202の検索が行われる。検索した結果、合致する管理エントリが存在する場合は、受信したIPデータグラムのIPヘッダ情報、合致する管理エントリがそれぞれ引数(Header、Entry)として渡される。また、検索した結果、合致する管理エントリが存在しない場合には、リアセンブル初期化処理(図6)により新規に管理エントリが作成され、その管理エントリが引数(Entry)として渡される。

例えば、全パケット長フィールドが1044バイトであり、IHLフィールドが5である場合には、以下の計算式からペイロードサイズは1Kバイトと算出される。

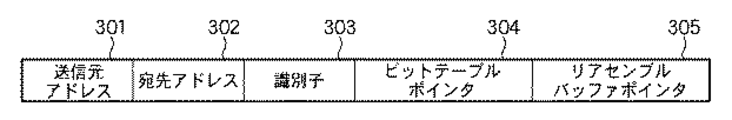

上述の方法でオフセットとペイロードサイズを取得した後、ステップS703へ処理を進め、ステップS701で特定したビットテーブル及びリアセンブルバッファの更新処理を行う。ビットテーブルの更新処理は、フラグメント前のペイロードデータ内の受信した部分に対応するビットに“1”をセットすることで行う。例えば、オフセットが0(ゼロ)、ペイロードサイズが24バイトであったとする。この場合は、ビットテーブルの先頭から3ビット分に“1”がセットされる。そして、リアセンブルバッファの更新処理は、フラグメント前のペイロードデータ内の受信した部分に対応する領域にペイロードデータをコピーすることで行う。

図8は、リアセンブル終了処理の処理手順を示すフローチャートである。尚、このリアセンブル終了処理は、リアセンブル処理が完了した場合、或いはタイムアウトした場合に実行される。この処理の実行前にはリアセンブル処理が完了、若しくはタイムアウトした管理エントリが特定されており、その管理エントリが引数(Entry)として渡される。

ここで、プロトコル処理装置におけるIPデータグラムを受信した場合の処理手順を、図9を用いて説明する。尚、このリアセンブル処理は、IPデータグラムを受信したことをトリガーとしてCPU101によって実行される。

次に、図面を参照しながら本発明に係る第二の実施形態を詳細に説明する。第二の実施形態は、第一の実施形態とIPデータグラム受信時の挙動のみが異なり、それ以外は同一である。

ここで、プロトコル処理装置におけるIPデータグラムを受信した場合の処理手順を、図10を用いて説明する。尚、このリアセンブル処理は、IPデータグラムを受信したことをトリガーとしてCPU101によって実行される。

Claims (16)

- 情報処理装置であって、

フラグメント化されたIPデータグラムを受信し、該IPデータグラムをリアセンブル処理する処理手段と、

リアセンブル処理対象外のIPデータグラムを特定する情報を保持する保持手段と、を有し、

前記処理手段は、前記保持手段に保持された情報で特定されるIPデータグラムを受信した場合、該IPデータグラムをリアセンブル処理せず、

前記保持手段は、前記処理手段によるリアセンブル処理が終了したIPデータグラムを特定する情報を保持することを特徴とする情報処理装置。 - 情報処理装置であって、

フラグメント化されたIPデータグラムを受信し、該IPデータグラムをリアセンブル処理する処理手段と、

リアセンブル処理対象外のIPデータグラムを特定する情報を保持する保持手段と、を有し、

前記処理手段は、前記保持手段に保持された情報で特定されるIPデータグラムを受信した場合、該IPデータグラムをリアセンブル処理せず、

前記保持手段は、一定時間内にアセンブル処理が終了しなかったIPデータグラムを特定する情報を保持することを特徴とする情報処理装置。 - 情報処理装置であって、

フラグメント化されたIPデータグラムを受信し、該IPデータグラムをリアセンブル処理する処理手段と、

リアセンブル処理対象外のIPデータグラムを特定する情報を保持する保持手段と、を有し、

前記処理手段は、前記リアセンブル処理を開始した後、前記保持手段に保持される情報で特定されるIPデータグラムを受信した場合、該IPデータグラムをリアセンブル処理しないで前記開始したリアセンブル処理を終了させることを特徴とする情報処理装置。 - 前記保持手段は、前記処理手段によるリアセンブル処理が終了したIPデータグラムを特定する情報を保持することを特徴とする請求項2または3に記載の情報処理装置。

- 前記保持手段は、一定時間内にリアセンブル処理が終了しなかったIPデータグラムを特定する情報を保持することを特徴とする請求項1乃至4のいずれか1項に記載の情報処理装置。

- 前記保持手段は、前記処理手段によるリアセンブル処理が終了したIPデータグラムを送信した送信元クライアントを特定する情報を保持することを特徴とする請求項1または3に記載の情報処理装置。

- 前記保持手段は、一定時間内にリアセンブル処理が終了しなかったIPデータグラムを送信した送信元クライアントを特定する情報を保持することを特徴とする請求項1乃至6のいずれか1項に記載の情報処理装置。

- 前記処理手段は、前記リアセンブル処理を開始した後、前記保持手段に保持される情報で特定されるIPデータグラムを受信した場合、該IPデータグラムをリアセンブル処理しないで前記開始したリアセンブル処理を終了させることを特徴とする請求項1または2に記載の情報処理装置。

- 前記処理手段は、前記リアセンブル処理しないIPデータグラムを破棄することを特徴とする請求項1乃至8のいずれか1項に記載の情報処理装置。

- 前記処理手段は、前記フラグメント化されたIPデータグラムを格納するリアセンブルバッファ、IPデータグラムの到着状況を管理するビットマップテーブル、リアセンブル処理のタイムアウトを計時するリアセンブルタイマのうち、少なくとも何れか一つを確保することを特徴とする請求項1乃至9のいずれか1項に記載の情報処理装置。

- 前記保持手段に保持される情報の保持期間が経過した場合には、前記保持手段に保持される情報を破棄する破棄手段を更に有することを特徴とする請求項1乃至10のいずれか1項に記載の情報処理装置。

- 前記保持手段に保持される情報の破棄条件を設定する設定手段と、

前記設定手段に設定された破棄条件に合致する情報を破棄する破棄手段とを更に有することを特徴とする請求項1乃至11のいずれか1項に記載の情報処理装置。 - 情報処理装置の処理方法であって、

処理手段が、フラグメント化されたIPデータグラムを受信し、該IPデータグラムをリアセンブル処理する処理工程と、

保持手段が、リアセンブル処理対象外のIPデータグラムを特定する情報を保持する保持工程と、を有し、

前記処理工程では、前記保持工程にて保持された情報で特定されるIPデータグラムを受信した場合、該IPデータグラムをリアセンブル処理せず、

前記保持工程では、前記処理工程にてリアセンブル処理が終了したIPデータグラムを特定する情報を保持することを特徴とする情報処理装置の処理方法。 - 情報処理装置の処理方法であって、

処理手段が、フラグメント化されたIPデータグラムを受信し、該IPデータグラムをリアセンブル処理する処理工程と、

保持手段が、リアセンブル処理対象外のIPデータグラムを特定する情報を保持する保持工程と、を有し、

前記処理工程では、前記保持工程にて保持された情報で特定されるIPデータグラムを受信した場合、該IPデータグラムをリアセンブル処理せず、

前記保持工程では、一定時間内にアセンブル処理が終了しなかったIPデータグラムを特定する情報を保持することを特徴とする情報処理装置の処理方法。 - 情報処理装置の処理方法であって、

処理手段が、フラグメント化されたIPデータグラムを受信し、該IPデータグラムをリアセンブル処理する処理工程と、

保持手段が、リアセンブル処理対象外のIPデータグラムを特定する情報を保持する保持工程と、を有し、

前記処理工程では、前記リアセンブル処理を開始した後、前記保持工程にて保持される情報で特定されるIPデータグラムを受信した場合、該IPデータグラムをリアセンブル処理しないで前記開始したリアセンブル処理を終了させることを特徴とする情報処理装置の処理方法。 - コンピュータを請求項1乃至12のいずれか1項に記載の情報処理装置として動作させるためのプログラム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009126822A JP5473406B2 (ja) | 2008-07-18 | 2009-05-26 | ネットワーク処理装置及びその処理方法 |

| US12/501,407 US20100014542A1 (en) | 2008-07-18 | 2009-07-11 | Network processing apparatus and processing method thereof |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008187913 | 2008-07-18 | ||

| JP2008187913 | 2008-07-18 | ||

| JP2009126822A JP5473406B2 (ja) | 2008-07-18 | 2009-05-26 | ネットワーク処理装置及びその処理方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010045767A JP2010045767A (ja) | 2010-02-25 |

| JP2010045767A5 JP2010045767A5 (ja) | 2012-06-28 |

| JP5473406B2 true JP5473406B2 (ja) | 2014-04-16 |

Family

ID=41530256

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009126822A Expired - Fee Related JP5473406B2 (ja) | 2008-07-18 | 2009-05-26 | ネットワーク処理装置及びその処理方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20100014542A1 (ja) |

| JP (1) | JP5473406B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5070125B2 (ja) * | 2008-05-19 | 2012-11-07 | キヤノン株式会社 | 受信装置及びその方法、通信システム及びその方法、並びに、プログラム |

| JP2012049883A (ja) * | 2010-08-27 | 2012-03-08 | Nec Access Technica Ltd | 通信装置およびパケット処理方法 |

| US8824437B2 (en) * | 2011-03-02 | 2014-09-02 | Ricoh Company, Ltd. | Wireless communications device, electronic apparatus, and methods for determining and updating access point |

| JP5429902B2 (ja) * | 2012-03-23 | 2014-02-26 | Necインフロンティア株式会社 | 通信システム、通信方法、及び通信プログラム |

| US8761181B1 (en) * | 2013-04-19 | 2014-06-24 | Cubic Corporation | Packet sequence number tracking for duplicate packet detection |

| JPWO2016103568A1 (ja) * | 2014-12-26 | 2017-10-12 | 日本電気株式会社 | パケット処理装置、方法、プログラム |

| US10089339B2 (en) * | 2016-07-18 | 2018-10-02 | Arm Limited | Datagram reassembly |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7058974B1 (en) * | 2000-06-21 | 2006-06-06 | Netrake Corporation | Method and apparatus for preventing denial of service attacks |

| DE60103331T2 (de) * | 2000-07-05 | 2004-09-23 | Roke Manor Research Ltd., Romsey | Verfahren zum Betreiben eines Puffers für das Wiederzusammenstellen von Paketen und Netzwerk-Router |

| US7356599B2 (en) * | 2001-08-30 | 2008-04-08 | International Business Machines Corporation | Method and apparatus for data normalization |

| US7403999B2 (en) * | 2001-12-28 | 2008-07-22 | International Business Machines Corporation | Classification support system and method for fragmented IP packets |

| US8370936B2 (en) * | 2002-02-08 | 2013-02-05 | Juniper Networks, Inc. | Multi-method gateway-based network security systems and methods |

| US7843968B2 (en) * | 2002-09-30 | 2010-11-30 | Sanyo Electric Co., Ltd. | Communication apparatus and applications thereof |

| US7454499B2 (en) * | 2002-11-07 | 2008-11-18 | Tippingpoint Technologies, Inc. | Active network defense system and method |

| US7706378B2 (en) * | 2003-03-13 | 2010-04-27 | Sri International | Method and apparatus for processing network packets |

| WO2005050935A1 (ja) * | 2003-11-21 | 2005-06-02 | Mitsubishi Denki Kabushiki Kaisha | 侵入検知装置およびその方法 |

| US7792147B1 (en) * | 2004-02-09 | 2010-09-07 | Symantec Corporation | Efficient assembly of fragmented network traffic for data security |

| JP4490331B2 (ja) * | 2004-08-03 | 2010-06-23 | 富士通株式会社 | 断片パケット処理方法及びこれを用いるパケット転送装置 |

| US20060198375A1 (en) * | 2004-12-07 | 2006-09-07 | Baik Kwang H | Method and apparatus for pattern matching based on packet reassembly |

| JP2007267051A (ja) * | 2006-03-29 | 2007-10-11 | Nec Engineering Ltd | パケット受信回路 |

| US7724776B2 (en) * | 2007-10-30 | 2010-05-25 | Telefonaktiebolaget L M Ericsson (Publ) | Method and ingress node for handling fragmented datagrams in an IP network |

| US8320372B2 (en) * | 2008-06-23 | 2012-11-27 | Alcatel Lucent | Processing of packet fragments |

-

2009

- 2009-05-26 JP JP2009126822A patent/JP5473406B2/ja not_active Expired - Fee Related

- 2009-07-11 US US12/501,407 patent/US20100014542A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010045767A (ja) | 2010-02-25 |

| US20100014542A1 (en) | 2010-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5473406B2 (ja) | ネットワーク処理装置及びその処理方法 | |

| US8526441B2 (en) | System and method for handling out-of-order frames | |

| US7613813B2 (en) | Method and apparatus for reducing host overhead in a socket server implementation | |

| US7953817B2 (en) | System and method for supporting TCP out-of-order receive data using generic buffer | |

| US7535907B2 (en) | TCP engine | |

| US9485178B2 (en) | Packet coalescing | |

| US7397800B2 (en) | Method and system for data placement of out-of-order (OOO) TCP segments | |

| EP1537695B1 (en) | System and method for tcp offload | |

| US7065086B2 (en) | Method and system for efficient layer 3-layer 7 routing of internet protocol (“IP”) fragments | |

| TWI332150B (en) | Processing data for a tcp connection using an offload unit | |

| US20050243834A1 (en) | Packet transfer method and device | |

| US7237031B2 (en) | Method and apparatus for caching protocol processing data | |

| KR101018575B1 (ko) | Rx fifo 버퍼를 사용하여 고속 네트워크애플리케이션에서 rx 패킷을 프로세싱하는 시스템 및방법 | |

| JP4779955B2 (ja) | パケット処理装置及びパケット処理方法 | |

| US20070022212A1 (en) | Method and system for TCP large receive offload | |

| EP1473867A2 (en) | System, method, and computer program product for ack promotion in a cable modem environment | |

| WO2010075795A1 (zh) | 分片信息处理的方法和装置 | |

| US20150264141A1 (en) | Communication apparatus, information processor, communication method, and computer-readable storage medium | |

| EP1460804B1 (en) | System and method for handling out-of-order frames (fka reception of out-of-order tcp data with zero copy service) | |

| JP2007274056A (ja) | データグラム再組立装置 | |

| US20060221827A1 (en) | Tcp implementation with message-count interface | |

| JP4769316B2 (ja) | パケットキューイング装置およびパケットキューイング方法 | |

| WO2004021143A2 (en) | Method and system for data placement of out-of-order (ooo) tcp segments |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120511 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120511 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130828 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130902 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131017 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131029 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140204 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5473406 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| LAPS | Cancellation because of no payment of annual fees |