JP5433966B2 - シフトレジスタおよびそれを用いた表示装置 - Google Patents

シフトレジスタおよびそれを用いた表示装置 Download PDFInfo

- Publication number

- JP5433966B2 JP5433966B2 JP2008094104A JP2008094104A JP5433966B2 JP 5433966 B2 JP5433966 B2 JP 5433966B2 JP 2008094104 A JP2008094104 A JP 2008094104A JP 2008094104 A JP2008094104 A JP 2008094104A JP 5433966 B2 JP5433966 B2 JP 5433966B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- voltage

- current path

- output

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Shift Register Type Memory (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Description

表示パネル上には、表示素子がマトリクス状に配置されている。走査ラインは行方向に並んだ各表示素子を接続する。データラインは列方向に並んだ各表示素子を接続する。

走査ドライバは、各走査ラインに順次走査パルスを印加し、各走査ラインに接続された表示素子を順次選択する。信号ドライバは、各データラインに画像データに対応した信号電圧を印加して、選択されている表示素子に対して画像データを書き込む。

小型化とコスト低減のためには、走査ドライバと信号ドライバあるいはその何れか一方をa−Siまたはp−Siを用いた薄膜トランジスタ(TFT,Thin Film Transistor)で、例えば表示素子と一体的に形成することが好ましい。更には、a−Siは、p−Siより比較的低コストで形成することができため、コスト低減のためにはa−SiによるTFTを用いることが好ましい。

ただし、a−Siは、ホールの移動度が極端に小さい。このため、a−SiによるTFTを用いる場合には、pチャネルTFTを製造することは困難であり、nチャネルTFTのみで回路を構成せざるを得ない。

請求項3に記載の発明は、請求項2に記載のシフトレジスタにおいて、前記インバータ回路は、更に、第6の電流路と第6の制御端子を有し、前記第6の電流路の一端に前記第1のクロック信号が印加され、前記第6の制御端子に前記リセット信号が印加される第6の薄膜トランジスタと、第7の電流路と第7の制御端子を有し、前記第7の電流路の一端が前記第6の薄膜トランジスタの前記第6の電流路の他端及び前記第5の薄膜トランジスタの前記第5の電流路の一端に接続され、前記第7の電流路の他端に前記基準電位の電圧が印加され、前記第7の制御端子に前記入力信号が印加される第7の薄膜トランジスタと、を有することを特徴とする。

図1は、本発明の実施の形態に係る液晶表示装置の一例を示す図であり、図2は、走査ラインに順次印加される走査パルスを示す図である。アクティブマトリクス駆動方式の液晶表示装置100は、図1に示すように、表示パネル1と、走査ドライバ2と、信号ドライバ3とを有している。

レジスタ回路40は、入力端子INと、出力端子OUTと、リセット端子RSTと、クロック端子CKmと、クロック端子CKpと、ローレベル電源電圧端子Vssとを有する。

または、走査ドライバ2を連続して駆動する場合には、1段目のレジスタ40の入力端子INに、最初の画像の表示を開始するときにイニシャルパルスとしてハイレベルのスタート信号を供給する。そして、2枚目以降の画像を表示するときには、1段目のレジスタ回路40の入力端子INに、スタート信号として最終段(n段目)のレジスタ回路40の出力端子OUTから出力される出力信号OUT(n)を供給しても良い。

クロック信号CK1とクロック信号CK2は2相クロック信号であり、方形波電圧出力回路41はパルス信号のクロック信号CK1を出力する回路であり、方形波電圧出力回路42はパルス信号のクロック信号CK2を出力する回路である。各レジスタ回路40のクロック端子CKpとクロック端子CKmにはクロック信号CK1とクロック信号CK2が交互に印加される。

nチャネルTFT52は、リセット端子RSTにハイレベルのリセット信号が入力すると、オン状態となって電流路の一端と他端とが導通し、ローレベルの電圧をノードn1に印加する。

図8に示す期間taは、入力期間である。入力期間では、図8(B)と図8(C)に示すように、クロック端子CKmにハイレベルの電圧が印加されているとき、入力端子INにハイレベルの入力信号が入力する。これにより、nチャネルTFT51aの電流路の一端と他端が導通し、図8(E)に示すように、ハイレベル電源電圧VddよりもnチャネルTFT51aのしきい値電圧Vthだけ低下した電圧がノードn1に印加される。

入力期間中、nチャネルTFT71は電流路の一端と他端が導通しているが、クロック端子CKpにローレベルの電圧が印加されているため、図8(F)に示すように、ノードn2(出力端子OUT)の電圧はローレベルである。

出力期間中、図8(C)と図8(D)に示すように、入力信号とリセット信号はともにローレベルである。このため、ノードn1はフローティングとなっている。このとき、ノードn1の電圧は、図8(E)に示すように、チャージポンプと同様の原理によってハイレベル電源電圧Vddを超えて上昇する。すなわち、ノードn1の電圧は、入力期間中にnチャネルTFT71のゲート−ドレイン電極間の浮遊容量や容量Ccに蓄積された電荷により生じる電圧と、クロック端子CKpから供給される電圧の和となる。

このように、出力期間中、nチャネルTFT71のゲート電極に印加される電圧はハイレベル電源電圧Vddよりも高くなる。このため、ノードn2(出力端子OUT)の電圧は、nチャネルTFT71のしきい値電圧Vth分の低下の影響を受けることがなく、ハイレベル電源電圧Vddまでフルスイングする。

図9は、出力期間tbとリセット期間tcを拡大した図である。図9(A)に示すように、出力期間tbに、クロック端子CKpに印加される電圧はローレベルとなる。しかし、図9(E)に示すように、リセット期間tcにリセット信号が入力するまでノードn1の電圧はハイレベルのままである。このとき、nチャネルTFT71の電流路の一端と他端は導通している。このため、矢印で示すようにノードn2(出力端子OUT)の電圧はローレベルとなる。その後、図9(D)に示すように、リセット信号RSTが入力すると、nチャネルTFT52の電流路の一端と他端が導通し、図9(E)に示すように、ノードn1の電圧はローレベルとなる。これにより、nチャネルTFT71はオフとなり、電流路の一端と他端が非導通となってノードn2はフローティングとなる。ノードn2(出力端子OUT)がフローティングである間、ノードn2(出力端子OUT)はローレベルの電圧を保持する。

ここで、図8(B)と図8(E)に示すように、出力期間tbを除くと、クロック端子CKmの電圧はノードn1の電圧より高いか、またはクロック端子CKmとノードn1の電圧は等しい。この場合、nチャネルTFT51aは、ノードn1に接続されている電流路の他端がソース電極であり、クロック端子CKmに接続されている電流路の一端がドレイン電極である。

一方、出力期間tbでは、クロック端子CKmの電圧はノードn1の電圧より低い。この場合、nチャネルTFT51aは、ノードn1に接続されている電流路の他端がドレイン電極であり、クロック端子CKmに接続されている電流路の一端がソース電極である。

このように、nチャネルTFT51aは、電流路の一端と他端のうちいずれがソース電極であり、いずれがドレイン電極であるかが変化する。

図10に示す保持回路50bは、nチャネルTFT51bの電流路の一端にハイレベル電源電圧Vddが供給される点が、図5の保持回路50aのnチャネルTFT51aと異なる。nチャネルTFT52は、保持回路50aと保持回路50bで同一である。

図5における保持回路50aを保持回路50bに置き変えたレジスタ回路40も、レジスタ回路40aと同様に動作する。しかし、nチャネルTFT51aとnチャネルTFT51bは、しきい値電圧Vthが劣化する程度が異なる。

一方、クロック端子CKmに接続されているnチャネルTFT51aのソース電極には、図8(B)に示すように、−15Vが印加される。しかし、nチャネルTFT51bのソース電極には、+15V(ハイレベル電源電圧Vdd)が印加される。このため、nチャネルTFT51aとnチャネルTFT51bのゲート−ソース間電圧Vgsは、それぞれ0Vと−30Vであり、異なる。

nチャネルTFT51aもクロック端子CKmに印加される電圧がハイレベル(例えば、+15V)であるときはリセット期間と同じく、ゲート−ソース間電圧Vgs=0V、ゲート−ドレイン間電圧Vgd=−30Vである。

一方、クロック端子CKmに印加される電圧がローレベル(例えば、−15V)であるとき、nチャネルTFT51aのゲート−ソース間電圧Vgs=0V、ゲート−ドレイン間電圧Vgd=0Vである。

上述したように、nチャネルTFT51aは、出力期間tbのゲート−ソース間電圧Vgsが0Vであり、および非動作期間でCKm端子の電圧がローレベル(−15V)であるときのゲート−ドレイン間電圧Vgdも0Vである。一方、nチャネルTFT51bは、出力期間tbのゲート−ソース間電圧Vgsが−30Vであり、非動作期間も常にゲート−ドレイン間電圧Vgdが−30Vである。

しかも、保持回路50aのnチャネルTFT51aは非動作期間でCKm端子の電圧がローレベル(例えば、−15V)であるとき、ドレイン−ソース間電圧Vdsが0Vである。このとき、nチャネルTFT51aにはリーク電流が流れない。従って、nチャネルTFT51aは非動作期間のリーク電流がnチャネルTFT51bのリーク電流の概ね半分に減少する。

従って、保持回路50aを用いたレジスタ回路40aは、保持回路50bを用いたレジスタ回路40よりも長期間安定して動作し、消費電力が減少する。

レジスタ回路40bは、保持回路50aと、インバータ回路60aと、出力回路70bとを有している。レジスタ回路40bは、インバータ回路60aが付加され、出力回路70bがnチャネルTFT72を含む点で図5のレジスタ回路40aと異なる。図5と図11の同じ構成要素には同じ符号が付されている。

nチャネルTFT72は、図12(G)に示すように、非動作期間に電流路の一端と他端が導通し、ノードn2(出力端子OUT)の電圧をローレベル電源電圧Vssに固定する。非動作期間のノードn1の電圧は、図12(E)に示すように、フローティングとなっているが、ノードn2の電位が安定しているため、容量Ccを介してノードn1の電位も安定化する。

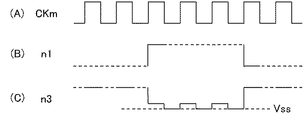

nチャネルTFT61aは、クロック端子CKmにハイレベルの電圧が印加されるとき、電流路の一端と他端が導通し、ノードn3にハイレベルの電圧を印加する。一方、nチャネルTFT61aは、クロック端子CKmにローレベルの電圧が印加されるとき、電流路の一端と他端が非導通となる。

このとき、クロック端子CKmの電圧がローレベルである間、nチャネルTFT61aの電流路の一端と他端は非導通となるため、図13(C)に示すように、ノードn3の電圧はローレベル電源電圧Vssまでフルスイングする。

一方、クロック端子CKmの電圧がハイレベルである間は、nチャネルTFT61aが導通し、nチャネルTFT61aとnチャネルTFT62を通って貫通電流が流れる。このため、図13(C)に示すように、ノードn3の電圧はローレベル電源電圧Vssから上昇する。

ここで、出力期間tbには、図12(B)に示すように、クロック端子CKmの電圧はローレベルである。このため、nチャネルTFT61aの電流路の一端と他端は非導通である。従って、図12(F)に示すように、ノードn3の電圧は出力期間tbにローレベル電源電圧Vssまでフルスイングする。

このように、レジスタ回路40bが図3に示すようにシフトレジスタ200を構成するとき、nチャネルTFT72の電流路の一端と他端が非導通とならなければならない出力期間tbには、ノードn3の電圧はローレベル電源電圧Vssまでフルスイングする。

nチャネルTFT61aのオン抵抗が小さくなると、図12(F)に示すように、入力期間taにおいて、ノードn3の電圧が十分に小さなレベルまで下がらない。しかし、図12(A)と(G)に示すように、入力期間taには出力回路70bのクロック端子CKpに印加される電圧と出力信号OUTは両方ともローレベルである。nチャネルTFT71の電流路の両端の電圧とnチャネルTFT72の電流路の両端の電圧が全てローレベルであるため、ノードn3の電圧が高くても問題は無い。

一方、上述したように、入力期間taには、nチャネルTFT61aとnチャネルTFT62が両方とも導通し、貫通電流が流れる。このとき、nチャネルTFT61aのしきい値電圧Vthは増加する。

また、上述したように、nチャネルTFT61aはチャネル幅を広くし、電流路の一端と他端の間に流れる電流の電流密度を小さくすることができる。

これらの効果により、nチャネルTFT61aは、劣化しにくく、インバータ回路60aを用いるレジスタ回路40aは長期間安定して動作する。

図14に示すレジスタ回路40cは、保持回路50bと、インバータ回路60aと、出力回路70bとを有している。レジスタ回路40cは、図11に示したレジスタ回路40bの保持回路50aを、図10に示した保持回路50bに置き換えたものである。レジスタ回路40cは、レジスタ回路40bと同様に動作する。

図15に示すレジスタ回路40dは、保持回路50cと、インバータ回路60aと、出力回路70bとを有している。レジスタ回路40dは、図11に示したレジスタ回路40bの保持回路50aを、保持回路50cに置き換えたものである。

レジスタ回路40dも、レジスタ回路40bと同様に動作する。

レジスタ回路40eは、保持回路50dと、インバータ回路60bと、出力回路70bとを有している。

レジスタ回路40eは、保持回路50dがnチャネルTFT53を含み、インバータ回路60bがnチャネルTFT63とnチャネルTFT64を含む点で図11のレジスタ回路40bと異なる。図11と図16の同じ構成要素には同じ符号が付されている。

nチャネルTFT53は、非動作期間のノードn1の電圧をローレベル電源電圧Vssに固定する。非動作期間のノードn1の電圧が安定化するため、ノイズに強くなり、出力回路70bに含まれる容量Ccを小さくすることができる。

なお、保持回路50dは、保持回路50bまたは保持回路50cにnチャネルTFT53を付加した構成としても良い。

nチャネルTFT63は、ゲート電極がリセット端子RSTに接続され、電流路の一端がクロック端子CKmに接続され、電流路の他端がノードn3に接続されている。nチャネルTFT64は、ゲート電極が入力端子INに接続され、電流路の一端がローレベル電源電圧端子Vssに接続され、電流路の他端がノードn3に接続されている。

nチャネルTFT63は、保持回路50aに含まれるnチャネルTFT51aと同様の理由により、しきい値電圧Vthの減少が抑えられ、劣化しにくい。

10…表示素子

51a、52、61a、62、63、71、72…nチャネルTFT

40a、40b、40c、40d、40e…レジスタ回路

50a、50b、50c、50d…保持回路

60a、60b…インバータ回路

70a、70b…出力回路

100…液晶表示装置

200…シフトレジスタ

LS1〜LSn…走査ライン

Claims (7)

- 縦続接続された複数のレジスタ回路からなる複数段のシフトレジスタであって、

前記各レジスタ回路は、

所定の基準電位の電圧と、前記基準電位より高い電位を有する第1の電圧と該第1の電圧より低い電位の第2の電圧とを交互に有する第1のクロック信号と、が印加され、前段の出力信号が入力信号として印加され、次段の出力信号がリセット信号として入力され、前記第1のクロック信号と前記入力信号と前記リセット信号とに基づく第1の信号を出力する保持回路と、

前記第1のクロック信号と前記基準電位の電圧と前記第1の信号とが印加され、前記第1のクロック信号と前記第1の信号とに基づく第2の信号を出力するインバータ回路と、

前記第1の信号と前記第2の信号とが印加され、該第1の信号と該第2の信号とに基づく信号を前記出力信号として出力する出力回路と、

を備え、

前記保持回路は、少なくとも、前記基準電位より高い電位を有する第3の電圧と、前記基準電位以上で前記第1の電圧より低い電位の第4の電圧とを有する信号を前記第1の信号として出力し、

前記インバータ回路は、前記第1のクロック信号の電圧レベルが前記第1の電圧であり、前記第1の信号の信号レベルが前記第3の電圧であるとき、前記第2の信号の信号レベルを前記基準電位に応じた電圧に変化させ、前記第1のクロック信号の電圧レベルが前記第1の電圧であり、前記第1の信号の信号レベルが前記第4の電圧であるとき、前記第2の信号の信号レベルを前記第1の電圧に応じた電圧に変化させる手段を有し、

前記保持回路は、第1の電流路と第1の制御端子を有し、前記第1の電流路の一端に前記第1のクロック信号が印加され、前記第1の制御端子に前記入力信号が印加され、前記第1の電流路の他端に前記第1の信号を出力する第1の薄膜トランジスタと、第2の電流路と第2の制御端子を有し、前記第2の電流路の一端が前記第1の薄膜トランジスタの前記第1の電流路の他端に接続され、前記第2の電流路の他端に前記基準電位の電圧が印加され、前記第2の制御端子に前記リセット信号が印加される第2の薄膜トランジスタと、第3の電流路と第3の制御端子を有し、前記第3の電流路の一端が前記第1の薄膜トランジスタの前記第1の電流路の他端に接続され、前記第3の電流路の他端に前記基準電位の電圧が印加され、前記第3の制御端子に前記第2の信号が印加され、該第2の信号の信号レベルが前記第1の電圧に応じた電圧であるときにオン状態となる第3の薄膜トランジスタと、を有し、

前記第1のクロック信号は、前記入力信号が印加される入力期間と前記リセット信号が入力されるリセット期間とにおいて前記第1の電圧に設定され、前記出力信号を出力する出力期間において前記第2の電圧に設定されることを特徴とするシフトレジスタ。 - 前記インバータ回路は、

第4の電流路と第4の制御端子を有し、前記第4の電流路の一端に前記第1のクロック信号が印加され、前記第4の制御端子が前記第4の電流路の一端に接続された第4の薄膜トランジスタと、

第5の電流路と第5の制御端子を有し、前記第5の電流路の一端が前記第4の薄膜トランジスタの前記第4の電流路の他端に接続されて前記第2の信号を出力し、前記第5の電流路の他端に前記基準電位の電圧が印加され、前記第5の制御端子に前記第1の信号が印加される第5の薄膜トランジスタと、

を有することを特徴とする請求項1に記載のシフトレジスタ。 - 前記インバータ回路は、更に、

第6の電流路と第6の制御端子を有し、前記第6の電流路の一端に前記第1のクロック信号が印加され、前記第6の制御端子に前記リセット信号が印加される第6の薄膜トランジスタと、

第7の電流路と第7の制御端子を有し、前記第7の電流路の一端が前記第6の薄膜トランジスタの前記第6の電流路の他端及び前記第5の薄膜トランジスタの前記第5の電流路の一端に接続され、前記第7の電流路の他端に前記基準電位の電圧が印加され、前記第7の制御端子に前記入力信号が印加される第7の薄膜トランジスタと、

を有することを特徴とする請求項2に記載のシフトレジスタ。 - 前記出力回路は、前記出力信号を出力する出力端子を有し、

2つの電圧レベルを交互に有する第2のクロック信号と、前記基準電位の電圧と、が印加され、

前記第2のクロック信号は電圧レベルとして、前記基準電位より高い電位を有する第5の電圧と、前記基準電位以上で前記第5の電圧より低い電位の第6の電圧と、を有し、前記第1のクロック信号が前記第1の電圧である期間と前記第2のクロック信号が前記第5の電圧である期間とは重ならないタイミングに設定され、

前記第1の信号の信号レベルが前記第3の電圧であり、前記第2の信号の信号レベルが前記基準電位に応じた電圧であるとき、前記出力信号の信号レベルを前記第2のクロック信号の信号レベルに近づけ、

前記第1の信号の信号レベルが前記第4の電圧であり、前記第2の信号の信号レベルが前記第1の電圧に応じた電圧であるとき、前記出力信号の信号レベルを前記基準電位に応じた電圧にする手段を有することを特徴とする請求項1に記載のシフトレジスタ。 - 前記出力回路は、第8の電流路と第8の制御端子を有し、前記第8の電流路の一端に前記第2のクロック信号が印加され、前記第8の電流路の他端が前記出力端子に接続され、前記第8の制御端子に前記第1の信号が印加される第8の薄膜トランジスタと、

第9の電流路と第9の制御端子を有し、前記第9の電流路の一端が前記第8の薄膜トランジスタの前記第8の電流路の他端に接続され、前記第9の電流路の他端に前記基準電位の電圧が印加され、前記第9の制御端子に前記第2の信号が印加される第9の薄膜トランジスタと、

一端が前記第8の薄膜トランジスタの前記第8の制御端子に接続され、他端が前記第8の薄膜トランジスタの前記第8の電流路の他端に接続された容量成分と、

を有することを特徴とする請求項4に記載のシフトレジスタ。 - 前記保持回路は、前記入力信号が印加されたとき、前記第1のクロック信号の信号レベルに応じた電圧を前記第1の信号として出力し、前記リセット信号が印加されたとき、前記基準電位に応じた電圧を前記第1の信号として出力する手段と、

前記入力信号及び前記リセット信号が前記入力端子及び前記リセット端子に印加されていないとき、前記第1の信号の信号レベルをそれ以前の信号レベルに基づく電圧にする手段と、

を有することを特徴とする請求項1に記載のシフトレジスタ。 - マトリクス状に配置された複数の表示素子と、

所定の方向に並んだ前記表示素子を接続する複数の走査ラインと、

請求項1から請求項6までのいずれか1項に記載のシフトレジスタを含み、当該シフトレジスタに含まれる個々のレジスタ回路の出力端子が個々の前記走査ラインに接続された走査ドライバと、

を備えることを特徴とする表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008094104A JP5433966B2 (ja) | 2008-03-31 | 2008-03-31 | シフトレジスタおよびそれを用いた表示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008094104A JP5433966B2 (ja) | 2008-03-31 | 2008-03-31 | シフトレジスタおよびそれを用いた表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009245564A JP2009245564A (ja) | 2009-10-22 |

| JP2009245564A5 JP2009245564A5 (ja) | 2011-05-12 |

| JP5433966B2 true JP5433966B2 (ja) | 2014-03-05 |

Family

ID=41307266

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008094104A Expired - Fee Related JP5433966B2 (ja) | 2008-03-31 | 2008-03-31 | シフトレジスタおよびそれを用いた表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5433966B2 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102012591B (zh) * | 2009-09-04 | 2012-05-30 | 北京京东方光电科技有限公司 | 移位寄存器单元及液晶显示器栅极驱动装置 |

| KR102139209B1 (ko) | 2010-02-18 | 2020-07-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 및 전자 장치 |

| TWI761910B (zh) * | 2011-08-29 | 2022-04-21 | 日商半導體能源研究所股份有限公司 | 半導體裝置 |

| JP6009153B2 (ja) | 2011-10-06 | 2016-10-19 | 株式会社ジャパンディスプレイ | 表示装置 |

| KR101354365B1 (ko) * | 2011-12-30 | 2014-01-23 | 하이디스 테크놀로지 주식회사 | 쉬프트 레지스터 및 이를 이용한 게이트 구동회로 |

| US9036766B2 (en) | 2012-02-29 | 2015-05-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2013160941A1 (ja) | 2012-04-25 | 2013-10-31 | パナソニック株式会社 | シフトレジスタ及び表示装置 |

| CN105632444B (zh) | 2016-03-16 | 2017-12-26 | 京东方科技集团股份有限公司 | 一种移位寄存器、栅极驱动电路及显示面板 |

| CN107146589A (zh) | 2017-07-04 | 2017-09-08 | 深圳市华星光电技术有限公司 | Goa电路及液晶显示装置 |

| CN107784977B (zh) * | 2017-12-11 | 2023-12-08 | 京东方科技集团股份有限公司 | 移位寄存器单元及其驱动方法、栅极驱动电路、显示装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3873165B2 (ja) * | 2000-06-06 | 2007-01-24 | カシオ計算機株式会社 | シフトレジスタ及び電子装置 |

| TWI220051B (en) * | 2003-05-22 | 2004-08-01 | Au Optronics Corp | Shift register circuit |

| JP2005251348A (ja) * | 2004-03-08 | 2005-09-15 | Casio Comput Co Ltd | シフトレジスタ回路及びその駆動制御方法 |

| JP4968671B2 (ja) * | 2006-11-27 | 2012-07-04 | Nltテクノロジー株式会社 | 半導体回路、走査回路、及びそれを用いた表示装置 |

| CN102651186B (zh) * | 2011-04-07 | 2015-04-01 | 北京京东方光电科技有限公司 | 移位寄存器及栅线驱动装置 |

-

2008

- 2008-03-31 JP JP2008094104A patent/JP5433966B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009245564A (ja) | 2009-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5433966B2 (ja) | シフトレジスタおよびそれを用いた表示装置 | |

| US8269713B2 (en) | Shift register | |

| US8023610B2 (en) | Semiconductor device and shift register circuit | |

| US8269714B2 (en) | Shift register | |

| US8018423B2 (en) | Shift register and liquid crystal display | |

| US8508457B2 (en) | Shift register for an active-matrix flat screen | |

| US7697655B2 (en) | Shift register and level controller | |

| JP4654923B2 (ja) | シフトレジスタ回路、及び表示駆動装置 | |

| JP5165153B2 (ja) | 走査信号線駆動回路およびそれを備えた表示装置、ならびに走査信号線の駆動方法 | |

| JP4959813B2 (ja) | 半導体装置及び表示装置 | |

| US20220059035A1 (en) | Gate driving circuit and display panel including the same | |

| JP5632001B2 (ja) | シフトレジスタ及び表示装置 | |

| TWI529682B (zh) | A scanning signal line driving circuit, a display device including the same, and a driving method of a scanning signal line | |

| US20150262703A1 (en) | Shift register, display device provided therewith, and shift-register driving method | |

| US9336736B2 (en) | Liquid crystal display device and method for driving auxiliary capacitance lines | |

| US10410597B2 (en) | Shift register | |

| JP2008112550A (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| CN107112051B (zh) | 单位移位寄存器电路、移位寄存器电路、单位移位寄存器电路的控制方法及显示装置 | |

| JP2009181612A (ja) | シフトレジスタ回路及び液晶表示装置 | |

| JP2007018299A (ja) | 電圧発生回路及び表示装置 | |

| JP2009017432A (ja) | レベルシフト回路および表示装置 | |

| JP4805353B2 (ja) | インバータ回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110329 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110329 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130319 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130517 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131112 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131125 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |