JP5367556B2 - デバッグ支援方法 - Google Patents

デバッグ支援方法 Download PDFInfo

- Publication number

- JP5367556B2 JP5367556B2 JP2009291746A JP2009291746A JP5367556B2 JP 5367556 B2 JP5367556 B2 JP 5367556B2 JP 2009291746 A JP2009291746 A JP 2009291746A JP 2009291746 A JP2009291746 A JP 2009291746A JP 5367556 B2 JP5367556 B2 JP 5367556B2

- Authority

- JP

- Japan

- Prior art keywords

- virtual

- application program

- program data

- program

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Debugging And Monitoring (AREA)

Description

上記第1および第2の仮想環境は上記応用プログラムの実行に関するデータをトレースしてトレースデータをそれぞれ作成し、

上記第3の仮想環境は上記第1および第2のプログラムデータを比較して差異を検出すると、上記第1および第2の仮想環境にトレース停止命令を送信し、

上記第1および第2の仮想環境は、上記トレース停止命令を受信するとトレースを停止するものである。

また、この発明は、同一の応用プログラムおよび同一のOSを搭載した第1および第2の仮想環境で、上記第1の仮想環境は1個のCPUにて上記応用プログラムが実行され上記応用プログラムの第1のプログラムデータを作成し、上記第2の仮想環境は複数個のCPUにて上記応用プログラムが実行され上記応用プログラムの第2のプログラムデータを作成し、第3の仮想環境は上記第1および第2の仮想環境上の上記第1および第2のプログラムデータを比較して差異を検出し、

上記第1および第2の仮想環境は第1および第2のデバッガをそれぞれ有し、上記第3の仮想環境が上記第1および第2のプログラムデータを比較して差異を検出すると、上記第1および第2の仮想環境にOS停止命令を送信し、

上記第1および第2の仮想環境は、上記OS停止命令を受信すると第1および第2のデバッガを起動するものである。

CPUを複数個使用した際に発生する応用プログラムの障害を容易にデバッグすることができる。

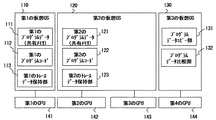

以下、本願発明の実施の形態について説明する。図1はこの発明の実施の形態1におけるデバッグ支援方法に用いられるシステムの構成を示す図、図2は図1に示したデバッグ支援方法の動作を説明するためのフローチャート、図3は1個のCPUにて処理を行う際の動作を示したフローチャート、図4は2個のCPUにて処理を行う際の動作を示したフローチャートである。図において、第1の仮想環境としての第1の仮想OS110と第2の仮想環境としての第2の仮想OS120とは同一の応用プログラムと同一のOSとを有するものである。第1の仮想OS110と第2の仮想OS120との異なる点は、第1の仮想OS110は第1のCPU141の1個のCPUのみにて処理されるのに対し、第2の仮想OS120は第2のCPU142および第3のCPU143の2個のCPUにて処理される点である。

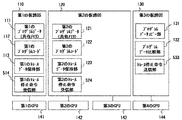

図7はこの発明の実施の形態2におけるデバッグ支援方法に用いられるシステムの構成を示す図、図8は図7に示したデバッグ支援方法の動作を説明するためのフローチャートである。上記実施の形態1では応用プログラムが動作する仮想OSがトレースデータをトレースし続ける場合について示したが、本実施の形態2においては、各仮想OS間の各プログラムデータに差異を検出した場合には、トレースデータの記録を停止し、容易にデバッグの支援を行うことができるものである。

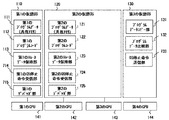

図9はこの発明の実施の形態3におけるデバッグ支援方法に用いられるシステムの構成を示す図、図10は図9に示したデバッグ支援方法の動作を説明するためのフローチャートである。上記実施の形態1では応用プログラムが動作する仮想OSがトレースデータをとり続ける場合について述べたが、本実施の形態3においては仮想OS間の各プログラムデータに差異が出た際に、仮想OSの動作を停止してデバッガを起動するものである。

112 第1のプログラムコード部、113 第1のトレースデータ保持部、

120 第2の仮想OS、121 第2のプログラムデータ、

132 第2のプログラムコード部、123 第2のトレースデータ保持部、

130 第3の仮想OS、131 プログラムデータコピー部、

132 プログラムデータ比較部、141 第1のCPU、142 第2のCPU、

143 第3のCPU、144 第4のCPU、344 第5のCPU、

514 第1のトレース停止命令受信部、524 第2のトレース停止命令受信部、

533 トレース停止命令送信部、714 第1のOS停止命令受信部、

715 第1のデバッガ部、724 第2のOS停止命令受信部、

725 第2のデバッガ部、733 OS停止命令送信部。

Claims (3)

- 同一の応用プログラムおよび同一のOSを搭載した第1および第2の仮想環境で、上記第1の仮想環境は1個のCPUにて上記応用プログラムが実行され上記応用プログラムの第1のプログラムデータを作成し、上記第2の仮想環境は複数個のCPUにて上記応用プログラムが実行され上記応用プログラムの第2のプログラムデータを作成し、第3の仮想環境は上記第1および第2の仮想環境上の上記第1および第2のプログラムデータを比較して差異を検出し、

上記第1および第2の仮想環境は上記応用プログラムの実行に関するデータをトレースしてトレースデータをそれぞれ作成し、

上記第3の仮想環境は上記第1および第2のプログラムデータを比較して差異を検出すると、上記第1および第2の仮想環境にトレース停止命令を送信し、

上記第1および第2の仮想環境は、上記トレース停止命令を受信するとトレースを停止するデバッグ支援方法。 - 同一の応用プログラムおよび同一のOSを搭載した第1および第2の仮想環境で、上記第1の仮想環境は1個のCPUにて上記応用プログラムが実行され上記応用プログラムの第1のプログラムデータを作成し、上記第2の仮想環境は複数個のCPUにて上記応用プログラムが実行され上記応用プログラムの第2のプログラムデータを作成し、第3の仮想環境は上記第1および第2の仮想環境上の上記第1および第2のプログラムデータを比較して差異を検出し、

上記第1および第2の仮想環境は第1および第2のデバッガをそれぞれ有し、上記第3の仮想環境が上記第1および第2のプログラムデータを比較して差異を検出すると、上記第1および第2の仮想環境にOS停止命令を送信し、

上記第1および第2の仮想環境は、上記OS停止命令を受信すると第1および第2のデバッガを起動するデバッグ支援方法。 - 上記第1および第2の仮想環境のプログラムデータは、メッセージキュであることを特徴とする請求項1または請求項2に記載のデバッグ支援方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009291746A JP5367556B2 (ja) | 2009-12-24 | 2009-12-24 | デバッグ支援方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009291746A JP5367556B2 (ja) | 2009-12-24 | 2009-12-24 | デバッグ支援方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011134033A JP2011134033A (ja) | 2011-07-07 |

| JP5367556B2 true JP5367556B2 (ja) | 2013-12-11 |

Family

ID=44346708

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009291746A Expired - Fee Related JP5367556B2 (ja) | 2009-12-24 | 2009-12-24 | デバッグ支援方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5367556B2 (ja) |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07271631A (ja) * | 1994-03-31 | 1995-10-20 | Fujitsu Ltd | デバッガ |

| JP4457581B2 (ja) * | 2003-05-28 | 2010-04-28 | 日本電気株式会社 | 耐障害システム、プログラム並列実行方法、耐障害システムの障害検出装置およびプログラム |

-

2009

- 2009-12-24 JP JP2009291746A patent/JP5367556B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011134033A (ja) | 2011-07-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7992042B2 (en) | Debug support device, and program for directing computer to perform debugging method | |

| JP4388518B2 (ja) | スレッドデバッグ装置、スレッドデバッグ方法及びプログラム | |

| US8677321B2 (en) | User-space probe based debugging | |

| US7966536B2 (en) | Method and apparatus for automatic scan completion in the event of a system checkstop | |

| JP2014507720A (ja) | デバッグ例外生成の制御 | |

| CN104932972B (zh) | 一种反动态调试应用程序的方法及装置 | |

| CN110209615A (zh) | 执行不可屏蔽中断的方法和装置 | |

| JP5367556B2 (ja) | デバッグ支援方法 | |

| JP5641181B2 (ja) | 二重化処理装置 | |

| JP6318214B2 (ja) | 汎用マイクロプロセッサを用いたplcのデバッグ方法 | |

| JP5163120B2 (ja) | デバッグシステム、デバッグ方法、およびプログラム | |

| JP2011018187A (ja) | 試験方法、試験プログラム、試験装置、及び試験システム | |

| JP2010015364A (ja) | マルチプロセッサシステム及び情報処理装置 | |

| CN110059040B (zh) | 一种基于risc-v架构的可嵌套异常和非屏蔽中断系统及方法 | |

| JP4633553B2 (ja) | デバッグシステム、デバッグ方法およびプログラム | |

| JP2010061258A (ja) | デュプレックスプロセッサシステム及びプロセッサ二重化方法 | |

| JP4872934B2 (ja) | コンピュータシステム、クライアントコンピュータ、os終了方法およびos終了プログラム | |

| JP2018206233A (ja) | 情報処理装置、プロセス切り替え方法及びプログラム | |

| JP2007213396A (ja) | デバッグシステム、オペレーションシステム、デバッグ方法、プログラム | |

| JP2024158473A (ja) | 情報処理システム、制御プログラム、及び例外プログラム | |

| JP2017199180A (ja) | 画像処理装置 | |

| JP2005196351A (ja) | コンピュータシステムおよびその保守方法 | |

| JP2014206807A (ja) | ソフトウェア検査方法及びプログラム | |

| KR20120047045A (ko) | 소프트웨어의 함수 추적을 통한 디버깅 방법 | |

| JP2013175076A (ja) | 情報処理装置および情報処理装置における異常分析方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130725 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130806 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130823 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130903 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130911 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5367556 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |