JP5285690B2 - 並列コンピュータ・システム、並列コンピュータ・システム上のノード・トラフィックを動的に再経路指定するためのコンピュータ実装方法、コンピュータ可読記録媒体及びコンピュータ・プログラム - Google Patents

並列コンピュータ・システム、並列コンピュータ・システム上のノード・トラフィックを動的に再経路指定するためのコンピュータ実装方法、コンピュータ可読記録媒体及びコンピュータ・プログラム Download PDFInfo

- Publication number

- JP5285690B2 JP5285690B2 JP2010503440A JP2010503440A JP5285690B2 JP 5285690 B2 JP5285690 B2 JP 5285690B2 JP 2010503440 A JP2010503440 A JP 2010503440A JP 2010503440 A JP2010503440 A JP 2010503440A JP 5285690 B2 JP5285690 B2 JP 5285690B2

- Authority

- JP

- Japan

- Prior art keywords

- node

- network

- nodes

- computer system

- parallel computer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 33

- 238000004590 computer program Methods 0.000 title claims 7

- 238000012544 monitoring process Methods 0.000 claims description 11

- 230000007246 mechanism Effects 0.000 claims description 10

- 230000008569 process Effects 0.000 claims description 10

- 238000004364 calculation method Methods 0.000 claims description 5

- 238000001514 detection method Methods 0.000 claims description 4

- 238000010586 diagram Methods 0.000 description 13

- 108090000623 proteins and genes Proteins 0.000 description 13

- 238000004891 communication Methods 0.000 description 9

- 238000012545 processing Methods 0.000 description 6

- 238000005192 partition Methods 0.000 description 4

- 230000008439 repair process Effects 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 238000011084 recovery Methods 0.000 description 2

- 239000002699 waste material Substances 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

- H04L45/22—Alternate routing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/20—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements

- G06F11/202—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where processing functionality is redundant

- G06F11/2023—Failover techniques

- G06F11/203—Failover techniques using migration

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/16—Combinations of two or more digital computers each having at least an arithmetic unit, a program unit and a register, e.g. for a simultaneous processing of several programs

- G06F15/163—Interprocessor communication

- G06F15/173—Interprocessor communication using an interconnection network, e.g. matrix, shuffle, pyramid, star, snowflake

- G06F15/17356—Indirect interconnection networks

- G06F15/17368—Indirect interconnection networks non hierarchical topologies

- G06F15/17381—Two dimensional, e.g. mesh, torus

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L41/00—Arrangements for maintenance, administration or management of data switching networks, e.g. of packet switching networks

- H04L41/06—Management of faults, events, alarms or notifications

- H04L41/0654—Management of faults, events, alarms or notifications using network fault recovery

- H04L41/0659—Management of faults, events, alarms or notifications using network fault recovery by isolating or reconfiguring faulty entities

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

- H04L45/02—Topology update or discovery

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

- H04L45/28—Routing or path finding of packets in data switching networks using route fault recovery

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

- H04L45/34—Source routing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/20—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements

- G06F11/202—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where processing functionality is redundant

- G06F11/2038—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where processing functionality is redundant with a single idle spare processing component

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/20—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements

- G06F11/202—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where processing functionality is redundant

- G06F11/2051—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where processing functionality is redundant in regular structures

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Quality & Reliability (AREA)

- Computer Hardware Design (AREA)

- Mathematical Physics (AREA)

- Software Systems (AREA)

- Hardware Redundancy (AREA)

- Multi Processors (AREA)

- Computer And Data Communications (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Retry When Errors Occur (AREA)

Description

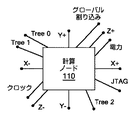

110・・・計算ノード

140・・・サービス・ノード

142・・・ノード/ネットワーク監視機構

144・・・問題リスト

150・・・制御システム・ネットワーク

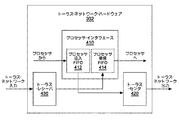

392・・・トーラス・ネットワーク・ハードウェア

394・・・ツリー・ネットワーク・ハードウェア

396・・・グローバル割り込みネットワーク・ハードウェア

510・・・トーラス・ネットワーク・パケット

512・・・パケット・ヘッダ

516・・・ヒント・ビット

Claims (17)

- 並列コンピュータ・システムであって、

論理的な3次元デカルト配列内で、各ノードをその6個の最近隣ノード(X+、X−、Y+、Y−、Z+及びZ−)に接続するトーラス・ネットワークによって接続された複数のノードと、

前記並列コンピュータ・システムの前記複数のノード及びネットワーク接続を監視し且つノード及びネットワーク接続の問題リストを作成するノード/ネットワーク監視機構とを備え、

前記複数のノードの少なくともいずれかは、前記問題リスト内のノード及びネットワーク接続を回避するように、各ノードから送信されるデータ・パケット内に6個の最近隣ノード(X+、X−、Y+、Y−、Z+及びZ−)用に設定されたヒント・ビットを使用して、データ・パケットを障害ノード又は障害ネットワーク接続を迂回して1つ以上の前記ネットワーク接続を介して動的に経路指定するものである、並列コンピュータ・システム。 - 前記ヒント・ビットが、トーラス・ネットワーク上でトラフィックを送信すべき好ましい方向を指示する複数の2進値であり、6つのビットをもって、XYZの順序で、X+ X− Y+ Y− Z+ Z−のように定義され、X+又はX−の何れか一方を設定することができるが、両方を設定することができないものである、請求項1に記載の並列コンピュータ・システム。

- 前記ヒント・ビット(516)が、前記ネットワーク接続を介して送信されるデータ・パケット(510)のヘッダ(512)内に含まれる、請求項1又は請求項2に記載の並列コンピュータ・システム。

- 前記ノードは、更新された前記問題リストを検出し、前記検出に応じて当該ノード上で実行中のアプリケーションを一時的に停止し、更新された前記問題リストに対応する前記ヒント・ビットを使用してデータ・パケットを動的に経路指定するようにし、前記アプリケーションを一時的に停止された点から再開するものである、請求項1ないし請求項3の何れか1項に記載の並列コンピュータ・システム。

- 前記並列コンピュータ・システムが、前記複数のノードを3次元トーラス・ネットワークで相互接続した超並列コンピュータ・システムである、請求項1ないし請求項4の何れか1項に記載の並列コンピュータ・システム。

- ヒント・ビットを使用することにより、並列コンピュータ・システム上で実行中のアプリケーションを再始動することなく、ヒント・ビットを使用して、当該並列コンピュータ・システム内の論理的な3次元デカルト配列内で、各ノードをその6個の最近隣ノード(X+、X−、Y+、Y−、Z+及びZ−)に接続するトーラス・ネットワークによって接続された複数の計算ノード上のノード・トラフィックを動的に再経路指定するためのコンピュータ実装方法であって、

問題について前記複数の計算ノード及びネットワーク接続を監視し且つ障害ノード及び障害ネットワーク接続を問題リスト内で特定するステップと、

更新済みの問題リストを検出するステップと、

アプリケーションを実行中の計算ノードの実行を一時的に停止させるステップと、

前記問題リスト内のノード又はネットワーク接続を分離するように、各ノードから送信されるデータ・パケット内に6個の最近隣ノード(X+、X−、Y+、Y−、Z+及びZ−)用に設定されたヒント・ビットを設定するステップと、

一時的に停止させていた前記アプリケーションの実行を再開するステップとを含む、コンピュータ実装方法。 - 前記ヒント・ビットが、トーラス・ネットワーク上でトラフィックを送信すべき好ましい方向を指示する複数の2進値であり、6つのビットをもって、XYZの順序で、X+ X− Y+ Y− Z+ Z−のように定義され、X+又はX−の何れか一方を設定することができるが、両方を設定することができないものである、請求項6に記載のコンピュータ実装方法。

- 前記ヒント・ビット(516)が、前記ネットワーク接続を介して送信されるデータ・パケット(510)のヘッダ(512)内に含まれる、請求項6又は請求項7に記載のコンピュータ実装方法。

- 前記並列コンピュータ・システムが、前記複数の計算ノードを3次元トーラス・ネットワークで相互接続した超並列コンピュータ・システムである、請求項6ないし請求項8の何れか1項に記載のコンピュータ実装方法。

- 少なくとも1つの障害ノードのプロセスを少なくとも1つのバックアップ・ノードに移動させるステップをさらに含む、請求項6ないし請求項9の何れか1項に記載のコンピュータ実装方法。

- 計算ノードに対する輻輳ネットワークを検出するステップと、

トラフィックを当該輻輳ネットワークを迂回して経路指定するように少なくとも1つのヒント・ビットを設定するステップとをさらに含む、請求項6ないし請求項10の何れか1項に記載のコンピュータ実装方法。 - 論理的な3次元デカルト配列内で、各ノードをその6個の最近隣ノード(X+、X−、Y+、Y−、Z+及びZ−)に接続するトーラス・ネットワークを構成するネットワーク接続によって接続された複数のノードを有する並列コンピュータ・システムにおいて、

コンピュータを、

前記複数のノード及びネットワーク接続を監視し且つノード及びネットワーク接続の問題リストを作成するノード/ネットワーク監視機構として機能させ、そして

前記問題リスト内のノード及びネットワーク接続を回避するように、各ノードから送信されるデータ・パケット内に6個の最近隣ノード(X+、X−、Y+、Y−、Z+及びZ−)用に設定されたヒント・ビットを使用して、データ・パケットを前記ネットワーク接続を介して動的に経路指定するノード経路指定機構として機能させるためのコンピュータ・プログラム。 - 前記ヒント・ビットが、トーラス・ネットワーク上でトラフィックを送信すべき好ましい方向を指示する複数の2進値であり、6つのビットをもって、XYZの順序で、X+ X− Y+ Y− Z+ Z−のように定義され、X+又はX−の何れか一方を設定することができるが、両方を設定することができないものである、請求項12に記載のコンピュータ・プログラム。

- 前記ヒント・ビット(516)が、前記ネットワーク接続を介して送信されるデータ・パケット(510)のヘッダ(512)内に含まれる、請求項12又は請求項13に記載のコンピュータ・プログラム。

- 前記ノードは、更新された前記問題リストを検出し、前記検出に応じて当該ノード上で実行中のアプリケーションを一時的に停止し、更新された前記問題リストに対応する前記ヒント・ビットを使用してデータ・パケットを動的に経路指定するようにし、前記アプリケーションを一時的に停止された点から再開するものである、請求項12ないし請求項14の何れか1項に記載のコンピュータ・プログラム。

- 前記並列コンピュータ・システムが、前記複数のノードを3次元トーラス・ネットワークで相互接続した超並列コンピュータ・システムである、請求項12ないし請求項15の何れか1項に記載のコンピュータ・プログラム。

- 請求項6ないし請求項11の何れか1項に記載の方法の各ステップをコンピュータに実行させるためのコンピュータ・プログラム。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/736,811 US7644254B2 (en) | 2007-04-18 | 2007-04-18 | Routing data packets with hint bit for each six orthogonal directions in three dimensional torus computer system set to avoid nodes in problem list |

| US11/736,811 | 2007-04-18 | ||

| PCT/EP2008/053377 WO2008128836A2 (en) | 2007-04-18 | 2008-03-20 | Dynamically rerouting node traffic on a parallel computer system |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010525433A JP2010525433A (ja) | 2010-07-22 |

| JP5285690B2 true JP5285690B2 (ja) | 2013-09-11 |

Family

ID=39739647

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010503440A Expired - Fee Related JP5285690B2 (ja) | 2007-04-18 | 2008-03-20 | 並列コンピュータ・システム、並列コンピュータ・システム上のノード・トラフィックを動的に再経路指定するためのコンピュータ実装方法、コンピュータ可読記録媒体及びコンピュータ・プログラム |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7644254B2 (ja) |

| EP (1) | EP2156291A2 (ja) |

| JP (1) | JP5285690B2 (ja) |

| KR (1) | KR20090122209A (ja) |

| CN (1) | CN101663649B (ja) |

| TW (1) | TW200907702A (ja) |

| WO (1) | WO2008128836A2 (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2462492B (en) * | 2008-08-14 | 2012-08-15 | Gnodal Ltd | A multi-path network |

| WO2010060923A1 (en) * | 2008-11-26 | 2010-06-03 | Danmarks Tekniske Universitet | Biologically inspired hardware cell architecture |

| EP2399192A4 (en) * | 2009-02-13 | 2016-09-07 | Ab Initio Technology Llc | COMMUNICATION WITH DATA STORAGE SYSTEMS |

| US8479215B2 (en) * | 2009-08-18 | 2013-07-02 | International Business Machines Corporation | Decentralized load distribution to reduce power and/or cooling costs in an event-driven system |

| US9135215B1 (en) * | 2009-09-21 | 2015-09-15 | Tilera Corporation | Route prediction in packet switched networks |

| US8359404B2 (en) * | 2010-01-08 | 2013-01-22 | International Business Machines Corporation | Zone routing in a torus network |

| US8713294B2 (en) * | 2009-11-13 | 2014-04-29 | International Business Machines Corporation | Heap/stack guard pages using a wakeup unit |

| CA2782414C (en) * | 2009-12-14 | 2021-08-03 | Ab Initio Technology Llc | Specifying user interface elements |

| US8559307B2 (en) * | 2009-12-28 | 2013-10-15 | Empire Technology Development Llc | Routing packets in on-chip networks |

| US8140889B2 (en) * | 2010-08-23 | 2012-03-20 | International Business Machines Corporation | Dynamically reassigning a connected node to a block of compute nodes for re-launching a failed job |

| JP5750963B2 (ja) * | 2011-03-22 | 2015-07-22 | 富士通株式会社 | 並列計算機システム、制御装置、並列計算機システムの制御方法および並列計算機システムの制御プログラム |

| US9811233B2 (en) | 2013-02-12 | 2017-11-07 | Ab Initio Technology Llc | Building applications for configuring processes |

| US9424229B2 (en) * | 2013-02-13 | 2016-08-23 | Advanced Micro Devices, Inc. | Parallel torus network interconnect |

| US10996989B2 (en) * | 2016-06-13 | 2021-05-04 | International Business Machines Corporation | Flexible optimized data handling in systems with multiple memories |

| CN106130895B (zh) * | 2016-08-18 | 2019-11-15 | 中国联合网络通信集团有限公司 | Sdn网络故障的重路由方法及装置 |

| US11423083B2 (en) | 2017-10-27 | 2022-08-23 | Ab Initio Technology Llc | Transforming a specification into a persistent computer program |

| TWI686696B (zh) | 2018-08-14 | 2020-03-01 | 財團法人工業技術研究院 | 計算節點及其失效偵測方法與雲端資料處理系統 |

| JP7167687B2 (ja) * | 2018-12-18 | 2022-11-09 | 富士通株式会社 | 情報処理装置、情報処理方法および情報処理プログラム |

| US11057265B2 (en) * | 2019-06-27 | 2021-07-06 | Cerner Innovation, Inc. | Path check insight |

| JP2021135983A (ja) * | 2020-02-28 | 2021-09-13 | 京セラドキュメントソリューションズ株式会社 | データ連携システムおよびデータ収集システム |

| CN113364603B (zh) * | 2020-03-06 | 2023-05-02 | 华为技术有限公司 | 环形网络的故障恢复方法及物理节点 |

| CN114860511A (zh) * | 2022-04-29 | 2022-08-05 | 上海阵量智能科技有限公司 | 数据处理方法和装置、芯片、电子设备、介质 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| AU3059689A (en) * | 1988-02-04 | 1989-08-25 | City University, The | Improvements in or relating to data handling arrays |

| US5495426A (en) * | 1994-01-26 | 1996-02-27 | Waclawsky; John G. | Inband directed routing for load balancing and load distribution in a data communication network |

| JPH07239835A (ja) * | 1994-02-25 | 1995-09-12 | Hitachi Ltd | 並列計算機のネットワーク内データ転送制御方式 |

| US6865149B1 (en) * | 2000-03-03 | 2005-03-08 | Luminous Networks, Inc. | Dynamically allocated ring protection and restoration technique |

| US7729261B2 (en) * | 2004-08-10 | 2010-06-01 | Alcatel Lucent | Forwarding of network traffic in respect of differentiated restricted transit network nodes |

| US20070053283A1 (en) * | 2005-09-06 | 2007-03-08 | International Business Machines Corporation | Correlation and consolidation of link events to facilitate updating of status of source-destination routes in a multi-path network |

| US7839786B2 (en) | 2006-10-06 | 2010-11-23 | International Business Machines Corporation | Method and apparatus for routing data in an inter-nodal communications lattice of a massively parallel computer system by semi-randomly varying routing policies for different packets |

| US7835284B2 (en) | 2006-10-06 | 2010-11-16 | International Business Machines Corporation | Method and apparatus for routing data in an inter-nodal communications lattice of a massively parallel computer system by routing through transporter nodes |

| US7680048B2 (en) | 2006-10-06 | 2010-03-16 | International Business Machiens Corporation | Method and apparatus for routing data in an inter-nodal communications lattice of a massively parallel computer system by dynamically adjusting local routing strategies |

| US8031614B2 (en) | 2006-10-06 | 2011-10-04 | International Business Machines Corporation | Method and apparatus for routing data in an inter-nodal communications lattice of a massively parallel computer system by dynamic global mapping of contended links |

| US20080178177A1 (en) | 2007-01-19 | 2008-07-24 | Charles Jens Archer | Method and Apparatus for Operating a Massively Parallel Computer System to Utilize Idle Processor Capability at Process Synchronization Points |

| US7631169B2 (en) | 2007-02-02 | 2009-12-08 | International Business Machines Corporation | Fault recovery on a massively parallel computer system to handle node failures without ending an executing job |

| US7706275B2 (en) | 2007-02-07 | 2010-04-27 | International Business Machines Corporation | Method and apparatus for routing data in an inter-nodal communications lattice of a massively parallel computer system by employing bandwidth shells at areas of overutilization |

-

2007

- 2007-04-18 US US11/736,811 patent/US7644254B2/en not_active Expired - Fee Related

-

2008

- 2008-03-20 CN CN2008800124505A patent/CN101663649B/zh not_active Expired - Fee Related

- 2008-03-20 EP EP08718093A patent/EP2156291A2/en not_active Withdrawn

- 2008-03-20 KR KR1020097017336A patent/KR20090122209A/ko active IP Right Grant

- 2008-03-20 WO PCT/EP2008/053377 patent/WO2008128836A2/en active Application Filing

- 2008-03-20 JP JP2010503440A patent/JP5285690B2/ja not_active Expired - Fee Related

- 2008-04-15 TW TW097113660A patent/TW200907702A/zh unknown

Also Published As

| Publication number | Publication date |

|---|---|

| EP2156291A2 (en) | 2010-02-24 |

| CN101663649A (zh) | 2010-03-03 |

| JP2010525433A (ja) | 2010-07-22 |

| CN101663649B (zh) | 2012-07-18 |

| WO2008128836A2 (en) | 2008-10-30 |

| TW200907702A (en) | 2009-02-16 |

| KR20090122209A (ko) | 2009-11-26 |

| WO2008128836A3 (en) | 2008-12-18 |

| US20080263386A1 (en) | 2008-10-23 |

| US7644254B2 (en) | 2010-01-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5285690B2 (ja) | 並列コンピュータ・システム、並列コンピュータ・システム上のノード・トラフィックを動的に再経路指定するためのコンピュータ実装方法、コンピュータ可読記録媒体及びコンピュータ・プログラム | |

| JP5285061B2 (ja) | 並列コンピュータ・システム、並列コンピュータ・システム内の障害回復のためのコンピュータ実装方法、製品及びコンピュータ・プログラム | |

| JP3709795B2 (ja) | コンピュータシステムと、コンピュータシステム内のモジュール間の通信方法 | |

| US20190260504A1 (en) | Systems and methods for maintaining network-on-chip (noc) safety and reliability | |

| US9244759B2 (en) | Error recovery to enable error-free message transfer between nodes of a computer network | |

| JP2004062535A (ja) | マルチプロセッサシステムの障害処理方法、マルチプロセッサシステム及びノード | |

| WO2017118080A1 (zh) | 一种中央处理器cpu热移除、热添加方法及装置 | |

| CN102629912B (zh) | 面向无缓冲片上网络的容错偏转路由方法及装置 | |

| US20040216003A1 (en) | Mechanism for FRU fault isolation in distributed nodal environment | |

| JP5307151B2 (ja) | リンクに基づくシステムにおけるシステムルーティング情報の変更 | |

| JP2008165531A (ja) | 複数のノードを有するコンピュータ・システムの故障ノードをフェイルオーバー(修復)する方法 | |

| US7656789B2 (en) | Method, system and storage medium for redundant input/output access | |

| US7930584B2 (en) | Cell boundary fault detection system | |

| US7573810B2 (en) | Avoiding deadlocks in performing failovers in communications environments | |

| Marcon et al. | Phoenix NoC: A distributed fault tolerant architecture | |

| US7826379B2 (en) | All-to-all sequenced fault detection system | |

| US20230261971A1 (en) | Robust Vertical Redundancy Of Networking Devices | |

| CN108632142B (zh) | 节点控制器的路由管理方法和装置 | |

| JPH1027115A (ja) | コンピュータシステムの障害情報採取回路 | |

| US20190121573A1 (en) | Storage system and storage control apparatus | |

| WO2023165743A1 (en) | Reset of a multi-node system | |

| Sadawarti et al. | Fault-tolerant routing in unique-path multistage interconnection networks | |

| JP2021158563A (ja) | データ処理装置およびデータ処理方法 | |

| Falih Mahmood | A Pipelined Fault Tolerant Architecture for Real time DSP Applications | |

| Marcon et al. | An implementation of a distributed fault-tolerant mechanism for 2D mesh NoCs |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101029 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130121 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130205 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130311 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130416 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130424 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130514 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130531 |

|

| LAPS | Cancellation because of no payment of annual fees |