JP5046451B2 - Method for manufacturing semiconductor display device - Google Patents

Method for manufacturing semiconductor display device Download PDFInfo

- Publication number

- JP5046451B2 JP5046451B2 JP2001288483A JP2001288483A JP5046451B2 JP 5046451 B2 JP5046451 B2 JP 5046451B2 JP 2001288483 A JP2001288483 A JP 2001288483A JP 2001288483 A JP2001288483 A JP 2001288483A JP 5046451 B2 JP5046451 B2 JP 5046451B2

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- layer

- region

- film

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Electrodes Of Semiconductors (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は薄膜トランジスタ(以下、TFTと略記)で構成された回路を有する半導体表示装置及びその作製方法に関するものである。半導体表示装置としては、例えばTFTで構成された液晶ディスプレイ及びEL(エレクトロルミネッセンス)ディスプレイ等の電気光学装置がある。

【0002】

【従来の技術】

近年、TFTを利用したアクティブマトリクス型の液晶ディスプレイ技術が注目されている。アクティブマトリクス表示はパッシブマトリクス表示に比べ、応答速度と視野角及びコントラストの点で有利な為、現在のノートパソコンや液晶テレビ等の主流になっている。

【0003】

TFTは、非晶質シリコン又は多結晶シリコンをチャネル層とするものが一般的である。特に低温プロセス(一般に600℃以下)で作製される多結晶シリコンTFTは、低価格化及び大面積化と同時に、電子又は正孔が大きな電界移動度を有する為、液晶ディスプレイに用いた場合、画素用トランジスタだけでなく周辺回路であるドライバーの一体化が達成できる特徴があり、各液晶ディスプレイメーカーで開発が進められてきた。

【0004】

しかし、多結晶シリコンTFTの場合、連続駆動させると移動度やオン電流(TFTがオン状態の場合に流れる電流)の低下及びオフ電流(TFTがオフ状態の場合に流れる電流)の増加等の劣化現象が観測されることがあり、信頼性上大きな問題である。この現象はホットキャリア現象と呼ばれており、ドレイン近傍の高電界により発生したホットキャリアの仕業であることが知られている。

【0005】

ところで、このホットキャリア現象は、最初にMOSトランジスタに於いて発見された現象である。この為、ホットキャリア対策として、これまで様々な基礎検討が行われてきており、設計ルール1.5μm以下のMOSトランジスタでは、ドレイン近傍の高電界によるホットキャリア現象の対策として、LDD(Lightly-Doped-Drainの略)構造が採用されている。LDD構造では、ゲート側壁のサイドウォールを利用してドレイン端部に低濃度不純物領域(n−領域)を設け、ドレイン接合の不純物濃度に傾斜を持たせることによりドレイン近傍の電界集中を緩和している。

【0006】

当該(しかし、)LDD構造の場合、シングルドレイン構造に比べ、ドレイン耐圧はかなり向上するが、低濃度不純物領域(n−領域)の抵抗が大きい為、ドレイン電流が減少するという難点が有る。また、サイドウォールの真下に高電界領域が存在し、そこで衝突電離が最大になり、ホットエレクトロンがサイドウォールに注入される為、低濃度不純物領域(n−領域)が空乏化し、更に抵抗が増加するLDD特有の劣化モードが問題になっている。チャネル長の縮小に伴い、以上の問題が顕在化してきた為、0.5μm以下のMOSトランジスタでは、この問題を克服する構造として、ゲート電極の端部にオーバーラップして低濃度不純物領域(n−領域)を形成するGOLD(Gate-Overlapped LDDの略)構造が考案され採用されている。

【0007】

この様な背景の下、液晶ディスプレイの構成素子である多結晶シリコンTFTに於いても、MOSトランジスタと同様にドレイン近傍の高電界を緩和する目的で、LDD構造及びGOLD構造の採用が検討されている。LDD構造の場合は、ゲート電極の外側領域に対応する多結晶シリコン層に低濃度不純物領域(n−領域)と、その外側にソース・ドレイン領域となる高濃度不純物領域(n+領域)を形成しており、オフ電流の抑制効果は高いが、ドレイン近傍の電界緩和によるホットキャリア抑制効果は小さいという難点がある。一方のGOLD構造の場合は、LDD構造の低濃度不純物領域(n−領域)がゲート電極端部とオーバーラップする様に形成されており、LDD構造に比べホットキャリア抑制効果は大きいが、オフ電流が大きくなるという難点がある。

【0008】

また、nチャネル型多結晶シリコンTFTに於けるGOLD構造の検討例としては、例えば「Mutuko Hatano,Hajime Akimoto and Takesi Sakai,IEDM97 TECHNICAL DIGEST,p523-526,1997」があり、GOLD構造TFTの基本特性が開示されている。当該GOLD構造TFTの基本的構造は、ゲート電極とLDD用側壁が多結晶シリコンで形成され、LDD用側壁の真下の活性層(多結晶シリコンで形成)に電界緩和領域である低濃度不純物領域(n−領域)、及びその外側にはソース領域又はドレイン領域である高濃度不純物領域(n+領域)が形成されている。その基本特性としては、通常のLDD構造TFTと比較し、ドレイン電界の緩和と共に大きいドレイン電流が得られ、またドレインアバランシェホットキャリア(Drain-Avalanche-Hot-Carrier)の抑制効果が大きいという特性が得られている。

【0009】

【発明が解決しようとする課題】

多結晶シリコンTFTで構成される液晶ディスプレイ等の半導体表示装置は、画素領域と駆動回路である周辺回路で構成されており、回路毎に要求されるTFT特性は異なっている。例えば、画素領域にはオフ電流の抑制効果の大きいLDD構造多結晶シリコンTFTが適しており、駆動回路である周辺回路にはホットキャリア耐性の大きいGOLD構造多結晶シリコンTFTが適している。半導体表示装置の性能向上の点では、画素領域はLDD構造多結晶シリコンTFTで構成し、駆動回路である周辺回路はGOLD構造多結晶シリコンTFTで構成することが好適であるが、製造工程が複雑になる為、製造原価の増大と歩留の低下が大きな課題である。

【0010】

本発明は、上記課題を解決することのできる半導体表示装置及びその作製方法を提供することを目的とする。

【0011】

【課題を解決する為の手段】

GOLD構造多結晶シリコンTFTのホットキャリア耐性とLDD構造多結晶シリコンTFTのオフ電流抑制効果の両方を具備する多結晶シリコンTFTで、液晶ディスプレイ等の半導体表示装置を構成した場合、画素領域と駆動回路である周辺回路に於いて、GOLD構造とLDD構造を別々に形成する必要がなく、作製工程の簡略化が期待できる。

【0012】

GOLD構造多結晶シリコンTFTの構造的特徴は、ソース領域又はドレイン領域である高濃度不純物領域(n+領域又はp+領域)の内側に存在する低濃度不純物領域(n−領域又はp−領域)が、当該ゲート電極とオーバーラップしていることである。LDD構造多結晶シリコンTFTの構造的特徴は、前記低濃度不純物領域(n−領域又はp−領域)が当該ゲート電極とオーバーラップしてないことである。この為、ゲート電極とオーバーラップしている低濃度不純物領域(Lov領域と定義)とゲート電極とオーバーラップしてない低濃度不純物領域(Loff領域と定義)の両方を具備したTFT構造を検討した(当該構造のTFTは、GOLD構造の一種なので、以下GOLD構造と記載)。

【0013】

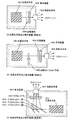

図1は、当該GOLD構造多結晶シリコンTFTの主な形成工程を示したものである。同図に於いて、ゲート電極は膜厚の薄く幅の大きい第1層ゲート電極104と膜厚の厚く幅の小さい第2層ゲート電極105の2層構造になっている。即ち、第1層ゲート電極104は第2層ゲート電極105よりチャネル方向の寸法が長い。ゲート電極の下側の基板構造は、ガラス基板101上に多結晶シリコン膜から成る半導体層102とゲート絶縁膜103が積層された基板構造となっており、その基板上に第1層ゲート電極104と第2層ゲート電極105から成る前記ゲート電極が形成されている。また、前記半導体層102には、ソース領域又はドレイン領域である高濃度不純物領域(n+領域又はp+領域)106が形成されている。尚、此処で使用される基板はガラス基板101に限定されず、耐熱性を有する透明絶縁性基板であれば構わない点を付記しておく(図1−A参照)。

【0014】

次に、所定膜厚のネガレジストを成膜し、第1層ゲート電極104をマスクに、基板の裏面から露光処理を行う。第1層ゲート電極104は導電性の金属材料でできている為、裏面からの露光光を遮光する性質があるが、ガラス基板101と多結晶シリコン膜から成る半導体層102とゲート絶縁膜103は透光性を有する。この為、現像工程に於いて、前記第1層ゲート電極104で遮光された領域のネガレジスト膜は現像液に溶解し、遮光されない領域のネガレジスト膜は現像液に不溶となり、ネガレジストパターン107が形成される。この際、遮光領域と非遮光領域の境界は第1層ゲート電極104の端部で一義的に決まる為、ネガレジストパターン107は第1層ゲート電極104をマスクに自己整合的に形成される。現像後のネガレジストパターン107はベーク処理が施され、最終的なネガレジストパターン107が形成される(図1−B参照)。

【0015】

次に、第1層ゲート電極104が露出した領域に対応する多結晶シリコン膜から成る半導体層102に、n型又はp型不純物の低濃度イオン注入を行う。このn型又はp型不純物の低濃度イオン注入により、Lov領域である低濃度不純物領域(n−領域又はp−領域)108が形成される。この際、イオン注入のマスクはネガレジストパターン107と膜厚の厚い第2層ゲート電極105で構成されている為、注入イオンに対する阻止能力は極めて高く、イオン注入時の加速電圧とイオン注入量を適宜選択することにより、第1層ゲート電極104の露出した領域に対応する半導体層102のみに適切な濃度の不純物をスルードープで独立にイオン注入することができる(図1−C参照)。

【0016】

此処で、イオン注入という用語の定義について明確にする。一般には質量分離した不純物イオンを注入する場合にイオン注入、質量未分離の不純物イオンを注入する場合にイオンドープの用語が適用されているが、本明細書では質量分離の有無に関係なく、多結晶シリコン膜に不純物を導入する工程を広い意味でイオン注入と定義している。

【0017】

次に、ネガレジストパターン107を除去した後、第1層ゲート電極104の外側に対応する半導体層102に、n型又はp型不純物の低濃度イオン注入を行う。このイオン注入により、Loff領域である低濃度不純物領域(n−−領域又はp−−領域)109が形成される。この際、既に形成されているソース・ドレイン領域である高濃度不純物領域(n+領域又はp+領域)106へも同時にイオン注入されるが、イオン注入量が少ない為に影響は殆どない。また、第1層ゲート電極104の下側のLov領域である低濃度不純物領域(n−領域又はp−領域)108へも前記第1層ゲート電極104を通して(スルードープ)同時にイオン注入されるが、殆どの注入イオンは第1層ゲート電極104で阻止される為、実質的な注入イオン量を問題ないレベルに抑えることができる。尚、此処では、ネガレジストパターン107を除去した後にイオン注入しているが、図1−Aの段階で実施しても基本的に同じである(図1−D参照)。

【0018】

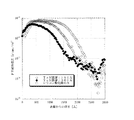

以上の工程により、Lov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTを形成することができる。此処で形成したGOLD構造多結晶シリコンTFTのTFT特性に関する検討結果を図2に示す。図2は移動度(μFE)劣化率とLov領域へのn型不純物(Pイオン)の注入量の関係及びオフ電流とLoff領域へのn型不純物(Pイオン)の注入量の関係を示したもので、Lov領域とLoff領域の寸法が共に0.7μm程度で同一であるという条件の下で評価したものである。此処ではホットキャリア耐性の評価法として、移動度(μFE)劣化率を指標に用いて評価した。図2中の黒点、白点が各々、Lov領域に関する結果、Loff領域に関する結果である。この図から判る様に、移動度(μFE)劣化率の低減の為にはLov領域に0.8×1014ions/cm2〜1.7×1014ions/cm2程度のPイオン注入量が必要であり、オフ電流の低減の為にはLoff領域に1×1013ions/cm2程度のPイオン注入量が必要であることが判る。本検討の結果、移動度(μFE)劣化率の低減とオフ電流の低減を両立できるGOLD構造多結晶シリコンTFTが形成可能であること、即ちホットキャリア耐性とオフ電流の抑制効果を共に有するGOLD構造多結晶シリコンTFTが形成可能であることを確認できた(図2参照)。

【0019】

尚、本実験に使用したGOLD構造多結晶シリコンTFTの構造について、以下に付記する。ソース領域又はドレイン領域等の形成される半導体層は膜厚50nmの多結晶シリコン膜、ゲート絶縁膜は膜厚110nmの酸化窒化シリコン膜、第1層ゲート電極は膜厚30nmのTaN膜、第2層ゲート電極は膜厚370nmのW膜で各々構成されている。また、イオン注入は、質量未分離の状態でイオン注入するイオンドープ装置を使用して検討した(図2参照)。

【0020】

次に、当該nチャネル型GOLD構造多結晶シリコンTFTの特性について、シミュレーションによる検討結果を図15に示す。図15−Aは、Lov領域へのPイオン注入量を振った場合のドレイン−チャネル接合部付近に於ける最大電子温度のシミュレーションデーターである。この結果から、Lov領域へのPイオン注入量は、1.5×1014ions/cm2の場合に電子温度が最小となる結果が得られた。このことは、Lov領域へのPイオン注入量が1.5×1014ions/cm2の場合に、ホットキャリア発生率が最小となることを示唆しており、上記の実験結果ともほぼ対応が取れている。また、図15−Bは、Lov領域へのPイオン注入量を1.5×1014ions/cm2に固定した状態で、Loff領域へのPイオン注入量を振った場合のドレイン−チャネル接合部付近に於ける最大電子温度とオフ電流(Ioff)のシミュレーションデーターである。この結果から、Loff領域へのPイオン注入量が1.5×1013ions/cm2から0.75×1013ions/cm2にかけて、ドレイン−チャネル接合部付近に於ける最大電子温度とオフ電流(Ioff)が共に急激に小さくなる結果が得られた。上記の実験結果に於いては、Loff領域へのPイオン注入量が少なくなるのに比例して、オフ電流(Ioff)がリニアに小さくなっているが、バラツキ等を考慮すると、大きな矛盾はないものと考える。一方、オン電流(Ion)については、図15−Cに示す様に、Loff領域へのPイオン注入量が少なくなるのに比例して、オン電流(Ion)が小さくなっているが、Pイオン注入量0.75×1013ions/cm2の場合でも、オン電流(Ion)が50μA程度あり、オン電流(Ion)として若干小さいけれども、周辺回路として適用可能と考える(図15参照)。

【0021】

従って、図15に示すシミュレーション結果からも、当該nチャネル型GOLD構造多結晶シリコンTFTの有効性が確認された。此処では、本シミュレーションの前提条件であるデバイス構造等について、以下に補足説明を記載する。当該GOLD構造多結晶シリコンTFTの構造は、W/L=8/6μm、Lov領域=Loff領域=0.75μm、ソース・ドレイン領域等の形成層であるシリコン膜として膜厚50nmの多結晶シリコン膜、ゲート絶縁膜として膜厚110nmのシリコン酸化窒化膜(誘電率=4.1)、第1層ゲート電極として膜厚30nmのTaN膜、第2層ゲート電極として膜厚370nmのW膜を想定し、更にチャネルドープ及びソース・ドレイン領域への不純物イオン注入(イオンドープ法)としてSIMS分析データーの不純物プロファイルに合わせ込んでシミュレーションを実効した。尚、本シミュレーションに於いては、キャリア活性化率が不明である為、人為的に活性化率を20%に設定してシミュレーションを行っている。また、シミュレーションではホットキャリア信頼性について直接的な評価は不可能である為、ドレイン−チャネル接合部の最大電子温度(電子の運動エネルギーに相当)を計算し、間接的にホットキャリアの評価を行っている。

【0022】

此処で重要なことは、ホットキャリア耐性とオフ電流の抑制効果を共に有するGOLD構造多結晶シリコンTFTを形成する為には、Lov領域とLoff領域の不純物濃度の適正値が異なっており、各々独立に制御する必要があることである。この為、当該GOLD構造多結晶シリコンTFTの形成工程に於いて、Lov領域へのイオン注入は、Loff領域へのイオン注入とは独立に、自己整合的に形成したネガレジストパターンをマスクにイオン注入していることである。

【0023】

本発明では、既に記載した様に、ネガレジストと裏面露光法の組み合わせにより、第1層ゲート電極104をマスクに自己整合的にネガレジストパターン107の形成を行っている。此処で、ポジレジストと露光装置を適用した通常のフォトリソグラフィ工程によりレジストパターンを形成することも可能であるが、この場合は自己整合技術が適用されない為、露光装置のアライメント精度に依存した重ね合わせ誤差が発生し、第1層ゲート電極104と前記レジストパターンの間に微小な間隙が生じることになる。この結果、次工程の低濃度イオン注入の際、第1層ゲート電極104と前記レジストパターンの間の微小間隙に対応した半導体層102の領域に同時にイオン注入される可能性があり、自己整合技術を利用しない通常のフォトリソグラフィ工程の適用は問題である。この問題を回避する為、本発明では、レジストパターンの形成に、ネガレジストと裏面露光法の組み合わせを適用している。

【0024】

本発明の特徴について、以下に簡潔に記載する。本発明は、液晶ディスプレイ等の半導体表示装置の作製に於いて、画素領域と駆動回路である周辺回路をLov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTで構成することにより、作製工程の簡略化と半導体表示装置の性能向上を共に実現することを特徴としている。

【0025】

また、本発明ではLov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTの形成に於いて、裏面露光法で自己整合的に形成されたネガレジストパターンをマスクにLov領域へのイオン注入を独立に行うことにより、Lov領域とLoff領域の不純物濃度の独立制御を可能とするものである。これにより、ホットキャリア耐性とオフ電流の抑制効果を共に有するGOLD構造多結晶シリコンTFTの形成を可能とするものである。

【0026】

【発明の実施の形態】

〔実施形態1〕

Lov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTの形成法について、図3に基づき記載する。

【0027】

本実施形態で使用する基板構造は、ガラス基板201上に多結晶シリコン膜から成る半導体層202とゲート絶縁膜203と第1層ゲート電極膜204と第2層ゲート電極膜205が各々所定膜厚に積層された基板を使用する。前記構造の基板上に、ゲート電極形成用のレジストパターン206を形成する(図3−A参照)。

【0028】

次に、前記レジストパターン206をマスクにドライエッチング処理の第1ステップを行う。この所定時間のドライエッチング処理により、第2層ゲート電極膜205のみが等方性エッチングされ、テーパー形状を有する第2層ゲート電極208が形成される。この際、ドライエッチングのマスクとなったレジストパターン206は、レジスト膜と被エッチング膜である第2層ゲート電極膜205との選択比の問題でレジスト膜が膜減りする為、ドライエッチング後レジストパターン207の形状に変形している(図3−B参照)。

【0029】

次に、連続してドライエッチング処理の第2ステップを行う。この所定時間のドライエッチング処理により、上記の第1ステップ工程で形成されたテーパー形状を有する第2層ゲート電極208をマスクに第1層ゲート電極膜204が異方性エッチングされ、第1層ゲート電極211が形成される。オーバーエッチングの過程で、下地のゲート絶縁膜203はプラズマに晒され若干エッチングされる為、ゲート絶縁膜212の形状に変形している(図3−C参照)。

【0030】

次に、第1層ゲート電極211と第2層ゲート電極210から成るゲート電極をマスクに、第1のイオン注入処理であるn型不純物の高濃度イオン注入を行う。この際、n型不純物としてP(リン)を用い、加速電圧が60〜100kVでドーズ量が5×1014〜5×1015ions/cm2のイオン注入条件でイオン注入する。この第1のイオン注入処理により、当該ゲート電極の外側に対応する多結晶シリコン膜から成る半導体層202に、ソース領域又はドレイン領域となるn型不純物の高濃度不純物領域(n+領域)213が形成される(図3−C参照)。

【0031】

次に、ドライエッチング処理の第3ステップを行う。この所定時間のドライエッチング処理により、第1層ゲート電極211と第2層ゲート電極210は共に等方性エッチングされ、第1層ゲート電極216とテーパー形状を有する第2層ゲート電極215が形成される。エッチングのマスクであるレジストパターンは、更に膜減りが進み、レジストパターン214の形状に変形している。また、下地のゲート絶縁膜についてもプラズマに晒された領域で更に膜減りが進み、ゲート絶縁膜217の形状に変形している(図3−D参照)。

【0032】

次に、連続してドライエッチング処理の第4ステップを行う。この所定時間のドライエッチング処理により、テーパー形状を有する第2層ゲート電極215はレジストパターン214をマスクに異方性エッチングされ、矩形形状の第2層ゲート電極218が形成される。この際、第2層ゲート電極218のエッチングの進行に伴い、第1層ゲート電極は端部からプラズマに晒される為、第1層ゲート電極219は端部に近づく程に残膜厚の薄くなるテーパ形状に形成される。また、下地のゲート絶縁膜217についてもプラズマに晒された領域で更に膜減りが進む為、ゲート絶縁膜217はゲート絶縁膜220の形状に変形している。この後、エッチングのマスクであるレジストパターンは除去される(図3−E参照)。

【0033】

次に、所定膜厚のネガレジスト膜を塗布ベーク処理することによりネガレジスト膜を成膜し、第1層ゲート電極219をマスクに、基板の裏面から露光処理を行う。前記第1層ゲート電極219は導電性の金属材料からできている為、裏面からの露光光を遮光する性質があり、第1層ゲート電極219以外の領域は、透光性を有するガラス基板201と半導体層202とゲート絶縁膜220の積層構造である為、裏面からの露光光を遮光できない。この為、次の現像工程に於いて、前記第1層ゲート電極219で遮光された領域のネガレジスト膜は現像液に溶解し、遮光されない領域のネガレジスト膜は現像液に不溶となり、ネガレジストパターン221が形成される。この際、遮光領域と非遮光領域の境界は第1層ゲート電極219の端部で一義的に決まる為、ネガレジストパターン221は第1層ゲート電極219をマスクに自己整合的に形成される。この後にベーク処理が施され、最終的なネガレジストパターン221が形成される(図3−F参照)。

【0034】

次に、第1層ゲート電極219が第2層ゲート電極218から露出した領域(露出領域)に対応する多結晶シリコン膜から成る半導体層202に、第2のイオン注入処理であるn型不純物の低濃度イオン注入を行う。此処では、イオン注入のマスクにネガレジストパターン221と膜厚の厚い第2層ゲート電極218を用いている為、注入イオンに対する阻止能力は極めて高く、イオン注入時の加速電圧とイオン注入量を適宜選択することにより、第1層ゲート電極219の露出した領域に対応する半導体層202のみに適切な濃度の不純物をスルードープで独立にイオン注入することができる。具体的なイオン注入条件としては、n型不純物としてP(リン)を用い、加速電圧が60〜100kVでドーズ量が0.8×1014ions/cm2〜1.7×1014ions/cm2の条件でイオン注入する。この結果、半導体層202の当該領域に於いては、Lov領域である低濃度不純物領域(n−領域)222が形成される。尚、第1層ゲート電極219は、ゲート電極の端部に近づく程に膜厚が薄くなるテーパー形状となっている為、スルードープでイオン注入される低濃度不純物領域(n−領域)222の不純物濃度には濃度勾配が存在し、第1層ゲート電極219の端部即ちソース領域又はドレイン領域である高濃度不純物領域(n+領域)213に近づく程、徐々に不純物濃度が高くなる傾向を有している(図3−G参照)。

【0035】

次に、ネガレジストパターン221を除去した後、第1層ゲート電極219の外側に対応する半導体層202に、n型不純物の低濃度イオン注入を行う。このイオン注入により、Loff領域である低濃度不純物領域(n−−領域)223が形成される。イオン注入条件は、n型不純物としてP(リン)を用い、加速電圧が60〜100kVでドーズ量が1×1013ions/cm2の条件でイオン注入する。この際、既に形成されているソース領域又はドレイン領域である高濃度不純物領域(n+領域)213へも同時にイオン注入されるが、イオン注入量が少ない為に影響は殆どない。また、第1層ゲート電極219の下側のLov領域である低濃度不純物領域(n−領域)222へも前記第1層ゲート電極219を通して(スルードープ)同時にイオン注入されるが、殆どの注入イオンは第1層ゲート電極219で阻止される為、実質的な注入イオン量を問題ないレベルに抑えることができる。尚、此処では、ネガレジストパターン221を除去した後にイオン注入しているが、図3−Eの段階でイオン注入を実施しても基本的に同じである(図3−H参照)。

【0036】

以上の工程により、Lov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTを形成することができ、当該GOLD構造多結晶シリコンTFTにはホットキャリア耐性とオフ電流抑制効果の両方の利点が備わっている特徴がある。

【0037】

〔実施形態2〕

Lov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTを形成する別の方法について、図4に基づき記載する。本実施形態は実施形態1と殆ど同じであるが、ゲート電極の形成法に若干の差異がある。従って、この点を重点的に記載する。

【0038】

本実施形態で使用する基板構造は、ガラス基板301上に多結晶シリコン膜から成る半導体層302とゲート絶縁膜303と第1層ゲート電極膜304と第2層ゲート電極膜305が各々所定膜厚に積層された基板を使用する。前記構造の基板上に、ゲート電極形成用のレジストパターン306を形成する(図4−A参照)。

【0039】

前記レジストパターン306をマスクにドライエッチング処理の第1ステップと第2ステップを連続処理することにより、第1層ゲート電極311とテーパー形状を有する第2層ゲート電極310が形成される。この際、ドライエッチングのマスクであるレジストパターン306は、ドライエッチング後レジストパターン309の形状に変形し、下地のゲート絶縁膜303は、膜減りによりゲート絶縁膜312の形状に変形している(図4−Bと図4−C参照)。

【0040】

次に、第1層ゲート電極311と第2層ゲート電極310から成るゲート電極をマスクに、第1のイオン注入処理であるn型不純物の高濃度イオン注入を行う。この第1のイオン注入処理により、ソース・ドレイン領域となるn型不純物の高濃度不純物領域(n+領域)313が形成される(図4−C参照)。

【0041】

次に、ドライエッチング処理の第3ステップを行う。この所定時間のドライエッチング処理により、テーパー形状を有する第2層ゲート電極310はレジストパターン309をマスクに異方性エッチングされ、矩形形状の第2層ゲート電極315が形成される。この際、第2層ゲート電極310のエッチングの進行に伴い、第1層ゲート電極は端部からプラズマに晒される為、第1層ゲート電極316は、端部に近づく程に残膜厚の薄くなるテーパ形状に形成される。また、下地のゲート絶縁膜312についてもプラズマに晒された領域で更に膜減りが進む為、ゲート絶縁膜312はゲート絶縁膜317の形状に変形している(図4−D参照)。

【0042】

次に、連続してドライエッチング処理の第4ステップを行う。この所定時間のドライエッチング処理により、第2層ゲート電極315から露出した第1層ゲート電極316は、そのテーパー形状領域の残膜厚が膜減りにより更に薄くなり、テーパー形状領域の端部が後退した第1層ゲート電極319が形成される。この際、ドライエッチングの処理条件を適宜変更することにより、第1層ゲート電極319は、前記テーパー形状領域の範囲内で、その寸法を自由に調整することが可能である。また、第1層ゲート電極319から露出した下地のゲート絶縁膜は、ドライエッチングによりさらに膜減りしており、ゲート絶縁膜320の形状に変形している。この後にドライエッチングのマスクであるレジストパターンは、除去される(図4−E参照)。

【0043】

次に、第1層ゲート電極319をマスクに裏面露光によるネガレジストパターンを自己整合的に形成する(図4−F参照)。

【0044】

次に、第1層ゲート電極319が第2層ゲート電極318から露出した領域に対応する多結晶シリコン膜から成る半導体層302に第2のイオン注入処理であるn型不純物の低濃度イオン注入(加速電圧:60〜100kV/ドーズ量:1×1014ions/cm2)を行う。このイオン注入処理により、Lov領域である低濃度不純物領域(n−領域)322が形成される(図4−G参照)。

【0045】

ネガレジストパターン321を除去した後、第1層ゲート電極319の外側に対応する多結晶シリコン膜から成る半導体層302に第3のイオン注入処理であるn型不純物の低濃度イオン注入(加速電圧:60〜100kV/ドーズ量:1×1013ions/cm2)を行う。このイオン注入処理により、Loff領域である低濃度不純物領域(n−−領域)323が形成される(図4−H参照)。

【0046】

【実施例】

〔実施例1〕

Lov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTで構成されるアクティブマトリクス型液晶ディスプレイの作製法について、図5〜11に基づき具体的に記載する。

【0047】

最初に、ガラス基板401上にプラズマCVD法により、各々組成比の異なる第1層目の酸化窒化シリコン膜402aを50nmと第2層目の酸化窒化シリコン膜402bを100nmの膜厚で堆積し、下地膜402を成膜する。尚、此処で用いるガラス基板401としては、石英ガラス又はバリウムホウケイ酸ガラス又はアルミノホウケイ酸ガラス等が有る。次に、前記下地膜402(402aと402b)上にプラズマCVD法により、非晶質シリコン膜55nmを堆積した後、ニッケル含有溶液を非晶質シリコン膜上に保持させた。この非晶質シリコン膜を脱水素化処理(500℃−1時間)した後、熱結晶化(550℃−4時間)を行い、更にレーザーアニール処理により多結晶シリコン膜とした。尚、ニッケル含有水溶液等の触媒元素を利用して、熱結晶化された多結晶シリコン膜は、通常の多結晶シリコン膜に比較し、結晶粒が概略同一方向に配向しており、高い電界効果移動度を有する等の特徴がある為、本明細書では特に結晶質シリコン膜とも称する(図5−A参照)。

【0048】

次にフォトリソグラフィ工程及びエッチング工程により、この多結晶シリコン膜をパターニングし、半導体層403〜407を形成した。この際、半導体層403〜407の形成後に、TFTのVthを制御する為の不純物元素(ボロン又はリン)のドーピングを実施しても構わない。次に半導体層403〜407を覆う様に、プラズマCVD法により110nm厚の酸化窒化シリコン膜から成るゲート絶縁膜408を形成し、更にゲート絶縁膜408上に30nm厚のTaN膜から成る第1層ゲート電極膜409と370nm厚のW膜から成る第2層ゲート電極膜410をスパッタ法により堆積した。此処で、第1層ゲート電極膜409と第2層ゲート電極膜410の材料としては、後のプロセス温度に耐え得る高融点金属及び高融点金属を含む化合物、例えば金属窒化物又は金属シリサイド等が挙げられる。本実施例では、第1層ゲート電極膜409にTaN膜、第2層ゲート電極膜410にW膜を採用した(図5−A参照)。

【0049】

上記構造の基板上に、フォトリソグラフィ処理を行うことにより、ゲート電極形成用のレジストパターン411a〜414aと電極形成用のレジストパターン415a〜416aを形成する(図5−B参照)。

【0050】

次に、前記レジストパターン411a〜416aをマスクにドライエッチング処理の第1ステップを行う。この所定時間のドライエッチング処理により、W膜から成る第2層ゲート電極膜410のみが等方性エッチングされ、テーパー形状を有する第2層ゲート電極417〜420と第2層電極421〜422が形成される。この際、ドライエッチングのマスクとなったレジストパターン411a〜416aは、レジスト膜と被エッチング膜である第2層ゲート電極膜(W膜)410との選択比の問題でレジスト膜が膜減りする為、ドライエッチング後レジストパターン411b〜416bの形状に変形している(図6−A参照)。

【0051】

次に、連続してドライエッチング処理の第2ステップを行う。この所定時間のドライエッチング処理により、上記の第1ステップ工程で形成されたテーパー形状を有する第2層ゲート電極417〜420をマスクに第1層ゲート電極膜409が異方性エッチングされ、第1層ゲート電極429〜432が形成される。また、テーパー形状を有する第2層電極421〜422をマスクに第1層ゲート電極膜409が異方性エッチングされ、第1層電極433〜434が形成される。この際、下地の酸化窒化シリコン膜から成るゲート絶縁膜408は、エッチングにより20nm程度膜減りし、残膜厚が90nm程度となっている。第2層電極も膜減りして、423〜426、427〜428になる。

(図6−B参照)。

【0052】

次に、第1層ゲート電極429〜432と第2層ゲート電極423〜426から成るゲート電極及び第1層電極433と第2層電極427から成る電極をマスクに、第1のイオン注入処理であるn型不純物の高濃度イオン注入を行う。この際、n型不純物としてP(リン)を用い、加速電圧が60〜100kVでドーズ量が5×1014〜5×1015ions/cm2のイオン注入条件でイオン注入する。この第1のイオン注入処理により、当該ゲート電極の外側に対応する多結晶シリコン膜から成る半導体層403〜406に、ソース・ドレイン領域となるn型不純物の高濃度不純物領域(n+領域)435〜438が形成される。一方、保持容量505の形成領域である半導体層407に於いては、容量形成用の当該電極をマスクにイオン注入され、電極の外側に対応する領域(露出領域)に高濃度不純物領域(n+領域)439が形成される。尚、前記高濃度不純物領域(n+領域)435〜439の不純物濃度は、最も高濃度領域で一般的に1×1020〜1×1022atoms/cm3程度である(図6−B参照)。

【0053】

此処で、前記高濃度不純物領域(n+領域)435〜439のP元素濃度について、図16のSIMS分析データーに基づき詳細に検討した。尚、図16は、Pイオン原料として5%濃度のホスフィン(PH3)/水素(H2)を使用し、▲1▼TaN膜(15nm)/シリコン酸化膜,▲2▼TaN膜(30nm)/シリコン酸化膜,▲3▼シリコン酸化膜の3種類の基板に対し、イオンドープ装置により加速電圧−電流密度が90kV−0.5μA/cm2の条件でドーズ量1.5×1014ions/cm2をイオン注入した場合のSIMS分析データーである。また、同図に於いて、深さ方向の不純物プロファイルは、TaN膜を除くシリコン酸化膜中の不純物プロファイルである。前記高濃度不純物領域(n+領域)435〜439の膜構造は、表面から酸化窒化シリコン膜(エッチング膜減りにより残膜厚90nm程度)と多結晶シリコン膜(50nm厚)で、酸化窒化シリコン膜と多結晶シリコン膜のイオン阻止能は、シリコン酸化膜のイオン阻止能と殆ど同じである。この為、図16の▲3▼シリコン酸化膜基板の不純物プロファイルを参考に、高濃度不純物領域(n+領域)435〜439の不純物濃度、即ち多結晶シリコン膜(50nm厚)中の不純物濃度を検討した。ドーズ量1.5×1014ions/cm2の場合、多結晶シリコン膜中の不純物濃度は5×1018〜8×1018atoms/cm3と読み取れる為、実際のドーズ量5×1014〜5×1015ions/cm2の場合は、比例計算により多結晶シリコン膜中の不純物濃度を1.7×1019〜2.7×1020atoms/cm3程度と考えられる。また、実際のイオン注入に於いては、加速電圧が60〜100kVの範囲を有している為、設定加速電圧の影響により、不純物濃度の範囲は更に広がることが予想される。この点を考慮し、高濃度不純物領域(n+領域)435〜439の不純物濃度の範囲は、最大範囲として最小値に0.2倍と最大値に20倍程度の補正係数を掛けた範囲が想定される。従って、高濃度不純物領域(n+領域)435〜439の不純物濃度は、3×1018〜5×1021atoms/cm3程度、より好ましくは1.7×1019〜2.7×1020atoms/cm3程度と推定される(図16参照)。

【0054】

次に、ドライエッチング処理の第3ステップを行う。この所定時間のドライエッチング処理により、テーパー形状を有する第2層ゲート電極423〜426と第2層電極427〜428はレジストパターン411c〜416cをマスクに異方性エッチングされ、矩形形状の第2層ゲート電極440〜443と第2層電極444〜445が形成される。この際、第2層ゲート電極423〜426と第2層電極427〜428のエッチングの進行に伴い、その下側に存在する第1層ゲート電極と第1層電極は端部からプラズマに晒される為、第1層ゲート電極446〜449と第1層電極450〜451は、端部に近づく程に残膜厚の薄くなるテーパ形状に形成される。また、下地のゲート絶縁膜は、プラズマに晒された領域で膜減りが進み、ゲート絶縁膜452の形状に変形している(図7−A参照)。

【0055】

次に、連続してドライエッチング処理の第4ステップを行う。この所定時間のドライエッチング処理により、第2層ゲート電極440〜443から露出した第1層ゲート電極446〜449は、そのテーパー形状領域の残膜厚が膜減りにより更に薄くなり、テーパー形状領域の端部が後退した第1層ゲート電極453〜456が形成される。この際、ドライエッチングの処理条件を適宜変更することにより、第1層ゲート電極453〜456は、前記テーパー形状領域の範囲内で、その寸法を自由に調整することが可能である。同様に、露出した第1層電極450〜451は、そのテーパー形状領域の残膜厚が膜減りにより更に薄くなり、テーパー形状領域の端部が後退した第1層電極457〜458が形成される。また、下地のゲート絶縁膜は、ドライエッチングにより更に膜減りしており、ゲート絶縁膜459の形状に変形している。この段階で、下地の酸化窒化シリコン膜から成るゲート絶縁膜459は更に膜減りが進行し、膜厚の厚い領域で残膜厚が50nm程度、膜厚の薄い領域で残膜厚が30nm程度となっている。この後に、ドライエッチングのマスクであるレジストパターンを除去する(図7−B参照)。

【0056】

次に、所定膜厚のネガレジスト膜を塗布ベーク処理することによりネガレジスト膜を成膜し、第1層ゲート電極453〜456と第1層電極457〜458をマスクに、基板の裏面から露光処理を行う。前記第1層ゲート電極453〜456と第1層電極457〜458は膜厚30nmのTaN膜でできており、波長350〜450nm程度の光に対して14%程度の透過率である(図11)為、裏面からの露光光(代表的波長:g線436nm,h線405nm,i線365nm)の殆どを遮光する性質がある。一方、第1層ゲート電極453〜456と第1層電極457〜458以外の領域は、透光性を有するガラス基板401と半導体層403〜407とゲート絶縁膜459の積層構造である為、裏面からの露光光を遮光できない。この為、次の現像工程に於いて、前記第1層ゲート電極453〜456と第1層電極457〜458で遮光された領域のネガレジスト膜は現像液に溶解し、遮光されない領域のネガレジスト膜は現像液に不溶となり、ネガレジストパターン460〜468が形成される。遮光領域と非遮光領域の境界は第1層ゲート電極453〜456と第1層電極457〜458の端部で一義的に決まる為、ネガレジストパターン460〜468は、第1層ゲート電極453〜456と第1層電極457〜458をマスクに自己整合的に形成される。この後にベーク処理が施され、最終的なネガレジストパターン460〜468が形成される(図8−A参照)。

【0057】

次に、第1層ゲート電極453〜456と第1層電極457が、第2層ゲート電極440〜443及び第2層電極444から露出した領域に対応する半導体層403〜407に、第2のイオン注入処理であるn型不純物の低濃度イオン注入を行う。此処では、イオン注入のマスクにネガレジストパターン460〜468と膜厚の厚い第2層ゲート電極440〜443及び第2層電極444を用いている為、注入イオンに対する阻止能力は極めて高い。この為、イオン注入時の加速電圧とイオン注入量を適宜選択することにより、第1層ゲート電極453〜456と第1層電極457の露出した領域に対応する半導体層403〜407の領域のみにスルードープで適切な濃度の不純物を独立にイオン注入することができる。具体的なイオン注入条件としては、n型不純物としてP(リン)を用い、加速電圧が60〜100kVでドーズ量が1×1014ions/cm2の条件でイオン注入する。この結果、ゲート電極形成用の半導体層403〜406にLov領域である低濃度不純物領域(n−領域)469〜472が形成され、容量形成用の半導体層407に低濃度不純物領域(n−領域)473(ゲート電極形成領域でない為、Lov領域ではない)が形成される。尚、第1層ゲート電極453〜456と第1層電極457は、ゲート電極の端部に近づく程に膜厚が薄くなるテーパー形状となっている為、スルードープでイオン注入される低濃度不純物領域(n−領域)469〜473の不純物濃度には濃度勾配が存在し、高濃度不純物領域(n+領域)435〜439に近づく程、徐々に不純物濃度が高くなる傾向を有している(図8−A参照)。

【0058】

此処で、前記低濃度不純物領域(n−領域)469〜472のP元素濃度について、図16のSIMS分析データーに基づき詳細に検討した。尚、図16は、Pイオン原料として5%濃度のホスフィン(PH3)/水素(H2)を使用し、▲1▼TaN膜(15nm)/シリコン酸化膜,▲2▼TaN膜(30nm)/シリコン酸化膜,▲3▼シリコン酸化膜の3種類の基板に対し、イオンドープ装置により加速電圧−電流密度が90kV−0.5μA/cm2の条件でドーズ量1.5×1014ions/cm2をイオン注入した場合のSIMS分析データーである。前記低濃度不純物領域(n−領域)469〜472の膜構造は、表面から第1層ゲート電極453〜456(TaN膜厚:エッチング膜減りの為、0〜30nm程度)と酸化窒化シリコン膜(110nm厚)と多結晶シリコン膜(50nm厚)で、酸化窒化シリコン膜と多結晶シリコン膜のイオン阻止能は、シリコン酸化膜のイオン阻止能と殆ど同じである。この為、図16の▲2▼TaN膜(30nm)/シリコン酸化膜と▲3▼シリコン酸化膜の不純物プロファイルを参考に、低濃度不純物領域(n−領域)469〜472の不純物濃度、即ち多結晶シリコン膜(50nm厚)中の不純物濃度を検討した。ドーズ量1.5×1014ions/cm2の場合、多結晶シリコン膜中の不純物濃度は1.5×1017〜8×1018atoms/cm3程度と読み取れる為、実際のドーズ量1×1014ions/cm2の場合は、比例計算により多結晶シリコン膜中の不純物濃度を1×1017〜5.3×1018atoms/cm3程度と考えられる。また、実際のイオン注入に於いては、加速電圧が60〜100kVの範囲を有している為、設定加速電圧の影響により、不純物濃度の範囲は更に広がることが予想される。この点を考慮し、低濃度不純物領域(n−領域)469〜472の不純物濃度の範囲は、最大範囲として最小値に0.2倍と最大値に5倍程度の補正係数を掛けた範囲が想定される。従って、低濃度不純物領域(n−領域)469〜472の不純物濃度は、2×1016〜2.7×1019atoms/cm3、より好ましくは1×1017〜5.3×1018atoms/cm3程度と推定される(図16参照)。

【0059】

次に、ネガレジストパターン460〜468を除去した後、第1層ゲート電極453〜456と第1層電極457の外側に対応する半導体層403〜407に、第3のイオン注入処理であるn型不純物の低濃度イオン注入を行う。このイオン注入により、ゲート電極形成用の半導体層403〜406にLoff領域である低濃度不純物領域(n−−領域)474〜477が形成され、容量形成用の半導体層407に低濃度不純物領域(n−−領域)478が形成される。この際、n型不純物としてP(リン)を用い、加速電圧が60〜100kVでドーズ量が1×1013ions/cm2の条件でイオン注入する。また、既に形成した前記高濃度不純物領域(n+領域)435〜439へも同時にイオン注入されるが、イオン注入量が少ない為に殆ど影響はない。また、既に形成した前記低濃度不純物領域(n−領域)469〜473へも前記第1層ゲート電極453〜456と第1層電極457を通して(スルードープ)同時にイオン注入されるが、殆どの注入イオンは第1層ゲート電極453〜456と第1層電極457で阻止される為、実質的な注入イオン量を問題ないレベルに抑えることができる。尚、此処では、ネガレジストパターン460〜468を除去した後にイオン注入しているが、ドライエッチングの第4ステップが終了した図7−Bの段階でイオン注入を実施しても基本的に同じである(図8−B参照)。

【0060】

此処で、前記低濃度不純物領域(n−−領域)474〜477のP元素濃度について、図16のSIMS分析データーに基づき詳細に検討した。尚、図16は、Pイオン原料として5%濃度のホスフィン(PH3)/水素(H2)を使用し、▲1▼TaN膜(15nm)/シリコン酸化膜,▲2▼TaN膜(30nm)/シリコン酸化膜,▲3▼シリコン酸化膜の3種類の基板に対し、イオンドープ装置により加速電圧−電流密度が90kV−0.5μA/cm2の条件でドーズ量1.5×1014ions/cm2をイオン注入した場合のSIMS分析データーである。前記低濃度不純物領域(n−−領域)474〜477の膜構造は、表面から酸化窒化シリコン膜(エッチング膜減りの為、残膜厚50nm程度と推定)と多結晶シリコン膜(50nm厚)で、酸化窒化シリコン膜と多結晶シリコン膜のイオン阻止能は、シリコン酸化膜のイオン阻止能と殆ど同じである為、図16の▲3▼シリコン酸化膜基板の不純物プロファイルを参考に、低濃度不純物領域(n−−領域)474〜477の不純物濃度、即ち多結晶シリコン膜(50nm厚)中の不純物濃度を検討した。ドーズ量1.5×1014ions/cm2の場合、多結晶シリコン膜中の不純物濃度は7×1018〜8×1018atoms/cm3と読み取れる為、実際のドーズ量1×1013ions/cm2の場合は、比例計算により多結晶シリコン膜中の不純物濃度を4.7×1017〜5.3×1017atoms/cm3程度と考えられる。また、実際のイオン注入に於いては、加速電圧が60〜100kVの範囲を有している為、設定加速電圧の影響により、不純物濃度の範囲は更に広がることが予想される。この点を考慮し、低濃度不純物領域(n−−領域)474〜477の不純物濃度の範囲は、最大範囲として最小値に0.01倍と最大値に5倍程度の補正係数を掛けた範囲が想定される。従って、低濃度不純物領域(n−−領域)474〜477の不純物濃度は、4.7×1015〜2.7×1018atoms/cm3、より好ましくは4.7×1017〜5.3×1017atoms/cm3程度と推定される(図16参照)。

【0061】

次に、駆動回路506に於けるpチャネル型TFT502の領域と画素領域507に於ける保持容量505の領域をレジスト開口させる為、フォトリソグラフィ処理により、レジストパターン479〜481が形成される(図9−A参照)。

【0062】

前記レジストパターン479〜481をマスクに、第4のイオン注入処理であるp型不純物の高濃度イオン注入を行う。pチャネル型TFT502の形成領域である半導体層404には、第1層ゲート電極454と第2層ゲート電極441をマスクに前記一導電型とは逆の導電型を付与するp型不純物であるB(ボロン)等がイオン注入される。この結果、第1層ゲート電極454の外側に対応する領域にソース・ドレイン領域となる高濃度不純物領域(p+領域)482が形成され、第1層ゲート電極454のみが露出した領域にスルードープにより低濃度不純物領域(p−領域)483が同時形成される。半導体層404には、n型不純物であるP(リン)が既にイオン注入されているが、B(ボロン)の濃度が2×1020〜2×1021atoms/cm3となる様に高濃度にイオン注入される為、p型不純物の高濃度不純物領域(p+領域)482と低濃度不純物領域(p−領域)483が形成され、pチャネル型TFT502として機能することができる。また、保持容量505の形成領域である半導体層407に於いても、第1層ゲート電極457の外側に対応する領域にp型不純物の高濃度不純物領域(p+領域)484が形成され、第1層ゲート電極457のみが露出した領域にスルードープにより低濃度不純物領域(p−領域)485が同時形成される。尚、保持容量505の領域に於いては、pチャネル型TFT502の領域と同様の構造が形成されているが、容量形成領域である為、TFT構造ではない(図9−A参照)。

【0063】

次に前記レジストパターン479〜481を除去した後、150nm厚の酸化窒化シリコン膜から成る第1の層間絶縁膜486がプラズマCVD法により堆積される。この後、半導体層403〜407に注入された不純物元素(n型不純物とp型不純物)の熱活性化の為、550℃−4時間の熱アニール処理が行われる。本実施例では、オフ電流値の低下と電界効果移動度の向上の為、不純物元素の熱活性化処理と同時に、半導体層403〜407の結晶化用触媒であるNi(ニッケル)がn型不純物である高濃度のP(リン)によりゲッタリングされている。このゲッタリング処理により、半導体層403〜407内部のニッケル(Ni)濃度の低減を実現している。この方法で製造された多結晶シリコンTFTは高い電界効果移動度を有しており、オフ電流値の低下等の良好な電気特性を示すことができる。尚、前記熱活性化処理を第1の層間絶縁膜486の堆積前に実施しても構わないが、ゲート電極等の配線材料の耐熱性が弱い場合、第1の層間絶縁膜486の堆積後に実施する方が好ましい。この後、半導体層403〜407のダングリングボンドを終端させる為、410℃−1時間の水素化処理が水素3%含有する窒素雰囲気中で行われる(図9−B参照)。

【0064】

次に前記第1の層間絶縁膜486の上に、1.6μm厚のアクリル樹脂膜から成る第2の層間絶縁膜487が成膜される。この後、フォトリソグラフィ処理とドライエッチング処理により、コンタクトホールが第2の層間絶縁膜487に形成される。この際、このコンタクトホールは、ソース配線として機能する電極(第1層電極458と第2層電極445)と高濃度不純物領域435,437,438,482,484を接続する様に形成される(図10−A参照)。

【0065】

次に、駆動回路506の高濃度不純物領域435,437,482と電気的に接続する為、金属配線488〜493が形成される。同時に、画素領域507の接続電極494,496,497とゲート配線495が形成される。この際、金属配線材料は、50nm厚のTi膜と500nm厚のAl−Ti合金膜の積層膜で構成されている。接続電極494は、不純物領域438を介して、ソース配線として機能する電極(第1層電極458と第2層電極445)と画素TFT504を電気的に接続する為に形成されている。接続電極496は、画素TFT504の不純物領域438と電気的に接続されており、接続電極497は保持容量505の不純物領域484と電気的に接続されている。ゲート配線495は、画素TFT504の複数のゲート電極(第1層ゲート電極456と第2層ゲート電極443)を電気的に接続する為に形成されている。次に、ITO(Indium-Tin-Oxides)等の透明導電膜が80〜120nmの厚さで堆積された後、フォトリソグラフィ処理とエッチング処理により、画素電極498が形成される。画素電極498は、接続電極496を介して、画素TFT504のソース・ドレイン領域である不純物領域438と電気的に接続されており、更に接続電極497を介して、保持容量505の不純物領域484とも電気的に接続されている(図10−B参照)。

【0066】

以上の製造工程により、Lov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTで構成されるアクティブマトリクス型液晶ディスプレイを製造することができる。

【0067】

〔実施例2〕

本発明は、様々な半導体表示装置(アクティブマトリクス型液晶表示装置,アクティブマトリクス型EL表示装置,アクティブマトリクス型EC表示装置)に適用することができる。従って、本発明は、前記半導体表示装置を表示媒体として組み込んだ電子機器全般に適用可能である。

【0068】

前記電子機器としては、ビデオカメラとデジタルカメラとプロジェクター(リア型又はフロント型)とヘッドマウントディスプレイ(ゴーグル型ディスプレイ)とゲーム機とカーナビゲーションとパーソナルコンピュータと携帯情報端末(モバイルコンピュータ,携帯電話,電子書籍等)等が挙げられ、それらの具体例を図12〜14に示す。

【0069】

図12−Aは、本体1001と映像入力部1002と表示装置1003とキーボード1004で構成されたパーソナルコンピューターである。本発明を表示装置1003及び他の回路に適用することができる。

【0070】

図12−Bはビデオカメラであり、本体1101と表示装置1102と音声入力部1103と操作スイッチ1104とバッテリー1105と受像部1106で構成される。本発明を表示装置1102及び他の回路に適用することができる。

【0071】

図12−Cはモバイルコンピュータ(モービルコンピュータ)であり、本体1201とカメラ部1202と受像部1203と操作スイッチ1204と表示装置1205で構成される。本発明を表示装置1205及び他の回路に適用することができる。

【0072】

図12−Dはゴーグル型ディスプレイであり、本体1301と表示装置1302とアーム部1303で構成される。本発明を表示装置1302及び他の回路に適用することができる。

【0073】

図12−Eはプログラムを記録した記録媒体(以下、記録媒体と略記)に用いるプレーヤーであり、本体1401と表示装置1402とスピーカー部1403と記録媒体1404と操作スイッチ1405で構成される。尚、この装置は記録媒体としてDVD及びCD等が用いられ、音楽鑑賞又はゲーム又はインターネットに利用可能である。本発明を表示装置1402及び他の回路に適用することができる。

【0074】

図12−Fは携帯電話であり、表示用パネル1501と操作用パネル1502と接続部1503と表示部1504と音声出力部1505と操作キー1506と電源スイッチ1507と音声入力部1508とアンテナ1509で構成される。表示用パネル1501と操作用パネル1502は、接続部1503で接続されている。表示用パネル1501の表示部1504が設置されている面と操作用パネル1502の操作キー1506が設置されている面との角度θは、接続部1503に於いて任意に変えることができる。本発明を表示部1504に適用することができる。

【0075】

図13−Aはフロント型プロジェクターであり、光源光学系及び表示装置1601とスクリーン1602で構成される。本発明を表示装置1601及び他の回路に適用することができる。

【0076】

図13−Bはリア型プロジェクターであり、本体1701と光源光学系及び表示装置1702とミラー1703〜1704とスクリーン1705で構成される。本発明を表示装置1702及び他の回路に適用することができる。

【0077】

尚、図13−Cは、図13−Aの光源光学系及び表示装置1601と図13−Bの光源光学系及び表示装置1702に於ける構造の一例を示した図である。光源光学系及び表示装置1601,1702は、光源光学系1801とミラー1802,1804〜1806とダイクロイックミラー1803と光学系1807と表示装置1808と位相差板1809と投射光学系1810で構成される。投射光学系1810は、投射レンズを備えた複数の光学レンズで構成される。この構成は、表示装置1808を3個使用している為、三板式と呼ばれている。また同図の矢印で示した光路に於いて、実施者は光学レンズ及び偏光機能を有するフィルム又は位相差を調整する為のフィルム又はIRフィルム等を適宜に設けても良い。

【0078】

また図13−Dは、図13−Cに於ける光源光学系1801の構造の一例を示した図である。本実施例に於いては、光源光学系1801はリフレクター1811と光源1812とレンズアレイ1813〜1814と偏光変換素子1815と集光レンズ1816で構成される。尚、同図に示した光源光学系は一例であり、この構成に限定されない。例えば、実施者は光源光学系に光学レンズ及び偏光機能を有するフィルム又は位相差を調整するフィルム又はIRフィルム等を適宜に設けても良い。

【0079】

次の図14−Aは、単板式の例を示したものである。同図に示した光源光学系及び表示装置は、光源光学系1901と表示装置1902と投射光学系1903と位相差板1904で構成される。投射光学系1903は、投射レンズを備えた複数の光学レンズで構成される。同図に示した光源光学系及び表示装置は図13−Aと図13−Bに於ける光源光学系及び表示装置1601,1702に適用できる。また光源光学系1901は図13−Dに示した光源光学系を用いれば良い。尚、表示装置1902にはカラーフィルター(図示しない)が設けられており、表示映像をカラー化している。

【0080】

また図14−Bに示した光源光学系及び表示装置は図14−Aの応用例であり、カラーフィルターを設ける代わりに、RGBの回転カラーフィルター円板1905を用いて表示映像をカラー化している。同図に示した光源光学系及び表示装置は図13−Aと図13−Bに於ける光源光学系及び表示装置1601,表示装置1702に適用できる。

【0081】

また図14−Cに示した光源光学系及び表示装置は、カラーフィルターレス単板式と呼ばれている。この方式は、表示装置1916にマイクロレンズアレイ1915を設け、ダイクロイックミラー(緑)1912とダイクロイックミラー(赤)1913とダイクロイックミラー(青)1914を用いて表示映像をカラー化している。投射光学系1917は、投射レンズを備えた複数の光学レンズで構成される。同図に示した光源光学系及び表示装置は、図13−Aと図13−Bに於ける光源光学系及び表示装置1601,表示装置1702に適用できる。また光源光学系1911としては、光源の他に結合レンズ及びコリメーターレンズを用いた光学系を用いれば良い。

【0082】

上記に示した様に、Lov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTで構成される半導体表示装置の応用範囲は極めて広く、本発明は様々な分野の半導体表示装置を組み込んだ電子機器に適用可能である。

【0083】

【発明の効果】

本発明は、Lov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTの形成に於いて、裏面露光法で自己整合的に形成されたネガレジストパターンをマスクにLov領域へのイオン注入を独立に行うことにより、Lov領域とLoff領域の不純物濃度の独立制御を可能とするものであり、以下の効果が挙げられる。

【0084】

(効果1)Lov領域とLoff領域の不純物濃度の制御により、当該GOLD構造多結晶シリコンTFTはホットキャリア耐性とオフ電流の抑制効果を共に有することができる為、半導体表示装置の画素領域と周辺回路を同一構造のTFTで形成でき、半導体表示装置の製造工程の簡略化に有効である。

【0085】

(効果2)本発明により半導体表示装置の製造工程の簡略化を実現できる為、半導体表示装置の歩留向上及び原価低減に有効である。

【0086】

(効果3)当該GOLD構造多結晶シリコンTFTはホットキャリア耐性とオフ電流の抑制効果を共に有することができる為、半導体表示装置の性能向上に有効である。

【図面の簡単な説明】

【図1】Lov領域とLoff領域を共に有するGOLD構造多結晶シリコンTFTの形成法を示す断面図である。

【図2】移動度(μFE)劣化率とオフ電流のn型不純物注入量依存性を示すグラフである。

【図3】2層構造ゲート電極形成技術と裏面露光技術を適用したGOLD構造多結晶シリコンTFTの形成法(1)を示す断面図である。

【図4】2層構造ゲート電極形成技術と裏面露光技術を適用したGOLD構造多結晶シリコンTFTの形成法(2)を示す断面図である。

【図5】2層構造ゲート電極形成技術と裏面露光技術を適用した半導体表示装置(液晶ディスプレイ)の作製法(1)を示す断面図である。

【図6】2層構造ゲート電極形成技術と裏面露光技術を適用した半導体表示装置(液晶ディスプレイ)の作製法(2)を示す断面図である。

【図7】2層構造ゲート電極形成技術と裏面露光技術を適用した半導体表示装置(液晶ディスプレイ)の作製法(3)を示す断面図である。

【図8】2層構造ゲート電極形成技術と裏面露光技術を適用した半導体表示装置(液晶ディスプレイ)の作製法(4)を示す断面図である。

【図9】2層構造ゲート電極形成技術と裏面露光技術を適用した半導体表示装置(液晶ディスプレイ)の作製法(5)を示す断面図である。

【図10】2層構造ゲート電極形成技術と裏面露光技術を適用した半導体表示装置(液晶ディスプレイ)の作製法(6)を示す断面図である。

【図11】TaN膜の透過率データーを示すグラフである。

【図12】半導体表示装置への適用例(1)を示す電子機器の概略図である。

【図13】半導体表示装置への適用例(2)を示す電子機器の概略図である。

【図14】半導体表示装置への適用例(3)を示す電子機器の概略図である。

【図15】nチャネル型GOLD構造多結晶シリコンTFTのシミュレーションデーター である。

【図16】Pイオン注入した場合のSIMS分析データーである。

【符号の説明】

101 :ガラス基板

102 :半導体層(多結晶シリコン膜)

103 :ゲート絶縁膜

104 :第1層ゲート電極

105 :第2層ゲート電極

106 :高濃度不純物領域(n+領域又はP+領域)

107 :ネガレジストパターン

108 :低濃度不純物領域(n−領域又はP−領域)

109 :低濃度不純物領域(n−−領域又はP−−領域)

201 :ガラス基板

202 :半導体層(多結晶シリコン膜)

203 :ゲート絶縁膜

204 :第1層ゲート電極膜

205 :第2層ゲート電極膜

206 :レジストパターン

207 :ドライエッチング後レジストパターン(ドライエッチングの第1ステップ処理後)

208 :第2層ゲート電極(ドライエッチングの第1ステップ処理後)

209 :ドライエッチング後レジストパターン(ドライエッチングの第2ステップ処理後)

210 :第2層ゲート電極(ドライエッチングの第2ステップ処理後)

211 :第1層ゲート電極(ドライエッチングの第2ステップ処理後)

212 :ゲート絶縁膜(ドライエッチングの第2ステップ処理後)

213 :高濃度不純物領域(n+領域)

214 :ドライエッチング後レジストパターン(ドライエッチングの第3ステップ処理後)

215 :第2層ゲート電極(ドライエッチングの第3ステップ処理後)

216 :第1層ゲート電極(ドライエッチングの第3ステップ処理後)

217 :ゲート絶縁膜(ドライエッチングの第3ステップ処理後)

218 :第2層ゲート電極(ドライエッチングの第4ステップ処理後)

219 :第1層ゲート電極(ドライエッチングの第4ステップ処理後)

220 :ゲート絶縁膜(ドライエッチングの第4ステップ処理後)

221 :ネガレジストパターン

222 :低濃度不純物領域(n−領域)

223 :低濃度不純物領域(n−−領域)

301 :ガラス基板

302 :半導体層(多結晶シリコン膜)

303 :ゲート絶縁膜

304 :第1層ゲート電極膜

305 :第2層ゲート電極膜

306 :レジストパターン

307 :ドライエッチング後レジストパターン(ドライエッチングの第1ステップ処理後)

308 :第2層ゲート電極(ドライエッチングの第1ステップ処理後)

309 :ドライエッチング後レジストパターン(ドライエッチングの第2ステップ処理後)

310 :第2層ゲート電極(ドライエッチングの第2ステップ処理後)

311 :第1層ゲート電極(ドライエッチングの第2ステップ処理後)

312 :ゲート絶縁膜(ドライエッチングの第2ステップ処理後)

313 :高濃度不純物領域(n+領域)

314 :ドライエッチング後レジストパターン(ドライエッチングの第3ステップ処理後)

315 :第2層ゲート電極(ドライエッチングの第3ステップ処理後)

316 :第1層ゲート電極(ドライエッチングの第3ステップ処理後)

317 :ゲート絶縁膜(ドライエッチングの第3ステップ処理後)

318 :第2層ゲート電極(ドライエッチングの第4ステップ処理後)

319 :第1層ゲート電極(ドライエッチングの第4ステップ処理後)

320 :ゲート絶縁膜(ドライエッチングの第4ステップ処理後)

321 :ネガレジストパターン

322 :低濃度不純物領域(n−領域)

323 :低濃度不純物領域(n−−領域)

401 :ガラス基板

402 :下地膜

402a:第1層目の酸化窒化シリコン膜

402b:第2層目の酸化窒化シリコン膜

403 〜407 :半導体層(多結晶シリコン膜)

408 :ゲート絶縁膜(酸化窒化シリコン膜)

409 :第1層ゲート電極膜(TaN膜)

410 :第2層ゲート電極膜(W膜)

411a〜416a:レジストパターン

411b〜416b:ドライエッチング後レジストパターン(ドライエッチングの第1ステップ処理後)

411c〜416c:ドライエッチング後レジストパターン(ドライエッチングの第2ステップ処理後)

411d〜416d:ドライエッチング後レジストパターン(ドライエッチングの第3ステップ処理後)

417 〜420 :第2層ゲート電極(ドライエッチングの第1ステップ処理後)

421 〜422 :第2層電極(ドライエッチングの第1ステップ処理後)

423 〜426 :第2層ゲート電極(ドライエッチングの第2ステップ処理後)

427 〜428 :第2層電極(ドライエッチングの第2ステップ処理後)

429 〜432 :第1層ゲート電極(ドライエッチングの第2ステップ処理後)

433 〜434 :第1層電極(ドライエッチングの第2ステップ処理後)

435 〜439 :高濃度不純物領域(n+領域)

440 〜443 :第2層ゲート電極(ドライエッチングの第3ステップ処理後)

444 〜445 :第2層電極(ドライエッチングの第3ステップ処理後)

446 〜449 :第1層ゲート電極(ドライエッチングの第3ステップ処理後)

450 〜451 :第1層電極(ドライエッチングの第3ステップ処理後)

452 :ゲート絶縁膜(ドライエッチングの第3ステップ処理後)

453 〜456 :第1層ゲート電極(ドライエッチングの第4ステップ処理後)

457 〜458 :第1層電極(ドライエッチングの第4ステップ処理後)

459 :ゲート絶縁膜(ドライエッチングの第4ステップ処理後)

460 〜468 :ネガレジストパターン

469 〜473 :低濃度不純物領域(n−領域)

474 〜478 :低濃度不純物領域(n−−領域)

479 〜481 :レジストパターン

482 :高濃度不純物領域(p+領域)

483 :低濃度不純物領域(p−領域)

484 :高濃度不純物領域(p+領域)

485 :低濃度不純物領域(p−領域)

486 :第1の層間絶縁膜(酸化窒化シリコン膜)

487 :第2の層間絶縁膜(アクリル樹脂膜)

488 〜493 :金属配線

494 :接続電極

495 :ゲート配線

496 〜497 :接続電極

498 :画素電極(ITO等)

501 :nチャネル型TFT

502 :pチャネル型TFT

503 :nチャネル型TFT

504 :画素TFT

505 :保持容量

506 :駆動回路

507 :画素領域[0001]

BACKGROUND OF THE INVENTION

The present invention relates to a semiconductor display device having a circuit formed of a thin film transistor (hereinafter abbreviated as TFT) and a manufacturing method thereof. As the semiconductor display device, for example, there are electro-optical devices such as a liquid crystal display and an EL (electroluminescence) display constituted by TFTs.

[0002]

[Prior art]

In recent years, active matrix liquid crystal display technology using TFTs has attracted attention. The active matrix display is more advantageous than the passive matrix display in terms of response speed, viewing angle, and contrast, and has become the mainstream of current notebook personal computers and liquid crystal televisions.

[0003]

A TFT generally uses amorphous silicon or polycrystalline silicon as a channel layer. In particular, a polycrystalline silicon TFT manufactured by a low-temperature process (generally 600 ° C. or less) has a low electric field and a large area, and at the same time, electrons or holes have a large electric field mobility. As a feature, it is possible to achieve integration of not only the transistors for the driver but also the driver, which is a peripheral circuit, and development has been promoted by each liquid crystal display manufacturer.

[0004]

However, in the case of a polycrystalline silicon TFT, when driven continuously, degradation such as a decrease in mobility and on-current (current that flows when the TFT is on) and an increase in off-current (current that flows when the TFT is off). A phenomenon may be observed, which is a big problem in reliability. This phenomenon is called a hot carrier phenomenon, and is known to be a work of hot carriers generated by a high electric field near the drain.

[0005]

By the way, this hot carrier phenomenon is a phenomenon first discovered in a MOS transistor. For this reason, various basic studies have been conducted so far as measures against hot carriers. In MOS transistors having a design rule of 1.5 μm or less, LDD (Lightly-Doped) is used as a measure against hot carrier phenomenon due to a high electric field near the drain. Abbreviation of -Drain) structure is adopted. In the LDD structure, a low-concentration impurity region (n-region) is provided at the drain end using the sidewall of the gate sidewall, and the concentration of the electric field in the vicinity of the drain is reduced by providing a gradient in the impurity concentration of the drain junction. Yes.

[0006]

In the (but) LDD structure, the drain breakdown voltage is considerably improved as compared with the single drain structure, but the drain current is reduced because the resistance of the low concentration impurity region (n− region) is large. In addition, there is a high electric field region directly under the sidewall, where impact ionization is maximized and hot electrons are injected into the sidewall, so that the low concentration impurity region (n− region) is depleted and the resistance is further increased. The degradation mode peculiar to the LDD that becomes a problem is a problem. As the channel length is reduced, the above problem has become apparent. Therefore, in a MOS transistor having a thickness of 0.5 μm or less, a structure for overcoming this problem overlaps with the end portion of the gate electrode to form a low-concentration impurity region (n A GOLD (abbreviation of Gate-Overlapped LDD) structure that forms a region is devised and adopted.

[0007]

Against this background, the adoption of the LDD structure and the GOLD structure in the polycrystalline silicon TFT which is a constituent element of the liquid crystal display is studied for the purpose of relaxing the high electric field in the vicinity of the drain as in the MOS transistor. Yes. In the case of the LDD structure, a low-concentration impurity region (n− region) is formed in the polycrystalline silicon layer corresponding to the outer region of the gate electrode, and a high-concentration impurity region (n + region) serving as a source / drain region is formed outside thereof. However, the effect of suppressing off-current is high, but the effect of suppressing hot carriers due to electric field relaxation near the drain is small. In the case of one GOLD structure, the low concentration impurity region (n− region) of the LDD structure is formed so as to overlap with the end portion of the gate electrode, and the hot carrier suppressing effect is large as compared with the LDD structure. Has the disadvantage of becoming larger.

[0008]

In addition, as a study example of the GOLD structure in the n-channel type polycrystalline silicon TFT, there is, for example, “Mutuko Hatano, Hajime Akimoto and Takesi Sakai, IEDM97 TECHNICAL DIGEST, p523-526, 1997”, and the basic characteristics of the GOLD structure TFT Is disclosed. The basic structure of the GOLD structure TFT is that a gate electrode and an LDD side wall are formed of polycrystalline silicon, and an active layer (formed of polycrystalline silicon) immediately below the LDD side wall is a low concentration impurity region (electric field relaxation region). n-region) and a high-concentration impurity region (n + region) which is a source region or a drain region is formed outside thereof. The basic characteristics are that, compared with a normal LDD structure TFT, a large drain current can be obtained along with the relaxation of the drain electric field, and the drain avalanche hot carrier (Drain-Avalanche-Hot-Carrier) suppression effect is large. It has been.

[0009]

[Problems to be solved by the invention]

A semiconductor display device such as a liquid crystal display composed of polycrystalline silicon TFTs is composed of a pixel region and a peripheral circuit which is a drive circuit, and the TFT characteristics required for each circuit are different. For example, an LDD structure polycrystalline silicon TFT having a large effect of suppressing off-current is suitable for the pixel region, and a GOLD structure polycrystalline silicon TFT having a high hot carrier resistance is suitable for a peripheral circuit as a drive circuit. From the viewpoint of improving the performance of the semiconductor display device, it is preferable that the pixel region is composed of an LDD structure polycrystalline silicon TFT and the peripheral circuit as a drive circuit is composed of a GOLD structure polycrystalline silicon TFT, but the manufacturing process is complicated. Therefore, an increase in manufacturing costs and a decrease in yield are major issues.

[0010]

An object of the present invention is to provide a semiconductor display device and a manufacturing method thereof that can solve the above-described problems.

[0011]

[Means for solving the problems]

When a semiconductor display device such as a liquid crystal display is configured with a polycrystalline silicon TFT having both hot carrier resistance of the GOLD structured polycrystalline silicon TFT and an off-current suppressing effect of the LDD structured polycrystalline silicon TFT, the pixel region and the drive circuit In the peripheral circuit, it is not necessary to separately form the GOLD structure and the LDD structure, and the manufacturing process can be simplified.

[0012]

A structural feature of the GOLD structure polycrystalline silicon TFT is that a low concentration impurity region (n− region or p− region) existing inside a high concentration impurity region (n + region or p + region) which is a source region or a drain region is It overlaps with the gate electrode. A structural feature of the LDD structure polycrystalline silicon TFT is that the low-concentration impurity region (n-region or p-region) does not overlap the gate electrode. Therefore, a TFT structure having both a low-concentration impurity region (defined as Lov region) overlapping with the gate electrode and a low-concentration impurity region (defined as Loff region) not overlapping with the gate electrode was examined. (Since the TFT having this structure is a kind of GOLD structure, it is hereinafter referred to as a GOLD structure).

[0013]

FIG. 1 shows the main steps of forming the GOLD structure polycrystalline silicon TFT. In the figure, the gate electrode has a two-layer structure of a first

[0014]

Next, a negative resist having a predetermined thickness is formed, and exposure processing is performed from the back surface of the substrate using the first

[0015]

Next, low-concentration ion implantation of n-type or p-type impurities is performed on the

[0016]

Here, the definition of the term ion implantation is clarified. In general, the term ion implantation is applied when implanting mass-separated impurity ions, and ion doping when implanting impurity ions that have not been mass-separated. In a broad sense, the process of introducing impurities into the crystalline silicon film is defined as ion implantation.

[0017]

Next, after removing the negative resist

[0018]

Through the above steps, a GOLD structure polycrystalline silicon TFT having both a Lov region and a Loff region can be formed. FIG. 2 shows the result of examination on the TFT characteristics of the GOLD structure polycrystalline silicon TFT formed here. Figure 2 shows the mobility (μ FE ) The relationship between the deterioration rate and the amount of n-type impurity (P ions) implanted into the Lov region, and the relationship between the off-current and the amount of n-type impurity (P ions) implanted into the Loff region. The evaluation was performed under the condition that both the dimensions of the regions were the same at about 0.7 μm. Here, as an evaluation method for hot carrier resistance, mobility (μ FE ) Evaluation was made using the deterioration rate as an index. The black points and white points in FIG. 2 are the results related to the Lov region and the Loff region, respectively. As can be seen from this figure, mobility (μ FE ) To reduce the deterioration rate, 0.8 × 10 14 ions / cm 2 ~ 1.7 × 10 14 ions / cm 2 A P ion implantation amount of about a degree is necessary, and in order to reduce the off-current, 1 × 10 6 in the Loff region. 13 ions / cm 2 It can be seen that a P ion implantation amount of a certain degree is necessary. As a result of this study, mobility (μ FE ) It is possible to form a GOLD structure polycrystalline silicon TFT capable of achieving both a reduction in degradation rate and a reduction in off current, that is, a GOLD structure polycrystalline silicon TFT having both hot carrier resistance and an off current suppressing effect. This was confirmed (see FIG. 2).

[0019]

The structure of the GOLD structure polycrystalline silicon TFT used in this experiment will be described below. The semiconductor layer in which the source region or the drain region is formed is a polycrystalline silicon film with a thickness of 50 nm, the gate insulating film is a silicon oxynitride film with a thickness of 110 nm, the first layer gate electrode is a TaN film with a thickness of 30 nm, Each layer gate electrode is composed of a W film having a thickness of 370 nm. In addition, ion implantation was examined using an ion doping apparatus in which ions are implanted in a mass unseparated state (see FIG. 2).

[0020]

Next, FIG. 15 shows a result of examination by simulation on the characteristics of the n-channel GOLD structure polycrystalline silicon TFT. FIG. 15-A is simulation data of the maximum electron temperature in the vicinity of the drain-channel junction when the P ion implantation amount into the Lov region is varied. From this result, the amount of P ion implantation into the Lov region is 1.5 × 10 5. 14 ions / cm 2 In this case, the result that the electron temperature is minimized was obtained. This is because the amount of P ion implantation into the Lov region is 1.5 × 10 5. 14 ions / cm 2 In this case, it is suggested that the hot carrier generation rate is minimized, and the above experimental results are almost compatible. FIG. 15-B shows that the amount of P ion implantation into the Lov region is 1.5 × 10 5. 14 ions / cm 2 This is simulation data of the maximum electron temperature and the off-current (Ioff) in the vicinity of the drain-channel junction when the amount of P ion implantation into the Loff region is varied in a fixed state. From this result, the amount of P ion implantation into the Loff region is 1.5 × 10 5. 13 ions / cm 2 To 0.75 × 10 13 ions / cm 2 As a result, both the maximum electron temperature and the off-current (Ioff) in the vicinity of the drain-channel junction were drastically reduced. In the above experimental results, the off-current (Ioff) decreases linearly in proportion to the decrease in the amount of P ion implantation into the Loff region, but there is no major contradiction when variations are considered. Think of things. On the other hand, regarding the on-current (Ion), as shown in FIG. 15C, the on-current (Ion) decreases in proportion to the amount of P ion implantation into the Loff region decreasing. Injection amount 0.75 × 10 13 ions / cm 2 Even in this case, the on-current (Ion) is about 50 μA and the on-current (Ion) is slightly small, but it can be applied as a peripheral circuit (see FIG. 15).

[0021]

Therefore, the effectiveness of the n-channel GOLD structure polycrystalline silicon TFT was also confirmed from the simulation results shown in FIG. Here, a supplementary explanation will be given below for the device structure, etc., which is a prerequisite for this simulation. The structure of the GOLD structure polycrystalline silicon TFT is as follows: W / L = 8/6 μm, Lov region = Loff region = 0.75 μm, a polycrystalline silicon film having a film thickness of 50 nm as a silicon film which is a formation layer of source / drain regions, etc. Suppose a silicon oxynitride film (dielectric constant = 4.1) having a thickness of 110 nm as the gate insulating film, a TaN film having a thickness of 30 nm as the first layer gate electrode, and a W film having a thickness of 370 nm as the second layer gate electrode. Further, simulation was performed by adjusting the impurity profile of SIMS analysis data as channel doping and impurity ion implantation (ion doping method) into the source / drain regions. In this simulation, since the carrier activation rate is unknown, the simulation is performed by artificially setting the activation rate to 20%. In addition, since direct evaluation of hot carrier reliability is impossible in simulation, the maximum electron temperature (equivalent to electron kinetic energy) at the drain-channel junction is calculated, and hot carrier evaluation is performed indirectly. ing.

[0022]

What is important here is that, in order to form a GOLD structure polycrystalline silicon TFT having both hot carrier resistance and an off-current suppressing effect, the appropriate values of the impurity concentrations in the Lov region and the Loff region are different from each other. It is necessary to control. For this reason, in the formation process of the GOLD structure polycrystalline silicon TFT, the ion implantation into the Lov region is performed independently of the ion implantation into the Loff region by using a negative resist pattern formed in a self-aligned manner as a mask. Is.

[0023]

In the present invention, as already described, the negative resist

[0024]

The features of the present invention are briefly described below. In manufacturing a semiconductor display device such as a liquid crystal display, the present invention includes a GOLD structure polycrystalline silicon TFT having a pixel region and a peripheral circuit which is a driving circuit as both a Lov region and a Loff region. It is characterized by realizing both simplification and performance improvement of a semiconductor display device.

[0025]

In the present invention, in the formation of the GOLD structure polycrystalline silicon TFT having both the Lov region and the Loff region, ion implantation into the Lov region is independently performed using a negative resist pattern formed in a self-aligned manner by the backside exposure method as a mask. By doing so, the impurity concentration in the Lov region and the Loff region can be independently controlled. This enables formation of a GOLD structure polycrystalline silicon TFT having both hot carrier resistance and an off-current suppressing effect.

[0026]

DETAILED DESCRIPTION OF THE INVENTION

A method for forming a GOLD structure polycrystalline silicon TFT having both a Lov region and a Loff region will be described with reference to FIG.

[0027]

In the substrate structure used in the present embodiment, a

[0028]

Next, a first step of dry etching is performed using the resist

[0029]

Next, the second step of the dry etching process is continuously performed. By this dry etching process for a predetermined time, the first layer

[0030]

Next, high-concentration ion implantation of n-type impurities, which is a first ion implantation process, is performed using the gate electrode formed of the first

[0031]

Next, the third step of the dry etching process is performed. By the dry etching process for a predetermined time, both the first

[0032]

Next, the fourth step of the dry etching process is continuously performed. By this dry etching process for a predetermined time, the second

[0033]

Next, a negative resist film having a predetermined thickness is applied and baked to form a negative resist film, and exposure is performed from the back surface of the substrate using the first

[0034]

Next, an n-type impurity that is a second ion implantation process is applied to the

[0035]

Next, after removing the negative resist

[0036]

Through the above steps, a GOLD structure polycrystalline silicon TFT having both a Lov region and a Loff region can be formed, and the GOLD structure polycrystalline silicon TFT has advantages of both hot carrier resistance and off-current suppression effect. There are features.

[0037]

[Embodiment 2]

Another method for forming a GOLD structure polycrystalline silicon TFT having both a Lov region and a Loff region will be described with reference to FIG. Although this embodiment is almost the same as

[0038]

In the substrate structure used in this embodiment, a

[0039]

Using the resist

[0040]

Next, high-concentration ion implantation of n-type impurities, which is a first ion implantation process, is performed using a gate electrode including the first

[0041]

Next, the third step of the dry etching process is performed. By this dry etching process for a predetermined time, the second-

[0042]

Next, the fourth step of the dry etching process is continuously performed. By this dry etching process for a predetermined time, the first

[0043]

Next, a negative resist pattern by backside exposure is formed in a self-aligning manner using the first

[0044]

Next, low-concentration ion implantation of n-type impurities, which is a second ion implantation process, is performed on the

[0045]

After removing the negative resist

[0046]

【Example】

[Example 1]

A method for manufacturing an active matrix type liquid crystal display including a GOLD structure polycrystalline silicon TFT having both a Lov region and a Loff region will be specifically described with reference to FIGS.

[0047]

First, a first layer of

[0048]

Next, the polycrystalline silicon film was patterned by a photolithography process and an etching process to form semiconductor layers 403 to 407. At this time, after forming the semiconductor layers 403 to 407, doping with an impurity element (boron or phosphorus) for controlling Vth of the TFT may be performed. Next, a

[0049]

Resist patterns 411a to 414a for forming a gate electrode and resist

[0050]

Next, a first step of a dry etching process is performed using the resist patterns 411a to 416a as a mask. By this dry etching process for a predetermined time, only the second layer

[0051]

Next, the second step of the dry etching process is continuously performed. By this dry etching process for a predetermined time, the first layer

(See FIG. 6-B).

[0052]

Next, a first ion implantation process is performed using the gate electrode composed of the first

[0053]

Here, the P element concentrations in the high concentration impurity regions (n + regions) 435 to 439 were examined in detail based on the SIMS analysis data of FIG. FIG. 16 shows a 5% concentration phosphine (PH Three ) / Hydrogen (H 2 (1) TaN film (15 nm) / silicon oxide film, (2) TaN film (30 nm) / silicon oxide film, and (3) silicon oxide film are accelerated by an ion doping apparatus. Voltage-current density is 90kV-0.5μA / cm 2 Dose amount 1.5 × 10 under the conditions of 14 ions / cm 2 Is SIMS analysis data in the case of ion implantation. Further, in the same figure, the impurity profile in the depth direction is the impurity profile in the silicon oxide film excluding the TaN film. The film structure of the high-concentration impurity regions (n + regions) 435 to 439 is composed of a silicon oxynitride film (residual film thickness of about 90 nm due to etching film reduction) and a polycrystalline silicon film (50 nm thickness) from the surface. The ion stopping ability of the polycrystalline silicon film is almost the same as the ion stopping ability of the silicon oxide film. Therefore, referring to the impurity profile of (3) silicon oxide film substrate in FIG. 16, the impurity concentration of the high concentration impurity region (n + region) 435 to 439, that is, the impurity concentration in the polycrystalline silicon film (50 nm thickness) is examined. did. Dose amount 1.5 × 10 14 ions / cm 2 In this case, the impurity concentration in the polycrystalline silicon film is 5 × 10. 18 ~ 8x10 18 atoms / cm Three The actual dose amount is 5 × 10 14 ~ 5x10 15 ions / cm 2 In this case, the impurity concentration in the polycrystalline silicon film is set to 1.7 × 10 6 by proportional calculation. 19 ~ 2.7 × 10 20 atoms / cm Three It is thought to be about. In actual ion implantation, since the acceleration voltage has a range of 60 to 100 kV, the impurity concentration range is expected to further expand due to the influence of the set acceleration voltage. Considering this point, the range of the impurity concentration of the high concentration impurity regions (n + regions) 435 to 439 is assumed to be a range obtained by multiplying the minimum value by a correction factor of about 0.2 times and the maximum value by about 20 times as the maximum range. Is done. Therefore, the impurity concentration of the high-concentration impurity regions (n + regions) 435 to 439 is 3 × 10 18 ~ 5x10 twenty one atoms / cm Three Degree, more preferably 1.7 × 10 19 ~ 2.7 × 10 20 atoms / cm Three The degree is estimated (see FIG. 16).

[0054]

Next, the third step of the dry etching process is performed. By this dry etching process for a predetermined time, the second-

[0055]

Next, the fourth step of the dry etching process is continuously performed. By this dry etching process for a predetermined time, the first

[0056]

Next, a negative resist film having a predetermined thickness is applied and baked to form a negative resist film, and exposure is performed from the back surface of the substrate using the first

[0057]

Next, the first

[0058]

Here, the P element concentrations in the low-concentration impurity regions (n− regions) 469 to 472 were examined in detail based on the SIMS analysis data of FIG. 16. FIG. 16 shows a 5% concentration phosphine (PH Three ) / Hydrogen (H 2 (1) TaN film (15 nm) / silicon oxide film, (2) TaN film (30 nm) / silicon oxide film, and (3) silicon oxide film are accelerated by an ion doping apparatus. Voltage-current density is 90kV-0.5μA / cm 2 Dose amount 1.5 × 10 under the conditions of 14 ions / cm 2 Is SIMS analysis data in the case of ion implantation. The film structure of the low-concentration impurity regions (n− regions) 469 to 472 includes first

[0059]

Next, after removing the negative resist

[0060]

Here, the P element concentration in the low concentration impurity regions (n−− regions) 474 to 477 was examined in detail based on the SIMS analysis data of FIG. 16. FIG. 16 shows a 5% concentration phosphine (PH Three ) / Hydrogen (H 2 (1) TaN film (15 nm) / silicon oxide film, (2) TaN film (30 nm) / silicon oxide film, and (3) silicon oxide film are accelerated by an ion doping apparatus. Voltage-current density is 90kV-0.5μA / cm 2 Dose amount 1.5 × 10 under the conditions of 14 ions / cm 2 Is SIMS analysis data in the case of ion implantation. The low-concentration impurity regions (n−− regions) 474 to 477 are composed of a silicon oxynitride film (estimated to have a remaining film thickness of about 50 nm due to etching film reduction) and a polycrystalline silicon film (50 nm thickness) from the surface. Since the ion stopping ability of the silicon oxynitride film and the polycrystalline silicon film is almost the same as the ion stopping ability of the silicon oxide film, the low concentration impurity is referred to by referring to the impurity profile of (3) silicon oxide film substrate in FIG. The impurity concentration in the region (n−− region) 474 to 477, that is, the impurity concentration in the polycrystalline silicon film (50 nm thickness) was examined. Dose amount 1.5 × 10 14 ions / cm 2 In this case, the impurity concentration in the polycrystalline silicon film is 7 × 10. 18 ~ 8x10 18 atoms / cm Three The actual dose amount is 1 × 10 13 ions / cm 2 In this case, the impurity concentration in the polycrystalline silicon film is determined to be 4.7 × 10 6 by proportional calculation. 17 ~ 5.3 × 10 17 atoms / cm Three It is thought to be about. In actual ion implantation, since the acceleration voltage has a range of 60 to 100 kV, the impurity concentration range is expected to further expand due to the influence of the set acceleration voltage. Considering this point, the impurity concentration range of the low-concentration impurity regions (n−− regions) 474 to 477 is a range obtained by multiplying the minimum value by a correction factor of about 0.01 times and the maximum value by about 5 times as the maximum range. Is assumed. Therefore, the impurity concentration of the low-concentration impurity regions (n−− regions) 474 to 477 is 4.7 × 10 7. 15 ~ 2.7 × 10 18 atoms / cm Three , More preferably 4.7 × 10 17 ~ 5.3 × 10 17 atoms / cm Three The degree is estimated (see FIG. 16).

[0061]

Next, resist

[0062]

Using the resist

[0063]

Next, after removing the resist

[0064]

Next, a second

[0065]

Next,

[0066]

Through the above manufacturing process, an active matrix liquid crystal display composed of a GOLD structure polycrystalline silicon TFT having both a Lov region and a Loff region can be manufactured.

[0067]

[Example 2]

The present invention can be applied to various semiconductor display devices (active matrix liquid crystal display devices, active matrix EL display devices, active matrix EC display devices). Therefore, the present invention can be applied to all electronic devices in which the semiconductor display device is incorporated as a display medium.

[0068]

Examples of the electronic device include a video camera, a digital camera, a projector (rear type or front type), a head mounted display (goggles type display), a game machine, a car navigation system, a personal computer, and a portable information terminal (mobile computer, cellular phone, electronic Books) etc., and specific examples thereof are shown in FIGS.

[0069]

FIG. 12A illustrates a personal computer including a main body 1001, a video input unit 1002, a display device 1003, and a

[0070]

FIG. 12B illustrates a video camera, which includes a main body 1101, a display device 1102, an

[0071]

FIG. 12C illustrates a mobile computer, which includes a main body 1201, a camera unit 1202, an

[0072]

FIG. 12D shows a goggle type display, which is composed of a main body 1301, a

[0073]

FIG. 12E shows a player used as a recording medium (hereinafter abbreviated as recording medium) in which a program is recorded, and includes a main body 1401, a

[0074]

FIG. 12-F shows a mobile phone, which includes a display panel 1501, an

[0075]

FIG. 13A shows a front projector, which includes a light source optical system and

[0076]

FIG. 13B shows a rear projector, which includes a main body 1701, a light source optical system and

[0077]

13C is a diagram showing an example of the structure of the light source optical system and

[0078]

FIG. 13-D is a diagram showing an example of the structure of the light source optical system 1801 in FIG. 13-C. In this embodiment, the light source optical system 1801 includes a reflector 1811, a light source 1812, lens arrays 1813 to 1814, a polarization conversion element 1815, and a condenser lens 1816. The light source optical system shown in the figure is an example and is not limited to this configuration. For example, the practitioner may appropriately provide a light source optical system with an optical lens and a film having a polarization function, a film for adjusting a phase difference, an IR film, or the like.

[0079]

FIG. 14A shows an example of a single plate type. The light source optical system and display device shown in FIG. 1 includes a light source optical system 1901, a display device 1902, a projection optical system 1903, and a phase difference plate 1904. The projection optical system 1903 is composed of a plurality of optical lenses provided with a projection lens. The light source optical system and display device shown in FIG. 13 can be applied to the light source optical system and

[0080]

The light source optical system and display device shown in FIG. 14-B is an application example of FIG. 14-A. Instead of providing a color filter, a display image is colored using an RGB rotating color filter disc 1905. . The light source optical system and display device shown in FIG. 13 can be applied to the light source optical system and

[0081]

Further, the light source optical system and the display device shown in FIG. 14-C are called a color filterless single plate type. In this system, a microlens array 1915 is provided in a display device 1916, and a display image is colored using a dichroic mirror (green) 1912, a dichroic mirror (red) 1913, and a dichroic mirror (blue) 1914. The projection optical system 1917 includes a plurality of optical lenses provided with a projection lens. The light source optical system and display device shown in FIG. 13 can be applied to the light source optical system and

[0082]

As shown above, the application range of the semiconductor display device composed of the GOLD structure polycrystalline silicon TFT having both the Lov region and the Loff region is very wide, and the present invention is an electronic apparatus incorporating semiconductor display devices in various fields. It is applicable to.

[0083]

【The invention's effect】

According to the present invention, in the formation of a GOLD structure polycrystalline silicon TFT having both a Lov region and a Loff region, ion implantation into the Lov region is independently performed using a negative resist pattern formed in a self-aligned manner by a backside exposure method as a mask. By doing so, the impurity concentration in the Lov region and the Loff region can be independently controlled, and the following effects can be given.

[0084]

(Effect 1) By controlling the impurity concentration in the Lov region and the Loff region, the GOLD structure polycrystalline silicon TFT can have both hot carrier resistance and an off-current suppressing effect. Therefore, the pixel region and the peripheral circuit of the semiconductor display device Can be formed with TFTs having the same structure, which is effective in simplifying the manufacturing process of the semiconductor display device.

[0085]

(Effect 2) Since the present invention can simplify the manufacturing process of the semiconductor display device, it is effective for improving the yield of the semiconductor display device and reducing the cost.

[0086]

(Effect 3) Since the GOLD structure polycrystalline silicon TFT can have both hot carrier resistance and an off-current suppressing effect, it is effective in improving the performance of the semiconductor display device.

[Brief description of the drawings]

FIG. 1 is a cross-sectional view showing a method for forming a GOLD structure polycrystalline silicon TFT having both a Lov region and a Loff region.

[Fig. 2] Mobility (μ FE ) A graph showing the dependence of the deterioration rate and off-current on the n-type impurity implantation amount.

FIG. 3 is a cross-sectional view showing a method (1) of forming a GOLD structure polycrystalline silicon TFT to which a two-layer structure gate electrode formation technique and a backside exposure technique are applied.

FIG. 4 is a cross-sectional view showing a formation method (2) of a GOLD structure polycrystalline silicon TFT to which a two-layer structure gate electrode formation technique and a backside exposure technique are applied.

FIG. 5 is a cross-sectional view showing a manufacturing method (1) of a semiconductor display device (liquid crystal display) to which a two-layer structure gate electrode formation technique and a backside exposure technique are applied.

FIG. 6 is a cross-sectional view showing a manufacturing method (2) of a semiconductor display device (liquid crystal display) to which a two-layer structure gate electrode formation technique and a backside exposure technique are applied.

FIG. 7 is a cross-sectional view showing a manufacturing method (3) of a semiconductor display device (liquid crystal display) to which a two-layer structure gate electrode formation technique and a backside exposure technique are applied.

FIG. 8 is a cross-sectional view showing a manufacturing method (4) of a semiconductor display device (liquid crystal display) to which a two-layer structure gate electrode formation technique and a backside exposure technique are applied.

FIG. 9 is a cross-sectional view showing a manufacturing method (5) of a semiconductor display device (liquid crystal display) to which a two-layer structure gate electrode formation technique and a backside exposure technique are applied.

FIG. 10 is a cross-sectional view showing a manufacturing method (6) of a semiconductor display device (liquid crystal display) to which a two-layer structure gate electrode formation technique and a backside exposure technique are applied.

FIG. 11 is a graph showing transmittance data of a TaN film.

FIG. 12 is a schematic diagram of an electronic apparatus showing an application example (1) to a semiconductor display device.

FIG. 13 is a schematic view of an electronic apparatus showing an application example (2) to a semiconductor display device.

FIG. 14 is a schematic diagram of an electronic apparatus showing an application example (3) to a semiconductor display device.

FIG. 15 is simulation data of an n-channel GOLD structure polycrystalline silicon TFT.

FIG. 16 shows SIMS analysis data when P ions are implanted.

[Explanation of symbols]

101: Glass substrate

102: Semiconductor layer (polycrystalline silicon film)

103: Gate insulation film

104: First layer gate electrode

105: Second layer gate electrode

106: High concentration impurity region (n + region or P + region)

107: Negative resist pattern

108: Low-concentration impurity region (n-region or P-region)

109: Low-concentration impurity region (n−− region or P−− region)

201: Glass substrate

202: Semiconductor layer (polycrystalline silicon film)

203: Gate insulation film

204: First layer gate electrode film

205: Second layer gate electrode film

206: Resist pattern

207: Resist pattern after dry etching (after first step of dry etching)

208: Second layer gate electrode (after first step of dry etching)

209: Resist pattern after dry etching (after the second step of dry etching)

210: Second layer gate electrode (after the second step of dry etching)

211: First layer gate electrode (after the second step of dry etching)

212: Gate insulating film (after the second step of dry etching)

213: High concentration impurity region (n + region)

214: Resist pattern after dry etching (after third step of dry etching)

215: Second layer gate electrode (after third step treatment of dry etching)

216: First layer gate electrode (after third step of dry etching)

217: Gate insulating film (after the third step of dry etching)

218: Second layer gate electrode (after the fourth step of dry etching)

219: First layer gate electrode (after the fourth step of dry etching)

220: Gate insulating film (after the fourth step of dry etching)

221: Negative resist pattern

222: Low-concentration impurity region (n-region)

223: Low-concentration impurity region (n−− region)

301: Glass substrate

302: Semiconductor layer (polycrystalline silicon film)

303: Gate insulating film

304: First layer gate electrode film

305: Second layer gate electrode film

306: Resist pattern

307: Resist pattern after dry etching (after first step of dry etching)

308: Second layer gate electrode (after first step of dry etching)

309: Resist pattern after dry etching (after the second step of dry etching)

310: Second layer gate electrode (after the second step of dry etching)

311: First layer gate electrode (after the second step of dry etching)

312: Gate insulating film (after the second step of dry etching)

313: High concentration impurity region (n + region)

314: Resist pattern after dry etching (after the third step of dry etching)

315: Second layer gate electrode (after third step of dry etching)

316: First layer gate electrode (after the third step of dry etching)

317: Gate insulating film (after the third step of dry etching)

318: Second layer gate electrode (after the fourth step of dry etching)

319: First layer gate electrode (after the fourth step of dry etching)

320: Gate insulating film (after the fourth step of dry etching)

321: Negative resist pattern

322: Low-concentration impurity region (n− region)

323: Low concentration impurity region (n−− region)

401: Glass substrate

402: Underlayer

402a: First layer silicon oxynitride film

402b: Second layer silicon oxynitride film

403 to 407: Semiconductor layer (polycrystalline silicon film)

408: Gate insulating film (silicon oxynitride film)

409: First layer gate electrode film (TaN film)

410: Second layer gate electrode film (W film)

411a to 416a: Resist pattern

411b to 416b: Resist pattern after dry etching (after first step of dry etching)

411c to 416c: Resist pattern after dry etching (after the second step of dry etching)

411d to 416d: Resist pattern after dry etching (after third step of dry etching)

417 to 420: Second layer gate electrode (after the first step of dry etching)

421 to 422: Second layer electrode (after the first step of dry etching)

423 to 426: Second layer gate electrode (after the second step of dry etching)

427 to 428: Second layer electrode (after the second step treatment of dry etching)

429 to 432: first layer gate electrode (after the second step of dry etching)

433-434: 1st layer electrode (after the 2nd step process of dry etching)

435 to 439: high-concentration impurity region (n + region)

440 to 443: Second layer gate electrode (after third step treatment of dry etching)

444 to 445: Second layer electrode (after third step treatment of dry etching)

446 to 449: first layer gate electrode (after third step treatment of dry etching)

450 to 451: First layer electrode (after the third step of dry etching)

452: Gate insulating film (after the third step of dry etching)

453 to 456: First layer gate electrode (after the fourth step of dry etching)

457 to 458: First layer electrode (after the fourth step of dry etching)

459: Gate insulating film (after the fourth step of dry etching)

460-468: Negative resist pattern

469 to 473: Low concentration impurity region (n− region)

474 to 478: low concentration impurity region (n−− region)

479 to 481: resist pattern

482: High concentration impurity region (p + region)

483: Low-concentration impurity region (p-region)

484: High concentration impurity region (p + region)

485: Low-concentration impurity region (p-region)

486: First interlayer insulating film (silicon oxynitride film)

487: Second interlayer insulating film (acrylic resin film)

488-493: Metal wiring

494: Connection electrode

495: Gate wiring

496 to 497: Connection electrodes

498: Pixel electrode (ITO etc.)

501: n-channel TFT

502: p-channel TFT

503: n-channel TFT

504: Pixel TFT

505: Holding capacity

506: Drive circuit

507: Pixel area

Claims (6)

前記第2層ゲート電極膜上にゲート電極形成用のレジストパターンを形成する第2の工程と、

前記レジストパターンをマスクにドライエッチングし、第1層ゲート電極と第2層ゲート電極とから成る第1形状のゲート電極を形成する第3の工程と、

前記半導体層のうち、前記第1形状のゲート電極に覆われていない領域に一導電型の不純物をイオン注入することによって、前記第1形状のゲート電極と重ならない第1の不純物領域を形成する第4の工程と、

前記第1形状のゲート電極上に存在するレジストパターンをマスクに前記第1形状のゲート電極の第1層ゲート電極及び第2層ゲート電極を追加エッチングし、第2形状のゲート電極の第1層ゲート電極及び第2層ゲート電極を形成し、前記第2形状のゲート電極の第1層ゲート電極は前記第1形状のゲート電極の第1層ゲート電極よりチャネル方向の寸法が短く、且つ前記第2形状のゲート電極の第2層ゲート電極よりチャネル方向の寸法の長くする第5の工程と、

前記第2形状のゲート電極上にレジストを形成し、前記第2形状のゲート電極の第1層ゲート電極をマスクに裏面露光を行い、自己整合的にネガレジストパターンを形成する第6の工程と、

前記半導体層のうち、前記第2形状のゲート電極の第1層ゲート電極の露出領域と重なる領域に前記一導電型と同一導電型の不純物をイオン注入することによって、前記第2形状のゲート電極の第1層ゲート電極と重なる第2の不純物領域を形成する第7の工程と、

前記ネガレジストパターンを除去する第8の工程と、

前記半導体層のうち、前記第2形状のゲート電極に覆われていない領域に前記一導電型と同一導電型の不純物をイオン注入することによって、前記第2形状のゲート電極と重ならない第3の不純物領域を形成する第9の工程とを備え、

前記第2の不純物領域を形成する際のドーズ量を前記第1の不純物領域を形成する際のドーズ量より低く、前記第3の不純物領域を形成する際のドーズ量より高くすることを特徴とする半導体表示装置の作製方法。A first step of sequentially laminating a semiconductor layer, a gate insulating film, a first layer gate electrode film, and a second layer gate electrode film on a transparent insulating substrate from the side closest to the transparent insulating substrate;

A second step of forming a resist pattern for forming a gate electrode on the second layer gate electrode film;

A third step of dry-etching using the resist pattern as a mask to form a first-shaped gate electrode comprising a first-layer gate electrode and a second-layer gate electrode;

A first impurity region that does not overlap with the first shape gate electrode is formed by ion-implanting one conductivity type impurity into a region of the semiconductor layer that is not covered with the first shape gate electrode. A fourth step;

Using the resist pattern present on the first shape gate electrode as a mask, the first layer gate electrode and the second layer gate electrode of the first shape gate electrode are additionally etched to form a first layer of the second shape gate electrode. Forming a gate electrode and a second layer gate electrode, wherein the first layer gate electrode of the second shape gate electrode is shorter in the channel direction than the first layer gate electrode of the first shape gate electrode, and the first shape gate electrode A fifth step of making the dimension in the channel direction longer than the second-layer gate electrode of the two-shaped gate electrode;

A sixth step of forming a resist on the second-shaped gate electrode, performing backside exposure using the first-layer gate electrode of the second-shaped gate electrode as a mask, and forming a negative resist pattern in a self-aligning manner; ,

The second shape gate electrode is formed by ion-implanting an impurity having the same conductivity type as the one conductivity type into a region of the semiconductor layer that overlaps the exposed region of the first layer gate electrode of the second shape gate electrode. A seventh step of forming a second impurity region overlapping with the first layer gate electrode ;

An eighth step of removing the negative resist pattern;

By implanting ions of the same conductivity type as the one conductivity type into a region of the semiconductor layer that is not covered with the second shape gate electrode, a third layer that does not overlap with the second shape gate electrode is formed. and a ninth step of forming an impurity region,

The dose amount when forming the second impurity region is lower than the dose amount when forming the first impurity region, and higher than the dose amount when forming the third impurity region. A method for manufacturing a semiconductor display device.

前記第2層ゲート電極膜上にゲート電極形成用のレジストパターンを形成する第2の工程と、

前記レジストパターンをマスクにドライエッチングし、第1層ゲート電極と第2層ゲート電極とから成る第1形状のゲート電極を形成する第3の工程と、

前記半導体層のうち、前記第1形状のゲート電極に覆われていない領域に一導電型の不純物イオンを注入することによって、前記第1形状のゲート電極と重ならない第1の不純物領域を形成する第4の工程と、

前記第1形状のゲート電極上に存在するレジストパターンをマスクに前記第1形状のゲート電極の第1層ゲート電極及び第2層ゲート電極を追加エッチングし、第2形状のゲート電極の第1層ゲート電極及び第2層ゲート電極を形成し、前記第2形状のゲート電極の第1層ゲート電極は前記第1形状のゲート電極の第1層ゲート電極よりチャネル方向の寸法が短く、且つ前記第2形状のゲート電極の第2層ゲート電極よりチャネル方向の寸法の長くする第5の工程と、

前記半導体層のうち、前記第2形状のゲート電極に覆われていない領域に前記一導電型と同一導電型の不純物をイオン注入することによって、前記第2形状のゲート電極と重ならない第3の不純物領域を形成する第6の工程と、

前記第2形状のゲート電極上にレジストを形成し、前記第2形状のゲート電極の第1層ゲート電極をマスクに裏面露光を行い、自己整合的にネガレジストパターンを形成する第7の工程と、

前記半導体層のうち、前記第2形状のゲート電極の第1層ゲート電極の露出領域と重なる領域に前記一導電型と同一導電型の不純物をイオン注入することによって、前記第2形状のゲート電極の第1層ゲート電極と重なる第2の不純物領域を形成する第8の工程とを備え、

前記第2の不純物領域を形成する際のドーズ量を前記第1の不純物領域を形成する際のドーズ量より低く、前記第3の不純物領域を形成する際のドーズ量より高くすることを特徴とする半導体表示装置の作製方法。A first step of sequentially forming a semiconductor layer, a gate insulating film, a first layer gate electrode film, and a second layer gate electrode film on a transparent insulating substrate from the side closer to the transparent insulating substrate;

A second step of forming a resist pattern for forming a gate electrode on the second layer gate electrode film;