JP5043217B2 - Game machine - Google Patents

Game machine Download PDFInfo

- Publication number

- JP5043217B2 JP5043217B2 JP2011168809A JP2011168809A JP5043217B2 JP 5043217 B2 JP5043217 B2 JP 5043217B2 JP 2011168809 A JP2011168809 A JP 2011168809A JP 2011168809 A JP2011168809 A JP 2011168809A JP 5043217 B2 JP5043217 B2 JP 5043217B2

- Authority

- JP

- Japan

- Prior art keywords

- serial

- game

- data

- effect control

- flag

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Pinball Game Machines (AREA)

Description

本発明は、外枠に対して開閉自在に設置される遊技枠と、遊技枠に取り付けられ、所定の板状体および板状体に取り付けられる各種部品を含む遊技盤とを備え、遊技盤を交換可能な遊技機に関する。 The present invention includes a game frame that can be opened and closed with respect to an outer frame, and a game board that is attached to the game frame and includes a predetermined plate-like body and various parts that are attached to the plate-like body. It relates to exchangeable gaming machines.

遊技機として、遊技球などの遊技媒体を発射装置によって遊技領域に発射し、遊技領域に設けられている入賞口などの入賞領域に遊技媒体が入賞すると、所定個の賞球が遊技者に払い出されるものがある。さらに、識別情報を可変表示(「変動」ともいう。)可能な可変表示装置が遊技盤に設けられ、可変表示装置において識別情報の可変表示の表示結果が特定表示結果となった場合に遊技者にとって有利な特定遊技状態に制御可能になるように構成されたものがある。 As a gaming machine, a game medium such as a game ball is launched into a game area by a launching device, and when a game medium wins a prize area such as a prize opening provided in the game area, a predetermined number of prize balls are paid out to the player. There is something to be done. Further, a variable display device capable of variably displaying the identification information (also referred to as “variation”) is provided on the game board, and the player when the display result of the variable display of the identification information in the variable display device becomes the specific display result. Some are configured to be controllable to a specific gaming state advantageous to the user.

特定遊技状態とは、所定の遊技価値が付与された遊技者にとって有利な状態を意味する。具体的には、特定遊技状態は、例えば特別可変入賞装置の状態を打球が入賞しやすい遊技者にとって有利な状態(大当り遊技状態)、遊技者にとって有利な状態になるための権利が発生した状態、景品遊技媒体払出の条件が成立しやすくなる状態などの所定の遊技価値が付与された状態である。 The specific game state means a state advantageous for a player who is given a predetermined game value. Specifically, the specific game state is, for example, a state in which a special variable winning device is advantageous for a player who is likely to win a ball (a big hit game state), or a state in which a right to be advantageous for a player has occurred. In this state, a predetermined game value such as a state where conditions for paying out premium game media are easily established is given.

そのような遊技機では、識別情報としての図柄を表示する可変表示装置の表示結果があらかじめ定められた特定の表示態様の組合せ(特定表示結果)になることを、通常、「大当り」という。大当りが発生すると、例えば、大入賞口が所定回数開放して打球が入賞しやすい大当り遊技状態に移行する。そして、各開放期間において、所定個(例えば10個)の大入賞口への入賞があると大入賞口は閉成する。そして、大入賞口の開放回数は、所定回数(例えば15ラウンド)に固定されている。なお、各開放について開放時間(例えば29.5秒)が決められ、入賞数が所定個に達しなくても開放時間が経過すると大入賞口は閉成する。また、大入賞口が閉成した時点で所定の条件(例えば、大入賞口内に設けられているVゾーンへの入賞)が成立していない場合には、大当り遊技状態を終了するように構成されたものもある。 In such a gaming machine, the fact that the display result of the variable display device that displays the symbol as identification information is a combination of specific display modes (specific display result) determined in advance is generally referred to as “big hit”. When the big hit occurs, for example, the big winning opening is opened a predetermined number of times, and the game shifts to a big hit gaming state where the hit ball is easy to win. And in each open period, if there is a prize for a predetermined number (for example, 10) of the big prize opening, the big prize opening is closed. And the number of times the special winning opening is opened is fixed to a predetermined number (for example, 15 rounds). An opening time (for example, 29.5 seconds) is determined for each opening, and even if the number of winnings does not reach a predetermined number, the big winning opening is closed when the opening time elapses. Further, when a predetermined condition (for example, winning in the V zone provided in the big prize opening) is not established at the time when the big prize opening is closed, the big hit gaming state is ended. Some are also available.

また、そのような遊技機では、遊技機の外枠に対して開閉自在に設置される遊技枠と、遊技枠に取り付けられ、所定の板状体および板状体に取り付けられる各種部品を含む遊技盤とが脱着自在に構成されたものがある。そのような遊技機では、遊技機の機種変更(例えば、新機種への変更)を行う場合には、遊技機全体を交換するのではなく、遊技枠をそのまま残し、遊技盤のみ交換される。すなわち、遊技盤のみを交換することによって遊技機の機種変更が行われ、遊技演出における演出内容が変更される。 In addition, in such a gaming machine, a game frame including a game frame installed to be openable and closable with respect to an outer frame of the gaming machine, a predetermined plate-like body, and various components attached to the plate-like body. There is a board that is detachable. In such a gaming machine, when changing the model of the gaming machine (for example, changing to a new model), the entire gaming machine is not replaced, but the gaming frame is left as it is, and only the gaming board is replaced. That is, by changing only the game board, the model of the gaming machine is changed, and the content of the effect in the game effect is changed.

また、特許文献1には、シリアルデータをパラレルデータに変換するIC回路を介して、CPUと遊技演出に用いるマルチカラーLEDとを接続するように構成された遊技機が記載されている。また、特許文献1には、マルチカラーLEDの発光状態を制御する際に、所定の制御単位時間内に出力するパルスの数を変えることによって、マルチカラーLEDの明るさを調整するように構成することが記載されている。

Further,

また、特許文献2には、各種表示器やスピーカなどを制御するための各制御基板のCPUに個別のアドレスを設定しておき、副制御基板のCPUと各制御基板のCPUとを双方向シリアルバス配線を介して接続することによって、遊技機の筐体とドアとの間の配線数を低減するように構成することが記載されている。

In

遊技枠と遊技盤とが着脱自在に構成された遊技機では、遊技機の機種変更のために遊技盤の交換を行う際に、遊技盤と遊技枠との間を接続する配線数が多いと、遊技盤と遊技枠との間の配線作業に手間がかかり煩雑である。特許文献1や特許文献2に記載された遊技機では、シリアル−パラレル変換用のIC回路を用いてCPUと表示器との間の配線数を低減したり、双方向シリアルバス配線を用いることによって制御基板間の配線数を低減することはできる。しかし、遊技枠と遊技盤とが着脱自在に構成された遊技機において、遊技盤と遊技枠との間の配線数を低減することはできず、遊技枠と遊技盤との着脱作業を容易に行えるようにすることができない。

In a gaming machine in which the game frame and the game board are detachable, when the game board is exchanged for changing the model of the game machine, there are many wirings connecting the game board and the game frame. The wiring work between the game board and the game frame is troublesome and cumbersome. In the gaming machines described in

そこで、本発明は、遊技枠と遊技盤とが着脱自在に構成された遊技機において、遊技枠と遊技盤との着脱作業を容易に行えるようにすることを目的とする。 Therefore, an object of the present invention is to make it possible to easily attach and detach a game frame and a game board in a game machine in which a game frame and a game board are detachable.

本発明による遊技機は、外枠に対して開閉自在に設置される遊技枠(例えば、遊技枠11)と、遊技枠に取り付けられ、所定の板状体および板状体に取り付けられる各種部品を含む遊技盤(例えば、遊技盤6)とを備え、遊技盤を交換可能な遊技機であって、遊技の進行を制御し、演出用の電気部品を制御させるための演出制御コマンドを送信する遊技制御手段(例えば、遊技制御用マイクロコンピュータ560)と、遊技制御手段が送信した演出制御コマンドに応じて演出用の電気部品(例えば、各ランプのLED125a〜125f,126a〜126f,281a〜281l,282a〜282f,283a〜283f、モータ151a,152a,153a)を制御する演出制御手段(例えば、演出制御用マイクロコンピュータ100)とを備え、遊技制御手段と演出制御手段とは、遊技盤に搭載され、遊技制御手段は、演出制御コマンドを演出制御手段に送信するコマンド送信手段(例えば、遊技制御用マイクロコンピュータ560におけるステップS29を実行する部分)を含み、演出制御手段は、遊技制御手段から受信した演出制御コマンドにもとづいて、演出用の電気部品を制御するための制御信号をシリアル信号方式で出力する出力手段(例えば、演出制御用マイクロコンピュータ100におけるステップS708を実行する部分)を含み、遊技盤に設けられた盤側シリアル−パラレル変換回路(例えば、シリアル−パラレル変換IC616〜619)および遊技枠に設けられた複数の枠側シリアル−パラレル変換回路(例えば、シリアル−パラレル変換IC611〜615)をさらに備え、盤側シリアル−パラレル変換回路は、演出制御手段の出力手段から入力された制御信号をシリアル信号方式からパラレル信号方式に変換して、演出用の電気部品のうち遊技盤に設けられた電気部品(例えば、ランプのLED125a〜125f,126a〜126f、モータ151a,152a,153a)に出力し、複数の枠側シリアル−パラレル変換回路は、演出制御手段の出力手段から入力された制御信号をシリアル信号方式からパラレル信号方式に変換して、演出用の電気部品のうち遊技枠に設けられた電気部品(例えば、ランプのLED281a〜281l,282a〜282f,283a〜283f,82a〜82d,83)に出力するものであり、盤側シリアル−パラレル変換回路と複数の枠側シリアル−パラレル変換回路、または演出制御手段と複数の枠側シリアル−パラレル変換回路は、1系統の配線を介して接続され(例えば、中継基板606,607がバス型に接続されることによって1系統の配線を介して接続される。各シリアル−パラレル変換IC611〜619がバス形式またはデイジーチェーン型に接続されることによって1系統に接続される)、さらに、盤側シリアル−パラレル変換回路または複数の枠側シリアル−パラレル変換回路の少なくとも一部は、同一の系統の配線で直列に接続され、出力手段は、同一の系統の配線に接続された全ての演出用の電気部品の制御信号の情報を含む固定長さのデータを単位データずつ所定周期ごとにシリアル信号方式で出力し、同一の系統の配線に接続された盤側シリアル−パラレル変換回路または複数の枠側シリアル−パラレル変換回路は、同一の系統の配線の下位側に接続された盤側シリアル−パラレル変換回路または複数の枠側シリアル−パラレル変換回路のいずれかに、所定周期ごとに出力された単位データの制御信号をそのまま順次転送するとともに、所定のタイミングで単位データにもとづいて制御信号を出力し、出力手段は、モータを駆動するための制御信号を出力可能であることを特徴とする。

そのような構成により、演出制御手段が、遊技制御手段から受信した演出制御コマンドにもとづいて、演出用の電気部品を制御するための制御信号をシリアル信号方式で出力する出力手段を含み、盤側シリアル−パラレル変換回路と複数の枠側シリアル−パラレル変換回路、または演出制御手段と複数の枠側シリアル−パラレル変換回路が、1系統の配線を介して接続されるように構成されているので、遊技盤と遊技枠との間の配線数を低減することができる。従って、遊技枠と遊技盤とが着脱自在に構成された遊技機において、遊技枠と遊技盤との着脱作業を容易に行えるようにすることができる。

A gaming machine according to the present invention includes a game frame (for example, a game frame 11) installed so as to be openable and closable with respect to an outer frame, a predetermined plate-like body, and various parts attached to the plate-like body. A game machine including a game board (for example, game board 6) including the game board, wherein the game board can be exchanged, and controls the progress of the game and transmits an effect control command for controlling electric parts for the effect. The control means (for example, the game control microcomputer 560) and the electric parts for the effect (for example, the

With such a configuration, the effect control means includes an output means for outputting a control signal for controlling the electric parts for the effect in a serial signal system based on the effect control command received from the game control means, Since the serial-parallel conversion circuit and the plurality of frame-side serial-parallel conversion circuits, or the production control means and the plurality of frame-side serial-parallel conversion circuits are configured to be connected via one line of wiring, The number of wires between the game board and the game frame can be reduced. Therefore, in the gaming machine in which the game frame and the game board are detachable, it is possible to easily attach and detach the game frame and the game board .

以下、本発明の実施形態を図面を参照して説明する。

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機を正面からみた正面図である。図2は遊技枠11の前面を示す正面図である。図3は遊技盤の前面を示す正面図である。なお、以下の実施の形態では、パチンコ遊技機を例に説明を行うが、本発明による遊技機はパチンコ遊技機に限られず、スロット機などの他の遊技機に適用することもできる。また、図2には、遊技枠11の前面のうち打球供給皿(上皿)3部分を拡大した図も示されている。

Hereinafter, embodiments of the present invention will be described with reference to the drawings.

First, the overall configuration of a pachinko gaming machine that is an example of a gaming machine will be described. FIG. 1 is a front view of a pachinko gaming machine as viewed from the front. FIG. 2 is a front view showing the front of the

パチンコ遊技機1は、縦長の方形状に形成された外枠(図示せず)と、外枠の内側に開閉可能に取り付けられた遊技枠11とで構成される。また、パチンコ遊技機1は、遊技枠11に開閉可能に設けられている額縁状に形成されたガラス扉枠2を有する。遊技枠11は、外枠に対して開閉自在に設置される前面枠(図示せず)と、機構部品等が取り付けられる機構板と、それらに取り付けられる種々の部品(後述する遊技盤を除く。)とを含む構造体である。

The

図1〜図3に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿(上皿)3がある。打球供給皿3の下部には、打球供給皿3に収容しきれない遊技球を貯留する余剰球受皿4と遊技球を発射する打球操作ハンドル(操作ノブ)5が設けられている。ガラス扉枠2の背面には、図3に示すように、遊技枠11の一部を構成するプラ枠がある。プラ枠は、機構板を含み、機構板に電源回路(図示せず)やスピーカ27などの部品が取り付けられている。また、遊技枠11のプラ枠には、遊技枠11と遊技盤6との間の配線を中継する中継基板607が設けられている。また、遊技枠11の前面枠には、図3に示すように、遊技盤6が着脱可能に取り付けられている。なお、遊技盤6は、それを構成する板状体と、その板状体に取り付けられた種々の部品とを含む構造体である。また、遊技盤6の前面には遊技領域7が形成されている。

As shown in FIGS. 1 to 3, the

遊技領域7の中央付近には、それぞれが演出用の飾り図柄を可変表示する複数の可変表示部を含む可変表示装置(画像表示装置)9が設けられている。可変表示装置9には、例えば「左」、「中」、「右」の3つの可変表示部(図柄表示エリア)がある。可変表示装置9は、特別図柄表示器8による特別図柄の可変表示期間中に、装飾用(演出用)の図柄としての飾り図柄の可変表示を行う。飾り図柄の可変表示を行う可変表示装置9は、演出制御基板に搭載されている演出制御用マイクロコンピュータによって制御される。

Near the center of the

可変表示装置9の下方には、識別情報としての特別図柄を可変表示する特別図柄表示器(特別図柄表示装置)8が設けられている。この実施の形態では、特別図柄表示器8は、例えば00〜99の数字を可変表示可能な簡易で小型の表示器(例えば7セグメントLED)で実現されている。なお、特別図柄表示器8は、2桁の数字を表示するものに限らず、0〜9など他の桁数の数字を可変表示するように構成されていてもよい。また、可変表示装置9は、特別図柄表示器8による特別図柄の可変表示期間中に、装飾用(演出用)の図柄としての飾り図柄の可変表示を行う。

Below the

特別図柄表示器8の右側には、始動入賞口13,14に入った有効入賞球数すなわち保留記憶(始動記憶または始動入賞記憶ともいう。)数を表示する4つの表示器からなる特別図柄保留記憶表示器18が設けられている。有効始動入賞がある毎に、1つの表示器の表示色を変化させる。そして、特別図柄表示器8の可変表示が開始される毎に、1つの表示器の表示色をもとに戻す。なお、可変表示装置9の表示領域内に、保留記憶数を表示する4つの表示領域からなる特別図柄保留記憶表示領域を設けるようにしてもよい。また、この実施の形態では、保留記憶数の上限値を4とするが、上限値をより大きい値にしてもよい。さらに、上限値を、遊技状態に応じて変更可能であるようにしてもよい。

On the right side of the

可変表示装置9の下方には、第1始動入賞口13が設けられている。第1始動入賞口13に入賞した遊技球は、遊技盤6の背面に導かれ、第1始動口スイッチ13aによって検出される。また、可変表示装置9の左側には、第2始動入賞口14を形成する可変入賞装置15が設けられている。第2始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ14aによって検出される。可変入賞球装置15は、ソレノイド16によって開状態にされる。

A first

可変表示装置9の右側には、遊技演出に用いられる可動部材としてのトロッコ151が設けられている。トロッコ151は、遊技演出において、演出制御手段の制御に従って、図4に示すように、可変表示装置9の右側から左側方向に飛び出すような演出を行うことができる。

On the right side of the

また、可変表示装置9の上部および右側には、遊技演出に用いられる可動部材としての梁152が設けられている。梁152は、遊技演出において、演出制御手段の制御に従って、図5に示すように、可変表示装置9の上部および右側から崩れ落ちるような演出を行うことができる。

Further, on the upper and right sides of the

さらに、可変表示装置9の下部には、遊技演出に用いられる可動部材としての骸骨153が設けられている。骸骨153は、遊技演出において、演出制御手段の制御に従って、図6に示すように、口の部分が開閉するような演出を行うことができる。また、骸骨153は、特別可変入賞球装置20を備え、大入賞口を形成している。この実施の形態では、骸骨153は、特定遊技状態(大当り状態)においてソレノイド21によって特別可変入賞球装置20が開放状態に制御されることによって入賞領域となる大入賞口が開放状態になる。大入賞口に入賞した入賞球はカウントスイッチ23で検出される。

Furthermore, a

また、パチンコ遊技機1は、遊技の進行中に遊技者が操作可能な操作ボタン81a〜81eを備えている。例えば、操作ボタン81a〜81eが操作(押下)されると、可動部材としてのトロッコ151や梁152、骸骨153が動作する。

The

ゲート32に遊技球が入賞しゲートスイッチ32aで検出されると、普通図柄表示器10の表示の可変表示が開始される。この実施の形態では、左右のランプ(点灯時に図柄が視認可能になる)が交互に点灯することによって可変表示が行われ、例えば、可変表示の終了時に右側のランプが点灯すれば当りになる。そして、普通図柄表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定回数、所定時間だけ開放状態になる。普通図柄表示器10の下部には、ゲート32に入った入賞球数を表示する4つのLEDによる表示部を有する普通図柄始動記憶表示器41が設けられている。ゲート32への入賞がある毎に、普通図柄始動記憶表示器41は点灯するLEDを1増やす。そして、普通図柄表示器10の可変表示が開始される毎に、点灯するLEDを1減らす。

When a game ball wins the

遊技盤6には、複数の入賞口(普通入賞口)29,30,33,39が設けられ、遊技球の入賞口29,30,33,39への入賞は、それぞれ入賞口スイッチ29a,30a,33a,39aによって検出される。各入賞口29,30,33,39は、遊技媒体を受け入れて入賞を許容する領域として遊技盤6に設けられる入賞領域を構成している。なお、始動入賞口13,14や大入賞口も、遊技媒体を受け入れて入賞を許容する入賞領域を構成する。また、それぞれの入賞口29,30,33,39に入賞した遊技球を1つのスイッチで検出するようにしてもよい。

The

遊技領域7の中央部には、可変表示装置9を囲むように飾り部材154が取り付けられており、飾り部材154の上部には、遊技中に点灯表示したり点滅表示される装飾ランプ(センター飾り用ランプ)が設けられている。なお、この実施の形態では、センター飾り用ランプとして6個のLED125a〜125fが設けられている。また、飾り部材154には、可変表示装置9を囲むように、遊技中に点灯表示したり点滅表示される装飾ランプ(ステージランプ)が設けられている。なお、この実施の形態では、ステージランプとして6個のLED126a〜126fが設けられている。

A

また、遊技領域7の下部には、入賞しなかった遊技球を吸収するアウト口26がある。また、遊技領域7の外側の左右上部には、効果音を発する2つのスピーカ27が設けられている。遊技領域7の外周には、天枠ランプ、左枠ランプおよび右枠ランプが設けられている。さらに、遊技領域7における各構造物の周囲には装飾LEDが設置されている。天枠ランプ、左枠ランプ、右枠ランプおよび装飾用LEDは、遊技機に設けられている装飾発光体の一例である。この実施の形態では、天枠ランプとして12個のLED281a〜281lが設けられている。また、左枠ランプとして6個のLED282a〜282fが設けられている。また、右枠ランプとして6個のLED283a〜283fが設けられている。また、構造物の周囲の装飾LEDとして、骸骨153に1個のLED127aが、特別可変入賞球装置20に2個のLED127b,127cが、操作ボタン81a〜81eに1個のLED83が、打球供給皿3に4個のLED82a〜82dが設けられている。

Further, at the lower part of the

打球発射装置から発射された遊技球は、打球レールを通って遊技領域7に入り、その後、遊技領域7を下りてくる。遊技球が第1始動入賞口13に入り第1始動口スイッチ13aで検出されると、または遊技球が第2始動入賞口14に入り第2始動入賞口スイッチ14aで検出されると、図柄の可変表示を開始できる状態であれば、特別図柄表示器8において特別図柄が可変表示(変動)を始めるとともに、可変表示装置9において飾り図柄が可変表示(変動)を始める。図柄の可変表示を開始できる状態でなければ、始動入賞記憶数を1増やす。

The game balls launched from the hit ball launching device enter the

特別図柄表示器8における特別図柄の可変表示、および可変表示装置9における飾り図柄の可変表示は、一定時間が経過したときに停止する。停止時の特別図柄(停止図柄)が大当り図柄(特定表示結果)であると、大当り遊技状態に移行する。すなわち、大入賞口が、一定時間経過するまで、または、所定個数(例えば10個)の遊技球が入賞するまで開放する。

The variable display of the special symbol on the

遊技球がゲート32に入賞すると、普通図柄表示器10において普通図柄が可変表示される状態になる。また、普通図柄表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定時間だけ開放状態になる。さらに、確変状態では、普通図柄表示器10における停止図柄が当り図柄になる確率が高められるとともに、可変入賞球装置15の開放時間と開放回数が高められる。また、時短状態(特別図柄の可変表示時間が短縮される遊技状態)において、可変入賞球装置15の開放時間と開放回数が高められるようにしてもよい。

When the game ball wins the

上記のように、この実施の形態のパチンコ遊技機1には、発光体としてのランプやLEDが各所に設けられている。さらに、プリペイドカードが挿入されることによって球貸しを可能にするプリペイドカードユニット(以下、単に「カードユニット」ともいう。)が、パチンコ遊技機1に隣接して設置される(図示せず)。

As described above, the

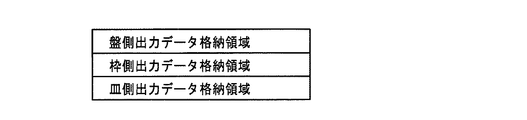

図7は、遊技枠11を開いた状態を示す説明図である。図7に示すように、遊技枠11側の裏面には、ICなどを搭載するための4つの基板(枠側IC基板)602〜605が取り付けられている。遊技枠11の上部に取り付けられた枠側IC基板602は、シリアルデータをパラレルデータに変換するシリアル−パラレル変換IC611,612が搭載されており、各シリアル−パラレル変換IC611,612から、天枠ランプの各LED281a〜281lに制御信号が供給される。また、遊技枠11の右側(裏面から見て左側)に取り付けられた枠側IC基板603は、シリアル−パラレル変換IC613が搭載されており、シリアル−パラレル変換IC613から、右枠ランプの各LED283a〜283fに制御信号が供給される。また、遊技枠11の左側(裏面から見て右側)に取り付けられた枠側IC基板604は、シリアル−パラレル変換IC614が搭載されており、シリアル−パラレル変換IC614から、左枠ランプの各LED282a〜282fに制御信号が供給される。

FIG. 7 is an explanatory diagram showing a state in which the

また、遊技枠11の下部に取り付けられた枠側IC基板605は、シリアル−パラレル変換IC615、およびパラレルデータをシリアルデータに変換する入力IC620が搭載されており、シリアル−パラレル変換IC615から、操作ボタン81a〜81eに設けられた操作ボタンランプのLED83および打球供給皿(上皿)3に設けられた皿ランプの各LED82a〜82dに制御信号が供給される。また、操作ボタン81a〜81eからの検出信号が入力IC620にパラレルに入力される。なお、図7には、枠側IC基板605を横から見た図も示されている。

The frame

なお、図7に示すように、この実施の形態では、各枠側IC基板602〜605のうち遊技枠11の上部に取り付けられた枠側IC基板602は、2つのシリアル−パラレル変換ICを搭載した集合基板として構成されている。そのように構成することによって、シリアル−パラレル変換ICを搭載する基板を集約することができ、遊技機における部品点数を低減することができる。

As shown in FIG. 7, in this embodiment, the frame

また、図7に示すように、遊技枠11側には中継基板607が取り付けられており、中継基板607からの配線は、枠側IC基板604に接続され、枠側IC基板604から枠側IC基板602に接続され、さらに枠側IC基板602から枠側IC基板603に接続される。また、中継基板607からの配線は、枠側基板605に接続される。また、各枠側IC基板602〜604間の配線や、枠側IC基板604,605と中継基板607との間の配線は、図7に示すように、各基板にコネクタ156a〜156hを用いて接続される。なお、図7では、基板に垂直方向に接続するタイプのコネクタを用いて配線接続を行う場合を示しているが、例えば、基板に対して水平方向に接続するタイプのコネクタを用いて配線接続を行うようにしてもよい。

Also, as shown in FIG. 7, a

図7に示すように、中継基板607のコネクタ156aからの配線は、枠側IC基板604のコネクタ156bに接続される。枠側IC基板604の配線パターンは、コネクタ156bからさらに分岐され、一方がシリアル−パラレル変換IC614に接続され、他の一方がコネクタ156cに接続されるようになっている。また、枠側IC基板604において、コネクタ156cは、枠側IC基板602側の端部に配置されている。枠側IC基板604のコネクタ156cからの配線は、枠側IC基板602のコネクタ156dに接続される。枠側IC基板602の配線パターンは、コネクタ156dからさらに3つに分岐され、シリアル−パラレル変換IC611、シリアル−パラレル変換IC612およびコネクタ156eに接続されるようになっている。また、枠側IC基板602において、コネクタ156eは、枠側IC基板603側の端部に配置されている。枠側IC基板602のコネクタ156eからの配線は、枠側IC基板603のコネクタ156fに接続される。枠側IC基板603の配線パターンは、シリアル−パラレル変換IC613に接続されるようになっている。

As shown in FIG. 7, the wiring from the

また、中継基板607のコネクタ156gからの配線は、枠側IC基板605のコネクタ156hに接続される。枠側IC基板605の配線パターンは、コネクタ156hからさらに分岐され、一方がシリアル−パラレル変換IC615に接続され、他の一方が入力IC620に接続されるようになっている。

Further, the wiring from the connector 156g of the

また、図7に示すように、遊技枠11の開放を検出するためのドア開放センサ155が取り付けられている。

Further, as shown in FIG. 7, a

図8は、遊技盤6の裏面を示す説明図である。図8に示すように、遊技盤6の裏面には、ICなどを搭載するための基盤(盤側IC基板)601が取り付けられている。盤側IC基板601には、シリアルデータをパラレルデータに変換する4つのシリアル−パラレル変換IC616〜619が搭載されており、シリアル−パラレル変換IC616から、各可動部材151〜153を駆動するためのモータ151a,152a,153aに制御信号が供給される。また、シリアル−パラレル変換IC617から、センター飾り用ランプの各LED125a〜125fに制御信号が供給される。また、シリアル−パラレル変換IC618から、ステージランプの各LED126a〜126fに制御信号が供給される。また、シリアル−パラレル変換IC619から、可動部材である骸骨153および特別可変入賞球装置20に設けられた各ランプのLED127a〜127bに制御信号が供給される。

FIG. 8 is an explanatory view showing the back surface of the

なお、図8に示すように、この実施の形態では、盤側IC基板601は、4つのシリアル−パラレル変換ICを搭載した集合基板として構成されている。そのように構成することによって、シリアル−パラレル変換ICを搭載する基板を集約することができ、遊技機における部品点数を低減することができる。

As shown in FIG. 8, in this embodiment, the board

また、盤側IC基板601は、パラレルデータをシリアルデータに変換する入力IC621が搭載されており、各可動部材151〜153の位置を検出するための位置センサ151b,152b,153bからの検出信号が入力IC621にパラレルに入力される。

The board

また、図8に示すように、遊技盤6側には中継基板606が取り付けられており、遊技枠11側には中継基板607が設けられている。演出制御手段からの配線は、まず中継基板606に接続され、さらに中継基板607に接続される。そして、中継基板606からの配線は、盤側IC基板601に接続される。また、盤側IC基板601と中継基板606との間の配線や、中継基板606,607間の配線、中継基板606と演出制御手段との間の配線は、図8に示すように、各基板にコネクタ157a〜157eを用いて接続される。なお、コネクタ157a〜157eの接続方法は、図7に示すコネクタ156a〜156hの接続方法と同様である。

As shown in FIG. 8, a

また、各枠側IC基板602〜605に搭載されたシリアル−パラレル変換IC611〜615と、盤側IC基板601に搭載されたシリアル−パラレル変換IC616〜619とを中継する中継基板を設けるようにしてもよい。この場合、中継基板は、遊技枠11側と遊技盤6側とのいずれに配置されていてもよい。

Further, a relay board is provided to relay the serial-

また、演出制御基板80と各枠側IC基板602〜605に搭載されたシリアル−パラレル変換IC611〜615とを中継する中継基板を設けるようにしてもよい。この場合、中継基板は、遊技枠11側と遊技盤6側とのいずれに配置されていてもよい。

Further, a relay board may be provided to relay the

プラ枠の上皿には遊技球を払い出す穴の上側に開口が形成され、開口に中継基板607が設けられる。中継基板607は表裏のコネクタを介して中継する基板であり、プラ枠表側にコネクタ157bが配置され裏側にコネクタ156a,156gが配置されている。また、中継基板607は、遊技盤6が取り付けられる開口の端部に配置される。また、図7に示すように、中継基板607は、遊技盤6が取り付けられる開口の端部の形状に沿うような形状に形成されている。なお、中継基板607は、表側に配置されるコネクタ157bと裏側に配置されるコネクタ156a,156gとの位置が重ならないようにずれた状態とされている。

An opening is formed in the upper plate of the plastic frame above the hole for paying out the game ball, and a

遊技盤6の裏側には中継基板606が設けられる。中継基板606は、図8に示すように、遊技盤6の端部に、プラ枠の中継基板607の近傍に位置するように設けられる。中継基板606はコネクタを介して中継する基板であり、コネクタ157b〜157dが配置されている。また、コネクタ157bは、遊技盤6が搭載する演出制御用マイクロコンピュータ100に接続されている。

A

図9は、主基板(遊技制御基板)31における回路構成の一例を示すブロック図である。なお、図9には、払出制御基板37および演出制御基板80等も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する遊技制御用マイクロコンピュータ(遊技制御手段に相当)560が搭載されている。遊技制御用マイクロコンピュータ560は、ゲーム制御(遊技進行制御)用のプログラム等を記憶するROM54、ワークメモリとして使用される記憶手段としてのRAM55、プログラムに従って制御動作を行うCPU56、I/Oポート部57、およびパラレルデータをシリアルデータに変換して出力するシリアル出力回路を含む。この実施の形態では、ROM54およびRAM55は遊技制御用マイクロコンピュータ560に内蔵されている。すなわち、遊技制御用マイクロコンピュータ560は、1チップマイクロコンピュータである。1チップマイクロコンピュータには、少なくともCPU56のほかRAM55が内蔵されていればよく、ROM54は外付けであっても内蔵されていてもよい。また、I/Oポート部57は、外付けであってもよい。

FIG. 9 is a block diagram illustrating an example of a circuit configuration in the main board (game control board) 31. FIG. 9 also shows the

遊技制御用マイクロコンピュータ560には、さらに、ハードウェア乱数を発生する乱数回路が内蔵されている。 The game control microcomputer 560 further includes a random number circuit for generating hardware random numbers.

なお、遊技制御用マイクロコンピュータ560においてCPU56がROM54に格納されているプログラムに従って制御を実行するので、以下、遊技制御用マイクロコンピュータ560(またはCPU56)が実行する(または、処理を行う)ということは、具体的には、CPU56がプログラムに従って制御を実行することである。このことは、主基板31以外の他の基板に搭載されているマイクロコンピュータについても同様である。

In the game control microcomputer 560, the CPU 56 executes control in accordance with the program stored in the

また、ゲートスイッチ32a、第1始動口スイッチ13a、第2始動口スイッチ14a、カウントスイッチ23、入賞口スイッチ29a,30a,33a,39aからの検出信号を遊技制御用マイクロコンピュータ560に与える入力ドライバ回路58も主基板31に搭載されている。また、可変入賞球装置15を開閉するソレノイド16、および大入賞口を形成する特別可変入賞球装置20を開閉するソレノイド21を遊技制御用マイクロコンピュータ560からの指令に従って駆動する出力回路59も主基板31に搭載されている。

Also, an input driver circuit for supplying detection signals from the

また、遊技制御用マイクロコンピュータ560は、特別図柄を可変表示する特別図柄表示器8、普通図柄を可変表示する普通図柄表示器10、特別図柄保留記憶表示器18および普通図柄保留記憶表示器41の表示制御を行う。

In addition, the game control microcomputer 560 includes a

また、遊技制御用マイクロコンピュータ560が搭載するシリアル出力回路78は、シフトレジスタなどによって構成され、CPU56が出力する演出制御コマンドをシリアルデータに変換して、中継基板77を介して演出制御基板80に送信する。また、シリアル出力回路78は、CPU56が出力する制御信号をシリアルデータに変換して、中継基板77を介して特別図柄表示器8や特別図柄保留記憶表示器18、普通図柄表示器10、普通図柄保留記憶表示器41に出力する。なお、特別図柄表示器8、特別図柄保留記憶表示器18、普通図柄表示器10および普通図柄保留記憶表示器41には、シリアルデータをパラレルデータに変換するシリアル−パラレル変換ICがそれぞれ設けられ、中継基板77からの制御信号をパラレルデータに変換して、特別図柄表示器8や特別図柄保留記憶表示器18、普通図柄表示器10、普通図柄保留記憶表示器41に供給される。

The

なお、大当り遊技状態の発生を示す大当り情報等の情報出力信号をホールコンピュータ等の外部装置に対して出力する情報出力回路(図示せず)も主基板31に搭載されている。

An information output circuit (not shown) that outputs an information output signal such as jackpot information indicating the occurrence of a jackpot gaming state to an external device such as a hall computer is also mounted on the

この実施の形態では、演出制御基板80に搭載されている演出制御手段(演出制御用マイクロコンピュータで構成される。)が、中継基板77を介して遊技制御用マイクロコンピュータ560からの演出制御コマンドをシリアルデータ方式として受信し、飾り図柄を可変表示する可変表示装置9の表示制御を行う。

In this embodiment, the effect control means (configured by the effect control microcomputer) mounted on the

また、演出制御基板80に搭載されている演出制御手段が、遊技盤6に設けられているセンター飾り用ランプ125a〜125fおよびステージランプ126a〜126fの表示制御を行うとともに、枠側に設けられている天枠ランプ281a〜281l、左枠ランプ282a〜282f、および右枠ランプ283a〜283fの表示制御を行い、スピーカ27からの音出力の制御を行う。

Further, the effect control means mounted on the

また、演出制御基板80の演出制御用マイクロコンピュータ100には、演出制御手段が出力する各ランプ125a〜125f,126a〜126f,281a〜281l,282a〜282f,283a〜283fを表示制御するための制御信号をパラレルデータからシリアルデータに変換するシリアル出力回路353が搭載されている。また、演出制御基板80の演出制御用マイクロコンピュータ100には、入力したシリアルデータをパラレルデータに変換して演出制御手段に出力するシリアル入力回路354が搭載されている。したがって、演出制御手段は、シリアル出力回路353を介して制御信号をシリアルデータ方式として出力することによって、各ランプ125a〜125f,126a〜126f,281a〜281l,282a〜282f,283a〜283fの表示制御を行う。

Further, the

また、遊技盤側には、シリアルデータをパラレルデータに変換するためのシリアル−パラレル変換ICが搭載された盤側IC基板601が設けられている。盤側IC基板601は、中継基板606を介して演出制御基板80と接続される。また、遊技枠11側には、シリアルデータをパラレルデータに変換するためのシリアル−パラレル変換ICが搭載された各枠側IC基板602,603,604,605が設けられている。各枠側IC基板602,603,604,605は、中継基板606,607を介して演出制御基板80と接続される。

On the game board side, a board-

なお、図9に示すように、演出制御基板80、中継基板606および中継基板607は、バス型に1系統の配線ルートで接続される。

As shown in FIG. 9, the

図10は、中継基板77および演出制御基板80の回路構成例を示すブロック図である。なお、図10に示す例では、演出制御に関して演出制御基板80のみを設ける場合を示すが、ランプドライバ基板および音声出力基板を設けてもよい。この場合、ランプドライバ基板および音声出力基板には、マイクロコンピュータは搭載されていないが、マイクロコンピュータを搭載してもよい。

FIG. 10 is a block diagram illustrating a circuit configuration example of the

演出制御基板80は、演出制御用CPU101、RAM(図示せず)、シリアル出力回路353、シリアル入力回路354、クロック信号出力部356および入力取込信号出力部357を含む演出制御用マイクロコンピュータ100を搭載している。なお、RAMは外付けであってもよい。演出制御基板80において、演出制御用CPU101は、内蔵または外付けのROM(図示せず)に格納されたプログラムに従って動作し、シリアル入力回路102および入力ポート103を介して演出制御コマンドを受信する。この場合、シリアル入力回路102は、シリアルデータ方式として受信した演出制御コマンドをパラレルデータに変換し出力する。また、演出制御用CPU101は、演出制御コマンドにもとづいて、VDP(ビデオディスプレイプロセッサ)109に可変表示装置9の表示制御を行わせる。

The

この実施の形態では、演出制御用マイクロコンピュータ100と共動して可変表示装置9の表示制御を行うVDP109が演出制御基板80に搭載されている。VDP109は、演出制御用マイクロコンピュータ100とは独立したアドレス空間を有し、そこにVRAMをマッピングする。VRAMは、画像データを展開するためのバッファメモリである。そして、VDP109は、VRAM内の画像データをフレームメモリを介して可変表示装置9に出力する。

In this embodiment, a

演出制御用CPU101は、受信した演出制御コマンドに従ってCGROM(図示せず)から必要なデータを読み出すための指令をVDP109に出力する。CGROMは、可変表示装置9に表示されるキャラクタ画像データや動画像データ、具体的には、人物、文字、図形や記号等(飾り図柄を含む)、および背景画像のデータをあらかじめ格納しておくためのROMである。VDP109は、演出制御用CPU101の指令に応じて、CGROMから画像データを読み出す。そして、VDP109は、読み出した画像データにもとづいて表示制御を実行する。

The

中継基板77には、主基板31から入力された信号を演出制御基板80に向かう方向にしか通過させない(演出制御基板80から中継基板77への方向には信号を通過させない)信号方向規制手段としての単方向性回路74が搭載されている。単方向性回路として、例えばダイオードやトランジスタが使用される。図10には、ダイオードが例示されている。

As a signal direction regulating means, the signal inputted from the

さらに、演出制御用CPU101は、シリアル出力回路353を介してランプを駆動する信号を出力する。シリアル出力回路は、入力したランプのLEDを駆動する信号(パラレルデータ)をシリアルデータに変換して中継基板606に出力する。また、演出制御用CPU101は、音声合成用IC173に対して音番号データを出力する。

Further, the

また、クロック信号出力部356は、クロック信号を中継基板606に出力する。クロック信号出力部356からのクロック信号は、中継基板606,607を介して各枠側IC基板602〜605に搭載されたシリアル−パラレル変換IC611〜615や入力IC620に供給される。また、クロック信号出力部356からのクロック信号は、中継基板606を介して盤側IC基板601に搭載されたシリアル−パラレル変換IC616〜619や入力IC621に供給される。したがって、この実施の形態では、各シリアル−パラレル変換IC611〜619および各入力IC620,621に共通のクロック信号が供給されることになる。

Further, the clock

また、入力取込信号出力部357は、演出制御用CPU101の指示に従って、中継基板606,607を介して、盤側IC基板601または枠側IC基板602〜605に入力取込信号(ラッチ信号)を出力する。枠側IC基板605に搭載された入力IC620は、演出制御用マイクロコンピュータ100からの入力取込信号を入力すると、操作ボタン81a〜81eの検出信号をラッチし、シリアルデータ方式として中継基板606,607を介して演出制御用マイクロコンピュータ100に出力する。また、盤側IC基板601に搭載された入力IC621は、演出制御用マイクロコンピュータ100からの入力取込信号を入力すると、各位置センサ151b,152b,153bの検出信号をラッチし、シリアルデータ方式として中継基板606を介して演出制御用マイクロコンピュータ100に出力する。

Further, the input capture

音声合成用IC173は、音番号データを入力すると、音番号データに応じた音声や効果音を発生し増幅回路175に出力する。増幅回路175は、音声合成用IC173の出力レベルを、ボリューム176で設定されている音量に応じたレベルに増幅した音声信号をスピーカ27に出力する。音声データROM174には、音番号データに応じた制御データが格納されている。音番号データに応じた制御データは、所定期間(例えば飾り図柄の変動期間)における効果音または音声の出力態様を時系列的に示すデータの集まりである。

When the

図11は、演出制御基板80、中継基板606,607、盤側IC基板601、枠側IC基板602,603,604,605の構成例を示すブロック図である。演出制御基板80の演出制御用マイクロコンピュータ100は、制御信号としてのシリアルデータとともに、クロック信号を中継基板607に出力する。また、入力IC620,621に入力信号をラッチさせるための入力取込信号を中継基板606に出力する。

FIG. 11 is a block diagram illustrating a configuration example of the

中継基板606は、演出制御用マイクロコンピュータ100から入力したシリアルデータおよびクロック信号を、盤側IC基板601に搭載された各シリアル−パラレル変換IC616〜619に供給する。そして、各シリアル−パラレル変換IC616〜619は、入力したシリアルデータをパラレルデータに変換して、遊技盤6に設けられた各ランプのLED125a〜125f,126a〜126f,127a〜127cや、各可動部材のモータ151a〜151cに供給する。

The

また、中継基板607は、バス型に1系統の配線ルートで中継基板606と接続されており、各シリアル−パラレル変換IC616〜619に接続されるシリアルデータ線300およびクロック信号線301は、盤側IC基板601上でバス形式に接続されている。なお、バス型に接続とは、1つの配線ルートに複数のシリアル−パラレル変換ICまたは中継基板が接続されていることである。

Further, the

また、盤側IC基板601に搭載された各シリアル−パラレル変換IC616〜619にはそれぞれ固有のIDがある。この実施の形態では、図11に示すように、IC616のIDは06であり、IC617のIDは07であり、IC618のIDは08であり、IC619のIDは09である。

Each serial-

また、盤側IC基板601には、遊技盤6上に設けられた各可動部材の位置センサの検出信号を入力する入力IC621が搭載されている。この実施の形態では、盤側IC基板601に搭載された入力IC621と演出制御用マイクロコンピュータ100とは、中継基板606を介して入力信号線302、クロック信号線301および入力取込信号線303が接続されており、演出制御用マイクロコンピュータ100は、所定のタイミングで、入力取込信号を中継基板606を介して入力IC621に出力する。すると、入力IC621は、入力取込信号(ラッチ信号)にもとづいて各位置センサの検出信号をラッチし、中継基板606を介して演出制御用マイクロコンピュータ100に出力する。この場合、入力IC621は、各位置センサからパラレルに入力した検出信号をシリアルデータに変換して出力する。なお、この実施の形態では、図11に示すように、入力IC621の固有のIDは11である。

In addition, an

中継基板607に入力されたシリアルデータおよびクロック信号は、図11に示すように、各枠側IC基板602〜605に搭載された各シリアル−パラレル変換IC611〜615に供給される。そして、各シリアル−パラレル変換IC611〜615は、入力したシリアルデータをパラレルデータに変換して、遊技枠11に設けられた各ランプのLED281a〜281l,282a〜282f,283a〜283f,82a〜82d,83に供給する。

As shown in FIG. 11, the serial data and the clock signal input to the

また、各シリアル−パラレル変換IC611〜614に接続されるシリアルデータ線およびクロック信号線は、各枠側IC基板602〜604上でバス形式に接続されている。この実施の形態では、図11に示すように、まず、枠側IC基板604のシリアル−パラレル変換IC614に入力され、シリアル−パラレル変換IC614から枠側IC基板602のシリアル−パラレル変換IC611およびシリアル−パラレル変換IC612の順に入力され、さらにシリアル−パラレル変換IC612から枠側IC基板603のシリアル−パラレル変換IC613に入力される。また、シリアル−パラレル変換IC615に接続されるシリアルデータ線およびクロック信号線は、中継基板607から直接接続される。

The serial data lines and clock signal lines connected to the serial-

また、各枠側IC基板602〜605に搭載された各シリアル−パラレル変換IC611〜615にはそれぞれ固有のIDがある。この実施の形態では、図11に示すように、IC611のIDは01であり、IC612のIDは02であり、IC613のIDは03であり、IC614のIDは04であり、IC615のIDは05である。

Each serial-

また、枠側IC基板605には、遊技枠11に設けられた操作ボタン81a〜81eの検出信号を入力する入力IC620が搭載されている。この実施の形態では、枠側IC基板605に搭載された入力IC620と演出制御用マイクロコンピュータ100とは、中継基板606,607を介して入力信号線、クロック信号線および入力取込信号線が接続されており、演出制御用マイクロコンピュータ100は、所定のタイミングで、入力取込信号を中継基板606,607を介して入力IC620に出力する。この場合、演出制御用マイクロコンピュータ100は、入力IC621に入力取込信号を出力するタイミングとは異なるタイミングで、入力取込信号を入力IC620に出力する。すると、入力IC620は、入力取込信号(ラッチ信号)にもとづいて操作ボタン81a〜81eからの検出信号をラッチし、中継基板606,607を介して演出制御用マイクロコンピュータ100に出力する。この場合、入力IC620は、操作ボタン81a〜81eからパラレルに入力した検出信号をシリアルデータに変換して出力する。なお、この実施の形態では、図11に示すように、入力IC620の固有のIDは10である。

In addition, an

盤側IC基板601に搭載されたシリアル−パラレル変換IC616〜619と各枠側IC基板602〜605に搭載されたシリアル−パラレル変換IC611〜615とは、1系統の配線を介して接続されている。1系統の配線を介して接続とは、具体的には、各中継基板606,607がバス型に接続されているとともに、各シリアル−パラレル変換IC611〜619がバス型またはデイジーチェーン型に接続されていることである。なお、この実施の形態では、図11に示すように、各シリアル−パラレル変換IC611〜619はバス型に接続されている。このように、この実施の形態では、盤側IC基板601に搭載された各シリアル−パラレル変換IC616〜619と、各枠側IC基板602〜605に搭載された各シリアル−パラレルIC611〜615とが、中継基板606,607を介してコネクタ156a〜156h,157a〜157eを用いて1系統の配線を介して接続されている。そのため、コネクタの着脱を行うだけで遊技枠11と遊技盤6との配線作業を行うことができ、遊技枠11遊技盤6との着脱作業をさらに容易に行えるようにすることができる。

The serial-

また、この実施の形態によれば、盤側IC基板601に搭載されたシリアル−パラレル変換IC616〜619、枠側IC基板602〜605に搭載されたシリアル−パラレル変換IC611〜615および入力IC620,621に、演出制御用マイクロコンピュータ100から共通のクロック信号を入力する。そのため、シリアル−パラレル変換IC611〜619へのクロック信号の配線と入力IC620,621へのクロック信号の配線とを共通化することができ、演出制御手段と盤側IC601基板との間の通信、および演出制御手段と枠側IC基板602〜605との間の通信を、それぞれ1チャネルを用いて実現することができ、配線数を低減することができる。また、盤側IC基板601に搭載されたシリアル−パラレル変換IC616〜619、枠側IC基板602〜605に搭載されたシリアル−パラレル変換IC611〜615、および入力IC620,621とを容易に同期させることができ、クロック信号用の配線数も低減することができる。

In addition, according to this embodiment, the serial-

この実施の形態では、各シリアル−パラレル変換IC611〜619には、あらかじめアドレスが付与されており、演出制御用マイクロコンピュータ100は、シリアルデータに変換した制御信号を出力する際に、シリアルデータにアドレスを付加して出力する。各シリアル−パラレル変換IC611〜619は、シリアルデータを入力すると、入力したシリアルデータに付加されているアドレスが自分のアドレスに合致するか否かを確認し、合致していればパラレルデータに変換して各ランプのLEDに供給する(すなわち、出力する)。アドレスが合致していなければ各ランプのLEDへの供給は行わない。

In this embodiment, each serial-

なお、図11に示すように、演出制御用マイクロコンピュータ100は、盤側IC基板601および枠側IC基板602〜605と双方向通信を行う(具体的には、シリアルデータを各シリアル−パラレル変換IC611〜619に送信し、入力信号を入力IC620,621から入力する)ものであるので、データ入力端子とデータ出力端子とを備えており、1チャネルでデータ入力とデータ出力とを行うことができる。この実施の形態では、図11に示すように、1つのチャネルのデータ入力端子とデータ出力端子とを、それぞれ異なる出力対象機器(本例では、シリアル−パラレル変換IC611〜619)と入力対象機器(本例では、入力IC620,621)に接続している。そのように構成することによって、本来、出力対象機器と入力対象機器とが別の機器である場合にはそれぞれ別のチャネルを用いて通信を行うべきところを、1つのチャネルのみを用いて双方向通信を可能としており、演出制御用マイクロコンピュータ100と盤側IC基板601および枠側IC基板602〜605との間のチャネル数を低減している。

As shown in FIG. 11, the

この実施の形態において、チャネルとは、データ線(出力データ線)、クロック信号線、入力信号線(入力データ線)、および入力取込信号線(入力データの読出要求の信号線)用の端子をセットにしたものである。なお、1つのチャネルにアース線や電源専用の端子を含んでもよい。また、この実施の形態では、1チャネルを用いてデータ入力とデータ出力の両方を行う場合を示すが、データ線(出力データ線)およびクロック信号線用の端子のみをセットにした出力専用のチャネルを用いてもよい。また、入力信号線(入力データ線)および入力取込信号線(入力データの読出要求の信号線)用の端子のみをセットにした入力専用のチャネルを用いてもよい。 In this embodiment, the channel is a terminal for a data line (output data line), a clock signal line, an input signal line (input data line), and an input take-in signal line (signal line for input data read request). Is a set. One channel may include a ground wire or a terminal dedicated to the power source. Further, in this embodiment, a case where both data input and data output are performed using one channel is shown, but an output-dedicated channel in which only a terminal for a data line (output data line) and a clock signal line is set. May be used. Alternatively, an input-only channel in which only terminals for input signal lines (input data lines) and input take-in signal lines (input data read request signal lines) are set may be used.

図12および図13は、各シリアル−パラレル変換IC611〜619に付与されるアドレスの例を示す説明図である。この実施の形態では、演出制御用マイクロコンピュータ100は、あらかじめRAMに設けられた所定のアドレス記憶領域に、図12および図13に示す各シリアル−パラレル変換IC611〜619のアドレスを記憶している。

12 and 13 are explanatory diagrams showing examples of addresses given to the serial-

この実施の形態では、図12および図13に示すように、各枠側IC基板602〜605に搭載されたシリアル−パラレル変換IC611〜615において、IC611にはアドレス01が付与され、IC612にはアドレス02が付与され、IC613にはアドレス03が付与され、IC614にはアドレス04が付与され、IC615にはアドレス05が付与されている。また、盤側IC基板601に搭載されたシリアル−パラレル変換IC616〜619において、IC616にはアドレス06が付与され、IC617にはアドレス07が付与され、IC618にはアドレス08が付与され、IC619にはアドレス09が付与されている。

In this embodiment, as shown in FIGS. 12 and 13, in the serial-

なお、各シリアル−パラレル変換IC611〜619に、アドレスとしてICの固有のIDと同じものを付与してもよく、ICの固有のIDとは異なる数字や文字、記号を含むアドレスを付与してもよい。

The serial-

また、図12および図13に示すように、アドレスが01であるシリアル−パラレル変換IC611は、シリアルデータをパラレルデータに変換し、遊技枠11の天枠ランプのLED(本例では天枠ランプ281a〜281lのうちのLED6個(281a〜281f))に供給する。また、アドレスが02であるシリアル−パラレル変換IC612は、シリアルデータをパラレルデータに変換し、遊技枠11の天枠ランプのLED(本例では天枠ランプ281a〜281lの他のLED6個(281g〜281l))に供給する。また、アドレスが03であるシリアル−パラレル変換IC613は、シリアルデータをパラレルデータに変換し、遊技枠11の右枠ランプのLED(本例ではLED6個(283a〜283f))に供給する。また、アドレスが04であるシリアル−パラレル変換IC614は、シリアルデータをパラレルデータに変換し、遊技枠11の左枠ランプのLED(本例ではLED6個(282a〜282f))に供給する。

As shown in FIGS. 12 and 13, the serial-

また、アドレスが05であるシリアル−パラレル変換IC615は、シリアルデータをパラレルデータに変換し、遊技枠11の打球供給皿3に設けられた皿ランプ(本例ではLED4個(82a〜82d))に供給するとともに、操作ボタン81a〜81eに設けられた操作ボタンランプ83(本例ではランプ1個)に供給する。

Further, the serial-

また、アドレスが06であるシリアル−パラレル変換IC616は、シリアルデータをパラレルデータに変換し、遊技盤6に設けられた各可動部材(本例では、梁、トロッコおよび骸骨の形状を模した役物)を駆動するためのモータ(本例ではモータ3個(151a,152a,153a)のそれぞれ正方向と逆方向)に供給する。また、アドレスが07であるシリアル−パラレル変換IC617は、シリアルデータをパラレルデータに変換し、遊技盤6中央に設けられた装飾用構造物(センター飾り)の各ランプ(本例ではLED6個(125a〜125f))に供給する。また、アドレスが08であるシリアル−パラレル変換IC618は、シリアルデータをパラレルデータに変換し、可変表示装置9の周囲に設けられた各ステージランプ(本例ではLED6個(126a〜126f))に供給する。また、アドレスが09であるシリアル−パラレル変換IC619は、シリアルデータをパラレルデータに変換し、可動部材(本例では骸骨153)周辺に設けられたランプのLED(本例ではLED3個(127a〜127c))に供給する。

Further, the serial-

また、この実施の形態では、各入力IC620,621にも、あらかじめアドレスが付与されている。図14は、各入力IC620,621に付与されるアドレスの例を示す説明図である。そして、演出制御用マイクロコンピュータ100は、あらかじめRAMに設けられた所定のアドレス記憶領域に、各入力IC620,621のアドレスを記憶している。この実施の形態では、図14に示すように、枠側IC基板605に搭載された入力IC620にはアドレス10が付与され、盤側IC基板601に搭載された入力IC621にはアドレス11が付与されている。

In this embodiment, each

なお、各入力IC620,621に、アドレスとしてICの固有のIDと同じものを付与してもよく、ICの固有のIDとは異なる数字や文字、記号を含むアドレスを付与してもよい。

Each

また、図14に示すように、アドレスが10である入力IC620は、遊技枠11に設けられた操作ボタン81a〜81eの検出信号(操作ボタン81a〜81e自体がオンされたか否か、操作ボタン81a〜81eの上下左右のいずれの部位がオンされたかを示す信号)をパラレルで入力し、シリアルデータに変換して出力する。また、アドレスが11である入力IC621は、遊技盤6の各可動部材に設けられた位置センサ151b,152b,153b(本例では3個)の検出信号をパラレルで入力し、シリアルデータに変換して出力する。

Further, as shown in FIG. 14, the

図15は、各シリアル−パラレル変換IC611〜619の構成を示すブロック図である。図15に示すように、シリアル−パラレル変換IC611〜619は、データラッチ部651、シフトレジスタ652、ヘッダ/アドレス検出部653、データバッファ655およびシンクドライバ656を含む。

FIG. 15 is a block diagram showing the configuration of each serial-parallel conversion IC 611-619. As illustrated in FIG. 15, the serial-

データラッチ部651は、例えばラッチ回路によって構成され、シリアルデータが入力されると、クロック信号のパルスの立ち上がりのタイミングで入力データを1ビット毎にラッチし、シフトレジスタ652に出力する。シフトレジスタ652は、データラッチ部651から1ビットずつ入力されたデータを順に格納する。また、シフトレジスタ652は、クロック信号のパルスの立ち上がりのタイミングで、格納データを1ビットずつシフトする。そのように繰り返し格納データを1ビットずつシフトしていくことによって、最終的にシフトレジスタ652にシリアルデータとして(すなわち、シリアル方式で)入力したデータが格納されることになる。

The data latch

図16は、演出制御用マイクロコンピュータ100から出力されるシリアルデータのフォーマットの例を示す説明図である。図16(A)は、遊技盤6や遊技枠11に設けられた各ランプのLEDを個別に点灯または消灯させるためのランプ点灯データとして出力されるシリアルデータのデータフォーマットである。また、図16(B)は、遊技盤6や遊技枠11に設けられた各ランプのLEDをリセットして全て消灯させるためのリセットコマンドとして出力されるシリアルデータのフォーマットである。

FIG. 16 is an explanatory diagram showing an example of the format of serial data output from the

図16(A)に示すように、ランプ点灯データは、28ビットで構成され、9ビットのヘッダデータ、マークビット(M)、8ビットのアドレス、8ビットのデータおよびエンドビット(E)を含む。 As shown in FIG. 16A, the lamp lighting data is composed of 28 bits, and includes 9-bit header data, mark bits (M), 8-bit addresses, 8-bit data, and end bits (E). .

ヘッダデータは、データの先頭を表すものであり、本例では1FF(h)である。マークビット(M)は、データの区切りを表すビット(本例では論理値0)であり、ヘッダデータとアドレスとの間、およびアドレスとデータとの間にそれぞれ挿入される。アドレスは、データ出力先のシリアル−パラレル変換ICのアドレスである。なお、アドレスとして、各シリアル−パラレル変換IC611〜619の固有の通し番号であるIDを用いてもよい。

The header data represents the head of the data, and is 1FF (h) in this example. The mark bit (M) is a bit (

データ(8ビット)は、各ランプのLEDの点灯状態を制御するためのものであり、例えば、点灯対象のランプのLEDに対応するビットとして論理値1を含み、非点灯対象のランプのLEDに対応するビットとして論理値0を含む。エンドビット(E)は、データの終了を示すものであり、本例では論理値0である。

The data (8 bits) is for controlling the lighting state of the LED of each lamp, and includes, for example, a

図16(B)に示すように、リセットコマンドは、19ビットで構成され、9ビットのヘッダデータ、マークビット(M)、8ビットのリセットデータおよびエンドビット(E)を含む。 As shown in FIG. 16B, the reset command is composed of 19 bits and includes 9-bit header data, mark bits (M), 8-bit reset data, and end bits (E).

ヘッダデータは、データの先頭を表すものであり、本例では1FF(h)である。マークビット(M)は、データの区切りを表すビット(本例では論理値0)であり、ヘッダデータとリセットデータとの間に挿入される。リセットデータは、各ランプのLEDの点灯状態をリセットして全て消灯させるためのものであり、例えば、全て論路値1を含むデータである。エンドビット(E)は、データの終了を示すものであり、本例では論理値0である。

The header data represents the head of the data, and is 1FF (h) in this example. The mark bit (M) is a bit (

この実施の形態では、図16(A)に示すランプ点灯データまたは図16(B)に示すリセットコマンドが入力され、クロック信号のパルスの立ち上がりのタイミングで、ビット単位で繰り返しシフトされてシフトレジスタ652に格納されることになる。

In this embodiment, the lamp lighting data shown in FIG. 16A or the reset command shown in FIG. 16B is input, and the

ヘッダ/アドレス検出部653は、シフトレジスタ652の格納データからヘッダおよびアドレスを検出する。まず、ヘッダ/アドレス検出部653は、シフトレジスタ652からのデータを常時検出し、検出したデータの内容がヘッダデータに相当する1FF(h)と一致するか否かを確認する。ヘッダデータ(1FF(h))と一致すれば、そのヘッダデータと一致した箇所をデータの先頭と判断し、シフトレジスタ652に1セットのランプ点灯データまたはリセットコマンドが格納されたと判断する。次いで、ヘッダ/アドレス検出部653は、シフトレジスタ652からアドレスに相当する先頭から11ビット目〜18ビット目のデータを検出し、そのシリアル−パラレル変換ICにあらかじめ付与されたアドレスと一致するか否かを確認する。盤側IC基板601および各枠側IC基板602〜605には、例えば、それぞれ搭載するシリアル−パラレル変換ICのアドレスを格納したアドレス格納レジスタ654が設けられており、ヘッダ/アドレス検出部653は、シフトレジスタ652から検出したアドレスが、あらかじめアドレス格納レジスタ654に格納するアドレスと一致するか否かを確認すればよい。アドレスが一致すれば、ヘッダ/アドレス検出653は、そのシリアル−パラレル変換ICを宛先とするデータを入力したと判定し、入力取込信号(ラッチ信号)をデータバッファ655に出力する。アドレスが一致しなければ、ヘッダ/アドレス検出653は、入力取込信号をデータバッファ655に出力しない。すなわち、この場合、そのシリアル−パラレル変換ICを宛先とするデータではないので、シフトレジスタ652に格納したデータをデータバッファ655に出力することなく、そのまま破棄することになる。

The header /

なお、図15では、盤側IC基板601および各枠側IC基板602〜605にあらかじめアドレス格納レジスタ654が設けられている場合を示しているが、アドレス格納レジスタ654に代えて、シリアル−パラレル変換ICに設けられているアドレス端子(8端子(8ビットのアドレスの各ビットにそれぞれ対応する))を介して、外部のハードウェア回路(例えば、演出制御基板80が搭載する回路)からアドレスを入力するようにしてもよい。そして、外部のハードウェア回路側から、各アドレス端子の入力をhighまたはlowに制御することによって、シリアル−パラレル変換ICにアドレスを入力してもよい。この場合、例えば、外部のハードウェア回路は、アドレスのいずれかのビットに対応する端子に電圧をかけることによってその端子に対する入力をhighとし、またはグランドにスイッチングすることによってその端子に対する入力をLowとするように制御する。

15 shows a case where the

データバッファ655は、例えば、ラッチレジスタによって構成され、ヘッダ/アドレス検出部653から入力取込信号を入力すると、シフトレジスタ652からデータ部分に相当する先頭から20ビット目〜27ビット目のデータを取り込んでラッチする。そして、データバッファ655は、取り込んだデータをパラレルデータ(Q0〜Q7)として各ランプのLEDに供給(すなわち、出力)することになる。

The

なお、シフトレジスタ652が格納したデータがリセットコマンドであった場合には、先頭から11ビット目〜18ビット目が全て論理値1のデータを格納することになる。この場合、データバッファ655は全ての論理値が1であるデータを取り込んだ場合にはリセットコマンドを入力したと判断し、全てのランプのLEDがリセットされ消灯されることになる。

If the data stored in the

シンクドライバ656は、所定の論理反転設定信号にもとづいて、データバッファ655が出力するパラレルデータの論理値を反転して出力したり、そのまま出力したりする。例えば、所定の論理反転設定信号がHighである場合には、データバッファ655が出力するパラレルデータのビット値が1である(すなわち、ランプ点灯データの対応するビット値が1)ときにオンとなり、各ランプのLEDにオン信号を出力する。この実施の形態では、あらかじめ論理反転設定信号の設定値が盤側IC基板601や各枠側IC基板602〜605に設けられたレジスタなどに設定されており、あらかじめ設定された設定値に従って各ランプのLEDにオン信号が出力され、各ランプのLEDが点灯するものとする。

The sync driver 656 inverts and outputs the logical value of the parallel data output from the

図17は、シリアル−パラレル変換ICへのシリアルデータおよびクロック信号の入力タイミングと、パラレルデータの出力タイミングとの例を示すタイミング図である。なお、図17では、シリアルデータ方式としてランプ点灯データを入力する場合を説明する。図17に示すように、シリアルデータは、ヘッダデータ、マークビット、アドレス、マークビット、データ、エンドビットの順に、シリアル−パラレル変換ICのシフトレジスタ652に1ビット単位で入力される。そして、この一連のデータを1セットとする。1セットのシリアルデータ(本例ではランプ点灯データ)が全て入力され終わるまで、ヘッダ/アドレス検出部653ではヘッダデータが検出されないので、データバッファ655の出力は変化しない。そのため、シリアル−パラレル変換ICからは、前回受信したシリアルデータにもとづく点灯パターンがそのままパラレルデータ方式として出力されている。

FIG. 17 is a timing diagram showing an example of the input timing of serial data and clock signals to the serial-parallel conversion IC and the output timing of parallel data. In FIG. 17, a case where lamp lighting data is input as a serial data method will be described. As shown in FIG. 17, the serial data is input to the

1セットのシリアルデータが全て入力され終わると、シフトレジスタ652の格納データからデータ部分がデータバッファ655にラッチされ、新たに受信したシリアルデータにもとづく点灯パターンがパラレルデータ方式として出力される。なお、この実施の形態では、図17に示すように、シリアル−パラレル変換ICが出力するパラレルデータのうち、Q0,Q4は、シリアルデータ入力完了後の次のクロック信号のパルスの立ち上がりのタイミングで、直ちに新たな点灯パターンのデータに切り替わる。また、Q1,Q5は、Q0,Q4より1クロック分遅れて新たな点灯パターンのデータに切り替わる。また、Q2,Q6は、Q0,Q4より2クロック分遅れて新たな点灯パターンのデータに切り替わる。さらに、Q3,Q7は、Q0,Q4より3クロック分遅れて新たな点灯パターンのデータに切り替わる。

When all sets of serial data have been input, the data portion from the data stored in the

図18は、各入力IC620,621の構成を示すブロック図である。図18に示すように、この実施の形態では、各入力IC620,621は、複数(本例では8個)のDフリップフロップ661〜668によって構成される。この実施の形態では、操作ボタン81a〜81eまたは各位置センサ151b,152b,153bからの検出信号が各入力IC620,621にパラレルに入力され、検出信号ごとにいずれかのDフリップフロップ661〜668に入力される。また、各Dフリップフロップ661〜668にはクロック信号が入力され、各Dフリップフロップ661〜668は、クロックの立ち上がりで順次シフト動作を行う。そして、パラレルに入力した検出信号をシリアルデータに変換して出力することになる。

FIG. 18 is a block diagram illustrating the configuration of each of the

各Dフリップフロップ661〜668には、演出制御用マイクロコンピュータ100から所定のタイミングで入力取込信号(ラッチ信号)が入力される。入力取込信号が入力されると、操作ボタン81a〜81eまたは各位置センサ151b,152b,153bから検出信号が、各Dフリップフロップ661〜668にラッチされる。そして、ラッチされた検出信号は、クロックの立ち上がりで順次シフトされ、シリアルデータ方式として出力される。

An input capture signal (latch signal) is input to each of the D flip-flops 661 to 668 from the

次に、遊技機の動作について説明する。図19は、主基板31における遊技制御用マイクロコンピュータ560が実行するメイン処理を示すフローチャートである。遊技機に対して電源が投入され電力供給が開始されると、リセット信号が入力されるリセット端子の入力レベルがハイレベルになり、遊技制御用マイクロコンピュータ560(具体的には、CPU56)は、プログラムの内容が正当か否か確認するための処理であるセキュリティチェック処理を実行した後、ステップS1以降のメイン処理を開始する。メイン処理において、CPU56は、まず、必要な初期設定を行う。

Next, the operation of the gaming machine will be described. FIG. 19 is a flowchart showing main processing executed by the game control microcomputer 560 on the

初期設定処理において、CPU56は、まず、割込禁止に設定する(ステップS1)。次に、割込モードを割込モード2に設定し(ステップS2)、スタックポインタにスタックポインタ指定アドレスを設定する(ステップS3)。そして、内蔵デバイスの初期化(内蔵デバイス(内蔵周辺回路)であるCTC(カウンタ/タイマ)およびPIO(パラレル入出力ポート)の初期化など)を行った後(ステップS4)、RAMをアクセス可能状態に設定する(ステップS5)。なお、割込モード2は、CPU56が内蔵する特定レジスタ(Iレジスタ)の値(1バイト)と内蔵デバイスが出力する割込ベクタ(1バイト:最下位ビット0)とから合成されるアドレスが、割込番地を示すモードである。

In the initial setting process, the CPU 56 first sets the interrupt prohibition (step S1). Next, the interrupt mode is set to interrupt mode 2 (step S2), and a stack pointer designation address is set to the stack pointer (step S3). After initialization of the built-in device (CTC (counter / timer) and PIO (parallel input / output port), which are built-in devices (built-in peripheral circuits)) is performed (step S4), the RAM is accessible (Step S5). In the interrupt

次いで、CPU56は、入力ポートを介して入力されるクリアスイッチ(例えば、電源基板に搭載されている。)の出力信号の状態を確認する(ステップS6)。その確認においてオンを検出した場合には、CPU56は、通常の初期化処理を実行する(ステップS10〜S15。S44,S45を含む。)。 Next, the CPU 56 checks the state of the output signal of the clear switch (for example, mounted on the power supply board) input via the input port (step S6). When the ON is detected in the confirmation, the CPU 56 executes a normal initialization process (steps S10 to S15, including S44 and S45).

クリアスイッチがオンの状態でない場合には、遊技機への電力供給が停止したときにバックアップRAM領域のデータ保護処理(例えばパリティデータの付加等の電力供給停止時処理)が行われたか否か確認する(ステップS7)。そのような保護処理が行われていないことを確認したら、CPU56は初期化処理を実行する。バックアップRAM領域にバックアップデータがあるか否かは、例えば、電力供給停止時処理においてバックアップRAM領域に設定されるバックアップフラグの状態によって確認される。 If the clear switch is not on, check whether data protection processing of the backup RAM area (for example, power supply stop processing such as addition of parity data) was performed when power supply to the gaming machine was stopped (Step S7). When it is confirmed that such protection processing is not performed, the CPU 56 executes initialization processing. Whether there is backup data in the backup RAM area is confirmed, for example, by the state of the backup flag set in the backup RAM area in the power supply stop process.

電力供給停止時処理が行われたことを確認したら、CPU56は、バックアップRAM領域のデータチェックを行う(ステップS8)。この実施の形態では、データチェックとしてパリティチェックを行う。よって、ステップS8では、算出したチェックサムと、電力供給停止時処理で同一の処理によって算出され保存されているチェックサムとを比較する。不測の停電等の電力供給停止が生じた後に復旧した場合には、バックアップRAM領域のデータは保存されているはずであるから、チェック結果(比較結果)は正常(一致)になる。チェック結果が正常でないということは、バックアップRAM領域のデータが、電力供給停止時のデータとは異なっていることを意味する。そのような場合には、内部状態を電力供給停止時の状態に戻すことができないので、電力供給の停止からの復旧時でない電源投入時に実行される初期化処理を実行する。 When it is confirmed that the power supply stop process has been performed, the CPU 56 performs data check of the backup RAM area (step S8). In this embodiment, a parity check is performed as a data check. Therefore, in step S8, the calculated checksum is compared with the checksum calculated and stored by the same process in the power supply stop process. When the power supply is stopped after an unexpected power failure or the like, the data in the backup RAM area should be saved, so the check result (comparison result) is normal (matched). That the check result is not normal means that the data in the backup RAM area is different from the data when the power supply is stopped. In such a case, since the internal state cannot be returned to the state when the power supply is stopped, an initialization process that is executed when the power is turned on is not performed when the power supply is stopped.

チェック結果が正常であれば、CPU56は、遊技制御手段の内部状態と演出制御手段等の電気部品制御手段の制御状態を電力供給停止時の状態に戻すための遊技状態復旧処理(ステップS41〜S43の処理)を行う。具体的には、ROM54に格納されているバックアップ時設定テーブルの先頭アドレスをポインタに設定し(ステップS41)、バックアップ時設定テーブルの内容を順次作業領域(RAM55内の領域)に設定する(ステップS42)。作業領域はバックアップ電源によって電源バックアップされている。バックアップ時設定テーブルには、作業領域のうち初期化してもよい領域についての初期化データが設定されている。ステップS41およびS42の処理によって、作業領域のうち初期化してはならない部分については、保存されていた内容がそのまま残る。初期化してはならない部分とは、例えば、電力供給停止前の遊技状態を示すデータ(特別図柄プロセスフラグ、確変フラグ、時短フラグなど)、出力ポートの出力状態が保存されている領域(出力ポートバッファ)、未払出賞球数を示すデータが設定されている部分などである。

If the check result is normal, the CPU 56 recovers the game state restoration process (steps S41 to S43) for returning the internal state of the game control means and the control state of the electrical component control means such as the effect control means to the state when the power supply is stopped. Process). Specifically, the start address of the backup setting table stored in the

また、CPU56は、電力供給復旧時の初期化コマンドとしての停電復旧指定コマンドを送信する(ステップS43)。そして、ステップS14に移行する。 Further, the CPU 56 transmits a power failure recovery designation command as an initialization command at the time of power supply recovery (step S43). Then, the process proceeds to step S14.

なお、この実施の形態では、バックアップフラグとチェックデータとの双方を用いてバックアップRAM領域のデータが保存されているか否か確認しているが、いずれか一方のみを用いてもよい。すなわち、バックアップフラグとチェックデータとのいずれかを、遊技状態復旧処理を実行するための契機としてもよい。 In this embodiment, it is confirmed whether the data in the backup RAM area is stored using both the backup flag and the check data. However, only one of them may be used. That is, either the backup flag or the check data may be used as an opportunity for executing the game state restoration process.

初期化処理では、CPU56は、まず、RAMクリア処理を行う(ステップS10)。なお、RAMクリア処理によって、所定のデータ(例えば大当り判定用乱数を生成するためのカウンタのカウント値のデータ)は0に初期化されるが、任意の値またはあらかじめ決められている値に初期化するようにしてもよい。また、RAM55の全領域を初期化せず、所定のデータ(例えば大当り判定用乱数を生成するためのカウンタのカウント値のデータ)をそのままにしてもよい。また、ROM54に格納されている初期化時設定テーブルの先頭アドレスをポインタに設定し(ステップS11)、初期化時設定テーブルの内容を順次作業領域に設定する(ステップS12)。

In the initialization process, the CPU 56 first performs a RAM clear process (step S10). The RAM clear process initializes predetermined data (for example, count value data of a counter for generating a big hit determination random number) to 0, but is initialized to an arbitrary value or a predetermined value. You may make it do. Alternatively, the entire area of the

ステップS11およびS12の処理によって、例えば、普通図柄判定用乱数カウンタ、普通図柄判定用バッファ、特別図柄バッファ、総賞球数格納バッファ、特別図柄プロセスフラグ、賞球中フラグ、球切れフラグ、払出停止フラグなど制御状態に応じて選択的に処理を行うためのフラグに初期値が設定される。 By the processing of steps S11 and S12, for example, a normal symbol determination random number counter, a normal symbol determination buffer, a special symbol buffer, a total prize ball number storage buffer, a special symbol process flag, an award ball flag, a ball out flag, and a payout stop An initial value is set to a flag such as a flag for selectively performing processing according to the control state.

また、CPU56は、サブ基板(主基板31以外のマイクロコンピュータが搭載された基板。)を初期化するための初期化指定コマンド(遊技制御用マイクロコンピュータ560が初期化処理を実行したことを示すコマンドでもある。)をサブ基板に送信する(ステップS13)。例えば、演出制御用マイクロコンピュータ100は、初期化指定コマンドを受信すると、可変表示装置9において、遊技機の制御の初期化がなされたことを報知するための画面表示、すなわち初期化報知を行う。

Further, the CPU 56 initializes a sub board (a board on which a microcomputer other than the

さらに、CPU56は、異常報知禁止フラグをセットするとともに(ステップS44)、禁止期間タイマに禁止期間値に相当する値を設定する(ステップS45)。禁止期間値は、後述する異常入賞の報知を禁止する期間を示す値である。また、異常報知禁止フラグは、異常入賞の報知が禁止されていることを示すフラグであり、禁止期間タイマがタイムアウトするまでセット状態に維持される。よって、可変表示装置9において初期化報知が開始されてから所定期間は、異常入賞の報知の開始が禁止される。

Further, the CPU 56 sets an abnormality notification prohibition flag (step S44) and sets a value corresponding to the prohibition period value in the prohibition period timer (step S45). The prohibition period value is a value indicating a period during which an abnormal winning notification described later is prohibited. The abnormality notification prohibition flag is a flag indicating that notification of an abnormal winning is prohibited, and is maintained in the set state until the prohibition period timer times out. Therefore, the start of the abnormal winning notification is prohibited for a predetermined period after the initialization notification is started in the

また、CPU56は、乱数回路を初期設定する乱数回路設定処理を実行する(ステップS14)。CPU56は、例えば、乱数回路設定プログラムに従って処理を実行することによって、乱数回路にランダムRの値を更新させるための設定を行う。また、乱数回路設定処理では、CPU56は、乱数回路の状態を確認する乱数回路確認処理も実行する。乱数回路確認処理では、CPU56は、乱数回路が出力する乱数確認信号を所定時間監視する。乱数確認信号は、乱数回路が内蔵するクロック信号発生回路が内部クロック信号を正常に出力している場合にはオン状態であり、そうでなければ(例えば、内部クロック信号のレベルが低下した場合には)オフ状態になる。CPU56は、所定時間継続して乱数確認信号のオフ状態を検出した場合には、遊技制御用マイクロコンピュータ560が内蔵する乱数回路に異常が発生したと判定し、主基板31の乱数回路エラーを報知することを指定する乱数回路エラー指定コマンドをサブ基板に送信する処理を実行する。所定時間継続して乱数確認信号のオフ状態を検出しなければ、CPU56は、乱数回路が正常に動作していると判定して、そのままステップS15に移行する。

Further, the CPU 56 executes random number circuit setting processing for initial setting of the random number circuit (step S14). For example, the CPU 56 performs setting according to the random number circuit setting program so as to cause the random number circuit to update the value of the random R. In the random number circuit setting process, the CPU 56 also executes a random number circuit confirmation process for confirming the state of the random number circuit. In the random number circuit confirmation process, the CPU 56 monitors a random number confirmation signal output from the random number circuit for a predetermined time. The random number confirmation signal is ON when the clock signal generation circuit built in the random number circuit normally outputs the internal clock signal, and otherwise (for example, when the level of the internal clock signal decreases) Will be off). If the CPU 56 detects the OFF state of the random number confirmation signal continuously for a predetermined time, the CPU 56 determines that an abnormality has occurred in the random number circuit built in the game control microcomputer 560 and notifies the random circuit error of the

そして、ステップS15において、CPU56は、所定時間(例えば2ms)毎に定期的にタイマ割込がかかるように遊技制御用マイクロコンピュータ560に内蔵されているCTCのレジスタの設定を行なう。すなわち、初期値として例えば2msに相当する値が所定のレジスタ(時間定数レジスタ)に設定される。この実施の形態では、2ms毎に定期的にタイマ割込がかかるとする。 In step S15, the CPU 56 sets a register of the CTC built in the game control microcomputer 560 so that a timer interrupt is periodically taken every predetermined time (for example, 2 ms). That is, a value corresponding to, for example, 2 ms is set in a predetermined register (time constant register) as an initial value. In this embodiment, it is assumed that a timer interrupt is periodically taken every 2 ms.

初期化処理の実行(ステップS10〜S15)が完了すると、CPU56は、メイン処理で、表示用乱数更新処理(ステップS17)および初期値用乱数更新処理(ステップS18)を繰り返し実行する。表示用乱数更新処理および初期値用乱数更新処理を実行するときには割込禁止状態に設定し(ステップS16)、表示用乱数更新処理および初期値用乱数更新処理の実行が終了すると割込許可状態に設定する(ステップS19)。この実施の形態では、表示用乱数とは、変動パターンを決定するための乱数であり、表示用乱数更新処理とは、表示用乱数を発生するためのカウンタのカウント値を更新する処理である。また、初期値用乱数更新処理とは、初期値用乱数を発生するためのカウンタのカウント値を更新する処理である。この実施の形態では、初期値用乱数とは、普通図柄に関して当りとするか否か決定するための乱数を発生するためのカウンタ(普通図柄当り判定用乱数発生カウンタ)等の、カウント値の初期値を決定するための乱数である。後述する遊技の進行を制御する遊技制御処理(遊技制御用マイクロコンピュータ560が、遊技機に設けられている可変表示装置、可変入賞球装置、球払出装置等の遊技用の装置を、自身で制御する処理、または他のマイクロコンピュータに制御させるために指令信号を送信する処理、遊技装置制御処理ともいう)において、普通図柄当り判定用乱数のカウント値が1周(普通図柄当り判定用乱数の取りうる値の最小値から最大値までの間の数値の個数分歩進したこと)すると、そのカウンタに初期値が設定される。 When the execution of the initialization process (steps S10 to S15) is completed, the CPU 56 repeatedly executes the display random number update process (step S17) and the initial value random number update process (step S18) in the main process. When executing the display random number update process and the initial value random number update process, the interrupt disabled state is set (step S16). When the display random number update process and the initial value random number update process are finished, the interrupt enabled state is set. Set (step S19). In this embodiment, the display random number is a random number for determining the variation pattern, and the display random number update process is a process for updating the count value of the counter for generating the display random number. The initial value random number update process is a process for updating the count value of the counter for generating the initial value random number. In this embodiment, the initial value random number is an initial count value such as a counter for generating a random number for determining whether or not to win a normal symbol (ordinary random number generation counter for normal symbol determination). It is a random number for determining the value. A game control process for controlling the progress of the game, which will be described later (the game control microcomputer 560 controls game devices such as a variable display device, a variable winning ball device, a ball payout device, etc. provided in the game machine itself. In the process of transmitting a command signal to be controlled by another microcomputer, or a game machine control process), the count value of the random number for determination per normal symbol is one round (the random number for determination per normal symbol is taken). When the value is incremented by the number of values between the minimum value and the maximum value of the possible values), an initial value is set in the counter.

タイマ割込が発生すると、CPU56は、図20に示すステップS20〜S36のタイマ割込処理を実行する。タイマ割込処理において、まず、電源断信号が出力されたか否か(オン状態になったか否か)を検出する電源断検出処理を実行する(ステップS20)。電源断信号は、例えば電源基板に搭載されている電圧低下監視回路が、遊技機に供給される電源の電圧の低下を検出した場合に出力する。そして、電源断検出処理において、CPU56は、電源断信号が出力されたことを検出したら、必要なデータをバックアップRAM領域に保存するための電力供給停止時処理を実行する。次いで、入力ドライバ回路58を介して、ゲートスイッチ32a、第1始動口スイッチ13a、第2始動口スイッチ14a、カウントスイッチ23、および入賞口スイッチ29a,30a,33a,39aの検出信号を入力し、それらの状態判定を行う(スイッチ処理:ステップS21)。

When the timer interrupt occurs, the CPU 56 executes the timer interrupt process in steps S20 to S36 shown in FIG. In the timer interrupt process, first, a power-off detection process for detecting whether or not a power-off signal is output (whether or not an on-state is turned on) is executed (step S20). The power-off signal is output when, for example, a voltage drop monitoring circuit mounted on the power supply board detects a drop in the voltage of the power supplied to the gaming machine. In the power-off detection process, when detecting that the power-off signal has been output, the CPU 56 executes a power supply stop process for saving necessary data in the backup RAM area. Next, detection signals from the

次に、CPU56は、特別図柄表示器8、普通図柄表示器10、特別図柄保留記憶表示器18、普通図柄保留記憶表示器41の表示制御を行う表示制御処理を実行する(ステップS22)。特別図柄表示器8および普通図柄表示器10については、ステップS34,S35で設定される出力バッファの内容に応じて各表示器に対して駆動信号を出力する制御を実行する。

Next, the CPU 56 executes display control processing for performing display control of the

また、CPU56は、正規の時期以外の時期において大入賞口に遊技球が入賞したことを検出した場合に異常入賞の報知を行わせるための処理を行う(ステップS23:異常入賞報知処理)。 Further, the CPU 56 performs a process for notifying an abnormal winning when it detects that a game ball has won a prize winning opening at a time other than the regular time (step S23: abnormal winning notifying process).

次に、遊技制御に用いられる大当り図柄決定用の乱数等の各判定用乱数を生成するための各カウンタのカウント値を更新する処理を行う(判定用乱数更新処理:ステップS24)。CPU56は、さらに、初期値用乱数および表示用乱数を生成するためのカウンタのカウント値を更新する処理を行う(初期値用乱数更新処理,表示用乱数更新処理:ステップS25,S26)。 Next, a process of updating the count value of each counter for generating each random number for determination such as a random number for determining jackpot symbols used for game control is performed (determination random number update process: step S24). The CPU 56 further performs a process of updating the count value of the counter for generating the initial value random number and the display random number (initial value random number update process, display random number update process: steps S25 and S26).

図21は、各乱数を示す説明図である。各乱数は、以下のように使用される。

(1)ランダム1:特別図柄のはずれ図柄(停止図柄)を決定する(はずれ図柄決定用)

(2)ランダム2:大当りを発生させるときの特別図柄の停止図柄を決定する(大当り図柄決定用)

(3)ランダム3:特別図柄の変動パターン(変動時間)を決定する(変動パターン決定用)

(4)ランダム4:普通図柄にもとづく当りを発生させるか否か決定する(普通図柄当り判定用)

(5)ランダム5:ランダム4の初期値を決定する(ランダム4初期値決定用)

FIG. 21 is an explanatory diagram showing each random number. Each random number is used as follows.

(1) Random 1: Decide a special symbol's off symbol (stop symbol) (for determining off symbol)

(2) Random 2: Determines the special symbol stop symbol when generating a big hit (for big hit symbol determination)

(3) Random 3: Determine the variation pattern (variation time) of special symbols (for variation pattern determination)

(4) Random 4: Determines whether or not to generate a hit based on the normal symbol (for normal symbol hit determination)

(5) Random 5:

図20に示された遊技制御処理におけるステップS24では、遊技制御用マイクロコンピュータ560は、(2)の大当り図柄決定用乱数、および(4)の普通図柄当り判定用乱数を生成するためのカウンタのカウントアップ(1加算)を行う。すなわち、それらが判定用乱数であり、それら以外の乱数が表示用乱数または初期値用乱数である。なお、遊技効果を高めるために、上記(1)〜(5)の乱数以外の乱数も用いるようにしてもよい。また、この実施の形態では、大当り判定用乱数は遊技制御用マイクロコンピュータ560に内蔵されたハードウェア(乱数回路)が生成する乱数であるが、大当り判定用乱数として、遊技制御用マイクロコンピュータ560によってプログラムにもとづいて生成されるソフトウェア乱数を用いてもよい。 In step S24 in the game control process shown in FIG. 20, the game control microcomputer 560 uses a counter for generating the jackpot symbol determination random number (2) and the random number for determination per regular symbol (4). Count up (add 1). That is, they are determination random numbers, and other random numbers are display random numbers or initial value random numbers. In addition, in order to improve a game effect, you may make it use random numbers other than the random number of said (1)-(5). In this embodiment, the big hit determination random number is a random number generated by the hardware (random number circuit) built in the game control microcomputer 560. However, the big hit determination random number is generated by the game control microcomputer 560 as the big hit determination random number. Software random numbers generated based on a program may be used.

さらに、CPU56は、特別図柄プロセス処理を行う(ステップS27)。特別図柄プロセス処理では、特別図柄表示器8および大入賞口を所定の順序で制御するための特別図柄プロセスフラグに従って該当する処理を実行する。CPU56は、特別図柄プロセスフラグの値を、遊技状態に応じて更新する。

Further, the CPU 56 performs special symbol process processing (step S27). In the special symbol process, the corresponding symbol is executed in accordance with a special symbol process flag for controlling the

次いで、普通図柄プロセス処理を行う(ステップS28)。普通図柄プロセス処理では、CPU56は、普通図柄表示器10の表示状態を所定の順序で制御するための普通図柄プロセスフラグに従って該当する処理を実行する。CPU56は、普通図柄プロセスフラグの値を、遊技状態に応じて更新する。

Next, normal symbol process processing is performed (step S28). In the normal symbol process, the CPU 56 executes a corresponding process according to the normal symbol process flag for controlling the display state of the

また、CPU56は、演出制御用マイクロコンピュータ100に演出制御コマンドを送出する処理を行う(演出制御コマンド制御処理:ステップS29)。なお、この実施の形態では、ステップS29において、遊技制御用マイクロコンピュータ560は、演出制御コマンドを構成するMODEデータまたはEXTデータ(送信先のシリアル−パラレル変換IC611〜619のアドレスが付加されたMODEデータまたはEXTデータ)に、ヘッダデータやマークビット、エンドビットを付加して送信制御を行う。そして、演出制御コマンドは、シリアル出力回路78によってシリアルデータに変換され、中継基板77を介して演出制御基板80に送信される。

Further, the CPU 56 performs a process of sending an effect control command to the effect control microcomputer 100 (effect control command control process: step S29). In this embodiment, in step S29, the game control microcomputer 560 causes the MODE data or EXT data (MODE data to which the addresses of the destination serial-

さらに、CPU56は、例えばホール管理用コンピュータに供給される大当り情報、始動情報、確率変動情報などのデータを出力する情報出力処理を行う(ステップS30)。 Further, the CPU 56 performs information output processing for outputting data such as jackpot information, start information, probability variation information supplied to the hall management computer, for example (step S30).

また、CPU56は、第1始動口スイッチ13a、第2始動口スイッチ14a、カウントスイッチ23および入賞口スイッチ29a,30a,33a,39aの検出信号にもとづく賞球個数の設定などを行う賞球処理を実行する(ステップS31)。具体的には、第1始動口スイッチ13a、第2始動口スイッチ14a、カウントスイッチ23および入賞口スイッチ29a,30a,33a,39aのいずれかがオンしたことにもとづく入賞検出に応じて、払出制御基板37に搭載されている払出制御用マイクロコンピュータに賞球個数を示す払出制御コマンド(賞球個数信号)を出力する。払出制御用マイクロコンピュータは、賞球個数を示す払出制御コマンドに応じて球払出装置97を駆動する。また、賞球処理では賞球エラーが発生したか否かの判定処理も行われる。例えば、賞球個数の設定値と実際の払出数とに食い違いが生じた場合に、CPU56は、賞球エラーが発生したと判定し、演出制御基板80が搭載する演出制御用マイクロコンピュータ100に、賞球エラーの発生を報知することを指定する賞球エラー報知指定コマンドを送信する制御を行う。

Further, the CPU 56 performs prize ball processing for setting the number of prize balls based on detection signals from the first start port switch 13a, the second start port switch 14a, the

また、CPU56は、満タンスイッチや球切れスイッチ、ドア開放センサ155の検出信号にもとづくエラー検出処理を実行する(ステップS32)。具体的には、満タンスイッチの検出信号に応じて、演出制御基板80に搭載されている演出制御用マイクロコンピュータ100に、満タンエラーが発生したことを報知することを指定する満タンエラー報知指定コマンドを送信する。また、球切れスイッチの検出信号に応じて、演出制御基板80に搭載されている演出制御用マイクロコンピュータ100に、球切れエラーが発生したことを報知することを指定する球切れエラー報知指定コマンドを送信する。ドア開放センサ155の検出信号に応じて、演出制御基板80に搭載されている演出制御用マイクロコンピュータ100に、ドア開放エラーが発生したことを報知することを指定するドア開放エラー報知指定コマンドを送信する。

Further, the CPU 56 executes an error detection process based on the detection signal from the full switch, the ball break switch, and the door opening sensor 155 (step S32). Specifically, a full tank error notification designation command for designating notification to the

この実施の形態では、出力ポートの出力状態に対応したRAM領域(出力ポートバッファ)が設けられているのであるが、CPU56は、出力ポートの出力状態に対応したRAM領域におけるソレノイドのオン/オフに関する内容を出力ポートに出力する(ステップS33:出力処理)。 In this embodiment, a RAM area (output port buffer) corresponding to the output state of the output port is provided. However, the CPU 56 relates to on / off of the solenoid in the RAM area corresponding to the output state of the output port. The contents are output to the output port (step S33: output process).

また、CPU56は、特別図柄プロセスフラグの値に応じて特別図柄の演出表示を行うための特別図柄表示制御データを特別図柄表示制御データ設定用の出力バッファに設定する特別図柄表示制御処理を行う(ステップS34)。CPU56は、例えば、特別図柄プロセス処理でセットされる開始フラグがセットされると終了フラグがセットされるまで、変動速度が1コマ/0.2秒であれば、0.2秒が経過する毎に、出力バッファに設定される表示制御データの値を+1する。また、CPU56は、出力バッファに設定された表示制御データに応じて、ステップS22において駆動信号を出力することによって、特別図柄表示器8における特別図柄の可変表示を実行する。

Further, the CPU 56 performs a special symbol display control process for setting special symbol display control data for effect display of special symbols in the output buffer for setting the special symbol display control data according to the value of the special symbol process flag ( Step S34). For example, if the change speed is 1 frame / 0.2 seconds until the end flag is set when the start flag set in the special symbol process is set, the CPU 56, for example, every 0.2 seconds passes. Then, the value of the display control data set in the output buffer is incremented by one. Further, the CPU 56 performs variable display of the special symbol on the

さらに、CPU56は、普通図柄プロセスフラグの値に応じて普通図柄の演出表示を行うための普通図柄表示制御データを普通図柄表示制御データ設定用の出力バッファに設定する普通図柄表示制御処理を行う(ステップS35)。CPU56は、例えば、普通図柄の変動に関する開始フラグがセットされると終了フラグがセットされるまで、普通図柄の変動速度が0.2秒ごとに表示状態(「○」および「×」)を切り替えるような速度であれば、0.2秒が経過する毎に、出力バッファに設定される表示制御データの値(例えば、「○」を示す1と「×」を示す0)を切り替える。また、CPU56は、出力バッファに設定された表示制御データに応じて、ステップS22において駆動信号を出力することによって、普通図柄表示器10における普通図柄の演出表示を実行する。

Further, the CPU 56 performs a normal symbol display control process for setting normal symbol display control data for effect display of the normal symbol in an output buffer for setting the normal symbol display control data according to the value of the normal symbol process flag ( Step S35). For example, when the start flag related to the variation of the normal symbol is set, the CPU 56 switches the display state (“◯” and “×”) for the variation rate of the normal symbol every 0.2 seconds until the end flag is set. With such a speed, the value of the display control data set in the output buffer (for example, 1 indicating “◯” and 0 indicating “x”) is switched every 0.2 seconds. Further, the CPU 56 outputs a normal signal on the

その後、割込許可状態に設定し(ステップS36)、処理を終了する。 Thereafter, the interrupt permission state is set (step S36), and the process ends.

以上の制御によって、この実施の形態では、遊技制御処理は2ms毎に起動されることになる。なお、遊技制御処理は、タイマ割込処理におけるステップS21〜S35(ステップS30を除く。)の処理に相当する。また、この実施の形態では、タイマ割込処理で遊技制御処理が実行されているが、タイマ割込処理では例えば割込が発生したことを示すフラグのセットのみがなされ、遊技制御処理はメイン処理において実行されるようにしてもよい。 With the above control, in this embodiment, the game control process is started every 2 ms. The game control process corresponds to the processes in steps S21 to S35 (excluding step S30) in the timer interrupt process. In this embodiment, the game control process is executed by the timer interrupt process. However, in the timer interrupt process, for example, only a flag indicating that an interrupt has occurred is set, and the game control process is performed by the main process. May be executed.

図22は、大当り判定テーブルを示す説明図である。大当り判定テーブルとは、ランダムRと比較される大当り判定値が設定されているテーブルである。大当り判定判定テーブルには、通常状態(確変状態でない遊技状態)において用いられる通常時大当り判定テーブル(図22(A)参照)と、確変状態において用いられる確変時大当り判定テーブル(図22(B)参照)とがある。図22(A),(B)の左欄に記載されている数値が大当り判定値である。CPU56は、ランダムRの値がいずれかの大当り判定値と一致すると、大当りとすることに決定する。CPU56は、所定の時期に、乱数回路のカウント値を抽出して抽出値を大当り判定用乱数値とするのであるが、大当り判定用乱数値が図21に示す大当り判定値に一致すると、特別図柄に関して大当り(確変大当りまたは通常大当り)とすることに決定する。 FIG. 22 is an explanatory diagram of a jackpot determination table. The jackpot determination table is a table in which a jackpot determination value to be compared with the random R is set. The jackpot determination determination table includes a normal jackpot determination table (see FIG. 22A) used in a normal state (a gaming state that is not a probability change state) and a probability change jackpot determination table (FIG. 22B) used in a probability change state. See). The numerical values described in the left column of FIGS. 22A and 22B are jackpot determination values. When the value of the random R matches any one of the jackpot determination values, the CPU 56 determines that the jackpot is to be made. The CPU 56 extracts the count value of the random number circuit at a predetermined time and uses the extracted value as the jackpot determination random value. If the jackpot determination random value matches the jackpot determination value shown in FIG. Is determined to be a big hit (probable big hit or normal big hit).

確変大当りとは、大当り遊技後の遊技状態を、通常状態に比べて大当りとすることに決定される確率が高い状態である確変状態に移行させるような大当りである。通常大当りとは、大当り遊技後の遊技状態を確変状態ではない状態に移行させるような大当りである。なお、確変大当りおよび通常大当りの場合には、ラウンド数は、小当りおよび突然確変大当りの場合よりも多く、例えば15ラウンドである。 The probability variation jackpot is a jackpot that shifts the gaming state after the jackpot game to a probability variation state in which there is a high probability of being determined to be a jackpot compared to the normal state. Usually, the big hit is a big hit that shifts the gaming state after the big hit game to a state that is not a probable change state. Note that the number of rounds in the case of a probable big hit and the normal big hit is larger than that in the case of a small hit and a sudden probable big hit, for example, 15 rounds.

小当りとは、大当り遊技状態において大入賞口の開放回数が2回まで許容される大当りである。なお、小当り遊技が終了した場合、遊技状態が確変状態に移行することはない。突然確変大当りとは、大当り遊技状態において大入賞口の開放回数が2回まで許容されるが大入賞口の開放時間が極めて短い大当りであり、かつ、大当り遊技後の遊技状態を確変状態に移行させるような大当りである。つまり、この実施の形態では、突然確変大当りと小当りとは、ラウンド数が同じである。 The small hit is a big hit in which the number of times of opening of the big winning opening is allowed up to two in the big hit gaming state. Note that when the small hit game ends, the gaming state does not shift to the probable change state. Suddenly probable jackpot is a jackpot where the number of times the big prize opening is allowed is 2 in the big hit gaming state, but the opening time of the big prize opening is extremely short, and the gaming state after the big hit game is shifted to the probable state It ’s a big hit. That is, in this embodiment, the number of rounds is the same between the sudden probability big hit and the small hit.

なお、突然確変大当りの大当り遊技では、ラウンド数は、通常大当りおよび確変大当りの場合よりも少なく、かつ、各ラウンドの大入賞口開放許容時間(例えば、通常大当りおよび確変大当りの場合の29秒に対して、0.5秒)は通常大当りおよび確変大当りの場合よりも短いが、ラウンド数のみを少なくしたり、大入賞口開放許容時間のみを短くするようにしてもよい。 In the big hit game of sudden probability change big hit, the number of rounds is smaller than in the case of normal big hit and probability variable big hit, and the allowance opening time for each round (for example, 29 seconds in the case of normal big hit and probability variable big hit) On the other hand, 0.5 seconds) is shorter than the case of the normal big hit and the probability variation big hit, but only the number of rounds may be reduced, or only the allowance opening allowance time may be shortened.

図23は、この実施の形態で用いられる変動パターンの一例を示す説明図である。後述するように、この実施の形態では、演出制御コマンドは2バイト構成であり、1バイト目はMODE(コマンドの分類)を表し、2バイト目はEXT(コマンドの種類)を表す。図23において、「EXT」とは、2バイト構成の演出制御コマンドにおける2バイト目のEXTデータを示す。また、「変動時間」は特別図柄の変動時間(識別情報の可変表示期間)を示す。 FIG. 23 is an explanatory diagram showing an example of a variation pattern used in this embodiment. As will be described later, in this embodiment, the presentation control command has a 2-byte structure, the first byte represents MODE (command classification), and the second byte represents EXT (command type). In FIG. 23, “EXT” indicates EXT data of the second byte in the effect control command having a two-byte structure. “Variation time” indicates the variation time of the special symbol (variable display period of identification information).

「通常変動」は、リーチ態様を伴わない変動パターンである。「通常変動・短縮」は、リーチ態様を伴わない変動パターンであり、かつ、変動時間が「通常変動」よりも短い変動パターンである。「ノーマルリーチ」は、リーチ態様を伴うが表示結果(停止図柄)が大当り図柄にならない変動パターンである。「リーチA」は、「ノーマルリーチ」とは異なるリーチ態様を持つ変動パターンである。リーチ態様が異なるとは、リーチ変動時間(リーチ演出が行われる期間)で可変表示装置9において異なった態様の変動態様(速度や回転方向等)やキャラクタ画像等が現れたり、可変表示装置9における背景図柄が異なることをいう。例えば、「ノーマルリーチ」では単に1種類の変動態様によってリーチ態様が実現されるのに対して、「リーチA」では、変動速度や変動方向が異なる複数の変動態様を含むリーチ態様が実現される。また、「リーチA・短縮」は、「リーチA」に類似したリーチ態様を持つ変動パターンであるが、リーチ変動時間は、「リーチA」に比べて短い。「リーチA・延長」は、「リーチA」に類似したリーチ態様を持つ変動パターンであるが、リーチ変動時間は、「リーチA」に比べて長い。

“Normal fluctuation” is a fluctuation pattern without a reach mode. “Normal fluctuation / shortening” is a fluctuation pattern without a reach mode and a fluctuation time shorter than “normal fluctuation”. “Normal reach” is a variation pattern that is accompanied by a reach mode but whose display result (stop symbol) does not become a big hit symbol. “Reach A” is a variation pattern having a reach form different from “normal reach”. A different reach mode means that a different mode of change mode (speed, direction of rotation, etc.), a character image, or the like appears in the

「リーチB」は、「ノーマルリーチ」および「リーチA」とは異なるリーチ態様を持つ変動パターンである。また、「リーチB・短縮」は、「リーチB」に類似したリーチ態様を持つ変動パターンであるが、リーチ変動時間は、「リーチB」に比べて短い。「リーチB・延長」は、「リーチB」に類似したリーチ態様を持つ変動パターンであるが、リーチ変動時間は、「リーチB」に比べて長い。「リーチC」は、「ノーマルリーチ」、「リーチA」および「リーチB」とは異なるリーチ態様を持つ変動パターンである。「リーチC・短縮」は、「リーチC」に類似したリーチ態様を持つ変動パターンであるが、リーチ変動時間は、「リーチC」に比べて短い。 “Reach B” is a fluctuation pattern having a reach mode different from “Normal reach” and “Reach A”. Further, “reach B / shortening” is a variation pattern having a reach manner similar to “reach B”, but the reach variation time is shorter than “reach B”. “Reach B / extension” is a variation pattern having a reach manner similar to “reach B”, but reach variation time is longer than “reach B”. “Reach C” is a variation pattern having a reach form different from “normal reach”, “reach A”, and “reach B”. “Reach C / shortening” is a variation pattern having a reach manner similar to “reach C”, but reach variation time is shorter than “reach C”.

また、「スーパーリーチA」は、「ノーマルリーチ」、「リーチA」、「リーチB」および「リーチC」とは異なるリーチ態様を持つ変動パターンであり、例えば動画像によるリーチ態様を持つ変動パターンである。「スーパーリーチB」は、「ノーマルリーチ」、「リーチA」、「リーチB」、「リーチC」および「スーパーリーチA」とは異なるリーチ態様を持つ変動パターンであり、例えば動画像によるリーチ態様を持つ変動パターンである。「リーチA・突確」は、「ノーマルリーチ」、「リーチA」、「リーチB」、「リーチC」、「スーパーリーチA」および「スーパーリーチB」とは異なるリーチ態様を持つ変動パターンである。なお、「リーチA・突確」のリーチ態様は、「リーチA」に類似するリーチ態様である。 “Super reach A” is a variation pattern having a reach mode different from “normal reach”, “reach A”, “reach B”, and “reach C”. is there. “Super reach B” is a variation pattern having a reach form different from “normal reach”, “reach A”, “reach B”, “reach C” and “super reach A”. This is a variation pattern. “Reach A / Accuracy” is a variation pattern having a reach form different from “Normal reach”, “Reach A”, “Reach B”, “Reach C”, “Super reach A” and “Super reach B”. It should be noted that the reach form of “reach A / accuracy” is a reach form similar to “reach A”.

この実施の形態では、通常大当りの場合には、遊技制御用マイクロコンピュータ560は、「リーチA・短縮」、「リーチA」、「リーチB・短縮」、「リーチB」、「リーチC・短縮」、「リーチC」、「スーパーリーチA」または「スーパーリーチB」を選択する。また、確変大当りの場合には、遊技制御用マイクロコンピュータ560は、「リーチA・延長」、「リーチB・延長」、「リーチC・短縮」、「リーチC」、「スーパーリーチA」または「スーパーリーチB」を選択する。突然確変大当りの場合には、「リーチA・突確」を選択する。 In this embodiment, in the case of a big hit, the game control microcomputer 560 is “reach A / shortening”, “reach A”, “reach B / shortening”, “reach B”, “reach C / shortening”. ", Reach C", "Super Reach A" or "Super Reach B". Further, in the case of a probable big hit, the game control microcomputer 560 is “reach A / extension”, “reach B / extension”, “reach C / shortening”, “reach C”, “super reach A” or “ Select "Super Reach B". In case of sudden big odds, select “Reach A / Random”.

また、図23に示すように、通常大当りの場合にのみ選択される変動パターンと、確変大当りの場合にのみ選択される変動パターンと、通常大当りのときにも確変大当りのときにも選択されうる変動パターンとがある。 Further, as shown in FIG. 23, the fluctuation pattern selected only in the case of the normal big hit, the fluctuation pattern selected only in the case of the probability big hit, and the normal big hit and the probability variable big hit can be selected. There are fluctuation patterns.

また、時短状態では、「通常変動・短縮」、「リーチA・短縮」、「リーチB・短縮」、および「リーチC・短縮」の変動パターンが選択される。非時短状態では、それ以外の変動パターンが選択される。ただし、「リーチA・突確」の変動パターンは、時短状態でも非時短状態でも使用される。 In the short-time state, the fluctuation patterns of “normal fluctuation / shortening”, “reach A / shortening”, “reach B / shortening”, and “reach C / shortening” are selected. In the non-time-short state, other variation patterns are selected. However, the variation pattern of “reach A / accuracy” is used in both the short-time state and the non-short-time state.

なお、この実施の形態では、大当りが発生し、大当り遊技が終了すると、その後、100回の特別図柄の変動(可変表示)の実行が完了するまで、遊技状態は時短状態になる。また、可変表示が終了すると大当り遊技が開始されるときの特別図柄の可変表示を開始するときに、確変状態にすることに決定された場合には、大当り遊技が終了すると遊技状態が確変状態に移行される。なお、そのときの遊技状態が確変状態であれば、確変状態が継続することになる。 In this embodiment, when a big hit occurs and the big hit game ends, the gaming state becomes a short-time state thereafter until the execution of 100 special symbol changes (variable display) is completed. In addition, when variable display of a special symbol is started when variable display is finished, when it is decided to change to a probable change state when the special symbol variable display is started, the game state is changed into a probable change state when the big hit game is ended. Migrated. If the gaming state at that time is a probability variation state, the probability variation state is continued.

確変状態に移行されたら、その後、100回の特別図柄の変動(可変表示)の実行が完了するまでは、確変状態かつ時短状態である。また、大当り遊技が終了した後の非確変状態において、100回の特別図柄の変動(可変表示)の実行が完了すると遊技状態は通常状態(確変状態でなく、かつ、時短状態でない遊技状態)に移行する。 After the transition to the probability changing state, the state of the probability changing state is short and the state is short until the execution of the variation (variable display) of 100 special symbols is completed. In addition, in the non-probability change state after the big hit game is over, the game state is changed to the normal state (the game state that is not the probability change state and not the short-time state) when the execution of 100 special symbol changes (variable display) is completed. Transition.

次に、遊技制御用マイクロコンピュータ560から演出制御用マイクロコンピュータ100に対する制御コマンドの送出方式について説明する。この実施の形態では、演出制御コマンドは、シリアル出力回路78によってパラレルデータからシリアルデータに変換され、主基板31から中継基板77を介して演出制御基板80に送信される。

Next, a method for sending a control command from the game control microcomputer 560 to the

この実施の形態では、演出制御コマンドは2バイト構成であり、1バイト目はMODE(コマンドの分類)を表し、2バイト目はEXT(コマンドの種類)を表す。MODEデータの先頭ビット(ビット7)は必ず「1」に設定され、EXTデータの先頭ビット(ビット7)は必ず「0」に設定される。なお、そのようなコマンド形態は一例であって他のコマンド形態を用いてもよい。例えば、1バイトや3バイト以上で構成される制御コマンドを用いてもよい In this embodiment, the presentation control command has a 2-byte structure, the first byte represents MODE (command classification), and the second byte represents EXT (command type). The first bit (bit 7) of the MODE data is always set to “1”, and the first bit (bit 7) of the EXT data is always set to “0”. Note that such a command form is an example, and other command forms may be used. For example, a control command composed of 1 byte or 3 bytes or more may be used.

図24は、シリアルデータ方式として送信される演出制御コマンドのフォーマットの例を示す説明図である。図24に示すように、演出制御コマンドを送信する際、遊技制御用マイクロコンピュータ560(具体的にはCPU56)は、まず、MODEデータ(アドレスが付加されたMODEデータ)にヘッダデータやマークビット、エンドビットを付加して送信制御を行う。すると、シリアル出力回路78は、ヘッダデータやアドレス、マークビット、エンドビットが付加されたMODEデータをシリアルデータに変換して、中継基板77を介して演出制御基板80に送信する。次いで、遊技制御用マイクロコンピュータ560は、EXTデータ(アドレスが付加されたEXTデータ)にヘッダデータやマークビット、エンドビットを付加して送信制御を行う。すると、シリアル出力回路78は、ヘッダデータやアドレス、マークビット、エンドビットが付加されたEXTデータをシリアルデータに変換して、中継基板77を介して演出制御基板80に送信する。

FIG. 24 is an explanatory diagram showing an example of the format of the effect control command transmitted as the serial data method. As shown in FIG. 24, when transmitting the effect control command, the game control microcomputer 560 (specifically, the CPU 56) first adds header data and mark bits to MODE data (MODE data to which an address is added), Transmission control is performed by adding an end bit. Then, the

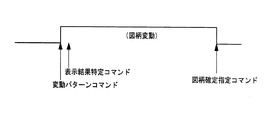

図25は、遊技制御用マイクロコンピュータ560が送信する演出制御コマンドの内容の一例を示す説明図である。図25に示す例において、コマンド8001(H)〜800E(H)は、特別図柄の可変表示に対応して可変表示装置9において可変表示される飾り図柄の変動パターンを指定する演出制御コマンド(変動パターンコマンド)である。なお、変動パターンを指定する演出制御コマンドは、変動開始を指定するためのコマンドでもある。従って、演出制御用マイクロコンピュータ100は、コマンド8001(H)〜800E(H)のいずれかを受信すると、可変表示装置9において飾り図柄の可変表示を開始するように制御する。なお、この実施の形態では、特別図柄の可変表示と飾り図柄の可変表示とは同期(可変表示開始時期および可変表示終了時期が同じ。)しているので、飾り図柄の変動パターン(変動時間)を決定することは、特別図柄の変動パターン(変動時間)を決定することも意味する。

FIG. 25 is an explanatory diagram showing an example of the contents of the effect control command transmitted by the game control microcomputer 560. In the example shown in FIG. 25, commands 8001 (H) to 800E (H) are effect control commands (variation) for designating a variation pattern of decorative symbols that are variably displayed on the

コマンド8C01(H)〜8C05(H)は、大当りとするか否か、および大当り遊技の種類を示す演出制御コマンドである。演出制御用マイクロコンピュータ100は、コマンド8C01(H)〜8C05(H)の受信に応じて飾り図柄の表示結果を決定するので、コマンド8C01(H)〜8C05(H)を表示結果特定コマンドという。

The commands 8C01 (H) to 8C05 (H) are effect control commands indicating whether or not to make a big hit and the type of the big hit game. The

コマンド8F00(H)は、飾り図柄の可変表示(変動)を終了して表示結果(停止図柄)を導出表示することを示す演出制御コマンド(図柄確定指定コマンド)である。演出制御用マイクロコンピュータ100は、図柄確定指定コマンドを受信すると、飾り図柄の可変表示(変動)を終了して表示結果を導出表示する。なお、導出表示とは、図柄を最終的に停止表示させることである。

Command 8F00 (H) is an effect control command (symbol confirmation designation command) indicating that the variable display (fluctuation) of the decorative symbols is terminated and the display result (stop symbol) is derived and displayed. When receiving the symbol confirmation designation command, the

コマンド9000(H)は、遊技機に対する電力供給が開始されたときに送信される演出制御コマンド(初期化指定コマンド:電源投入指定コマンド)である。コマンド9200(H)は、遊技機に対する電力供給が再開されたときに送信される演出制御コマンド(停電復旧指定コマンド)である。遊技制御用マイクロコンピュータ560は、遊技機に対する電力供給が開始されたときに、バックアップRAMにデータが保存されている場合には、停電復旧指定コマンドを送信し、そうでない場合には、初期化指定コマンドを送信する。 Command 9000 (H) is an effect control command (initialization designation command: power-on designation command) transmitted when power supply to the gaming machine is started. Command 9200 (H) is an effect control command (power failure recovery designation command) transmitted when power supply to the gaming machine is resumed. When the power supply to the gaming machine is started, the game control microcomputer 560 transmits a power failure recovery designation command if data is stored in the backup RAM, and if not, initialization designation is performed. Send a command.

コマンド9F00(H)は、客待ちデモンストレーションを指定する演出制御コマンド(客待ちデモ指定コマンド)である。また、コマンド9F55(H)は、メイン処理における乱数回路確認処理において乱数回路の異常発生を検出した場合に、主基板31の乱数回路エラーを報知することを指定する演出制御コマンド(乱数回路エラー指定コマンド)である。