JP4914558B2 - アクティブマトリックスディスプレイ装置 - Google Patents

アクティブマトリックスディスプレイ装置 Download PDFInfo

- Publication number

- JP4914558B2 JP4914558B2 JP2003514534A JP2003514534A JP4914558B2 JP 4914558 B2 JP4914558 B2 JP 4914558B2 JP 2003514534 A JP2003514534 A JP 2003514534A JP 2003514534 A JP2003514534 A JP 2003514534A JP 4914558 B2 JP4914558 B2 JP 4914558B2

- Authority

- JP

- Japan

- Prior art keywords

- data storage

- pixels

- image data

- column

- row

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000011159 matrix material Substances 0.000 title claims description 41

- 238000013500 data storage Methods 0.000 claims description 44

- 239000003990 capacitor Substances 0.000 claims description 40

- 230000006870 function Effects 0.000 claims description 6

- 239000004973 liquid crystal related substance Substances 0.000 description 7

- 239000000463 material Substances 0.000 description 7

- 239000000758 substrate Substances 0.000 description 6

- 238000001514 detection method Methods 0.000 description 5

- 238000000034 method Methods 0.000 description 5

- 238000013459 approach Methods 0.000 description 4

- 230000003068 static effect Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 230000002411 adverse Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000005297 material degradation process Methods 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 241001270131 Agaricus moelleri Species 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 210000000056 organ Anatomy 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920001690 polydopamine Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3291—Details of drivers for data electrodes in which the data driver supplies a variable data voltage for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0828—Several active elements per pixel in active matrix panels forming a digital to analog [D/A] conversion circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0262—The addressing of the pixel, in a display other than an active matrix LCD, involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependent on signals of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/029—Improving the quality of display appearance by monitoring one or more pixels in the display panel, e.g. by monitoring a fixed reference pixel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

- G09G2330/022—Power management, e.g. power saving in absence of operation, e.g. no data being entered during a predetermined time

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Liquid Crystal Display Device Control (AREA)

- Thin Film Transistor (AREA)

Description

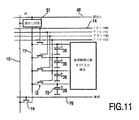

例示として、各行に沿った複数の行電極を有し、各行電極が、各画像データ記憶キャパシタをデータラインに接続するようスイッチを切り換え、選択ラインが、前記データラインが対応する列電極を接続するようスイッチを制御し、前記読出し回路が、読出しラインの制御の下でデータライン上のデータを列電極に読み出してもよい。

ΔV=Vcap.Cs/(Cs+CLC)

となり、Vcapは、記憶キャパシタ駆動ライン61で揺れ動く電圧であり、それは、(特定の行に対する)奇数フィールドで+Vcapとなり、(特定の行に対する)偶数フィールドで−Vcapとなり、Cs及びCLCはそれぞれ、記憶キャパシタ60のキャパシタンス及びLC表示素子16のキャパシタンスである。

1)画素電圧を0又はVcolに回復するよう記憶キャパシタ駆動ライン61をスイッチ。

2)列電極16をVcolにプレチャージ(図7において、プレチャージ制御信号PCがハイになると、プレチャージが生じる。)。

3)列電極の画素の状態を検知するためにT2をターンオン。Vpix=Vcolの場合、T3がターンオンされるとともに、列電極がVSS(0V)まで放電さ れ、Vpix=0の場合、T3がターンオフされ、列電極電圧がVcolに保持される。これは、列電極電圧がVpixに対する反転されていることを意味する。

4)記憶キャパシタ駆動ライン61を以前のレベルに戻す。

5)T1をターンオンすることによって、反転されたデータを画素に書き戻す。

6)LCを駆動するのに適切な他の画素電圧に結合するよう記憶キャパシタ駆動ライン61をスイッチする。

所望の場合、Vssは、0V以外の他の値をとることができる。

Claims (7)

- 行列配置した複数の画素と、対応する画素の列に沿って延在する列電極とを具え、

前記複数の画素の各々が、画像データ記憶キャパシタンスと、

前記列電極と前記画像データ記憶キャパシタンスとの間に接続され、前記画像データ記憶キャパシタンスの電圧を一旦取り込み、前記取り込んだ画像データ記憶キャパシタンスの状態に基づいて前記列電極を荷電するバッファとして機能する読出し回路と、を有することを特徴とするアクティブマトリックス表示装置。 - 行電極と、前記対応する画素の行に沿って延在する読出しラインとを有する請求項1記載のアクティブマトリックス表示装置であって、

前記複数の画素の各々が、対応する行電極によって選択されたときに対応する列電極を前記データ記憶キャパシタンスに接続するスイッチを有し、

前記読み出し回路が、前記画像データ記憶キャパシタンスの電圧を前記対応する列電極に読み出すために対応する読出しラインによって制御されることを特徴とするアクティブマトリックス表示装置。 - 前記複数の画素の各々が、画素表示素子を駆動する駆動回路を有し、前記駆動回路が、前記画像データ記憶キャパシタンスに接続された入力部を有することを特徴とする請求項2記載のアクティブマトリックス表示装置。

- 前記複数の画素の各々が、複数の画像データ記憶キャパシタンスを有することを特徴とする請求項1〜3のいずれか1項に記載のアクティブマトリックス表示装置。

- 前記複数の画像データ記憶キャパシタンスの各々に接続された専用の読出し回路を有することを特徴とする請求項4記載のアクティブマトリックス表示装置。

- 行列配置した複数の画素と、行電極と、対応する画素の列に沿って延在する列電極と、対応する画素の行に沿って延在する読出しラインとを具え、

前記複数の画素の各々が、画像データ記憶キャパシタンスと、

対応する行電極によって選択されたときに対応する列電極を前記データ記憶キャパシタンスに接続する第1スイッチと、

前記画像データ記憶キャパシタンスに接続された入力部を有し、画素表示素子を駆動する駆動回路と、

前記列電極と前記駆動回路の出力部との間に配置され、前記画像データ記憶キャパシタンスの電圧に基づいて前記列電極を荷電するために対応する読出しラインによって制御され、前記対応する読出しラインの制御の下で前記駆動回路の出力部を前記対応する列電極に接続する第2スイッチとを有することを特徴とするアクティブマトリックス表示装置。 - 行列配置した複数の画素と、対応する画素の列に沿って延在する列電極と、対応する画素の行に沿って延在する読出しライン、選択ラインおよび複数の行電極とを具え、

前記複数の画素の各々が、複数の画像データ記憶キャパシタンスと、

データラインと、

対応する行電極によって選択されたときに対応する画像データ記憶キャパシタンスを前記データラインに接続する複数の第3スイッチと、

前記列電極と前記データラインとの間に接続され、前記複数の行電極の1つによって選択された前記画像データ記憶キャパシタンスの電圧を一旦取り込み、前記取り込んだ画像データ記憶キャパシタンスの電圧に基づいて前記列電極を荷電するバッファとして機能する読出し回路と、

前記列電極上の電圧を前記複数の行電極の1つによって選択された前記画像データ記憶キャパシタンスに書き込むように、前記選択ラインの制御の下で前記列電極を前記データラインを介して前記第3スイッチに接続する第4スイッチと、

を有し、

前記読み出し回路が、前記読出しラインの制御の下で前記データライン上にある前記複数の行電極の1つによって選択された前記画像データキャパシタンスの電圧を前記対応する列電極に読み出すことを特徴とするアクティブマトリックス表示装置。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB0117226.1 | 2001-07-14 | ||

| GBGB0117226.1A GB0117226D0 (en) | 2001-07-14 | 2001-07-14 | Active matrix display devices |

| GBGB0125969.6A GB0125969D0 (en) | 2001-07-14 | 2001-10-30 | Active matrix display devices |

| GB0125969.6 | 2001-10-30 | ||

| PCT/IB2002/002993 WO2003009268A2 (en) | 2001-07-14 | 2002-07-12 | Active matrix display devices |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004536347A JP2004536347A (ja) | 2004-12-02 |

| JP2004536347A5 JP2004536347A5 (ja) | 2011-06-02 |

| JP4914558B2 true JP4914558B2 (ja) | 2012-04-11 |

Family

ID=9918520

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003514534A Expired - Fee Related JP4914558B2 (ja) | 2001-07-14 | 2002-07-12 | アクティブマトリックスディスプレイ装置 |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP4914558B2 (ja) |

| KR (1) | KR100888461B1 (ja) |

| GB (2) | GB0117226D0 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100613091B1 (ko) * | 2004-12-24 | 2006-08-16 | 삼성에스디아이 주식회사 | 데이터 집적회로 및 이를 이용한 발광 표시장치와 그의구동방법 |

| US7952546B2 (en) * | 2007-06-27 | 2011-05-31 | Chimei Innolux Corporation | Sample/hold circuit, electronic system, and control method utilizing the same |

| JP5125378B2 (ja) * | 2007-10-03 | 2013-01-23 | セイコーエプソン株式会社 | 制御方法、制御装置、表示体および情報表示装置 |

| JP5011514B2 (ja) * | 2009-03-19 | 2012-08-29 | 奇美電子股▲ふん▼有限公司 | 液晶表示装置の駆動方法及び液晶表示装置 |

| JP5386409B2 (ja) * | 2010-03-08 | 2014-01-15 | 群創光電股▲ふん▼有限公司 | アクティブマトリクス型ディスプレイ装置及びこれを有する電子機器 |

| KR101917837B1 (ko) * | 2011-11-10 | 2018-11-14 | 엘지디스플레이 주식회사 | 액정 디스플레이 장치와 이의 구동방법 |

| WO2013105393A1 (ja) * | 2012-01-12 | 2013-07-18 | シャープ株式会社 | 画素回路及び表示装置 |

| KR102378589B1 (ko) * | 2015-08-21 | 2022-03-28 | 삼성디스플레이 주식회사 | 디멀티플렉서, 이를 포함한 표시장치 및 그의 구동방법 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5799688A (en) * | 1980-12-11 | 1982-06-21 | Sharp Kk | Display driving circuit |

| JPS59208590A (ja) * | 1983-05-11 | 1984-11-26 | シャープ株式会社 | 表示装置の駆動回路 |

| JP3102666B2 (ja) * | 1993-06-28 | 2000-10-23 | シャープ株式会社 | 画像表示装置 |

| JP3832086B2 (ja) * | 1998-04-15 | 2006-10-11 | セイコーエプソン株式会社 | 反射型液晶装置及び反射型プロジェクタ |

-

2001

- 2001-07-14 GB GBGB0117226.1A patent/GB0117226D0/en not_active Ceased

- 2001-10-30 GB GBGB0125969.6A patent/GB0125969D0/en not_active Ceased

-

2002

- 2002-07-12 JP JP2003514534A patent/JP4914558B2/ja not_active Expired - Fee Related

- 2002-07-12 KR KR1020037003629A patent/KR100888461B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| KR20040023563A (ko) | 2004-03-18 |

| JP2004536347A (ja) | 2004-12-02 |

| GB0117226D0 (en) | 2001-09-05 |

| KR100888461B1 (ko) | 2009-03-11 |

| GB0125969D0 (en) | 2001-12-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6897843B2 (en) | Active matrix display devices | |

| US7230597B2 (en) | Active matrix array devices | |

| KR100417572B1 (ko) | 표시장치 | |

| US7586473B2 (en) | Active matrix array device, electronic device and operating method for an active matrix array device | |

| KR101037554B1 (ko) | 액티브 매트릭스 디스플레이 장치 및 그의 구동 방법 | |

| US20020063671A1 (en) | Active matrix liquid crystal display devices | |

| US7545355B2 (en) | Image display apparatus and driving method thereof | |

| KR100726052B1 (ko) | 전기 광학 장치 및 그의 구동 방법, 디지털 구동 액정 표시 장치, 전자 기기 및 프로젝터 | |

| US9208714B2 (en) | Display panel for refreshing image data and operating method thereof | |

| US11043163B2 (en) | Display device and electronic shelf label | |

| KR100465472B1 (ko) | 액티브 매트릭스형 표시 장치 | |

| JP4914558B2 (ja) | アクティブマトリックスディスプレイ装置 | |

| US10559286B2 (en) | Display device | |

| US8791895B2 (en) | Liquid crystal display device and drive method therefor | |

| US8339351B2 (en) | Display device | |

| US8736591B2 (en) | Display device using pixel memory circuit to reduce flicker with reduced power consumption | |

| JP2004536347A5 (ja) | ||

| WO2020066176A1 (ja) | 表示装置及び電子看板 | |

| KR100879769B1 (ko) | 능동 매트릭스 어레이 장치 | |

| JP2020052219A (ja) | 表示装置及び電子看板 | |

| JP2020042191A (ja) | 表示装置及び電子看板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050711 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20070202 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080722 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081022 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20081202 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090401 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20090407 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20091204 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100720 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100726 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100820 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100827 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110216 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110222 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110316 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110322 |

|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20110418 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111130 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120123 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150127 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |