以下、本発明の一実施形態を図面を参照して説明する。

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機1を正面からみた正面図、図2はパチンコ遊技機1の内部構造を示す全体背面図、図3はパチンコ遊技機1の遊技盤を背面からみた背面図である。なお、ここでは、遊技機の一例としてパチンコ遊技機を示すが、本発明はパチンコ遊技機に限られず、例えばコイン遊技機等であってもよい。また、画像式の遊技機やスロット機に適用することもできる。

図1に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿3がある。打球供給皿3の下部には、打球供給皿3からあふれた景品玉を貯留する余剰玉受皿4と打球を発射する打球操作ハンドル(操作ノブ)5が設けられている。ガラス扉枠2の後方には、遊技盤6が着脱可能に取り付けられている。また、遊技盤6の前面には遊技領域7が設けられている。

遊技領域7の中央付近には、複数種類の図柄を可変表示するための可変表示部9と7セグメントLEDによる可変表示器10とを含む可変表示装置8が設けられている。この実施の形態では、可変表示部9には、「左」、「中」、「右」の3つの図柄表示エリアがある。可変表示装置8の側部には、打球を導く通過ゲート11が設けられている。通過ゲート11を通過した打球は、玉出口13を経て始動入賞口14の方に導かれる。通過ゲート11と玉出口13との間の通路には、通過ゲート11を通過した打球を検出するゲートスイッチ12がある。また、始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ17によって検出される。また、始動入賞口14の下部には開閉動作を行う可変入賞球装置15が設けられている。可変入賞球装置15は、ソレノイド16によって開状態とされる。

可変入賞球装置15の下部には、特定遊技状態(大当り状態)においてソレノイド21によって開状態とされる開閉板20が設けられている。この実施の形態では、開閉板20が大入賞口を開閉する手段となる。開閉板20から遊技盤6の背面に導かれた入賞球のうち一方(Vゾーン)に入った入賞球はVカウントスイッチ22で検出される。また、開閉板20からの入賞球はカウントスイッチ23で検出される。可変表示装置8の下部には、始動入賞口14に入った入賞球数を表示する4個の表示部を有する始動入賞記憶表示器18が設けられている。この例では、4個を上限として、始動入賞がある毎に、始動入賞記憶表示器18は点灯している表示部を1つずつ増やす。そして、可変表示部9の可変表示が開始される毎に、点灯している表示部を1つ減らす。

遊技盤6には、複数の入賞口19,24が設けられ、遊技球の入賞口19,24への入賞は入賞口スイッチ19a,24aによって検出される。遊技領域7の左右周辺には、遊技中に点滅表示される装飾ランプ25が設けられ、下部には、入賞しなかった打球を吸収するアウト口26がある。また、遊技領域7の外側の左右上部には、効果音を発する2つのスピーカ27が設けられている。遊技領域7の外周には、遊技効果LED28aおよび遊技効果ランプ28b,28cが設けられている。

そして、この例では、一方のスピーカ27の近傍に、景品玉払出時に点灯する賞球ランプ51が設けられ、他方のスピーカ27の近傍に、補給玉が切れたときに点灯する球切れランプ52が設けられている。さらに、図1には、パチンコ遊技台1に隣接して設置され、プリペイドカードが挿入されることによって玉貸しを可能にするカードユニット50も示されている。

カードユニット50には、使用可能状態であるか否かを示す使用可表示ランプ151、カード内に記録された残額情報に端数(100円未満の数)が存在する場合にその端数を打球供給皿3の近傍に設けられる度数表示LEDに表示させるための端数表示スイッチ152、カードユニット50がいずれの側のパチンコ遊技機1に対応しているのかを示す連結台方向表示器153、カードユニット50内にカードが投入されていることを示すカード投入表示ランプ154、記録媒体としてのカードが挿入されるカード挿入口155、およびカード挿入口155の裏面に設けられているカードリーダライタの機構を点検する場合にカードユニット50を解放するためのカードユニット錠156が設けられている。

打球発射装置から発射された打球は、打球レールを通って遊技領域7に入り、その後、遊技領域7を下りてくる。打球が通過ゲート11を通ってゲートスイッチ12で検出されると、可変表示器10の表示数字が連続的に変化する状態になる。また、打球が始動入賞口14に入り始動口スイッチ17で検出されると、図柄の変動を開始できる状態であれば、可変表示部9内の図柄が回転を始める。図柄の変動を開始できる状態でなければ、始動入賞記憶を1増やす。

可変表示部9内の画像の回転は、一定時間が経過したときに停止する。停止時の画像の組み合わせが大当り図柄の組み合わせであると、大当り遊技状態に移行する。すなわち、開閉板20が、一定時間経過するまで、または、所定個数(例えば10個)の打球が入賞するまで開放する。そして、開閉板20の開放中に打球が特定入賞領域に入賞しVカウントスイッチ22で検出されると、継続権が発生し開閉板20の開放が再度行われる。継続権の発生は、所定回数(例えば15ラウンド)許容される。

停止時の可変表示部9内の画像の組み合わせが確率変動を伴う大当り図柄の組み合わせである場合には、次に大当りとなる確率が高くなる。すなわち、高確率状態という遊技者にとってさらに有利な状態となる。また、可変表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定時間だけ開状態になる。さらに、高確率状態では、可変表示器10における停止図柄が当り図柄になる確率が高められるとともに、可変入賞球装置15の開放時間と開放回数が高められる。

次に、パチンコ遊技機1の裏面の構造について図2を参照して説明する。

可変表示装置8の背面では、図2に示すように、機構板36の上部に景品玉タンク38が設けられ、パチンコ遊技機1が遊技機設置島に設置された状態でその上方から景品玉が景品玉タンク38に供給される。景品玉タンク38内の景品玉は、誘導樋39を通って玉払出装置に至る。

機構板36には、中継基板30を介して可変表示部9を制御する可変表示制御ユニット29、基板ケース32に覆われ遊技制御用マイクロコンピュータ等が搭載された遊技制御基板(主基板)31、可変表示制御ユニット29と遊技制御基板31との間の信号を中継するための中継基板33、および景品玉の払出制御を行う賞球制御用マイクロコンピュータ等が搭載された賞球制御基板37が設置されている。さらに、機構板36の下部には、モータの回転力を利用して打球を遊技領域7に発射する打球発射装置34と、遊技効果ランプ・LED28a,28b,28c、賞球ランプ51および球切れランプ52に信号を送るためのランプ制御基板35が設置されている。

また、図3はパチンコ遊技機1の遊技盤を背面からみた背面図である。誘導樋39を通った玉は、図3に示されるように、球切れ検出器187a,187bを通過して玉供給樋186a,186bを経て玉払出装置97に至る。玉払出装置97から払い出された景品玉は、連絡口45を通ってパチンコ遊技機1の前面に設けられている打球供給皿3に供給される。連絡口45の側方には、パチンコ遊技機1の前面に設けられている余剰玉受皿4に連通する余剰玉通路46が形成されている。入賞にもとづく景品玉が多数払い出されて打球供給皿3が満杯になり、ついには景品玉が連絡口45に到達した後さらに景品玉が払い出されると景品玉は、余剰玉通路46を経て余剰玉受皿4に導かれる。さらに景品玉が払い出されると、感知レバー47が満タンスイッチ48を押圧して満タンスイッチ48がオンする。その状態では、玉払出装置97内のステッピングモータの回転が停止して玉払出装置97の動作が停止するとともに、必要に応じて打球発射装置34の駆動も停止する。なお、この実施の形態では、電気的駆動源の駆動によって遊技球を払い出す玉払出装置として、ステッピングモータの回転によって遊技球が払い出される玉払出装置97を例示するが、その他の駆動源によって遊技球を送り出す構造の玉払出装置を用いてもよいし、電気的駆動源の駆動によってストッパを外し遊技球の自重によって払い出しがなされる構造の玉払出装置を用いてもよい。

賞球払出制御を行うために、入賞口スイッチ19a,24a、始動口スイッチ17およびVカウントスイッチ22からの信号が、主基板31に送られる。主基板31のCPU56は、始動口スイッチ17がオンすると6個の賞球払出に対応した入賞が発生したことを知る。また、カウントスイッチ23がオンすると15個の賞球払出に対応した入賞が発生したことを知る。そして、入賞口スイッチがオンすると10個の賞球払出に対応した入賞が発生したことを知る。なお、この実施の形態では、例えば、入賞口24に入賞した遊技球は、入賞口24からの入賞球流路に設けられている入賞口スイッチ24aで検出され、入賞口19に入賞した遊技球は、入賞口19からの入賞球流路に設けられている入賞口スイッチ19aで検出される。

図4は、主基板31における回路構成の一例を示すブロック図である。なお、図4には、賞球制御基板37、ランプ制御基板35、音制御基板70、発射制御基板91および表示制御基板80も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する基本回路53と、ゲートスイッチ12、始動口スイッチ17、Vカウントスイッチ22、カウントスイッチ23および入賞口スイッチ19a,24aからの信号を基本回路53に与えるスイッチ回路58と、可変入賞球装置15を開閉するソレノイド16および開閉板20を開閉するソレノイド21を基本回路53からの指令に従って駆動するソレノイド回路59と、始動記憶表示器18の点灯および滅灯を行うとともに7セグメントLEDによる可変表示器10と装飾ランプ25とを駆動するランプ・LED回路60とが搭載されている。

また、基本回路53から与えられるデータに従って、大当りの発生を示す大当り情報、可変表示部9の画像表示開始に利用された始動入賞球の個数を示す有効始動情報、確率変動が生じたことを示す確変情報等をホール管理コンピュータ等のホストコンピュータに対して出力する情報出力回路64を含む。

基本回路53は、ゲーム制御用のプログラム等を記憶するROM54、ワークメモリとして使用される揮発性記憶手段の一例であるRAM55、制御用のプログラムに従って制御動作を行うCPU56およびI/Oポート部57を含む。この実施の形態では、ROM54,RAM55はCPU56に内蔵されている。すなわち、CPU56は、1チップマイクロコンピュータである。なお、1チップマイクロコンピュータは、少なくともRAM55が内蔵されていればよく、ROM54およびI/Oポート部57は外付けであっても内蔵されていてもよい。また、I/Oポート部57は、マイクロコンピュータにおける情報入出力可能な端子である。

さらに、主基板31には、電源投入時に基本回路53をリセットするための初期リセット回路65と、基本回路53から与えられるアドレス信号をデコードしてI/Oポート部57のうちのいずれかのI/Oポートを選択するための信号を出力するアドレスデコード回路67とが設けられている。

なお、玉払出装置97から主基板31に入力されるスイッチ情報もあるが、図4ではそれらは省略されている。

遊技球を打撃して発射する打球発射装置は発射制御基板91上の回路によって制御される駆動モータ94で駆動される。そして、駆動モータ94の駆動力は、操作ノブ5の操作量に従って調整される。すなわち、発射制御基板91上の回路によって、操作ノブ5の操作量に応じた速度で打球が発射されるように制御される。

図5は、電源監視および電源バックアップのためのCPU56周りの一構成例を示すブロック図である。図5に示すように、電源基板に搭載されている第1の電源監視回路(第1の電源監視手段)からの電圧低下信号が、CPU56のマスク不能割込端子(NMI端子)に入力されている。第1の電源監視回路は、遊技機が使用する各種直流電源のうちのいずれかの電源の電圧を監視して電源電圧低下を検出する回路である。従って、CPU56は、マスク不能割込(NMI)によって電源断の状況を確認することができる。

主基板31には、第2の電源監視回路903が搭載されている。この例では、第2の電源監視回路903において、電源監視用IC904が、第1の電源監視回路が監視する電源電圧と等しい電源電圧である+30V電源電圧を監視して電圧値が所定値以下になるとローレベルの電圧低下信号を発生する。そして、例えば、電源基板に搭載される第1の電源監視回路の検出電圧(電圧低下信号を出力することになる電圧)を+16Vとし、第2の電源監視回路903の検出電圧を+8Vとする。そのように構成した場合には、同一の電圧を監視するので、第1の電圧監視回路が電圧低下信号を出力するタイミングと第2の電圧監視回路が電圧低下信号を出力するタイミングの差を所望の所定期間に確実に設定することができる。所望の所定期間とは、第1の電源監視回路からの電圧低下信号に応じて電源断時処理を開始してから電源断時処理が確実に完了するまでの期間である。

第2の電源監視回路903からの電圧低下信号は、初期リセット回路65からの初期リセット信号と論理和をとられた後に、CPU56のリセット端子に入力される。従って、CPU56は、初期リセット回路65からの初期リセット信号がローレベルを呈しているとき、または、第2の電源監視回路903からの電圧低下信号がローレベルを呈しているときに、システムリセット状態(非動作状態)になる。

なお、初期リセット回路65のリセットIC651は、遊技機に電源が投入され+5V電源の電圧が上昇していくときに、+5V電源電圧が所定値以上になると、出力信号をハイレベルにする。すなわち、初期リセット信号をオフ状態にする。

CPU56等の駆動電源である+5V電源から電力が供給されていない間、RAMの少なくとも一部は、電源基板から供給されるバックアップ電源によってバックアップされ、遊技機に対する電源が断しても内容は保存される。そして、+5V電源が復旧すると、初期リセット回路65からリセット信号が発せられるので、CPU56は、通常の動作状態に復帰する。そのとき、必要なデータがバックアップされているので、停電等からの復旧時には停電発生時の遊技状態に復帰することができる。

図6は、電源基板910の一構成例を示すブロック図である。電源基板910は、主基板31、表示制御基板80、音制御基板70、ランプ制御基板35および賞球制御基板37等の遊技装置制御基板と独立して設置され、遊技機内の各遊技装置制御基板および機構部品が使用する電圧を生成する。この例では、AC24V、DC+30V、DC+21V、DC+12VおよびDC+5Vを生成する。また、バックアップ電源となるコンデンサ916は、DC+5Vすなわち各基板上のIC等を駆動する電源のラインから充電される。

トランス911は、交流電源からの交流電圧を24Vに変換する。AC24V電圧は、コネクタ915に出力される。また、整流回路912は、AC24Vから+30Vの直流電圧を生成し、DC−DCコンバータ913およびコネクタ915に出力する。DC−DCコンバータ913は、+21V、+12Vおよび+5Vを生成してコネクタ915に出力する。コネクタ915は例えば中継基板に接続され、中継基板から各遊技装置制御基板および機構部品に必要な電圧の電力が供給される。なお、トランス911の入力側には、遊技機に対する電源供給を停止したり開始させたりするための電源スイッチ918が設置されている。

DC−DCコンバータ913からの+5Vラインは分岐してバックアップ+5Vラインを形成する。バックアップ+5Vラインとグラウンドレベルとの間には大容量のコンデンサ916が接続されている。コンデンサ916は、遊技機に対する電力供給が遮断されたときの遊技装置制御基板のバックアップRAM(電源バックアップされているRAMすなわち記憶内容保持状態となりうる記憶手段)に対して記憶状態を保持できるように電力を供給するバックアップ電源となる。また、+5Vラインとバックアップ+5Vラインとの間に、逆流防止用のダイオード917が挿入される。

なお、バックアップ電源として、+5V電源から充電可能な電池を用いてもよい。電池を用いる場合には、+5V電源から電力供給されない状態が所定時間継続すると容量がなくなるような充電池が用いられる。

また、電源基板910には、上述した第1の電源回路を構成する電源監視用IC902が搭載されている。電源監視用IC902は、+30V電源電圧を導入し、+30V電源電圧を監視することによって電源断の発生を検出する。具体的には、+30V電源電圧が所定値(この例では+16V)以下になったら、電源断が生ずるとして電圧低下信号を出力する。なお、+30V電源電圧は、交流から直流に変換された直後の電圧である。電源監視用IC902からの電圧低下信号は、主基板31や賞球制御基板37等に供給される。

電源監視用IC902が電源断を検知するための所定値は、通常時の電圧より低いが、各遊技装置制御基板上のCPUが暫くの間動作しうる程度の電圧である。また、電源監視用IC902が、CPUを駆動するための電圧(この例では+5V)よりも高く、かつ、交流から直流に変換された直後の電圧を監視するように構成されているので、CPUが必要とする電圧に対して監視範囲を広げることができる。従って、より精密な監視を行うことができる。さらに、監視電圧として+30Vを用いる場合には、遊技機の各種スイッチに供給される電圧が+12Vであることから、電源瞬断時のスイッチオン誤検出の防止も期待できる。すなわち、+30V電源の電圧を監視すると、+30V作成の以降に作られる+12Vが落ち始める以前の段階でそれの低下を検出できる。よって、+12V電源の電圧が低下するとスイッチ出力がオン状態を呈するようになるが、+12Vより早く低下する+30V電源電圧を監視して電源断を認識すれば、スイッチ出力がオン状態を呈する前に電源復旧待ちの状態に入ってスイッチ出力を検出しない状態となることができる。

また、電源監視用IC902は、遊技装置制御基板とは別個の電源基板910に搭載されているので、第1の電源監視回路から複数の遊技装置制御基板に電圧低下信号を供給することができる。電圧低下信号を必要とする遊技装置制御基板が幾つあっても第1の電源監視手段は1つ設けられていればよいので、各遊技装置制御基板における各遊技装置制御手段が後述する電源復帰制御を行っても、遊技機のコストはさほど上昇しない。

次に遊技機の動作について説明する。

図7は、主基板31におけるCPU56が実行するメイン処理を示すフローチャートである。遊技機に対する電源が投入されると、メイン処理において、CPU56は、まず、停電からの復旧時であったか否か確認する(ステップS1)。停電からの復旧時であったか否かは、例えば、電源断時にバックアップRAM領域に設定される電源断フラグによって確認される。

すなわち、RAM領域が電源バックアップされている状態で遊技機に電源が再投入されるとRAMには電源断時の状態が保存されているので電源断フラグも正確に保存されている。RAM領域が電源バックアップされていない状態で遊技機に電源が投入されると、RAMの内容は不定になっているので、電源断フラグの値は正しくない。従って、電源断フラグのセット状態に応じて停電からの復旧時であったか否か確認することができる。なお、仮に、電源バックアップされていない状態で遊技機に電源が投入されたときに電源断フラグがセット状態になってしまったとしても、後述するパリティ診断によって、停電からの復旧時であったと誤って判断されてしまうことは防止される。

停電からの復旧時であった場合には、CPU56は、後述する停電復旧処理を実行する(ステップS4)。なお、停電からの復旧時でない場合には、CPU56は、通常の初期化処理を実行する(ステップS2)。その後、メイン処理では、タイマ割込フラグの監視(ステップS6)の確認を行うループ処理に移行する。なお、ループ内では、表示用乱数更新処理(ステップS5)も実行される。

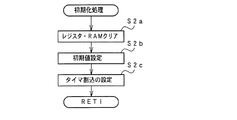

通常の初期化処理では、図8に示すように、レジスタおよびRAMのクリア処理(ステップS2a)と、必要な初期値設定処理(ステップS2b)が行われた後に、2ms毎に定期的にタイマ割込がかかるようにCPU56に設けられているタイマレジスタの初期設定(タイムアウトが2msであることと繰り返しタイマが動作する設定)が行われる(ステップS2c)。すなわち、ステップS2cで、タイマ割込を能動化する処理と、タイマ割込インタバルを設定する処理とが実行される。

従って、この実施の形態では、CPU56の内部タイマが繰り返しタイマ割込を発生するように設定される。この実施の形態では、繰り返し周期は2msに設定される。そして、図9に示すように、タイマ割込が発生すると、CPU56は、タイマ割込フラグをセットする(ステップS11)。

CPU56は、ステップS6において、タイマ割込フラグがセットされたことを検出すると、タイマ割込フラグをリセットするとともに(ステップS7)、遊技制御処理を実行する(ステップS9)。以上の制御によって、この実施の形態では、遊技制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理ではフラグセットのみがなされ、遊技制御処理はメイン処理において実行されるが、タイマ割込処理で遊技制御処理を実行してもよい。

図10は、遊技制御処理を示すフローチャートである。遊技制御処理において、CPU56は、まず、表示制御基板80に送出される表示制御コマンドをRAM55の所定の領域に設定する処理を行った後に(表示制御データ設定処理:ステップS21)、表示制御コマンドを出力する処理を行う(表示制御データ出力処理:ステップS22)。

次いで、各種出力データの格納領域の内容を各出力ポートに出力する処理を行う(データ出力処理:ステップS23)。また、ホール管理用コンピュータに出力される大当り情報、始動情報、確率変動情報などの出力データを格納領域に設定する出力データ設定処理を行う(ステップS24)。さらに、パチンコ遊技機1の内部に備えられている自己診断機能によって種々の異常診断処理が行われ、その結果に応じて必要ならば警報が発せられる(エラー処理:ステップS25)。

次に、遊技制御に用いられる大当り判定用の乱数等の各判定用乱数を示す各カウンタを更新する処理を行う(ステップS26)。

さらに、CPU56は、特別図柄プロセス処理を行う(ステップS27)。特別図柄プロセス制御では、遊技状態に応じてパチンコ遊技機1を所定の順序で制御するための特別図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、特別図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。また、普通図柄プロセス処理を行う(ステップS28)。普通図柄プロセス処理では、7セグメントLEDによる可変表示器10を所定の順序で制御するための普通図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、普通図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。

さらに、CPU56は、スイッチ回路58を介して、ゲートセンサ12、始動口センサ17、カウントセンサ23および入賞口スイッチ19a,24aの状態を入力し、各入賞口や入賞装置に対する入賞があったか否か判定する(スイッチ処理:ステップS29)。CPU56は、さらに、停止図柄の種類を決定する乱数等の表示用乱数を更新する処理を行う(ステップS30)。

また、CPU56は、賞球制御基板37との間の信号処理を行う(ステップS31)。すなわち、所定の条件が成立すると賞球制御基板37に賞球制御コマンドを出力する。賞球制御基板37に搭載されている賞球制御用CPUは、賞球制御コマンドに応じて玉払出装置97を駆動する。

以上のように、メイン処理には遊技制御処理に移行すべきか否かを判定する処理が含まれ、CPU56の内部タイマが定期的に発生するタイマ割込にもとづくタイマ割込処理で遊技制御処理に移行すべきか否かを判定するためのフラグがセットされるので、遊技制御処理の全てが確実に実行される。つまり、遊技制御処理の全てが実行されるまでは、次回の遊技制御処理に移行すべきか否かの判定が行われないので、遊技制御処理中の全ての各処理が実行完了することは保証されている。

従来の一般的な遊技制御処理は、定期的に発生する外部割込によって、強制的に最初の状態に戻されていた。図10に示された例に則して説明すると、例えば、ステップS31の処理中であっても、強制的にステップS21の処理に戻されていた。つまり、遊技制御処理中の全ての各処理が実行完了する前に、次回の遊技制御処理が開始されてしまう可能性があった。

なお、ここでは、主基板31のCPU56が実行する遊技制御処理は、CPU56の内部タイマが定期的に発生するタイマ割込にもとづくタイマ割込処理でセットされるフラグに応じて実行されたが、定期的に(例えば2ms毎)信号を発生するハードウェア回路を設け、その回路からの信号をCPU56の外部割込端子に導入し、割込信号によって遊技制御処理に移行すべきか否かを判定するためのフラグをセットするようにしてもよい。そのように構成した場合にも、遊技制御処理の全てが実行されるまでは、フラグの判定が行われないので、遊技制御処理中の全ての各処理が実行完了することが保証される。

図11は、電源基板910の第1の電源監視回路からの電圧低下信号にもとづくNMIに応じて実行される停電発生NMI処理の一例を示すフローチャートである。停電発生NMI処理において、CPU56は、まず、割込禁止に設定する(ステップS41)。停電発生NMI処理ではRAM内容の保存を確実にするためにチェックサムの生成処理を行う。その処理中に他の割込処理が行われたのではチェックサムの生成処理が完了しないうちにCPUが動作し得ない電圧にまで低下してしまうことがことも考えられるので、まず、他の割込が生じないような設定がなされる。

次いで、CPU56は、電源断フラグが既にセットされているか否か確認する(ステップS42)。電源断フラグが既にセットされていれば、以後の処理を行わない。電源断フラグがセットされていなければ、以下の電源断時処理を実行する。すなわち、ステップS43からステップS49の処理を実行する。まず、全ての出力ポートをオフ状態にする(ステップS43)。そして、必要ならば各レジスタの内容をバックアップRAM領域に格納する(ステップS44)。さらに、バックアップRAM領域のバックアップチェックデータ領域に適当な初期値を設定し(ステップS45)、初期値およびバックアップRAM領域のデータについて順次排他的論理和をとって(ステップS46)、最終的な演算値をバックアップパリティデータ領域に設定する(ステップS47)。その後、電源断フラグをセットする(ステップS48)。また、RAMアクセス禁止状態にする(ステップS49)。電源電圧が低下していくときには、各種信号線のレベルが不安定になってRAM内容が化ける可能性があるが、このようにRAMアクセス禁止状態にしておけば、バックアップRAM内のデータが化けることはない。

次いで、CPU56は、ループ処理にはいる。すなわち、何らの処理もしない状態になる。従って、図5に示された電源監視用IC904からのリセット信号によって外部から動作禁止状態にされる前に、内部的に動作停止状態になる。よって、電源断時に確実にCPU56は動作停止する。その結果、上述したRAMアクセス禁止の制御および動作停止制御によって、電源電圧が低下していくことに伴って生ずる可能性がある異常動作に起因するRAMの内容破壊等を確実に防止することができる。

なお、この実施の形態では、停電発生NMI処理では最終部でプログラムをループ状態にしたが、ホールト(HALT)命令を発行するように構成してもよい。

また、RAMアクセス禁止にする前にセットされる電源断フラグは、上述したように、電源投入時において停電からの復旧か否かを判断する際に使用される。また、ステップS41からS49の処理は、第2の電源監視手段が電圧低下信号を発生する前に完了する。換言すれば、第2の電源監視手段が電圧低下信号を発生する前に完了するように、第1の電圧監視手段および第2の電圧監視手段の検出電圧の設定が行われている。

この実施の形態では、電源断時処理開始時に、電源断フラグの確認が行われる。そして、電源断フラグが既にセットされている場合には電源断時処理を実行しない。上述したように、電源断フラグは、電源断時処理が完了したことを示すフラグである。従って、例えば、リセット待ちのループ状態で何らかの原因で再度NMIが発生したとしても、電源断時処理が重複して実行されてしまうようなことはない。

図12は、停電復旧処理(ステップS4)の一例を示すフローチャートである。停電復旧処理において、CPU56は、まず、バックアップRAM領域のデータチェック(この例ではパリティチェック)を行う(ステップS51)。不測の電源断が生じた後に復旧した場合には、バックアップRAM領域のデータは保存されていたはずであるから、チェック結果は正常になる。チェック結果が正常でない場合には、内部状態を電源断時の状態に戻すことができないので、停電復旧時でない電源投入時に実行される初期化処理(ステップS2)と同様の初期化処理を実行する(ステップS52,S54)。

チェック結果が正常であれば、CPU56は、内部状態を電源断時の状態に戻すための遊技状態復旧処理を行うとともに(ステップS53)、電源断フラグをクリアする(ステップS55)。

なお、ここでは、ステップS1で停電からの復旧か否かを確認し、停電からの復旧時であればパリティチェックを行ったが、最初に、パリティチェックを実行し、チェック結果が正常でなければ停電からの復旧ではないと判断してステップS2の初期化処理を実行し、チェック結果が正常であれば遊技状態復帰処理を行ってもよい。すなわち、パリティチェックの結果をもって停電からの復旧であるか否かを判断してもよい。

図13は、バックアップパリティデータ作成方法を説明するための説明図である。ただし、図13に示す例では、簡単のために、バックアップデータRAM領域のデータのサイズを3バイトとする。電源電圧低下にもとづく停電発生処理において、図13(A)に示すように、バックアップチェックデータ領域に、初期データ(この例では00H)が設定される。次に、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)がバックアップパリティデータ領域に設定される。

電源が再投入されたときには、停電復旧処理においてパリティ診断が行われるが、図13(B)はパリティ診断の例を示す説明図である。バックアップ領域の全データがそのまま保存されていれば、電源再投入時に、図13(A)に示すようなデータがバックアップ領域に設定されている。

ステップS51の処理において、CPU56は、バックアップRAM領域のバックアップパリティデータ領域に設定されていたデータ(この例では「39H」)を初期データとして、バックアップデータ領域の各データについて順次排他的論理和をとる処理を行う。バックアップ領域の全データがそのまま保存されていれば、最終的な演算結果は、「00H」、すなわちバックアップチェックデータ領域に設定されているデータと一致する。バックアップRAM領域内のデータにビット誤りが生じていた場合には、最終的な演算結果は「00H」にならない。

よって、CPU56は、最終的な演算結果とバックアップチェックデータ領域に設定されているデータとを比較して、一致すればパリティ診断正常とする。一致しなければ、パリティ診断異常とする。

なお、この実施の形態では、停電発生処理で、チェックデータ(この例ではパリティデータ)の生成が行われたが、チェックデータの生成を行わず、電源断フラグのセットのみを行うようにしてもよい。

以上のように、この実施の形態では、遊技制御手段には、遊技機の電源が断しても、所定期間電源バックアップされるバックアップRAMが設けられ、電源投入時に、CPU56(具体的にはCPU56が実行するプログラム)は、バックアップRAMがバックアップ状態にあればバックアップデータにもとづいて遊技状態を回復させる遊技状態復旧処理(ステップS53)を行うように構成される。従って、電源断が発生しても遊技者に不利益がもたらされることを防止することができる遊技機が提供される。

以下、遊技状態復旧処理について説明する。

まず、この実施の形態において、主基板31のCPU56が、表示制御基板80、音制御基板70およびランプ制御基板35に送出する表示制御コマンド、音制御コマンドおよびランプ制御コマンドについて説明する。各制御コマンドは、図10に示された遊技制御処理における特別図柄プロセス処理(ステップS28)で遊技進行に応じて送出することが決定され、表示制御データ設定処理(ステップS21)で具体的なデータが設定され、表示制御データ出力処理(ステップS22)で出力ポートから出力されることによって送出される。

図14(A)は、可変表示部9における図柄変動に関する各制御コマンドの送出タイミング例を示す説明図である。この実施の形態では、主基板31のCPU56は、図柄変動を開始させるときに、表示制御基板80、音制御基板70およびランプ制御基板35のそれぞれに対して変動開始コマンドを送出する。表示制御基板80に対しては、さらに、左右中図柄の確定図柄を示す図柄指定コマンドを送出する。

そして、図柄変動を確定させるときに、表示制御基板80、音制御基板70およびランプ制御基板35のそれぞれに対して変動停止コマンドを送出する。表示制御基板80、音制御基板70およびランプ制御基板35に搭載されている各CPUは、変動開始コマンドで指定された変動態様に応じた表示制御、音発生制御およびランプ点灯制御を行う。なお、変動開始コマンドには変動時間を示す情報が含まれている。

図14(B)は、可変表示部9の表示結果が所定の大当り図柄であった場合に実行される大当り遊技に関する各制御コマンドの送出タイミング例を示す説明図である。この実施の形態では、主基板31のCPU56は、大当り遊技開始時に、表示制御基板80、音制御基板70およびランプ制御基板35のそれぞれに対して大当り開始コマンドを送出する。また、所定時間経過後に、1ラウンド(1R)指定コマンドを送出する。表示制御基板80、音制御基板70およびランプ制御基板35に搭載されている各CPUは、大当り開始コマンドを受信すると、大当り開始時の表示制御、音発生制御およびランプ点灯制御を行う。また、1ラウンド指定コマンドを受信すると、大当り中の表示制御、音発生制御およびランプ点灯制御を行う。ただし、表示制御基板80のCPUは、1ラウンド目の表示を行う。

その後、主基板31のCPU56は、表示制御基板80に対して各ラウンドを示すコマンド等を順次送出する。表示制御基板80のCPUは、それらのコマンドに応じて対応する表示制御を行う。

また、大当り遊技終了時に、主基板31のCPU56は、表示制御基板80、音制御基板70およびランプ制御基板35のそれぞれに対して大当り終了コマンドを送出する。そして、所定時間経過後に、通常画面表示コマンドを送出する。各遊技装置制御手段は、通常画面表示コマンドを受信すると、制御状態を遊技待ちの状態にする。

図15は、図12に示された停電復旧処理で行われる遊技状態復旧処理の一例を示すフローチャートである。この例では、CPU56は、レジスタ内容を復元する必要があれば、バックアップRAMに保存されていた値をレジスタに復元する(ステップS61)。そして、バックアップRAMに保存されていたデータにもとづいて停電時の遊技状態を確認する。例えば、特別図柄プロセス処理の進行状況に対応した特別図柄プロセスフラグの値によって遊技状態を確認することができる。

遊技状態が図柄変動中であった場合には(ステップS62)、変動開始コマンドを表示制御基板80、音制御基板70およびランプ制御基板35に送出する制御を行う(ステップS63)。また、遊技状態が大当り遊技中であった場合には(ステップS64)、停電前に最後の送出された制御コマンドを表示制御基板80、音制御基板70およびランプ制御基板35に送出する制御を行う(ステップS65)。そして、それ以外の遊技状態であった場合には、例えば、通常画面表示コマンドを制御コマンドを表示制御基板80、音制御基板70およびランプ制御基板35に送出する制御を行う(ステップS66)。また、例えば、大当り中であった場合の可変入賞球装置15の状態復帰は、RAMのデータが保存されているため、後の遊技制御処理内で自動的に行われる。

図16は、停電が発生した後に復旧した場合の制御状態の一例を示す説明図である。図16において、可変表示の状態は表示制御基板80のCPU(表示制御手段)によって実現され、音の状態は音制御基板70のCPU(音制御手段)によって実現され、ランプの状態はランプ制御基板35のCPU(ランプ制御手段)によって実現される。

図16(A)は、図柄変動中に停電が生じた後に復旧した場合の例を示す。この場合には、電源復旧時に、主基板31から変動開始コマンドが送出される(図16におけるステップS63)。変動開始コマンドは、図柄変動開始時に送出されるコマンドであるから、可変表示制御、音制御およびランプ制御の状態は、変動開始時の状態に戻る。この実施の形態では、変動開始コマンドには変動時間を指定する情報を含まれ、主基板31のCPU56は変動開始コマンド送出後では変動終了時の確定コマンド(変動停止コマンド)まで何も送出しない(図柄指定コマンドを除く)。従って、図柄変動中に停電が生じた場合には、変動途中の状態から変動を再開することはできないが、変動開始コマンドを再送出することによって、表示制御、音制御およびランプ制御は同期した状態に戻る。

なお、主基板31において、変動開始時に使用した各種パラメータはバックアップRAMに保存されている。従って、電源復旧後の変動における表示結果(確定図柄)等は、停電によって中断した変動においてなされるはずであった表示結果等と同じである。従って、遊技者に不利益が与えられるということはない。

図16(B)は、大当り遊技中に停電が生じた後に復旧した場合の例を示す。この場合には、電源復旧時に、主基板31から停電前の最後に表示制御基板80、音制御基板70およびランプ制御基板35に送出されたコマンドが再送出される(図15におけるステップS65)。従って、音制御およびランプ制御は、大当り遊技中の制御状態に戻る。また、表示制御も、停電時に行われていた状態に戻る。

なお、主基板31において、大当り遊技中の各種パラメータ(大入賞口開放回数、大入賞口入賞球数等)はバックアップRAMに保存されている。従って、遊技者にとっての遊技状態も停電前の状態に戻るので、遊技者に不利益が与えられるということはない。

なお、上記の実施の形態では、遊技制御手段において、データ保存処理および復旧処理が行われる場合について説明したが、賞球制御手段、音声制御手段、ランプ制御手段および表示制御手段におけるRAMの一部も電源バックアップされ、賞球制御手段、表示制御手段、音制御手段およびランプ制御手段も、上述したような処理を行ってもよい。ただし、賞球制御手段、表示制御手段、音制御手段およびランプ制御手段は、復旧時にコマンド送出処理を行う必要はない。

また、この実施の形態では、2つの電源監視回路が設けられている。そして、電源電圧が低下していくときに、第2の電源監視手段(この例では電源監視用IC904)が電圧低下信号を発生する時期は、第1の電源監視手段(この例では電源監視用IC902)が電圧低下信号を発生する時期よりも遅くなるように設定されている。さらに、第2の電源監視手段からの電圧低下信号は、CPU56のリセット端子に入力されている。

すると、CPU56は、図17に示すように、第1の電源監視回路(電源監視用IC902)からの電圧低下信号にもとづいて停電発生処理(電源断時処理)を実行した後に電源断待ちに入るのであるが、電源断待ち状態において、リセット状態に入ることになる。すなわち、CPU56の動作が停止する。電源待ち状態では+5V電源電圧値が徐々に低下するので入出力状態が不定になるが、CPU56はリセット状態になるので、不定データにもとづいて異常動作してしまうことは防止される。

このように、この実施の形態では、CPU56が、第1の電源監視手段からの検出出力の入力に応じて電源断時処理を実行するとともに、第2の電源監視手段(電源監視用IC904)からの検出出力の入力に応じてシステムリセットされるように構成したので、電源断時に確実なデータ保存を行うことができ、遊技者に不利益がもたらされることを防止することができる。

さらに、この実施の形態では、停電発生処理(電源断時処理)において、電源断時処理が既に実行されたことを示す電源断時フラグがセットされている場合には電源断時処理を実行しないように構成されている。電源が断する過程では一般に電源電圧が不安定になるので、図17に破線で示すように再度NMIが発生する可能性がある。すると、停電発生処理において電源断時フラグの確認を行わない場合には、再度発生したNMIによって再度電源断時処理が実行される。

最初に実行された正規の電源断時処理では、例えばレジスタの内容をバックアップRAMに格納する処理が行われる(図11におけるステップS44参照)。最初に実行された正規の電源断時処理後のリセット待ちの状態では電源電圧は徐々に低下していくので、レジスタの内容が破壊される可能性もある。すなわち、レジスタ値は、電源断が検出されたときの状態(最初にNMIが発生したとき)から変化している可能性がある。そのような状態で再度電源断時処理が実行されると、電源断が検出されたときの状態のレジスタ値とは異なる値がバックアップRAMに格納されてしまう。すると、電源復旧時に実行される停電復旧処理において、電源断が検出されたときの状態のレジスタ値とは異なる値がレジスタに復旧されてしまう。その結果、電源断時の遊技状態とは異なる遊技状態が再現されてしまう可能性が生ずる。

ところが、この実施の形態のように、既に電源断時処理が実行された後には、NMIが発生したとしても電源断時処理を実行しないように構成すれば、電源復旧時に、電源断時の遊技状態とは異なる遊技状態が再現されてしまう可能性はなくなる。

上記の実施の形態では、第1の電源監視手段は電源基板910に搭載され、第2の電源監視手段は主基板31に搭載されていたが、第2の電源監視手段を電源基板910に搭載し、第1の電源監視手段を主基板31に搭載してもよい。

図18は、第2の電源監視手段が搭載された電源基板910の構成例を示すブロック図である。この例では、第2の電源監視手段として、+30V電源電圧が例えば+8Vになると電圧低下信号を出力する電源監視用IC904が搭載されている。

図19は、第1の電源監視手段が搭載された主基板31のCPU56周りの構成を示すブロック図である。この例では、第1の電源監視手段として、+30V電源電圧が例えば+16Vになると電圧低下信号を出力する電源監視用IC902が搭載されている。そして、電源監視用IC902からの電圧低下信号がCPU56のNMI端子に入力されている。また、電源基板910の電源監視用IC904からの電圧低下信号は、初期リセット回路65からの初期リセット信号と論理和をとられた後に、CPU56のリセット端子に入力される。

このような構成によっても、上述した実施の形態の場合と同様の制御を実現することができる。

なお、上記の実施の形態では、第1の電源監視手段からの検出信号がマイクロコンピュータのNMI端子に入力されNMI処理によって電源断時処理が実行される場合を例にとったが、第1の電源監視手段からの検出信号をマスク可能割込端子(IRQ端子)に入力しIRQ端子への割込信号にもとづく割込処理によって電源断時処理を実行するようにしてもよい。その場合には、割込処理プログラムは、例えば、最初に電源断フラグをチェックし既に電源断フラグがセットされていれば処理を終了し、電源断フラグがセットされていなければ電源断時処理を実行して電源断フラグをセットした後にループするかHALT命令を発行するように構成される。あるいは、最初に割込マスクをセットし、電源断時処理を実行して電源断フラグをセットした後にループするかHALT命令を発行するように構成される。

また、上記の各実施の形態のパチンコ遊技機1は、始動入賞にもとづいて可変表示部9に可変表示される特別図柄の停止図柄が所定の図柄の組み合わせになると所定の遊技価値が遊技者に付与可能になる第1種パチンコ遊技機であったが、始動入賞にもとづいて開放する電動役物の所定領域への入賞があると所定の遊技価値が遊技者に付与可能になる第2種パチンコ遊技機や、始動入賞にもとづいて可変表示される図柄の停止図柄が所定の図柄の組み合わせになると開放する所定の電動役物への入賞があると所定の権利が発生または継続する第3種パチンコ遊技機であっても、本発明を適用できる。

また、上記の各実施の形態では、以下のような遊技機も開示されている。

遊技制御マイクロコンピュータが、割込に応じた処理で電源断時処理が実行されたことを示す電源断フラグをセットするとともに、その処理の開始時に電源断フラグがセットされているか否かを判定しセットされていれば電源断時処理を実行しないように構成されている。

電源監視手段は、IC駆動電源よりも高い電位の電圧を監視するように構成されている。

電源監視手段は、交流から直流に変換された直後の電圧を監視するように構成されている。

遊技機には電源監視手段が電圧低下を検出した所定期間後に電源電圧低下を検出する第2の電源監視手段が設けられ、遊技制御マイクロコンピュータが、第2の電源監視手段からの検出出力の入力に応じてシステムリセットされるように構成されている。

電源監視手段は、遊技制御基板とは別個に設けられ遊技制御基板および他の基板で使用される各電圧を生成する電源基板に搭載され、第2の電源監視手段は、遊技制御基板に搭載されているように構成されている。

電源監視手段と第2の電源監視手段とは同一の電源電圧を監視し、第2の電源監視手段が電圧低下を検出する電圧は、電源監視手段が電圧低下を検出する電圧よりも低いように構成されている。

電源断時処理には、記憶手段へのアクセスを防止する処理が含まれている。

遊技制御マイクロコンピュータが、割込に応じた処理で電源断時処理が実行されたことを示す電源断フラグをセットするとともに、その処理の開始時に電源断フラグがセットされているか否かを判定しセットされていれば電源断時処理を実行しないように構成されている場合には、遊技制御マイクロコンピュータは、割込の発生に応じて電源断時処理を実行すべきか否かを容易に判断することができる。

電源監視手段が、IC駆動電源よりも高い電位の電圧を監視するように構成されている場合には、遊技制御マイクロコンピュータ等のICが必要とする電圧に対して監視範囲を広げることができ、より精密な監視を行うことができる。

電源監視手段が、交流から直流に変換された直後の電圧を監視するように構成されている場合には、電圧低下を素早く検出することができ、電源断時処理を確実に実行することができる。

遊技機には電源監視手段が電圧低下を検出した所定期間後に電源電圧低下を検出する第2の電源監視手段が設けられ、遊技制御マイクロコンピュータが、第2の電源監視手段からの検出出力の入力に応じてシステムリセットされるように構成されている場合には、システムリセットによって遊技制御マイクロコンピュータの動作が外部からも停止されるので、電源断時により確実なデータ保存を行うことができる。

電源監視手段が遊技制御基板とは別個に設けられ遊技制御基板および他の基板で使用される各電圧を生成する電源基板に搭載され、第2の電源監視手段が遊技制御基板に搭載されているように構成されている場合には、電源基板の電源監視手段から複数の制御基板に検出出力を供給することができるので、遊技機のコストはさほど上昇しない。

電源監視手段と第2の電源監視手段とは同一の電源電圧を監視し、第2の電源監視手段が電圧低下を検出する電圧は、電源監視手段が電圧低下を検出する電圧よりも低いように構成されている場合には、電源監視手段が検出出力を発生するタイミングと第2の電源監視手段が検出出力を発生するタイミングの差を所望の所定期間に確実に設定することができる。

電源断時処理には、記憶手段へのアクセスを防止する処理が含まれている場合には、電源断時に記憶手段内のデータが破壊されることをより確実に防止できる。